The New FPGA Architecture by Applying The CSBox

The New FPGA Architecture by Applying The CS-Box Structure Zhou Lin, Catherine October 13, 2003

Outline Introduction to the Xilinx FPGA architecture Introduction to the CS-box structure – Preliminaries – The connection way of pad pins and wire segments. – The connection way of logic block pins and wire segments.

Outline Experimental results – Channel width – Routing area Future work

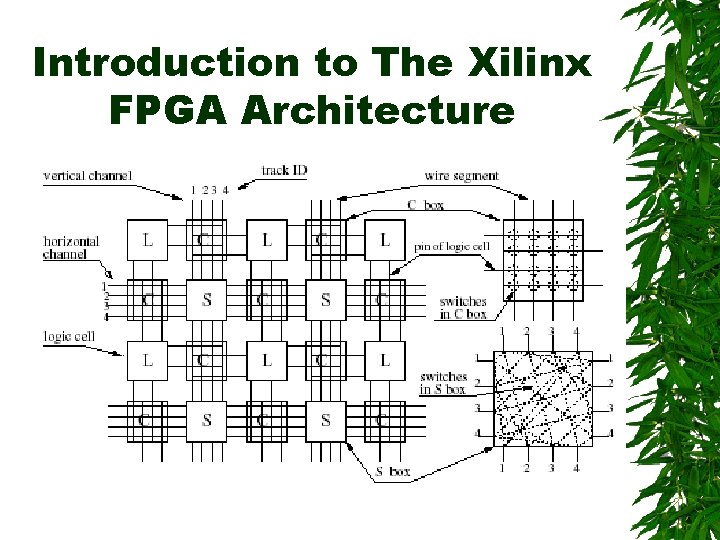

Introduction to The Xilinx FPGA Architecture

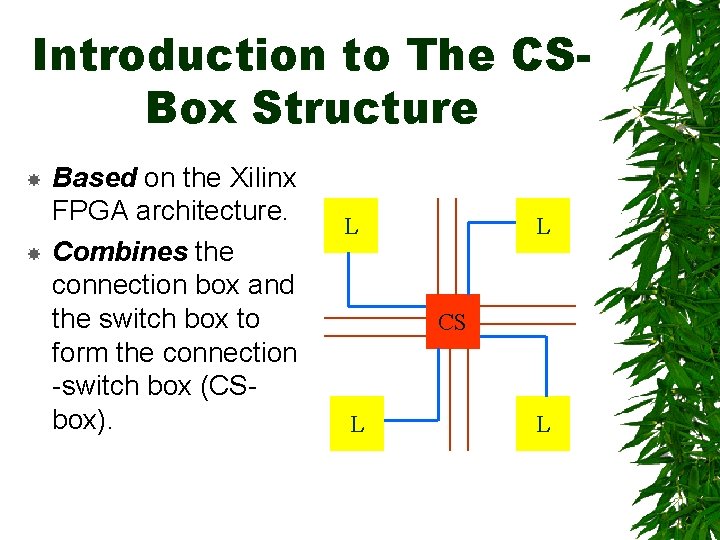

Introduction to The CSBox Structure Based on the Xilinx FPGA architecture. Combines the connection box and the switch box to form the connection -switch box (CSbox). L L CS L L

Introduction to The CSBox Structure (cont’) Two types of switches in the CS-box – Those connecting one wire segment to another. They are set in the same way as in the switch box in the Xilinx FPGA. – Those connecting one pin to one wire segment or vice versa. The way to set them is the main topic in our research.

Introduction to The CSBox Structure (cont’) Two types of CS-boxes – Containing the switches that connect pad pins to wire segments or vice versa. – Containing the switches that connect logic block pins to wire segments or vice versa.

Introduction to The CSBox Structure (cont’) Preliminaries – W: Channel width. The number of wire segments in one channel. – Fc_pad: The number of wire segments each pad pin can be connected to. – Fc_input: The number of wire segments each input logic pin can be connected to. – Fc_output: The number of wire segments each output logic pin can be connected to. – P: The number of non-global pins on each logic block or pad.

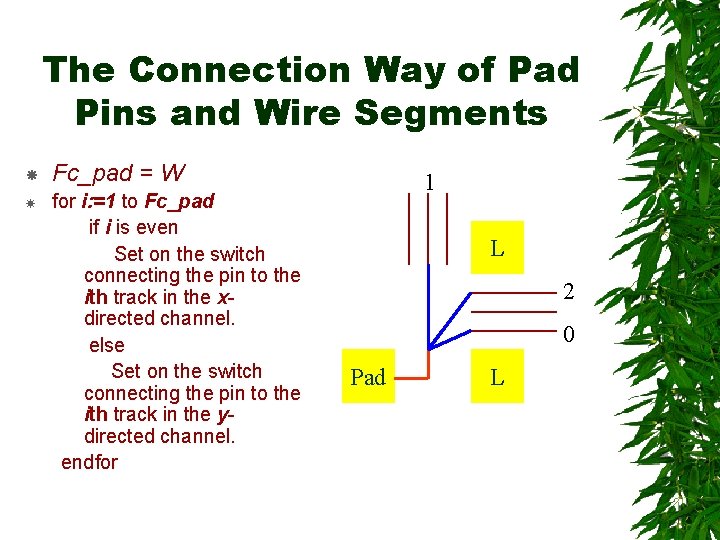

The Connection Way of Pad Pins and Wire Segments Fc_pad = W for i: =1 to Fc_pad if i is even Set on the switch connecting the pin to the ith track in the xdirected channel. else Set on the switch connecting the pin to the ith track in the ydirected channel. endfor 1 L 2 0 Pad L

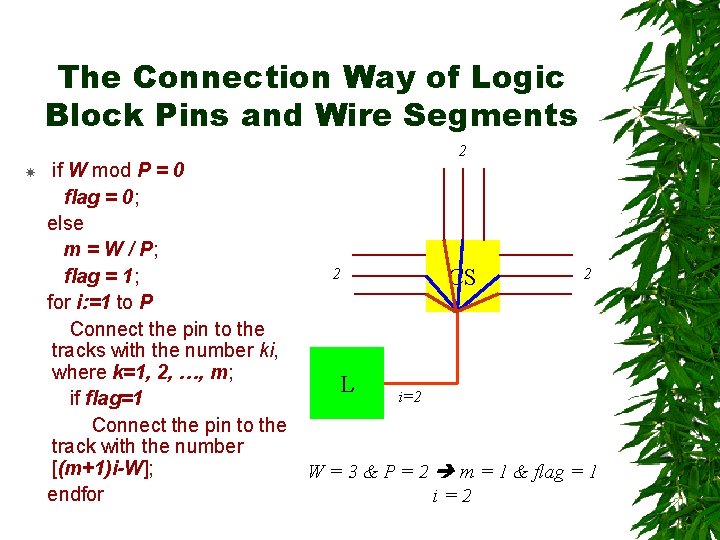

The Connection Way of Logic Block Pins and Wire Segments if W mod P = 0 flag = 0; else m = W / P; flag = 1; for i: =1 to P Connect the pin to the tracks with the number ki, where k=1, 2, …, m; if flag=1 Connect the pin to the track with the number [(m+1)i-W]; endfor 2 CS 2 L 2 i=2 W = 3 & P = 2 m = 1 & flag = 1 i=2

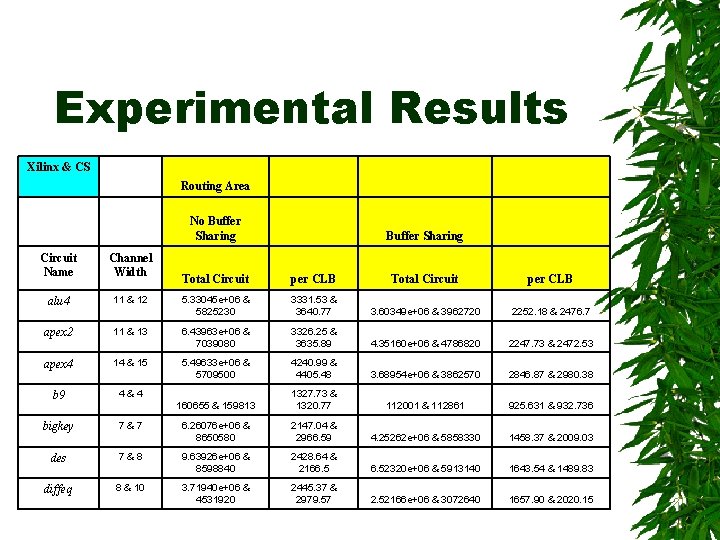

Experimental Results Xilinx & CS Routing Area No Buffer Sharing Circuit Name Channel Width alu 4 11 & 12 apex 2 11 & 13 apex 4 14 & 15 b 9 4&4 bigkey 7&7 des 7&8 diffeq 8 & 10 Buffer Sharing Total Circuit per CLB 5. 33045 e+06 & 5825230 3331. 53 & 3640. 77 3. 60349 e+06 & 3962720 2252. 18 & 2476. 7 6. 43963 e+06 & 7039080 3326. 25 & 3635. 89 4. 35160 e+06 & 4786820 2247. 73 & 2472. 53 5. 49633 e+06 & 5709500 4240. 99 & 4405. 48 3. 68954 e+06 & 3862570 2846. 87 & 2980. 38 160655 & 159813 1327. 73 & 1320. 77 112001 & 112861 925. 631 & 932. 736 6. 26076 e+06 & 8650580 2147. 04 & 2966. 59 4. 25262 e+06 & 5858330 1458. 37 & 2009. 03 9. 63926 e+06 & 8598840 2428. 64 & 2166. 52320 e+06 & 5913140 1643. 54 & 1489. 83 3. 71940 e+06 & 4531920 2445. 37 & 2979. 57 2. 52166 e+06 & 3072640 1657. 90 & 2020. 15

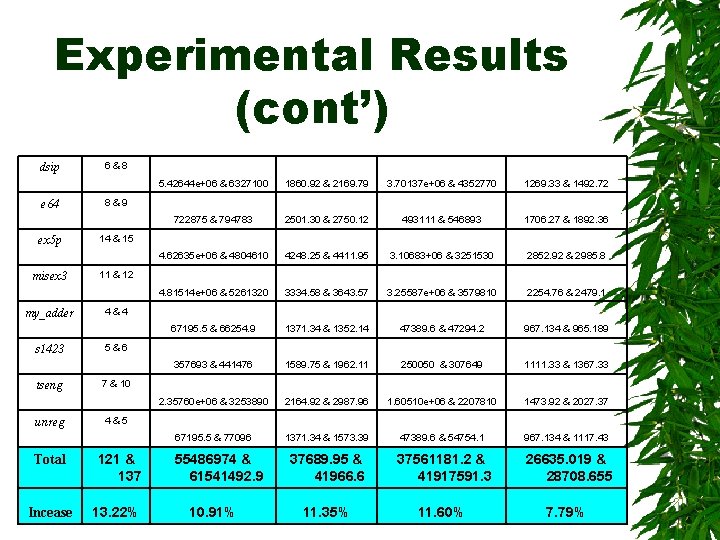

Experimental Results (cont’) dsip e 64 ex 5 p misex 3 my_adder s 1423 tseng unreg 6&8 5. 42644 e+06 & 6327100 1860. 92 & 2169. 79 3. 70137 e+06 & 4352770 1269. 33 & 1492. 72 722875 & 794783 2501. 30 & 2750. 12 493111 & 546893 1706. 27 & 1892. 36 4. 62635 e+06 & 4804610 4248. 25 & 4411. 95 3. 10683+06 & 3251530 2852. 92 & 2985. 8 4. 81514 e+06 & 5261320 3334. 58 & 3643. 57 3. 25587 e+06 & 3579810 2254. 76 & 2479. 1 67195. 5 & 66254. 9 1371. 34 & 1352. 14 47389. 6 & 47294. 2 967. 134 & 965. 189 357693 & 441476 1589. 75 & 1962. 11 250050 & 307649 1111. 33 & 1367. 33 2. 35760 e+06 & 3253890 2164. 92 & 2987. 96 1. 60510 e+06 & 2207810 1473. 92 & 2027. 37 67195. 5 & 77096 1371. 34 & 1573. 39 47389. 6 & 54754. 1 967. 134 & 1117. 43 37689. 95 & 41966. 6 37561181. 2 & 41917591. 3 26635. 019 & 28708. 655 11. 35% 11. 60% 7. 79% 8&9 14 & 15 11 & 12 4&4 5&6 7 & 10 4&5 Total 121 & 137 Incease 13. 22% 55486974 & 61541492. 9 10. 91%

Future Do more experiments – Set Fc_pad, Fc_input and Fc_output equal to W / 2. – Apply different switch box structures into the FPGA with CS-boxes.

- Slides: 13