The Motorola 68230 Parallel Interface Timer PIT A

- Slides: 12

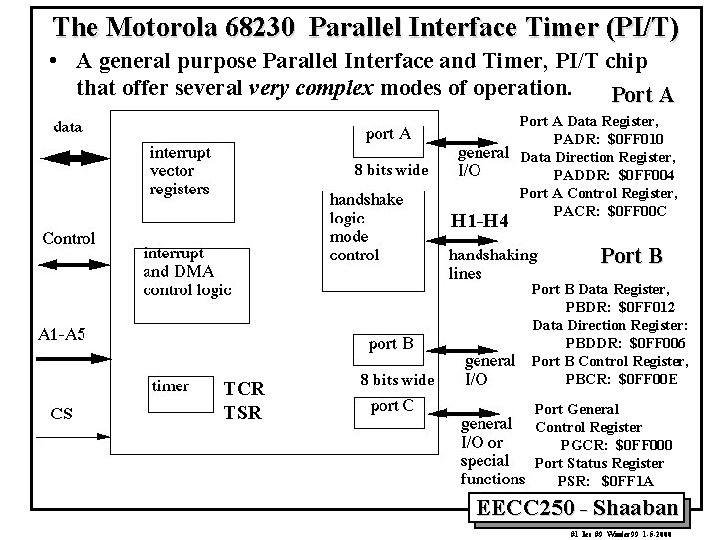

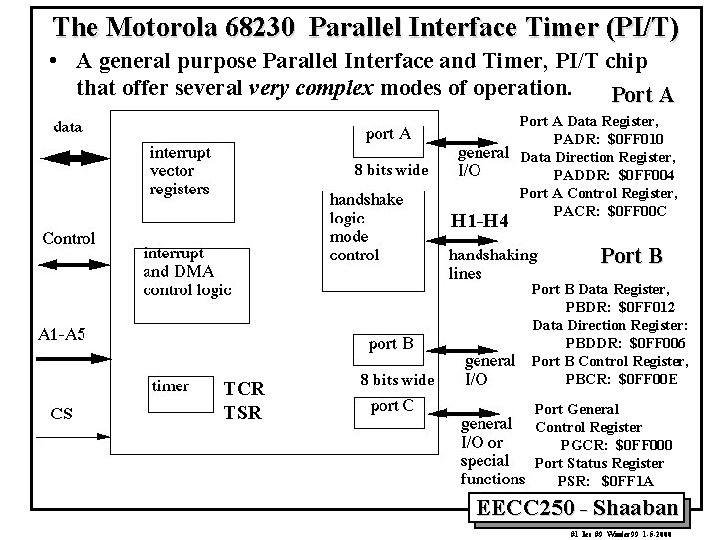

The Motorola 68230 Parallel Interface Timer (PI/T) • A general purpose Parallel Interface and Timer, PI/T chip that offer several very complex modes of operation. Port A 8 bits wide H 1 -H 4 Port A Data Register, PADR: $0 FF 010 Data Direction Register, PADDR: $0 FF 004 Port A Control Register, PACR: $0 FF 00 C Port B TCR TSR 8 bits wide Port B Data Register, PBDR: $0 FF 012 Data Direction Register: PBDDR: $0 FF 006 Port B Control Register, PBCR: $0 FF 00 E Port General Control Register PGCR: $0 FF 000 Port Status Register PSR: $0 FF 1 A EECC 250 - Shaaban #1 lec #9 Winter 99 1 -5 -2000

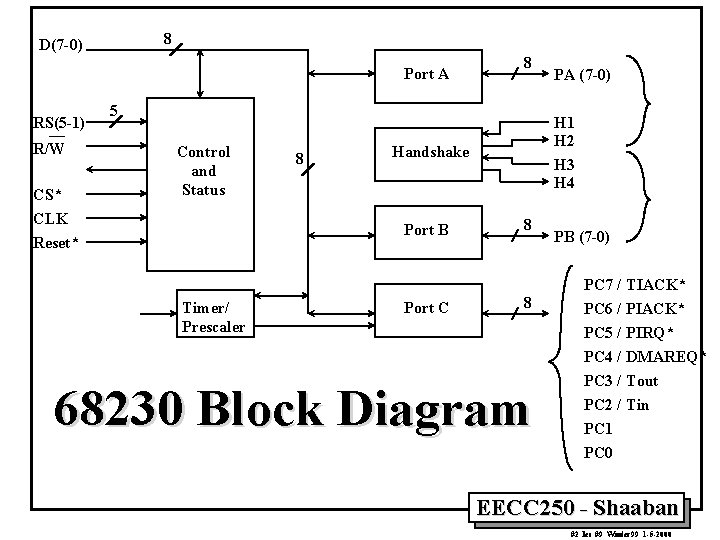

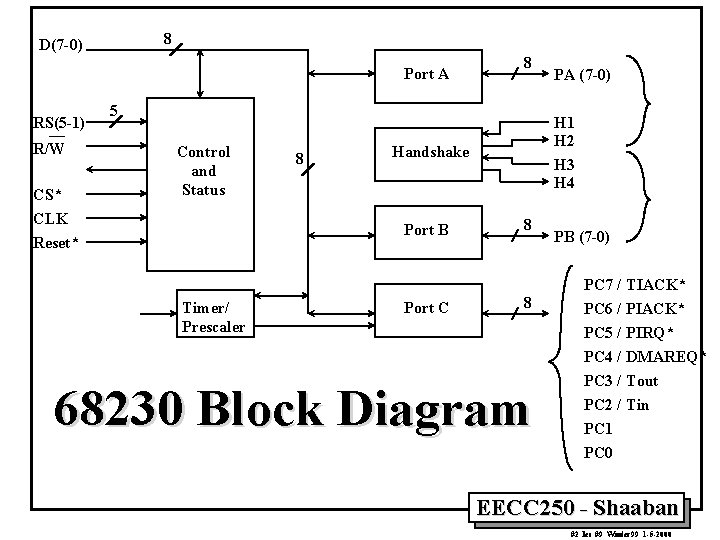

8 D(7 -0) Port A RS(5 -1) __ R/W CS* CLK Reset* 8 5 Control and Status 8 Timer/ Prescaler H 1 H 2 H 3 H 4 Handshake Port B Port C PA (7 -0) 8 8 68230 Block Diagram PB (7 -0) PC 7 / TIACK* PC 6 / PIACK* PC 5 / PIRQ* PC 4 / DMAREQ* PC 3 / Tout PC 2 / Tin PC 1 PC 0 EECC 250 - Shaaban #2 lec #9 Winter 99 1 -5 -2000

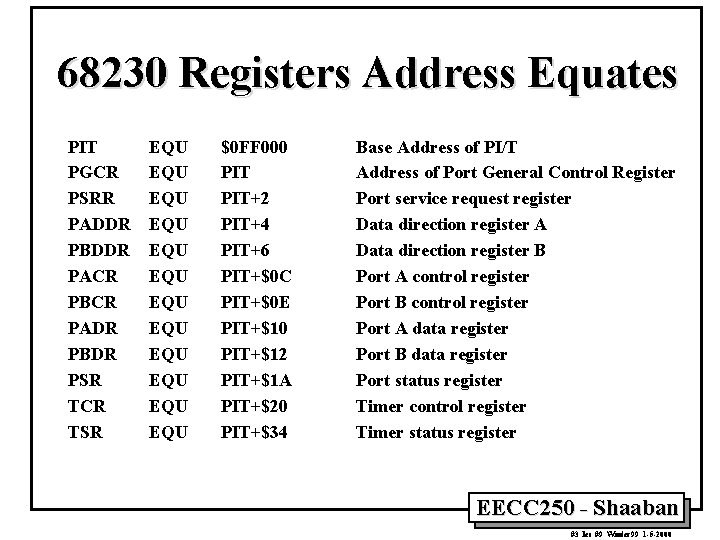

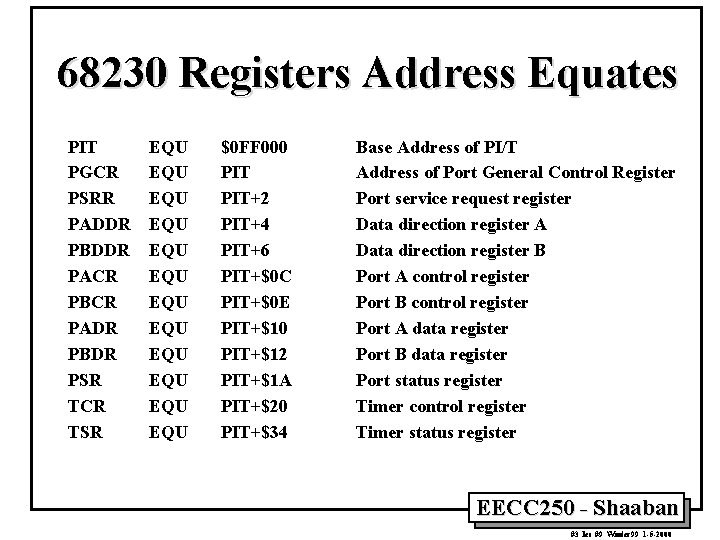

68230 Registers Address Equates PIT PGCR PSRR PADDR PBDDR PACR PBCR PADR PBDR PSR TCR TSR EQU EQU EQU $0 FF 000 PIT+2 PIT+4 PIT+6 PIT+$0 C PIT+$0 E PIT+$10 PIT+$12 PIT+$1 A PIT+$20 PIT+$34 Base Address of PI/T Address of Port General Control Register Port service request register Data direction register A Data direction register B Port A control register Port B control register Port A data register Port B data register Port status register Timer control register Timer status register EECC 250 - Shaaban #3 lec #9 Winter 99 1 -5 -2000

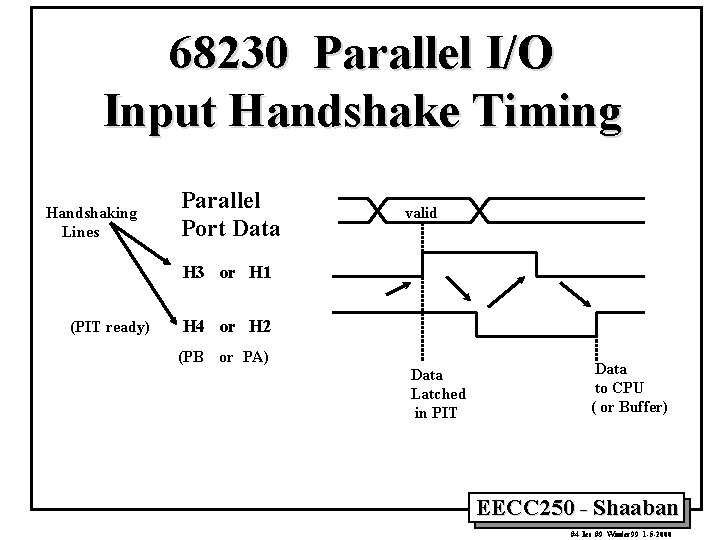

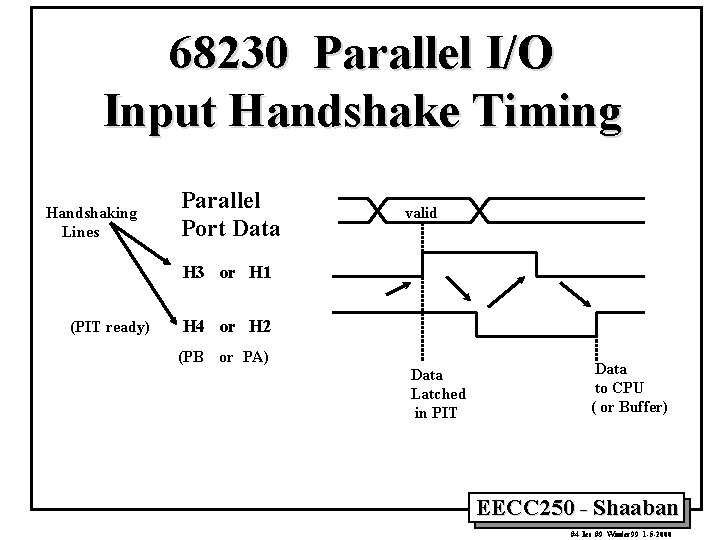

68230 Parallel I/O Input Handshake Timing Handshaking Lines Parallel Port Data valid H 3 or H 1 (PIT ready) H 4 or H 2 (PB or PA) Data Latched in PIT Data to CPU ( or Buffer) EECC 250 - Shaaban #4 lec #9 Winter 99 1 -5 -2000

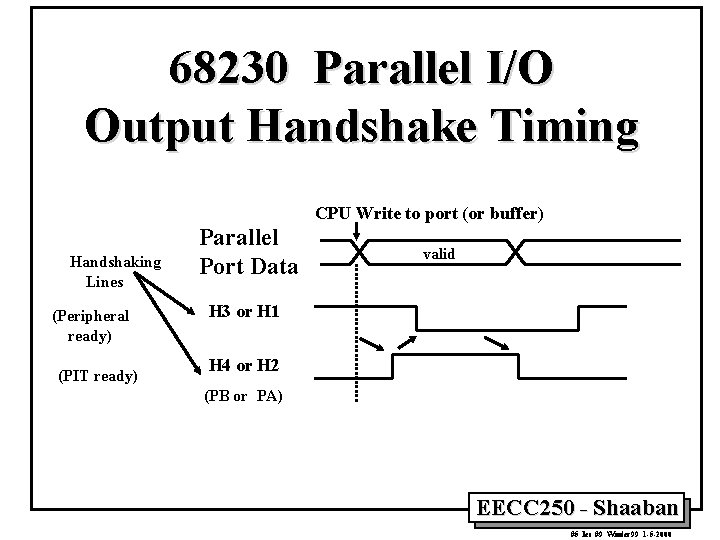

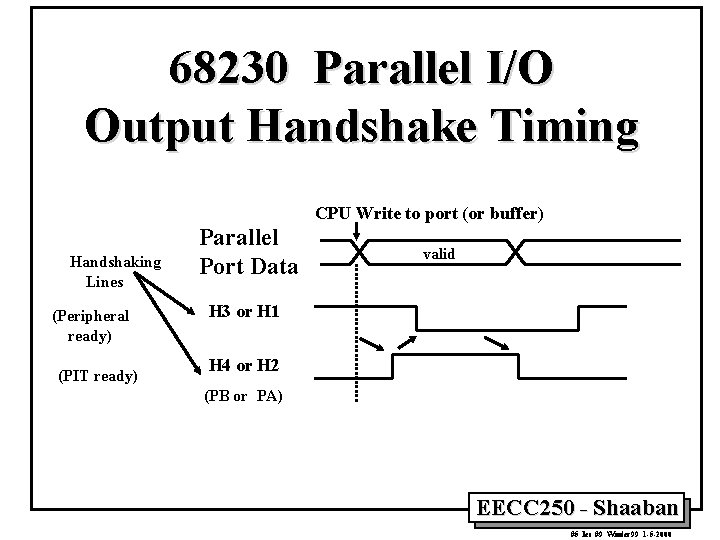

68230 Parallel I/O Output Handshake Timing CPU Write to port (or buffer) Handshaking Lines (Peripheral ready) (PIT ready) Parallel Port Data valid H 3 or H 1 H 4 or H 2 (PB or PA) EECC 250 - Shaaban #5 lec #9 Winter 99 1 -5 -2000

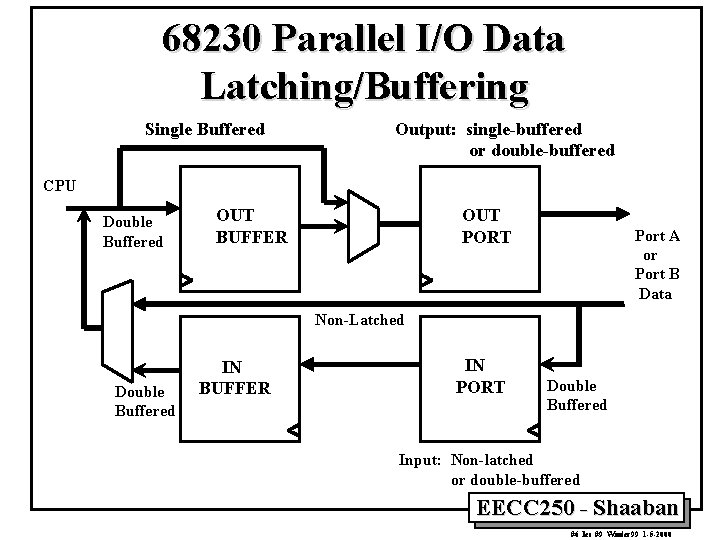

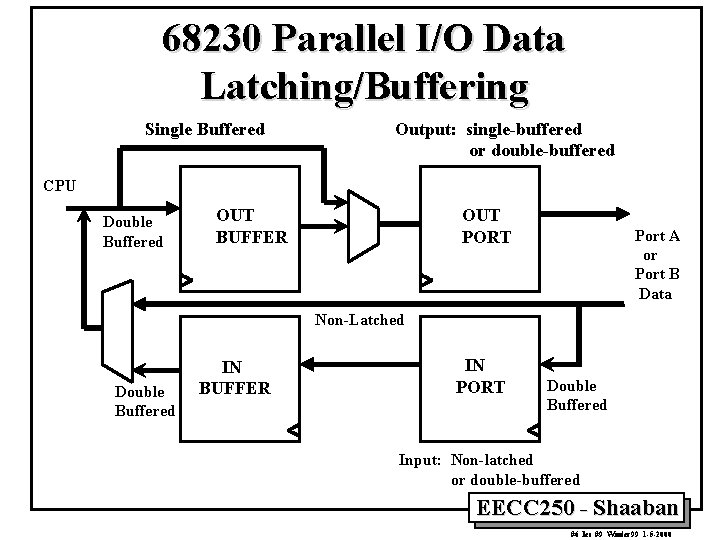

68230 Parallel I/O Data Latching/Buffering Single Buffered Output: single-buffered or double-buffered CPU Double Buffered OUT BUFFER OUT PORT Port A or Port B Data Non-Latched Double Buffered IN BUFFER IN PORT Double Buffered Input: Non-latched or double-buffered EECC 250 - Shaaban #6 lec #9 Winter 99 1 -5 -2000

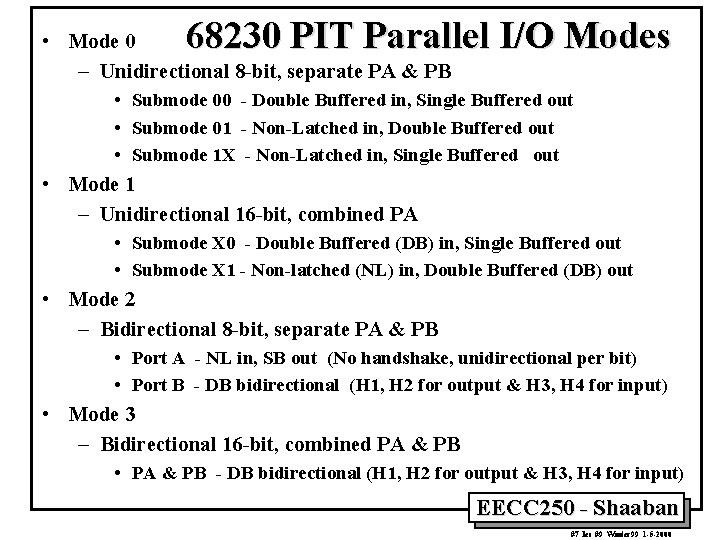

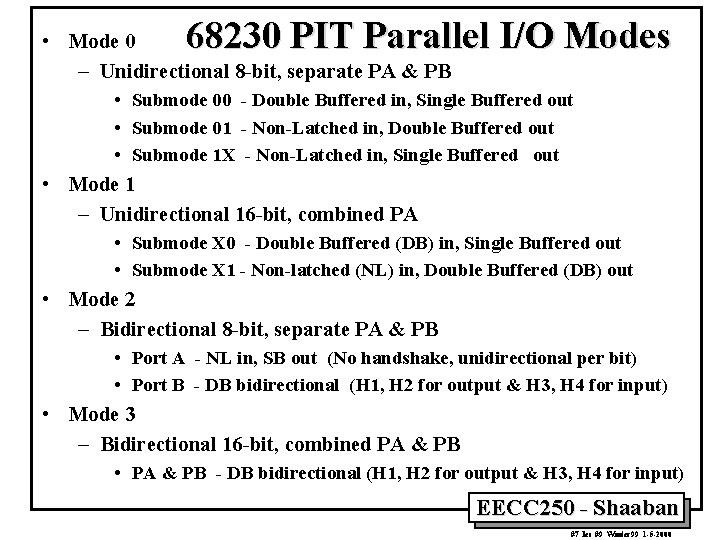

68230 PIT Parallel I/O Modes • Mode 0 – Unidirectional 8 -bit, separate PA & PB • Submode 00 - Double Buffered in, Single Buffered out • Submode 01 - Non-Latched in, Double Buffered out • Submode 1 X - Non-Latched in, Single Buffered out • Mode 1 – Unidirectional 16 -bit, combined PA • Submode X 0 - Double Buffered (DB) in, Single Buffered out • Submode X 1 - Non-latched (NL) in, Double Buffered (DB) out • Mode 2 – Bidirectional 8 -bit, separate PA & PB • Port A - NL in, SB out (No handshake, unidirectional per bit) • Port B - DB bidirectional (H 1, H 2 for output & H 3, H 4 for input) • Mode 3 – Bidirectional 16 -bit, combined PA & PB • PA & PB - DB bidirectional (H 1, H 2 for output & H 3, H 4 for input) EECC 250 - Shaaban #7 lec #9 Winter 99 1 -5 -2000

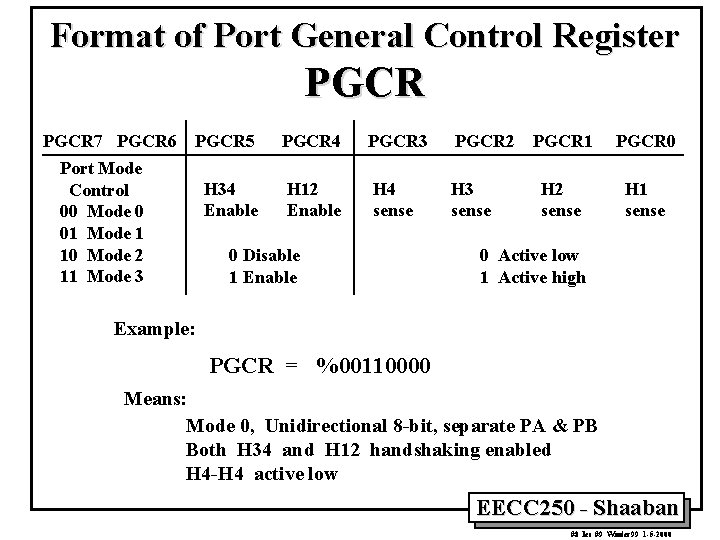

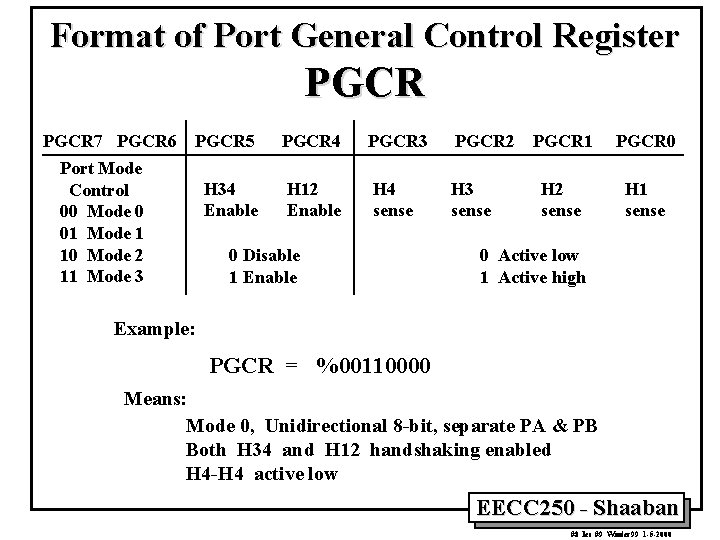

Format of Port General Control Register PGCR 7 PGCR 6 Port Mode Control 00 Mode 0 01 Mode 1 10 Mode 2 11 Mode 3 PGCR 5 PGCR 4 PGCR 3 PGCR 2 H 34 Enable H 12 Enable H 4 sense H 3 sense 0 Disable 1 Enable PGCR 1 PGCR 0 H 2 sense H 1 sense 0 Active low 1 Active high Example: PGCR = %00110000 Means: Mode 0, Unidirectional 8 -bit, separate PA & PB Both H 34 and H 12 handshaking enabled H 4 -H 4 active low EECC 250 - Shaaban #8 lec #9 Winter 99 1 -5 -2000

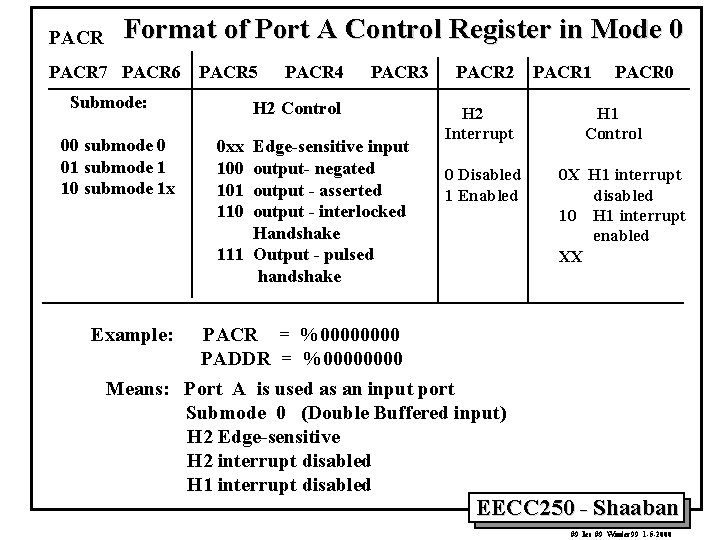

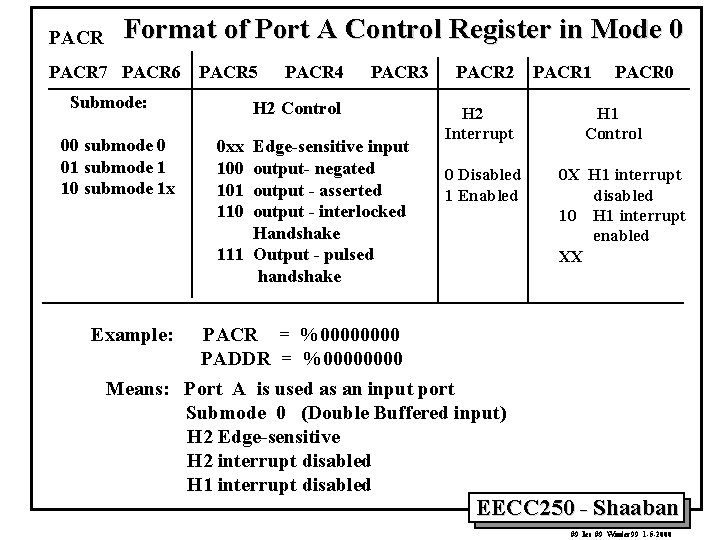

PACR Format of Port A Control Register in Mode 0 PACR 7 PACR 6 PACR 5 Submode: 00 submode 0 01 submode 1 10 submode 1 x PACR 4 PACR 3 H 2 Control 0 xx 100 101 110 Edge-sensitive input output- negated output - asserted output - interlocked Handshake 111 Output - pulsed handshake PACR 2 H 2 Interrupt 0 Disabled 1 Enabled PACR 1 PACR 0 H 1 Control 0 X H 1 interrupt disabled 10 H 1 interrupt enabled XX Example: PACR = %0000 PADDR = %0000 Means: Port A is used as an input port Submode 0 (Double Buffered input) H 2 Edge-sensitive H 2 interrupt disabled H 1 interrupt disabled EECC 250 - Shaaban #9 lec #9 Winter 99 1 -5 -2000

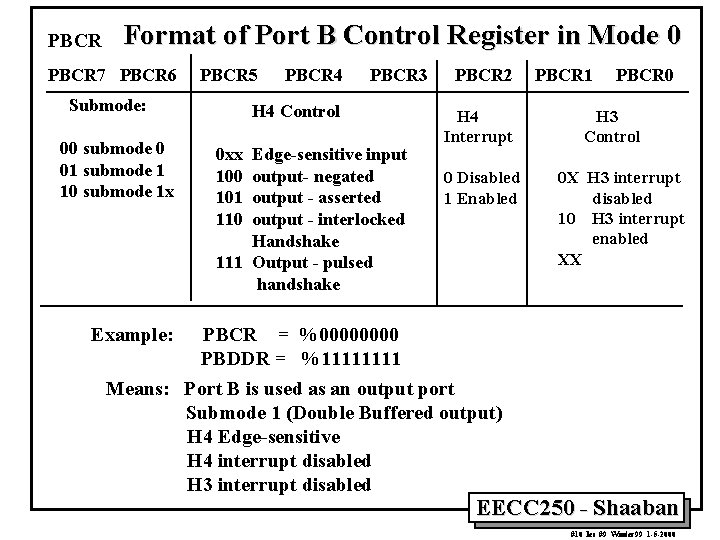

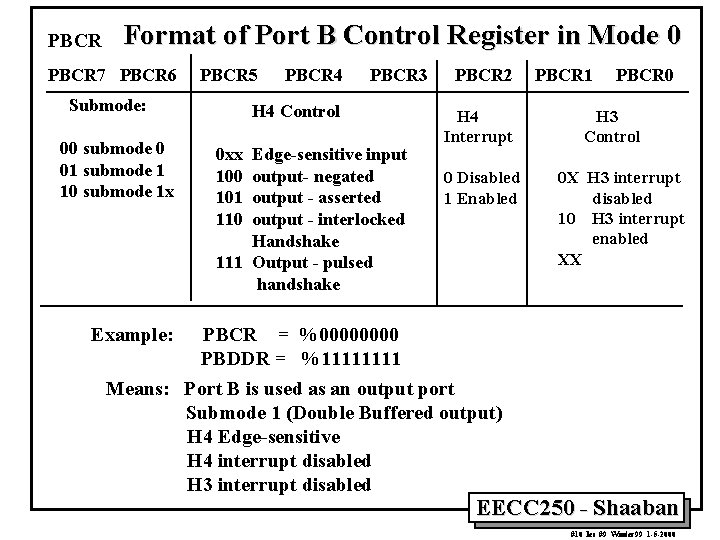

PBCR Format of Port B Control Register in Mode 0 PBCR 7 PBCR 6 PBCR 5 Submode: 00 submode 0 01 submode 1 10 submode 1 x PBCR 4 PBCR 3 H 4 Control 0 xx 100 101 110 Edge-sensitive input output- negated output - asserted output - interlocked Handshake 111 Output - pulsed handshake PBCR 2 H 4 Interrupt 0 Disabled 1 Enabled PBCR 1 PBCR 0 H 3 Control 0 X H 3 interrupt disabled 10 H 3 interrupt enabled XX Example: PBCR = %0000 PBDDR = %1111 Means: Port B is used as an output port Submode 1 (Double Buffered output) H 4 Edge-sensitive H 4 interrupt disabled H 3 interrupt disabled EECC 250 - Shaaban #10 lec #9 Winter 99 1 -5 -2000

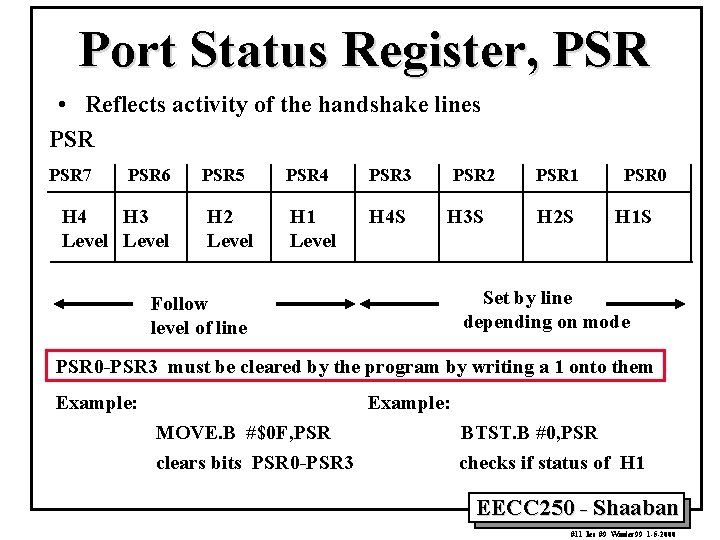

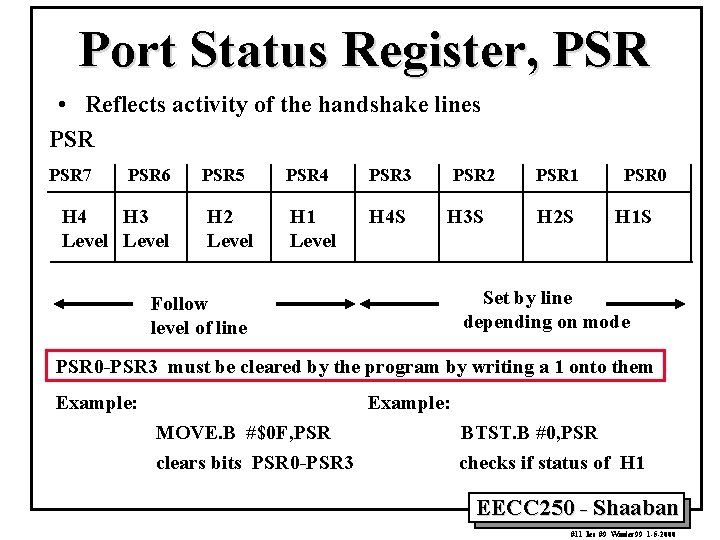

Port Status Register, PSR • Reflects activity of the handshake lines PSR 7 PSR 6 H 4 H 3 Level PSR 5 PSR 4 PSR 3 H 2 Level H 1 Level H 4 S PSR 2 H 3 S PSR 1 H 2 S PSR 0 H 1 S Set by line depending on mode Follow level of line PSR 0 -PSR 3 must be cleared by the program by writing a 1 onto them Example: MOVE. B #$0 F, PSR clears bits PSR 0 -PSR 3 BTST. B #0, PSR checks if status of H 1 EECC 250 - Shaaban #11 lec #9 Winter 99 1 -5 -2000

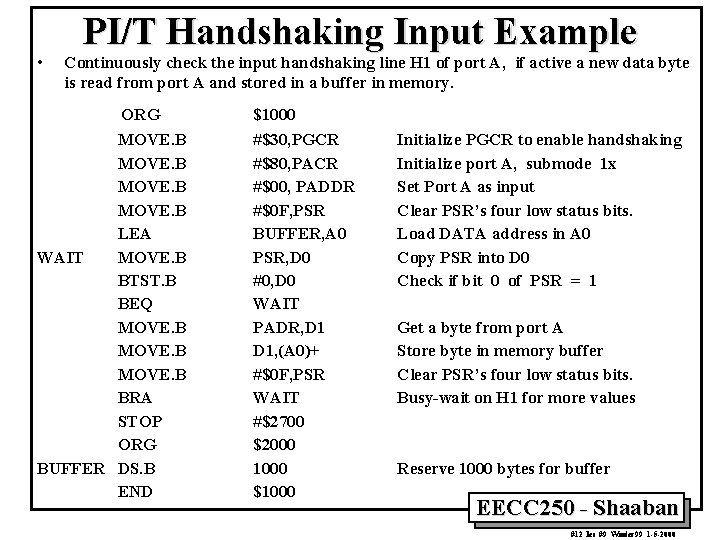

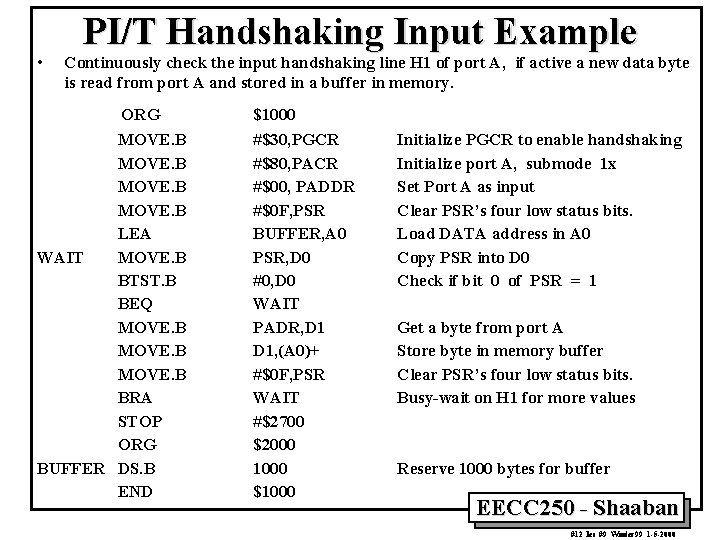

• PI/T Handshaking Input Example Continuously check the input handshaking line H 1 of port A, if active a new data byte is read from port A and stored in a buffer in memory. ORG MOVE. B LEA WAIT MOVE. B BTST. B BEQ MOVE. B BRA STOP ORG BUFFER DS. B END $1000 #$30, PGCR #$80, PACR #$00, PADDR #$0 F, PSR BUFFER, A 0 PSR, D 0 #0, D 0 WAIT PADR, D 1, (A 0)+ #$0 F, PSR WAIT #$2700 $2000 1000 $1000 Initialize PGCR to enable handshaking Initialize port A, submode 1 x Set Port A as input Clear PSR’s four low status bits. Load DATA address in A 0 Copy PSR into D 0 Check if bit 0 of PSR = 1 Get a byte from port A Store byte in memory buffer Clear PSR’s four low status bits. Busy-wait on H 1 for more values Reserve 1000 bytes for buffer EECC 250 - Shaaban #12 lec #9 Winter 99 1 -5 -2000