The MGPA ECAL readout chip for CMS MultiGain

![Linearity: Mid and Low gain channels low linearity [% fullscale] mid spec. relative signal Linearity: Mid and Low gain channels low linearity [% fullscale] mid spec. relative signal](https://slidetodoc.com/presentation_image/4f24a803a749d4665a3af2d1cf11418e/image-11.jpg)

![pulse shape matching [%] Pulse Shape Matching spec. pulse shape matching close to spec. pulse shape matching [%] Pulse Shape Matching spec. pulse shape matching close to spec.](https://slidetodoc.com/presentation_image/4f24a803a749d4665a3af2d1cf11418e/image-13.jpg)

- Slides: 21

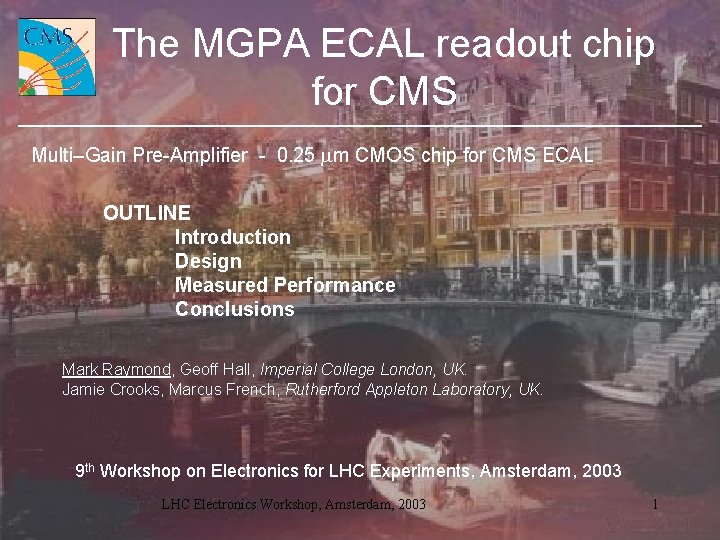

The MGPA ECAL readout chip for CMS Multi–Gain Pre-Amplifier - 0. 25 mm CMOS chip for CMS ECAL OUTLINE Introduction Design Measured Performance Conclusions Mark Raymond, Geoff Hall, Imperial College London, UK. Jamie Crooks, Marcus French, Rutherford Appleton Laboratory, UK. 9 th Workshop on Electronics for LHC Experiments, Amsterdam, 2003 LHC Electronics Workshop, Amsterdam, 2003 1

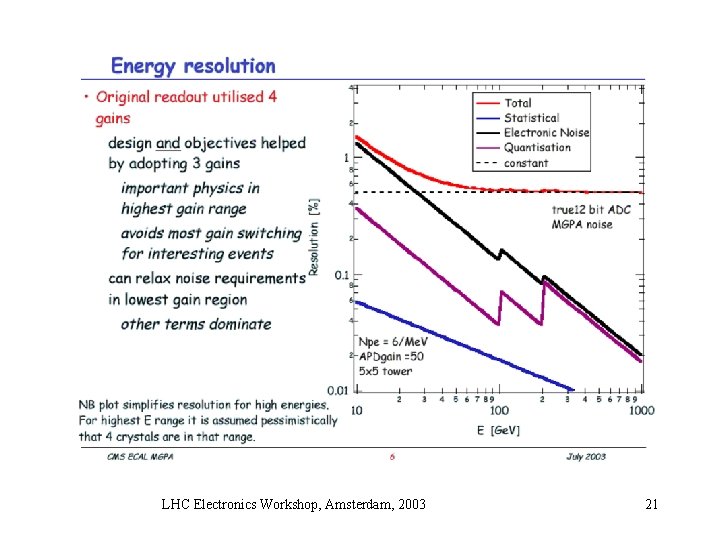

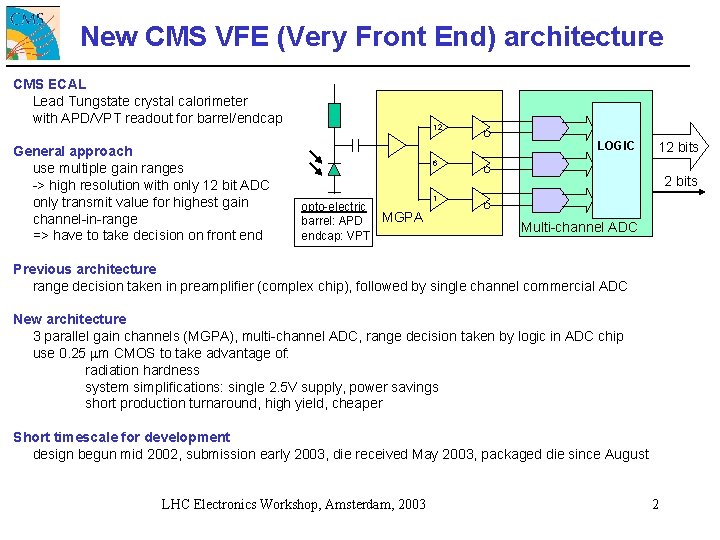

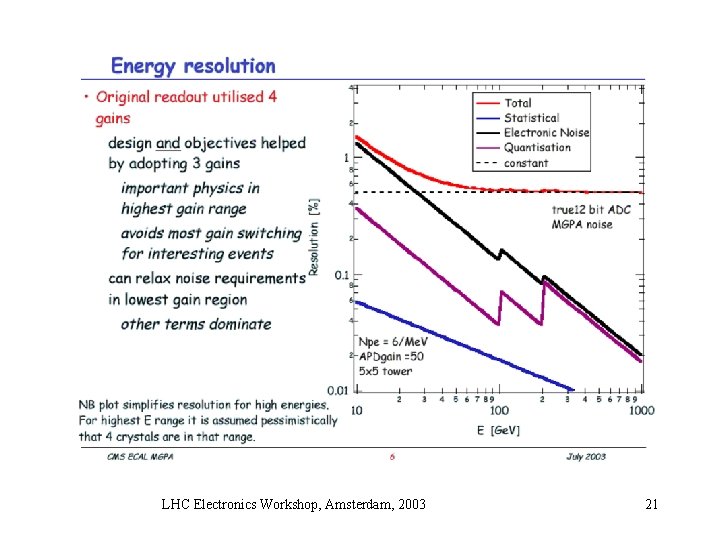

New CMS VFE (Very Front End) architecture CMS ECAL Lead Tungstate crystal calorimeter with APD/VPT readout for barrel/endcap General approach use multiple gain ranges -> high resolution with only 12 bit ADC only transmit value for highest gain channel-in-range => have to take decision on front end 12 LOGIC 12 bits 6 2 bits opto-electric MGPA barrel: APD endcap: VPT 1 Multi-channel ADC Previous architecture range decision taken in preamplifier (complex chip), followed by single channel commercial ADC New architecture 3 parallel gain channels (MGPA), multi-channel ADC, range decision taken by logic in ADC chip use 0. 25 mm CMOS to take advantage of: radiation hardness system simplifications: single 2. 5 V supply, power savings short production turnaround, high yield, cheaper Short timescale for development design begun mid 2002, submission early 2003, die received May 2003, packaged die since August LHC Electronics Workshop, Amsterdam, 2003 2

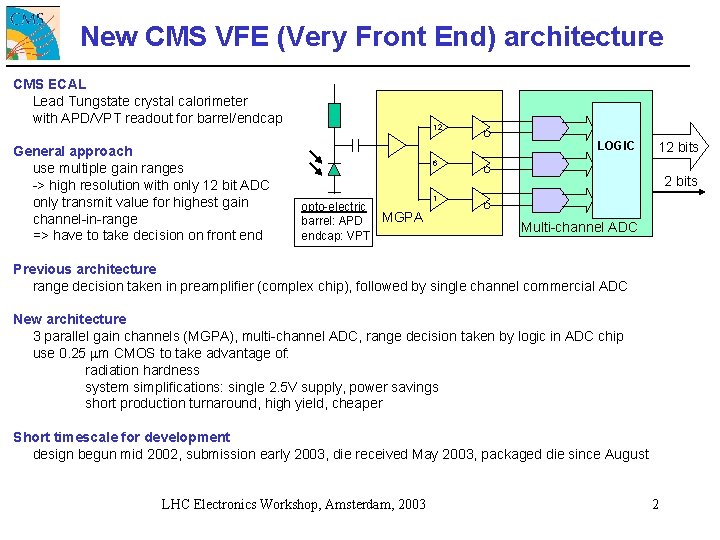

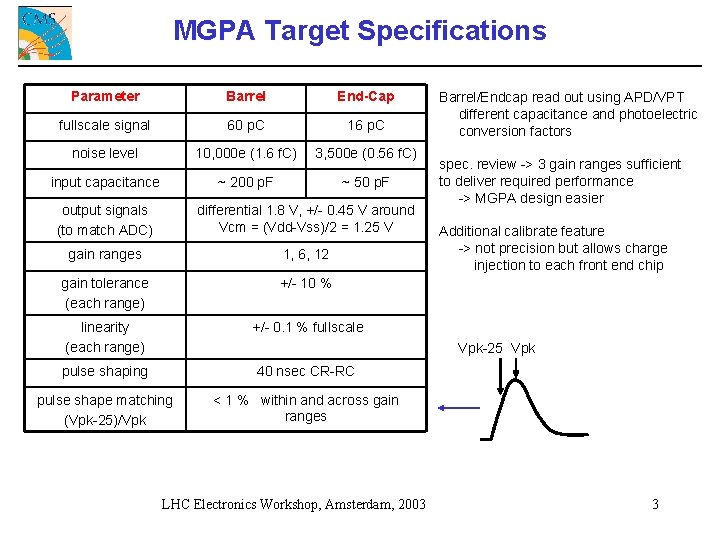

MGPA Target Specifications Parameter Barrel End-Cap fullscale signal 60 p. C 16 p. C noise level 10, 000 e (1. 6 f. C) 3, 500 e (0. 56 f. C) input capacitance ~ 200 p. F ~ 50 p. F output signals (to match ADC) differential 1. 8 V, +/- 0. 45 V around Vcm = (Vdd-Vss)/2 = 1. 25 V gain ranges 1, 6, 12 gain tolerance (each range) +/- 10 % linearity (each range) +/- 0. 1 % fullscale pulse shaping 40 nsec CR-RC pulse shape matching (Vpk-25)/Vpk < 1 % within and across gain ranges Barrel/Endcap read out using APD/VPT different capacitance and photoelectric conversion factors spec. review -> 3 gain ranges sufficient to deliver required performance -> MGPA design easier Additional calibrate feature -> not precision but allows charge injection to each front end chip Vpk-25 Vpk LHC Electronics Workshop, Amsterdam, 2003 3

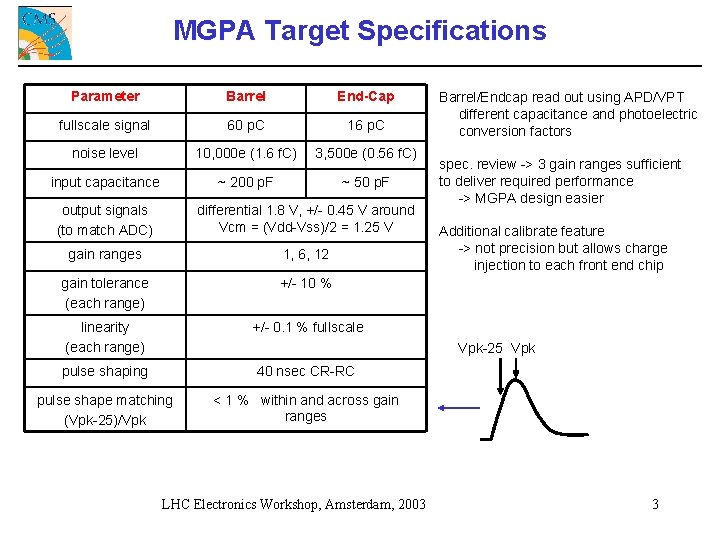

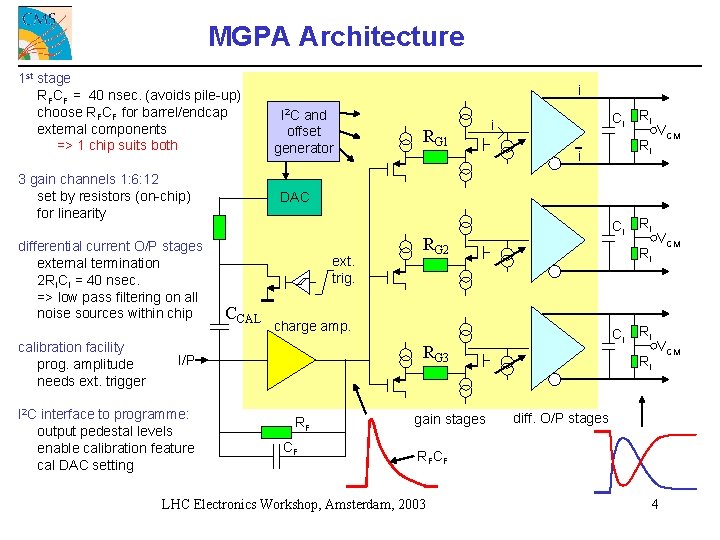

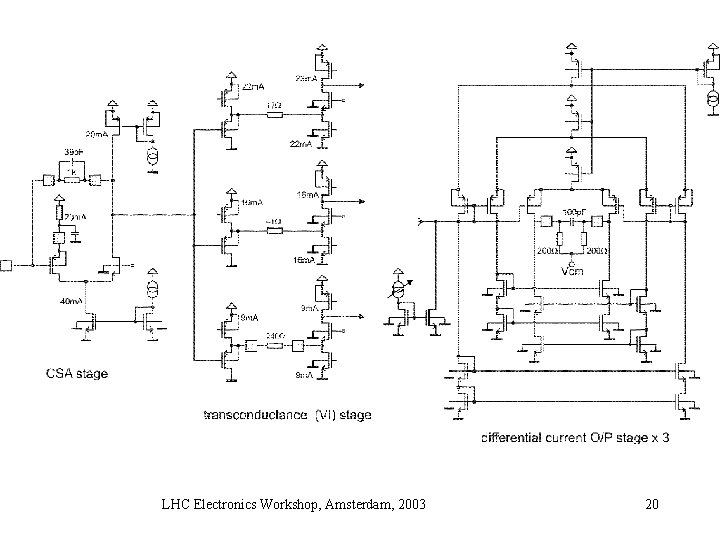

MGPA Architecture 1 st stage RFCF = 40 nsec. (avoids pile-up) choose RFCF for barrel/endcap external components => 1 chip suits both 3 gain channels 1: 6: 12 set by resistors (on-chip) for linearity differential current O/P stages external termination 2 RICI = 40 nsec. => low pass filtering on all noise sources within chip calibration facility prog. amplitude needs ext. trigger i I 2 C and offset generator i RI VCM DAC ext. trig. CCAL CI RI RG 2 RI charge amp. CI RI RG 3 I/P I 2 C interface to programme: output pedestal levels enable calibration feature cal DAC setting RG 1 CI RI i RF CF gain stages RI VCM diff. O/P stages RFCF LHC Electronics Workshop, Amsterdam, 2003 4

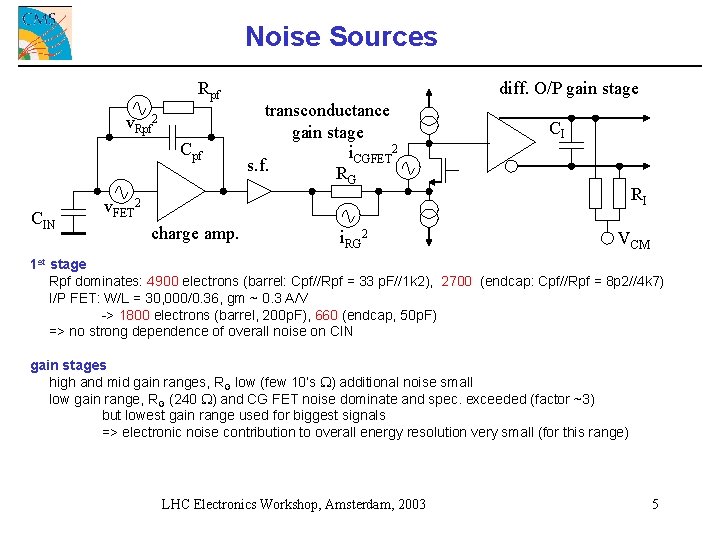

Noise Sources Rpf v. Rpf 2 Cpf CIN diff. O/P gain stage transconductance gain stage i. CGFET 2 s. f. RG CI RI v. FET 2 charge amp. i. RG 2 VCM 1 st stage Rpf dominates: 4900 electrons (barrel: Cpf//Rpf = 33 p. F//1 k 2), 2700 (endcap: Cpf//Rpf = 8 p 2//4 k 7) I/P FET: W/L = 30, 000/0. 36, gm ~ 0. 3 A/V -> 1800 electrons (barrel, 200 p. F), 660 (endcap, 50 p. F) => no strong dependence of overall noise on CIN gain stages high and mid gain ranges, RG low (few 10’s W) additional noise small low gain range, RG (240 W) and CG FET noise dominate and spec. exceeded (factor ~3) but lowest gain range used for biggest signals => electronic noise contribution to overall energy resolution very small (for this range) LHC Electronics Workshop, Amsterdam, 2003 5

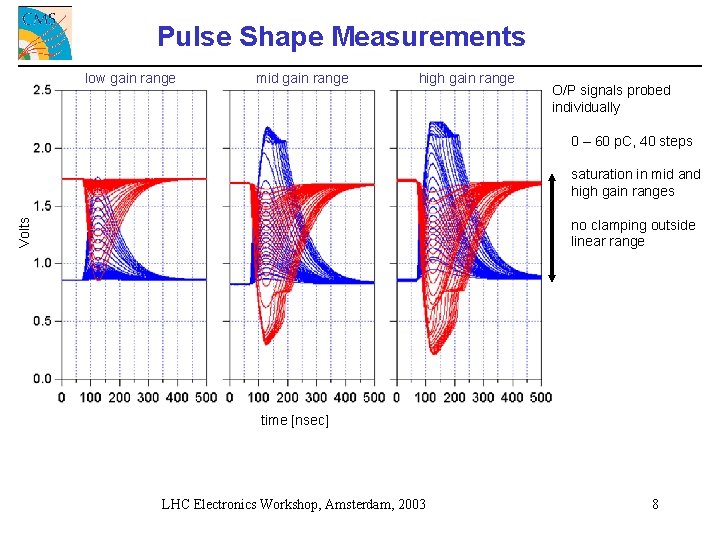

Chip Layout layout issues offset gen. I 2 C diff. O/P stage gain channels segregated as much as poss. with separate power pads -> try to avoid inter-channel coupling lots of multiple power pads high gain stage die size ~ 4 mm x 4 mm diff. O/P stage packaged in 100 pin TQFP (14 mm x 14 mm) mid gain stage 1 st stage low gain stage diff. O/P stage LHC Electronics Workshop, Amsterdam, 2003 6

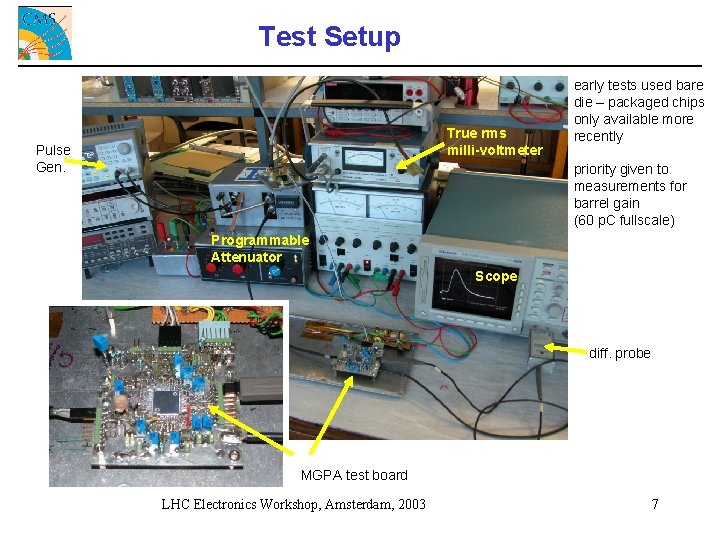

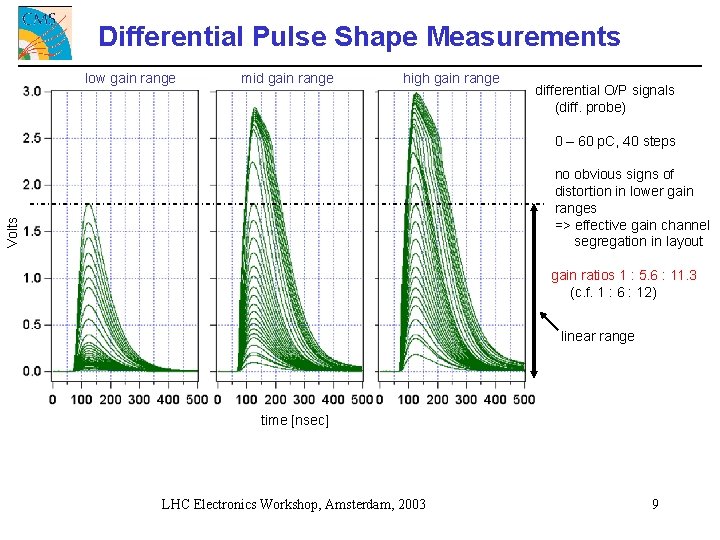

Test Setup True rms milli-voltmeter Pulse Gen. early tests used bare die – packaged chips only available more recently priority given to measurements for barrel gain (60 p. C fullscale) Programmable Attenuator Scope diff. probe MGPA test board LHC Electronics Workshop, Amsterdam, 2003 7

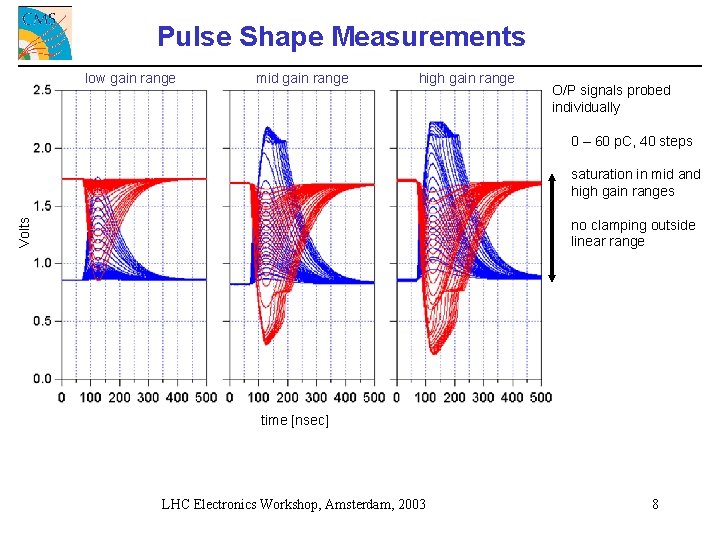

Pulse Shape Measurements low gain range mid gain range high gain range O/P signals probed individually 0 – 60 p. C, 40 steps saturation in mid and high gain ranges Volts no clamping outside linear range time [nsec] LHC Electronics Workshop, Amsterdam, 2003 8

Differential Pulse Shape Measurements low gain range mid gain range high gain range differential O/P signals (diff. probe) 0 – 60 p. C, 40 steps Volts no obvious signs of distortion in lower gain ranges => effective gain channel segregation in layout gain ratios 1 : 5. 6 : 11. 3 (c. f. 1 : 6 : 12) linear range time [nsec] LHC Electronics Workshop, Amsterdam, 2003 9

Linearity: High Gain Channel linearity within (or close to) spec for a range of gain stage bias currents linearity [% fullscale] => not v. sensitive to bias conditions spec. relative signal size 5. 4 p. C Linearity [% fullscale] = peak pulse ht. – fit (to pk pulse ht) X 100 fullscale signal LHC Electronics Workshop, Amsterdam, 2003 10

![Linearity Mid and Low gain channels low linearity fullscale mid spec relative signal Linearity: Mid and Low gain channels low linearity [% fullscale] mid spec. relative signal](https://slidetodoc.com/presentation_image/4f24a803a749d4665a3af2d1cf11418e/image-11.jpg)

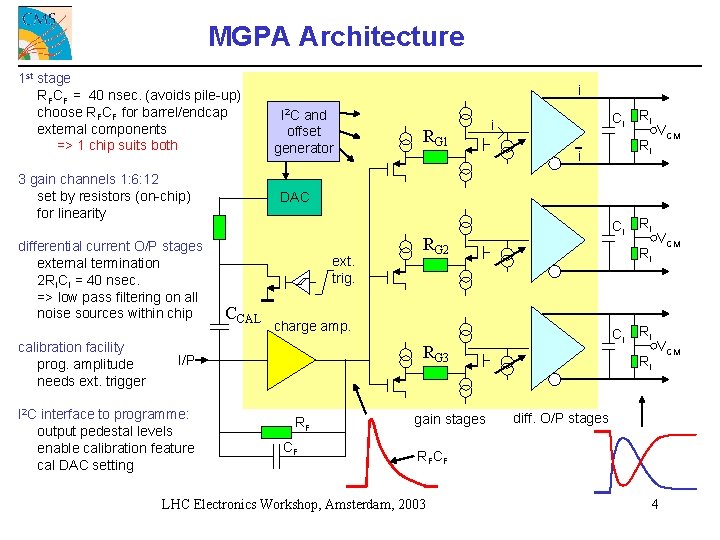

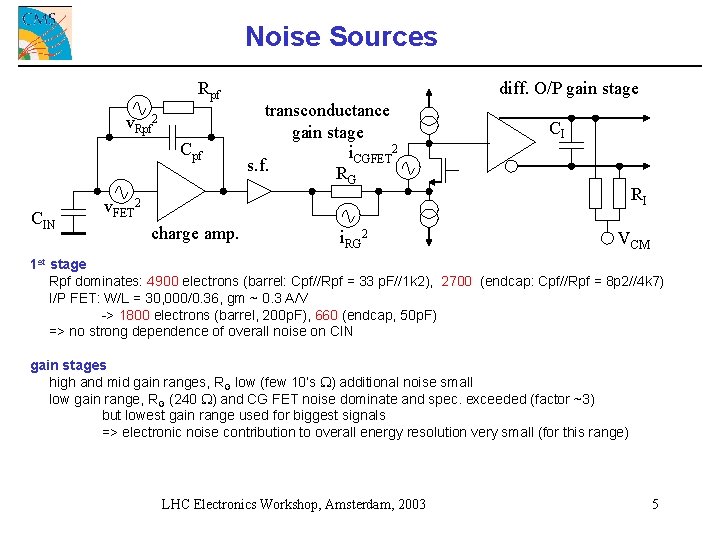

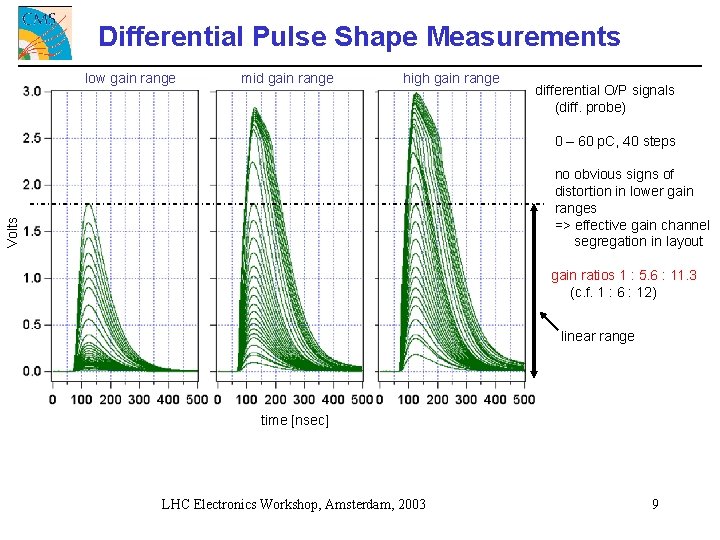

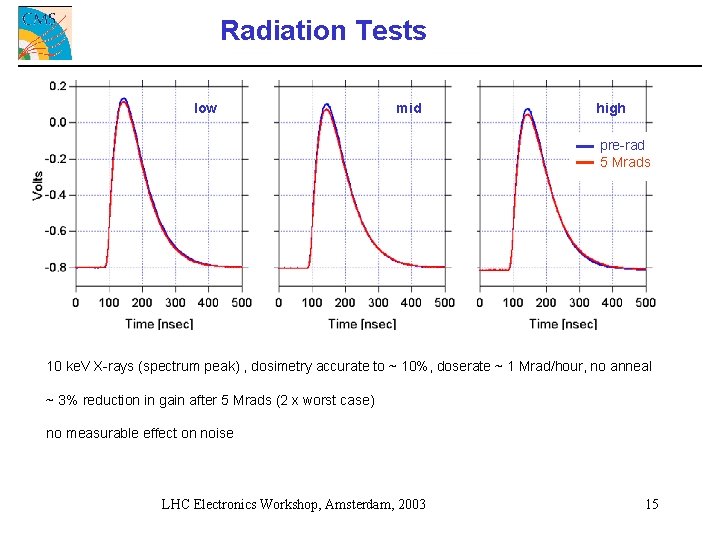

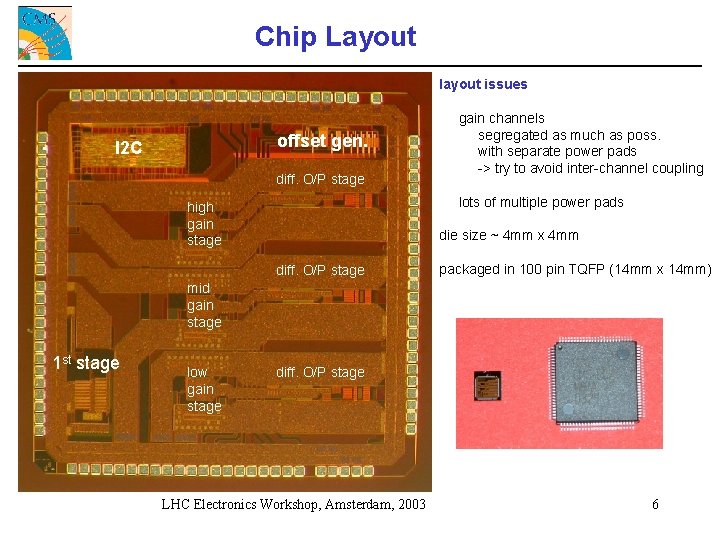

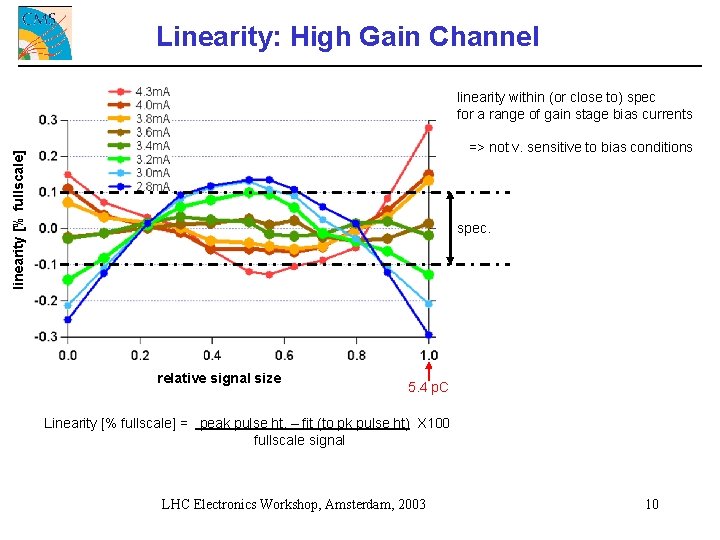

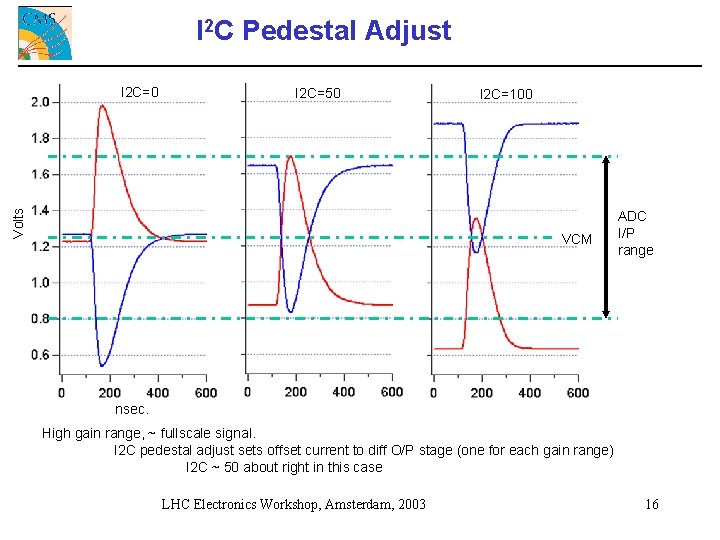

Linearity: Mid and Low gain channels low linearity [% fullscale] mid spec. relative signal size 11 p. C 60 p. C similar picture to high gain channel LHC Electronics Workshop, Amsterdam, 2003 11

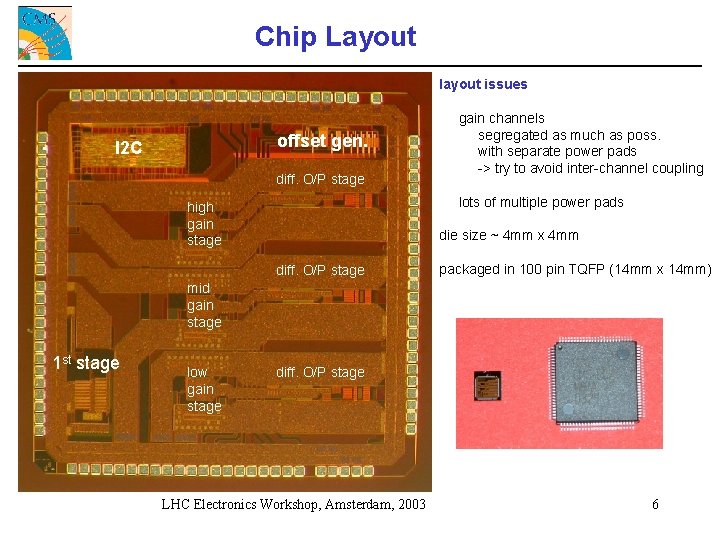

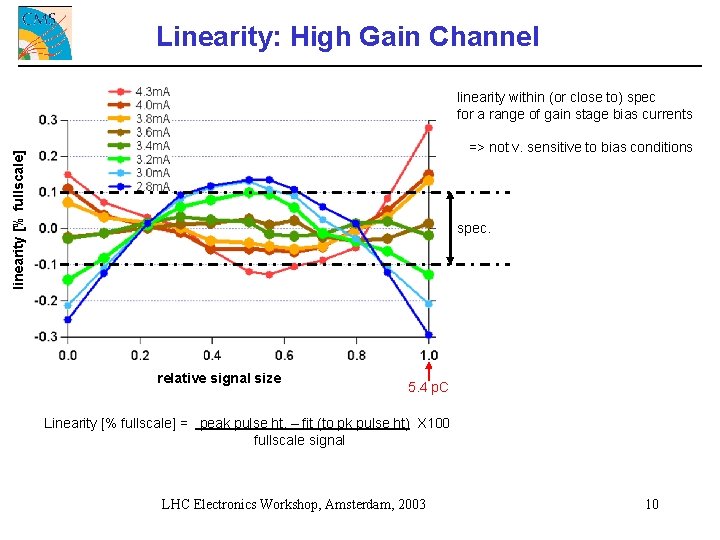

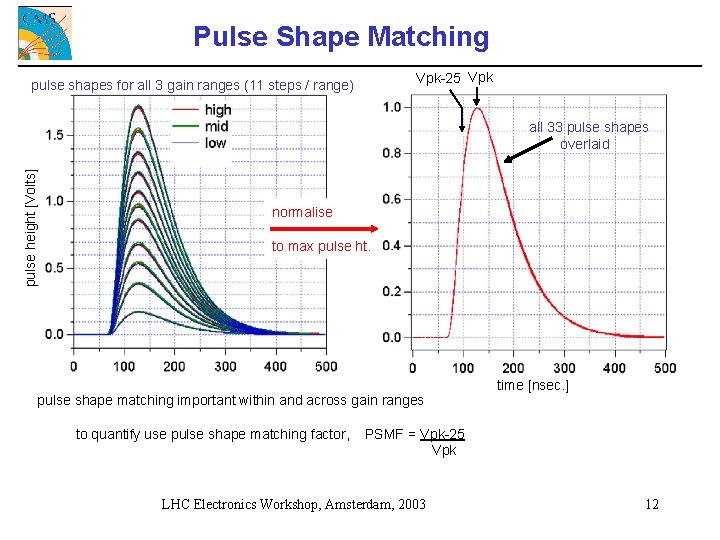

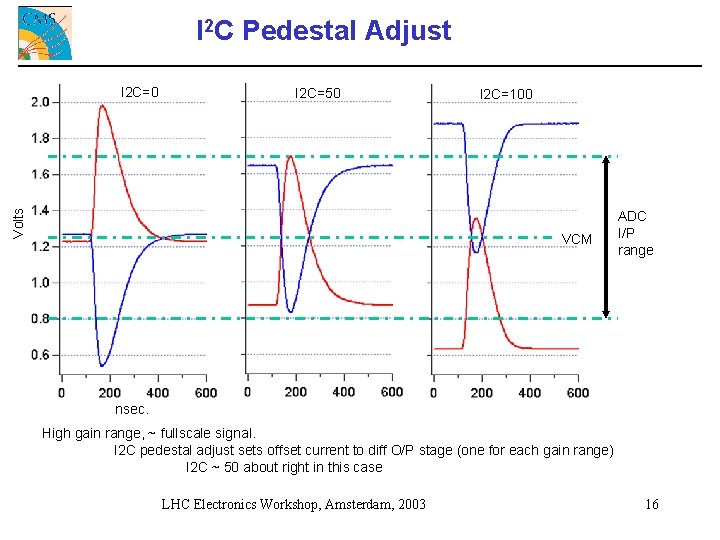

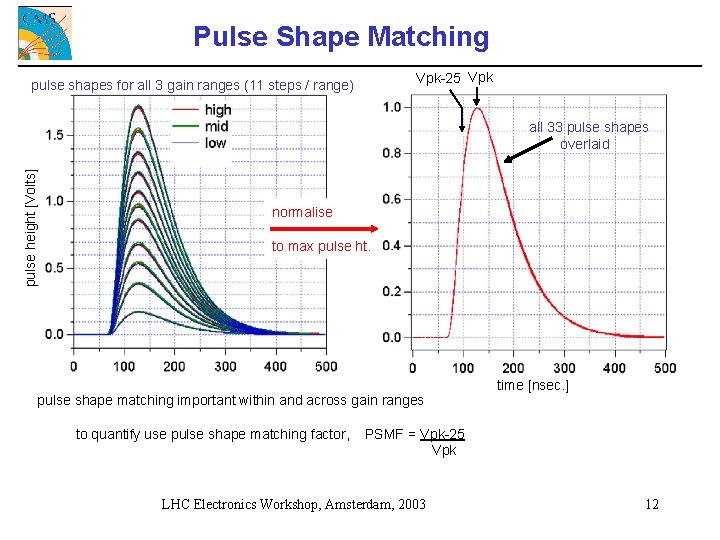

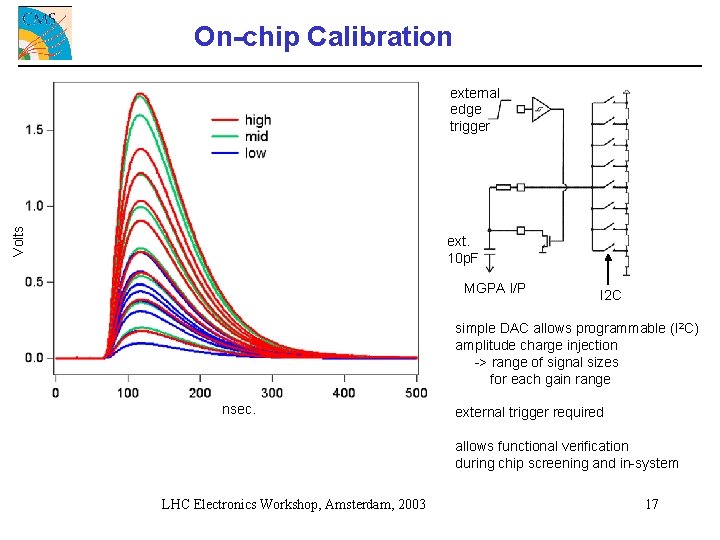

Pulse Shape Matching Vpk-25 Vpk pulse shapes for all 3 gain ranges (11 steps / range) pulse height [Volts] all 33 pulse shapes overlaid normalise to max pulse ht. pulse shape matching important within and across gain ranges to quantify use pulse shape matching factor, time [nsec. ] PSMF = Vpk-25 Vpk LHC Electronics Workshop, Amsterdam, 2003 12

![pulse shape matching Pulse Shape Matching spec pulse shape matching close to spec pulse shape matching [%] Pulse Shape Matching spec. pulse shape matching close to spec.](https://slidetodoc.com/presentation_image/4f24a803a749d4665a3af2d1cf11418e/image-13.jpg)

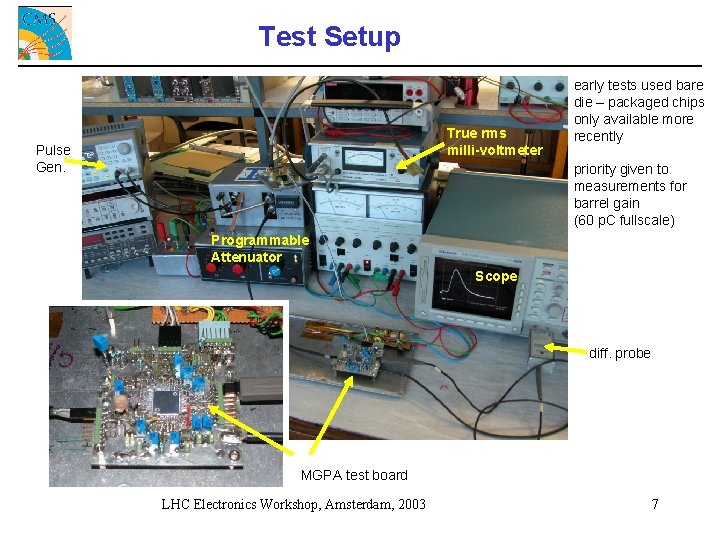

pulse shape matching [%] Pulse Shape Matching spec. pulse shape matching close to spec. (+/- 1%) relative signal size [1=fullscale] Pulse shape matching [%] = (PSMF – Average PSMF) x 100 Average PSMF (Average PSMF = average over all pulse shapes and all 3 gain ranges) LHC Electronics Workshop, Amsterdam, 2003 13

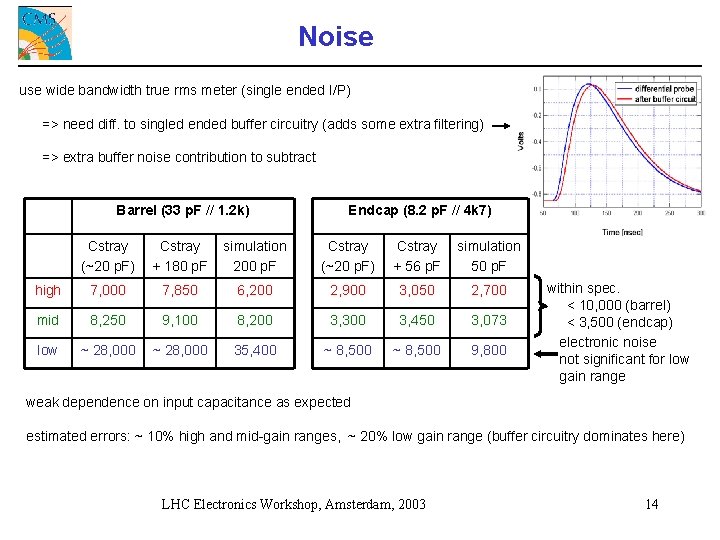

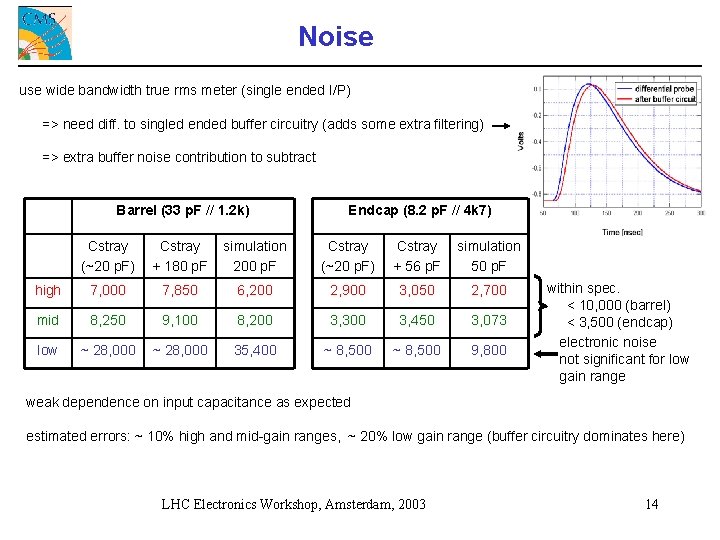

Noise use wide bandwidth true rms meter (single ended I/P) => need diff. to singled ended buffer circuitry (adds some extra filtering) => extra buffer noise contribution to subtract Barrel (33 p. F // 1. 2 k) Endcap (8. 2 p. F // 4 k 7) Cstray (~20 p. F) Cstray + 180 p. F simulation 200 p. F Cstray (~20 p. F) Cstray + 56 p. F simulation 50 p. F high 7, 000 7, 850 6, 200 2, 900 3, 050 2, 700 mid 8, 250 9, 100 8, 200 3, 300 3, 450 3, 073 low ~ 28, 000 35, 400 ~ 8, 500 9, 800 within spec. < 10, 000 (barrel) < 3, 500 (endcap) electronic noise not significant for low gain range weak dependence on input capacitance as expected estimated errors: ~ 10% high and mid-gain ranges, ~ 20% low gain range (buffer circuitry dominates here) LHC Electronics Workshop, Amsterdam, 2003 14

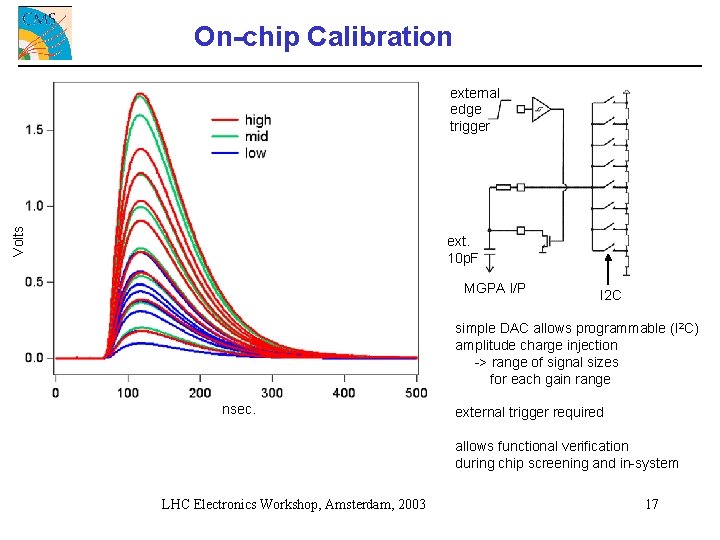

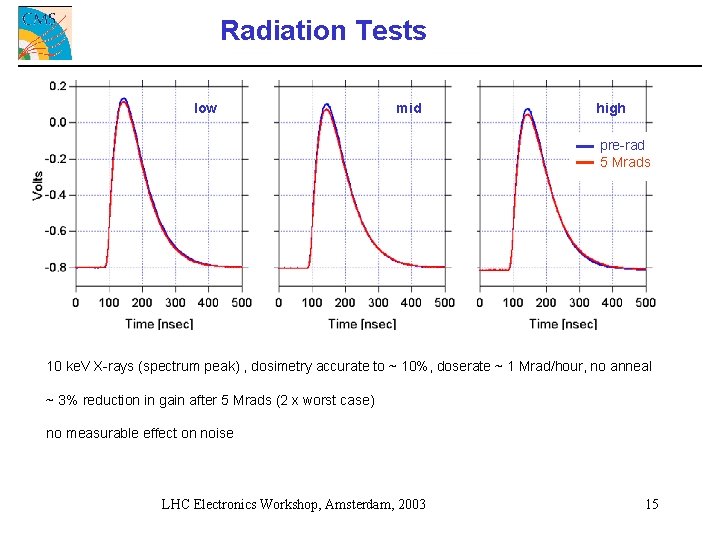

Radiation Tests low mid high pre-rad 5 Mrads 10 ke. V X-rays (spectrum peak) , dosimetry accurate to ~ 10%, doserate ~ 1 Mrad/hour, no anneal ~ 3% reduction in gain after 5 Mrads (2 x worst case) no measurable effect on noise LHC Electronics Workshop, Amsterdam, 2003 15

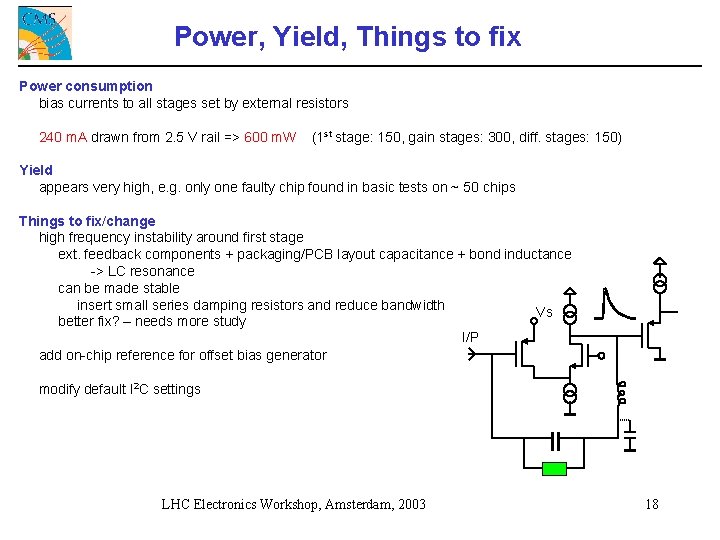

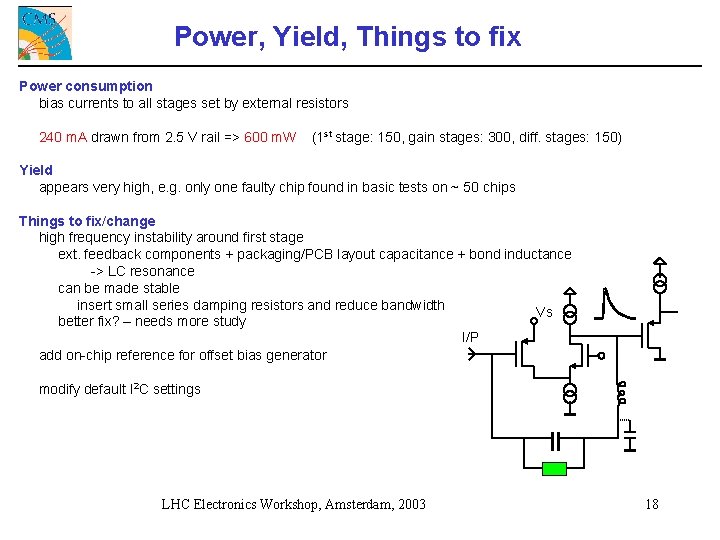

I 2 C Pedestal Adjust I 2 C=50 Volts I 2 C=0 I 2 C=100 VCM ADC I/P range nsec. High gain range, ~ fullscale signal. I 2 C pedestal adjust sets offset current to diff O/P stage (one for each gain range) I 2 C ~ 50 about right in this case LHC Electronics Workshop, Amsterdam, 2003 16

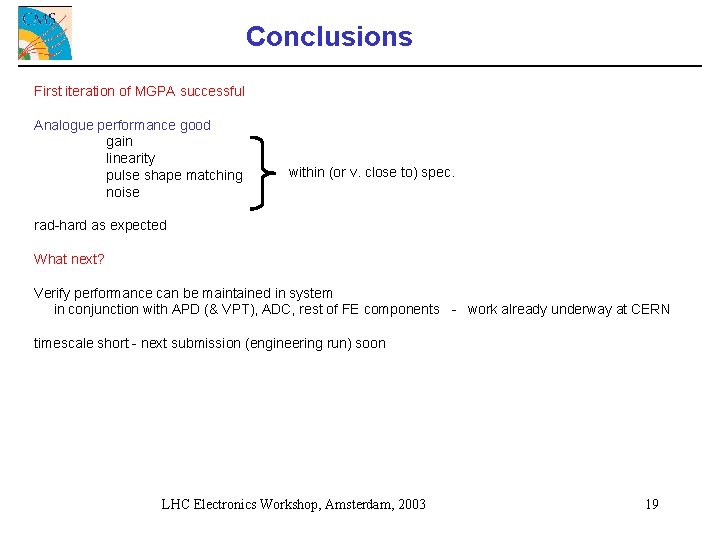

On-chip Calibration Volts external edge trigger ext. 10 p. F MGPA I/P I 2 C simple DAC allows programmable (I 2 C) amplitude charge injection -> range of signal sizes for each gain range nsec. external trigger required allows functional verification during chip screening and in-system LHC Electronics Workshop, Amsterdam, 2003 17

Power, Yield, Things to fix Power consumption bias currents to all stages set by external resistors 240 m. A drawn from 2. 5 V rail => 600 m. W (1 st stage: 150, gain stages: 300, diff. stages: 150) Yield appears very high, e. g. only one faulty chip found in basic tests on ~ 50 chips Things to fix/change high frequency instability around first stage ext. feedback components + packaging/PCB layout capacitance + bond inductance -> LC resonance can be made stable insert small series damping resistors and reduce bandwidth Vs better fix? – needs more study I/P add on-chip reference for offset bias generator modify default I 2 C settings LHC Electronics Workshop, Amsterdam, 2003 18

Conclusions First iteration of MGPA successful Analogue performance good gain linearity pulse shape matching noise within (or v. close to) spec. rad-hard as expected What next? Verify performance can be maintained in system in conjunction with APD (& VPT), ADC, rest of FE components - work already underway at CERN timescale short - next submission (engineering run) soon LHC Electronics Workshop, Amsterdam, 2003 19

LHC Electronics Workshop, Amsterdam, 2003 20

LHC Electronics Workshop, Amsterdam, 2003 21