The M 2 ASIC A mixed analoguedigital ASIC

- Slides: 22

The M 2 ASIC A mixed analogue/digital ASIC for acquisition and control in data handling systems Olle Martinsson AMICSA, October 2 -3, 2006 1 SAAB SPACE

M 2 summary A mixed analogue/digital ASIC, including 32 kgates and a 12 bit ADC, developed by Austrian Aerospace and Saab Space under an ESA contract Main application as generic core circuit for data handling I/O board Controlled via OBDH bus or UART interface Digital I/O functions include all common data handling system interfaces, such as: High level command pulse generation Serial command acquisition Etc. 3. 3 V supply Low power, typical consumption 12 m. W 2 SAAB SPACE

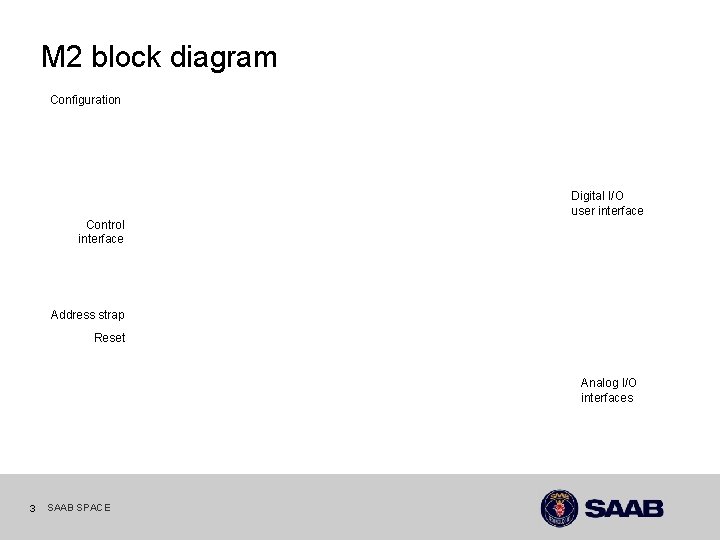

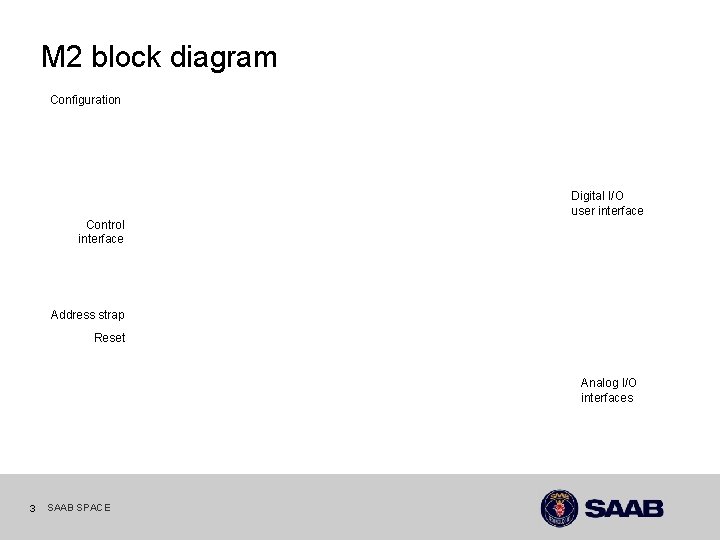

M 2 block diagram Configuration Digital I/O user interface Control interface Address strap Reset Analog I/O interfaces 3 SAAB SPACE

M 2 implementation 4 • Commercial, epi-layered CMOS technology, AMIS 0. 35µ with analog options (double poly capacitors, high resistive poly resistors) • Radiation tolerant by “Rad hard by design” • Digital cell library developed within the project • Digital part designed using VHDL, logic synthesis and place & route • Chip size 25 mm 2 • Prototypes via Europractice MPW in 160 pin CQFP package • Tested showing full functionality and full performance at first run • Implemented on a prototype I/O board for system level test, showing similar or better performance compared to existing designs SAAB SPACE

Rad hard by design The methodology to reach radiation hardness has basically been the same for analogue and digital parts. This includes: Selection of submicron CMOS assures small threshold voltage drifts NMOS edge leakage avoided by enclosed shaped transistors Leakage between NMOS devices avoided by guard rings Latchup avoided by guard rings and good substrate connections SEU hardness achieved by means of resistive feedback in flip-flops ─ Limits maximum possible clock rate, but + Makes the design hard also to transients in combinatorial logic Only low level measures, mainly on layout level, to achieve radiation hardness radiation aspects have only marginal impact on system, VHDL and schematic level design 5 SAAB SPACE

Cell library design based on “shadow” library M 2 cells selected as a subset of and compared with cells of a commercially available “shadow” library of a similar process Cell library, just like analog parts and top level design, developed using a low cost PC based tool from Tanner, including: Schematic editor Spice simulator Layout editor Design rule check Extraction Layout vs. schematic Place & route 6 SAAB SPACE

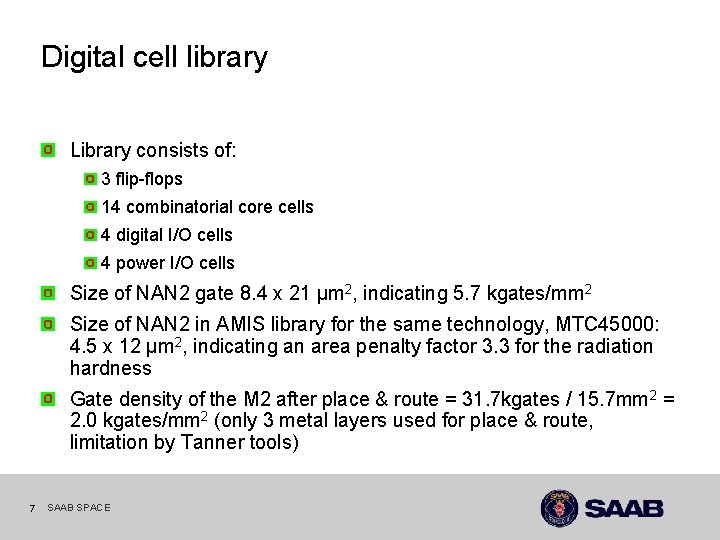

Digital cell library Library consists of: 3 flip-flops 14 combinatorial core cells 4 digital I/O cells 4 power I/O cells Size of NAN 2 gate 8. 4 x 21 μm 2, indicating 5. 7 kgates/mm 2 Size of NAN 2 in AMIS library for the same technology, MTC 45000: 4. 5 x 12 μm 2, indicating an area penalty factor 3. 3 for the radiation hardness Gate density of the M 2 after place & route = 31. 7 kgates / 15. 7 mm 2 = 2. 0 kgates/mm 2 (only 3 metal layers used for place & route, limitation by Tanner tools) 7 SAAB SPACE

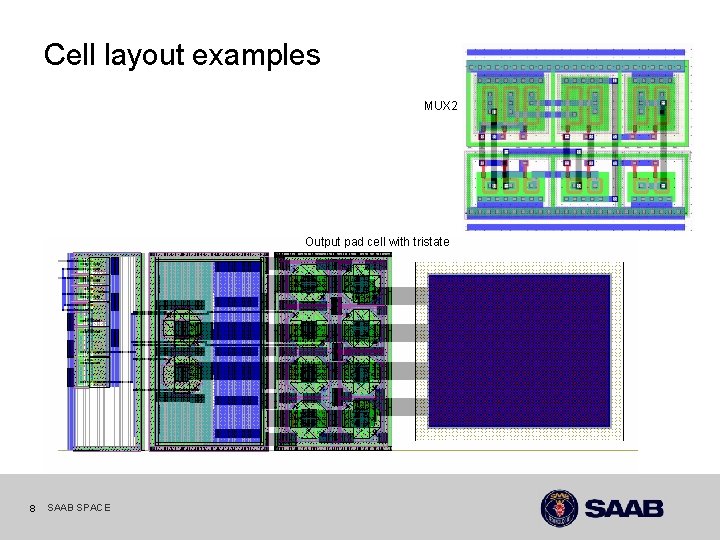

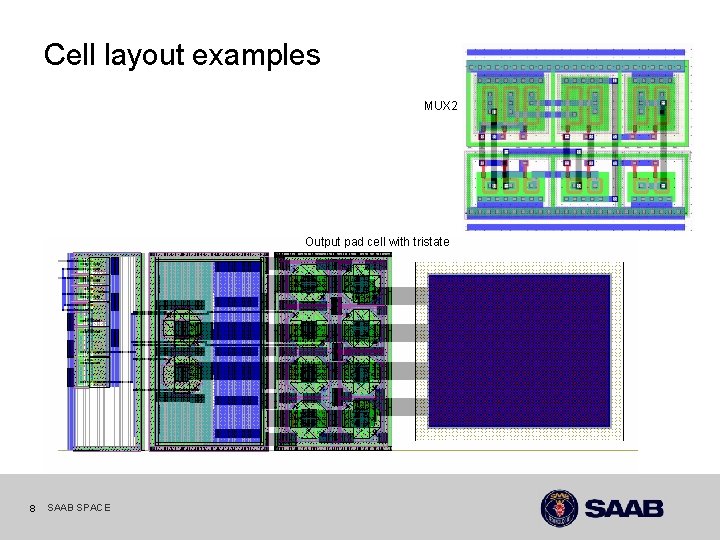

Cell layout examples MUX 2 Output pad cell with tristate 8 SAAB SPACE

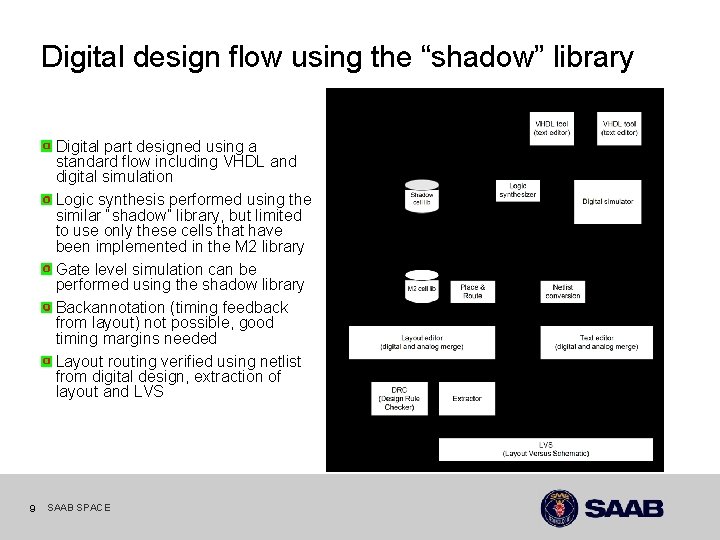

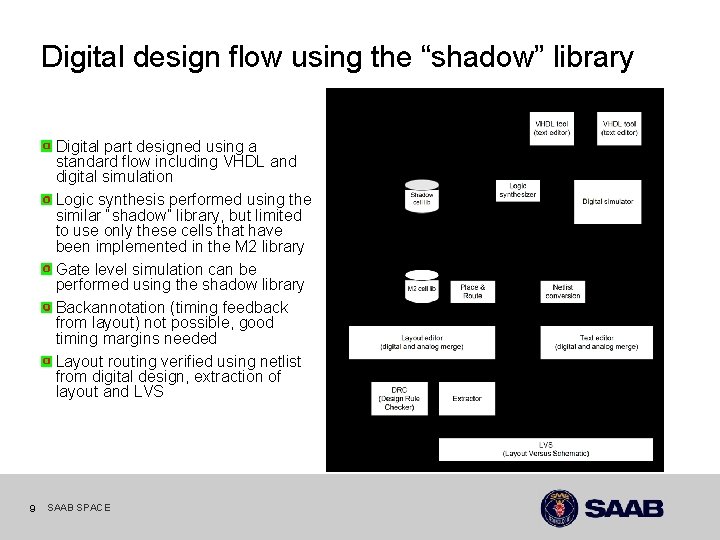

Digital design flow using the “shadow” library Digital part designed using a standard flow including VHDL and digital simulation Logic synthesis performed using the similar “shadow” library, but limited to use only these cells that have been implemented in the M 2 library Gate level simulation can be performed using the shadow library Backannotation (timing feedback from layout) not possible, good timing margins needed Layout routing verified using netlist from digital design, extraction of layout and LVS 9 SAAB SPACE

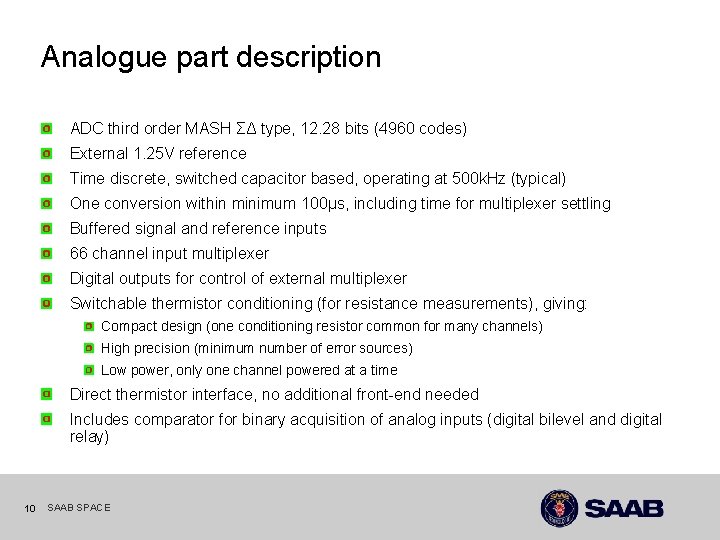

Analogue part description ADC third order MASH ΣΔ type, 12. 28 bits (4960 codes) External 1. 25 V reference Time discrete, switched capacitor based, operating at 500 k. Hz (typical) One conversion within minimum 100µs, including time for multiplexer settling Buffered signal and reference inputs 66 channel input multiplexer Digital outputs for control of external multiplexer Switchable thermistor conditioning (for resistance measurements), giving: Compact design (one conditioning resistor common for many channels) High precision (minimum number of error sources) Low power, only one channel powered at a time Direct thermistor interface, no additional front-end needed Includes comparator for binary acquisition of analog inputs (digital bilevel and digital relay) 10 SAAB SPACE

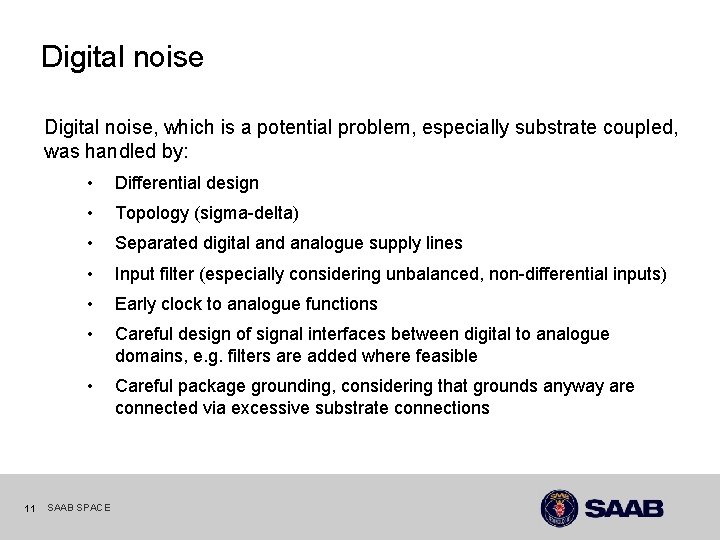

Digital noise, which is a potential problem, especially substrate coupled, was handled by: 11 • Differential design • Topology (sigma-delta) • Separated digital and analogue supply lines • Input filter (especially considering unbalanced, non-differential inputs) • Early clock to analogue functions • Careful design of signal interfaces between digital to analogue domains, e. g. filters are added where feasible • Careful package grounding, considering that grounds anyway are connected via excessive substrate connections SAAB SPACE

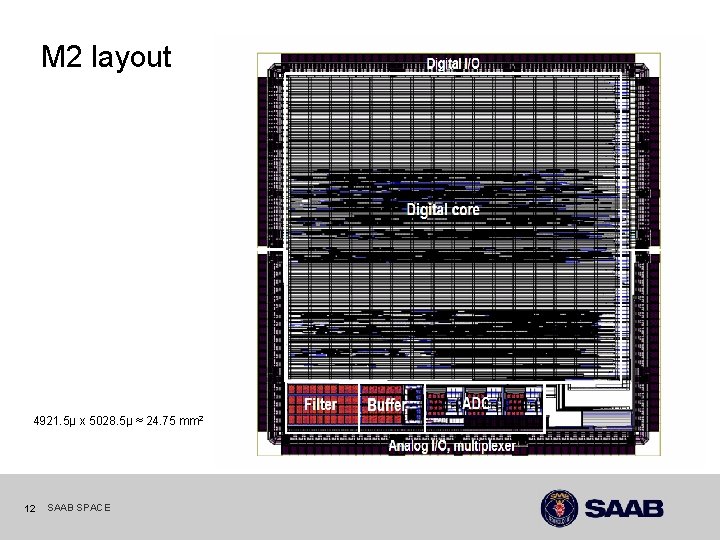

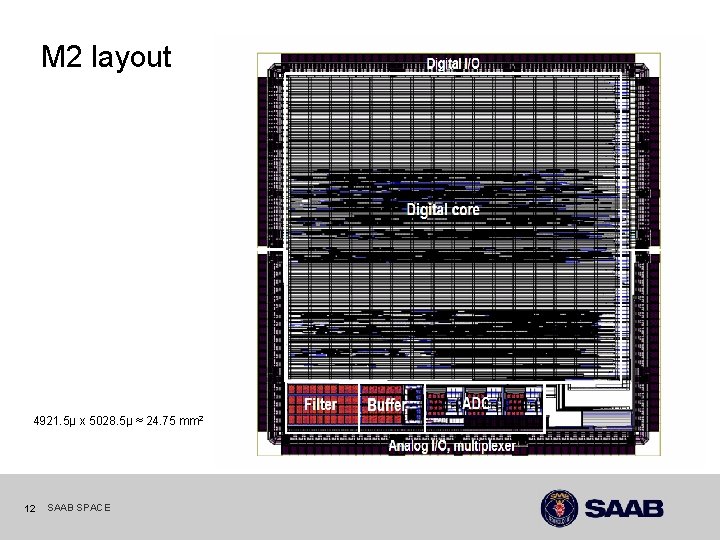

M 2 layout 4921. 5µ x 5028. 5µ ≈ 24. 75 mm 2 12 SAAB SPACE

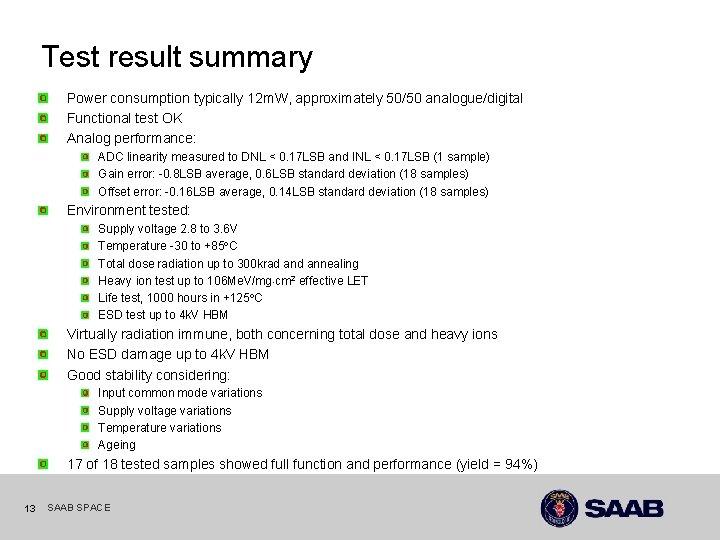

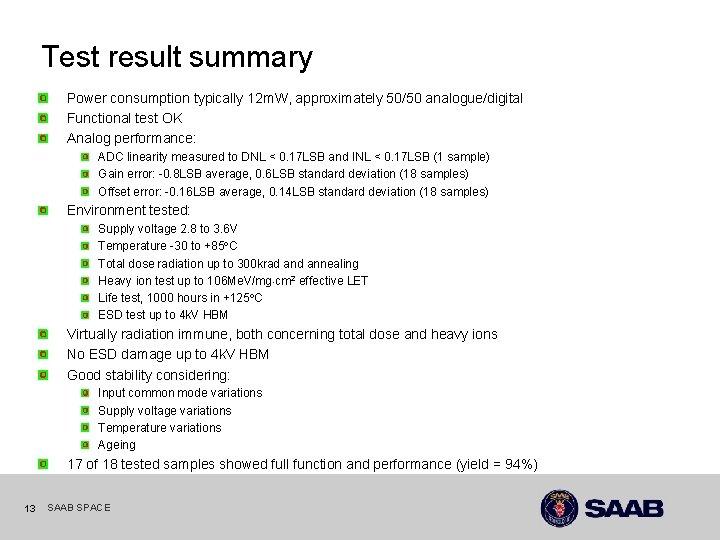

Test result summary Power consumption typically 12 m. W, approximately 50/50 analogue/digital Functional test OK Analog performance: ADC linearity measured to DNL < 0. 17 LSB and INL < 0. 17 LSB (1 sample) Gain error: -0. 8 LSB average, 0. 6 LSB standard deviation (18 samples) Offset error: -0. 16 LSB average, 0. 14 LSB standard deviation (18 samples) Environment tested: Supply voltage 2. 8 to 3. 6 V Temperature -30 to +85 C Total dose radiation up to 300 krad annealing Heavy ion test up to 106 Me. V/mg cm 2 effective LET Life test, 1000 hours in +125 C ESD test up to 4 k. V HBM Virtually radiation immune, both concerning total dose and heavy ions No ESD damage up to 4 k. V HBM Good stability considering: Input common mode variations Supply voltage variations Temperature variations Ageing 17 of 18 tested samples showed full function and performance (yield = 94%) 13 SAAB SPACE

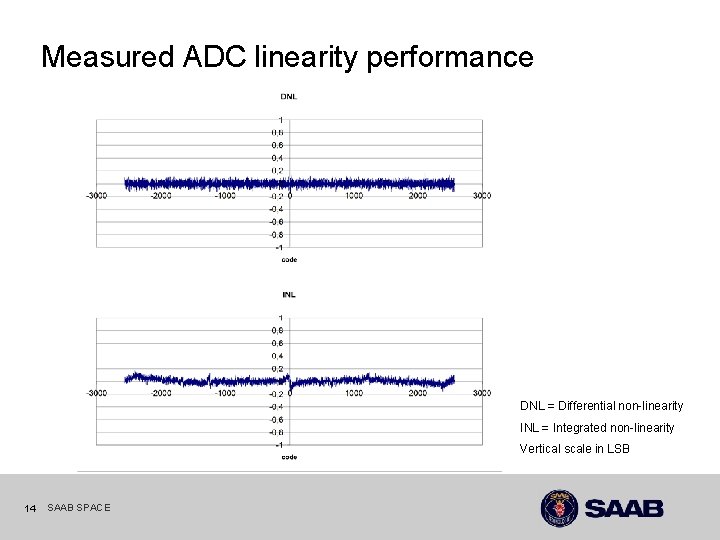

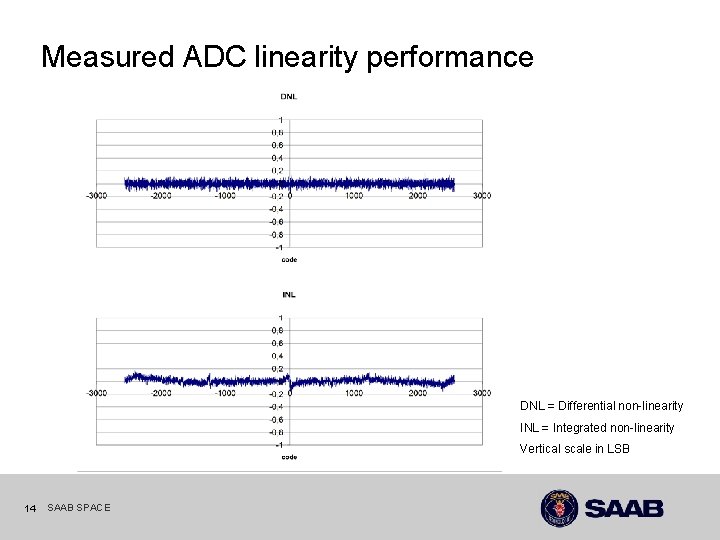

Measured ADC linearity performance DNL = Differential non-linearity INL = Integrated non-linearity Vertical scale in LSB 14 SAAB SPACE

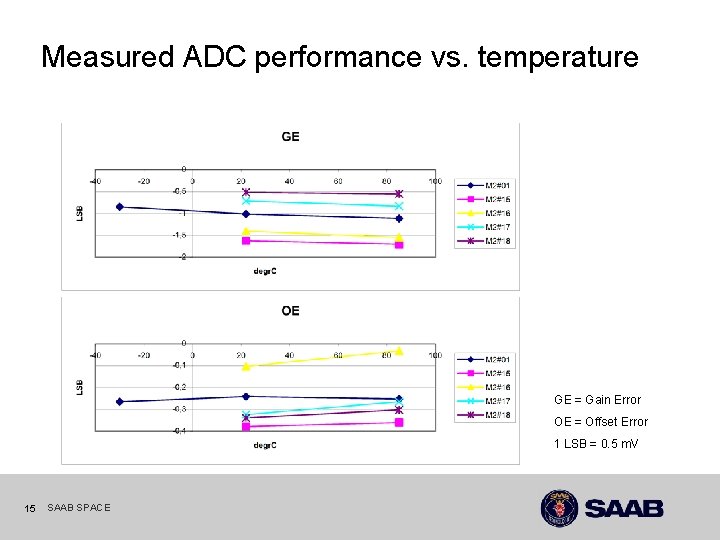

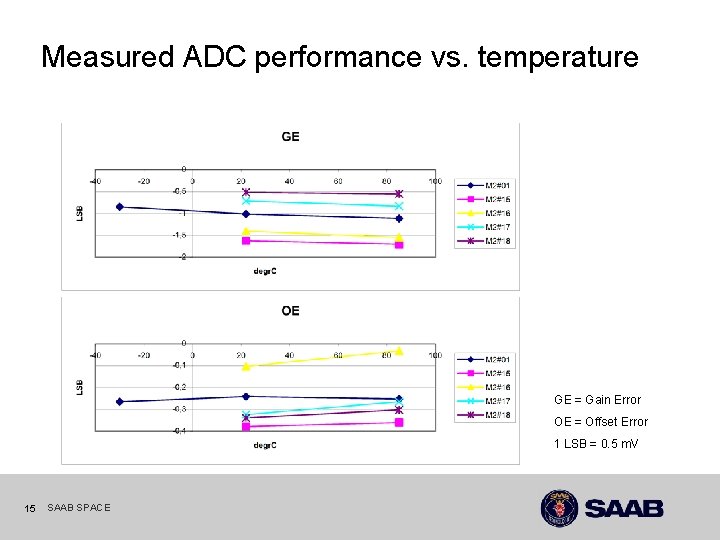

Measured ADC performance vs. temperature GE = Gain Error OE = Offset Error 1 LSB = 0. 5 m. V 15 SAAB SPACE

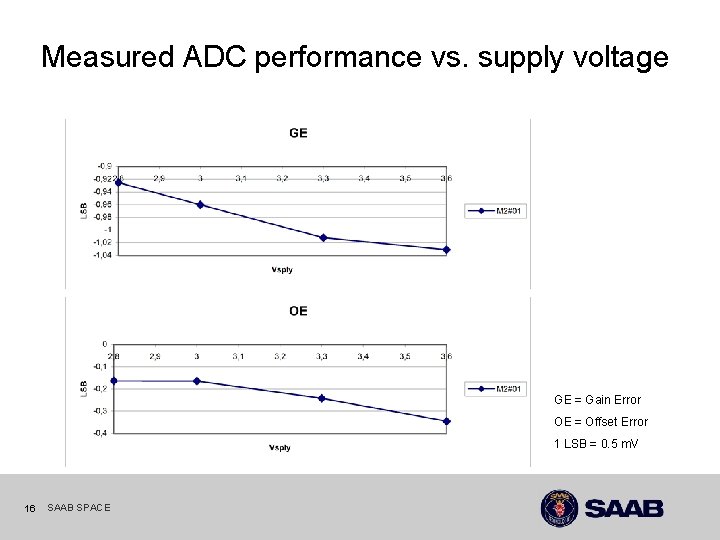

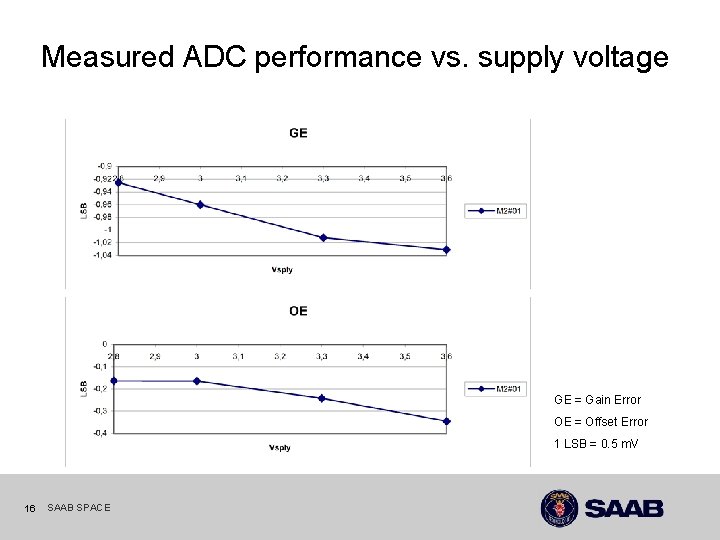

Measured ADC performance vs. supply voltage GE = Gain Error OE = Offset Error 1 LSB = 0. 5 m. V 16 SAAB SPACE

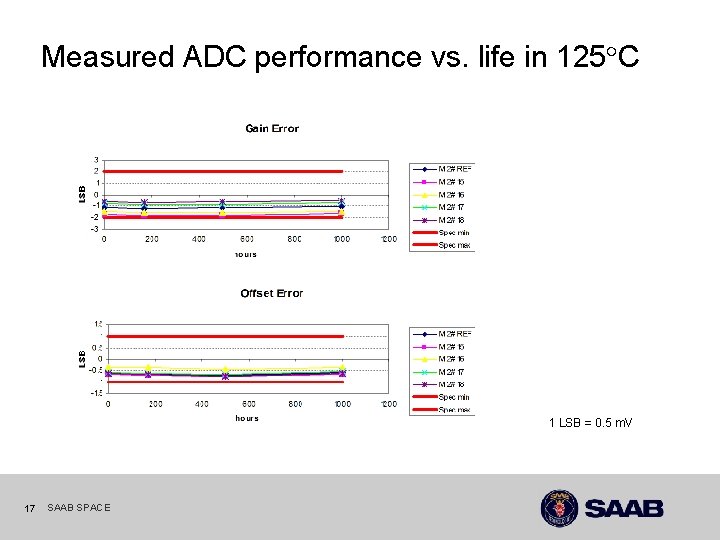

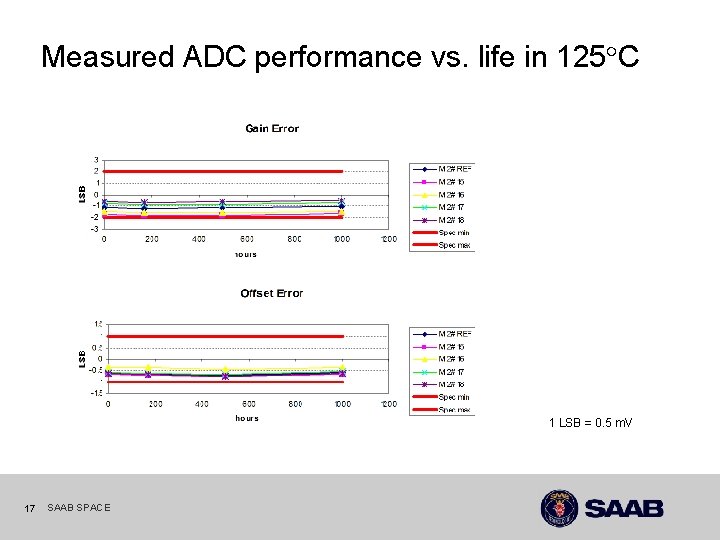

Measured ADC performance vs. life in 125 C 1 LSB = 0. 5 m. V 17 SAAB SPACE

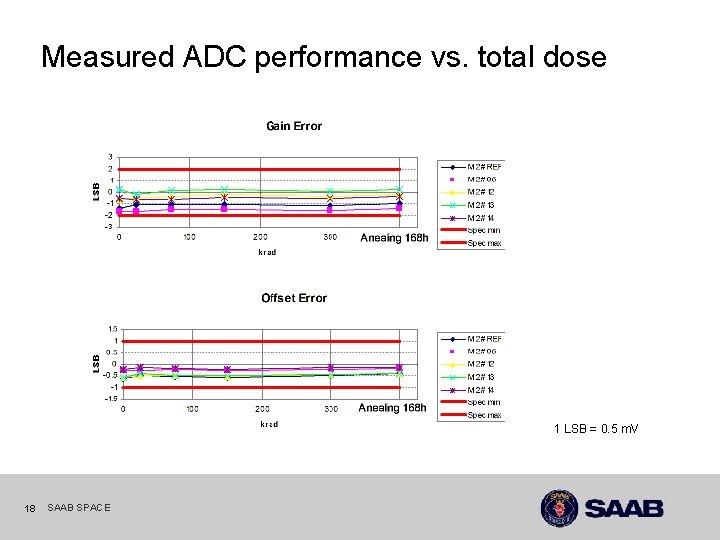

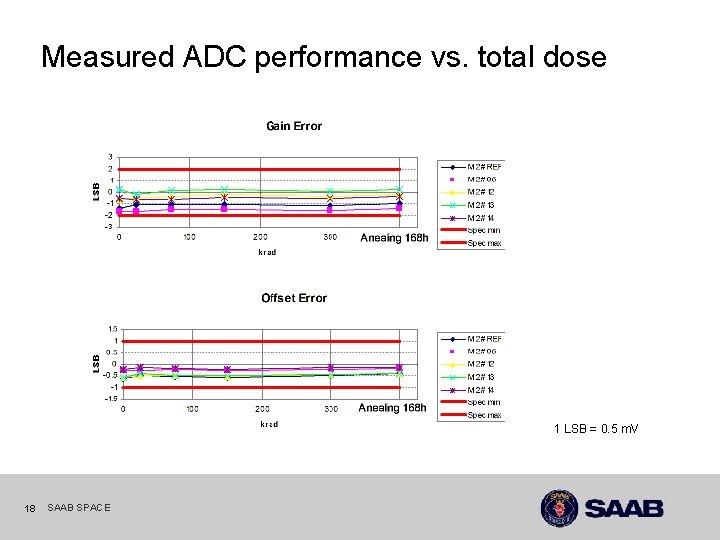

Measured ADC performance vs. total dose 1 LSB = 0. 5 m. V 18 SAAB SPACE

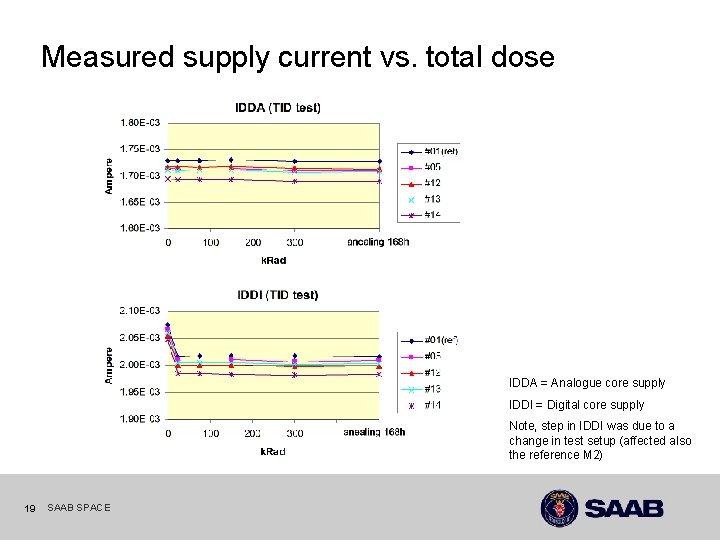

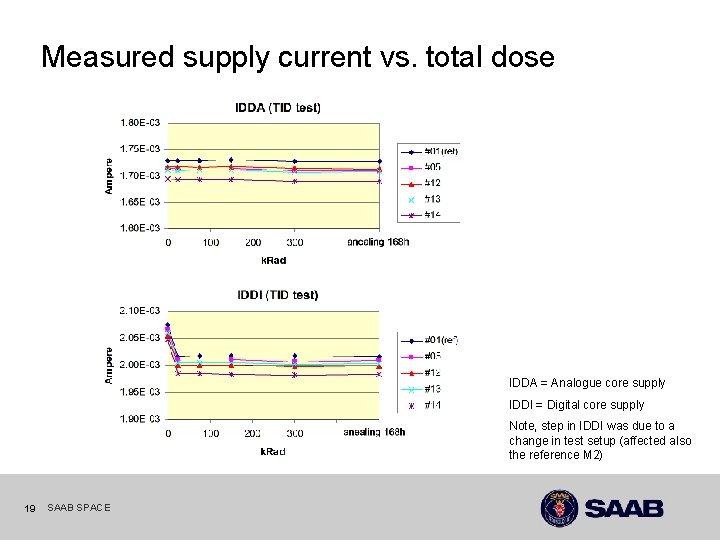

Measured supply current vs. total dose IDDA = Analogue core supply IDDI = Digital core supply Note, step in IDDI was due to a change in test setup (affected also the reference M 2) 19 SAAB SPACE

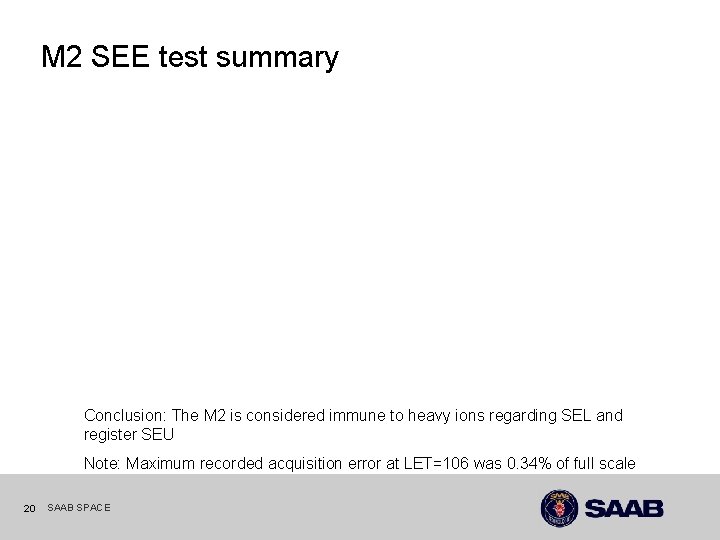

M 2 SEE test summary Conclusion: The M 2 is considered immune to heavy ions regarding SEL and register SEU Note: Maximum recorded acquisition error at LET=106 was 0. 34% of full scale 20 SAAB SPACE

via 1 array 3 D cell 21 SAAB SPACE

www. space. se 22 SAAB SPACE