The Lp GBT Project Paulo Moreira On behalf

The Lp. GBT Project Paulo Moreira On behalf of the GBT collaboration 2015 – 02 – 23 http: //cern. ch/proj-gbt Paulo. Moreira@cern. ch 1

Outline • GBT Project News • Lp. GBT & VL+ Link Architecture • The Low power GBTX (Lp. GBTX) – Achieving lower operation – Link bandwidth • Downlink • Uplink – FEC 5 • Uplink – FEC 12 – Slow control functionality • Lp. GBT project developments – GBLD 10 – Lp. GBLD – Lp. GBTX http: //cern. ch/proj-gbt Paulo. Moreira@cern. ch 2

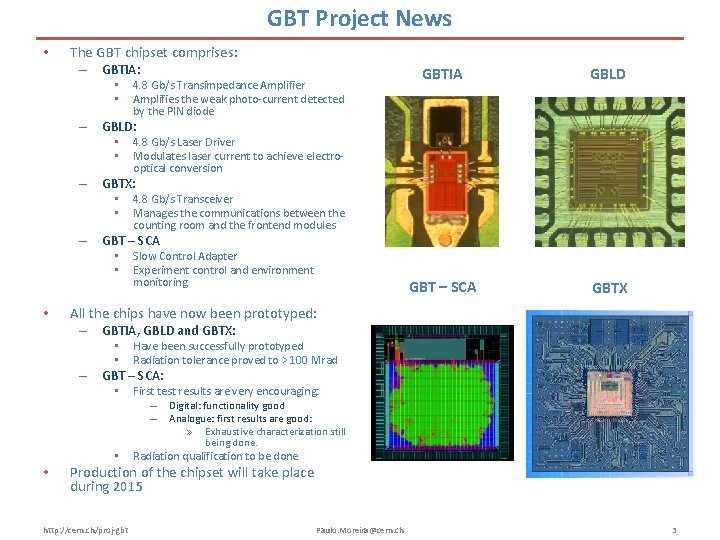

GBT Project News • The GBT chipset comprises: – GBTIA: • • 4. 8 Gb/s Transimpedance Amplifier Amplifies the weak photo-current detected by the PIN diode GBTIA GBLD GBT – SCA GBTX – GBLD: • • 4. 8 Gb/s Laser Driver Modulates laser current to achieve electrooptical conversion – GBTX: • • 4. 8 Gb/s Transceiver Manages the communications between the counting room and the frontend modules – GBT – SCA • • • Slow Control Adapter Experiment control and environment monitoring All the chips have now been prototyped: – GBTIA, GBLD and GBTX: • • Have been successfully prototyped Radiation tolerance proved to > 100 Mrad – GBT – SCA: • • First test results are very encouraging: – Digital: functionality good – Analogue: first results are good: » Exhaustive characterization still • Radiation qualification to be done being done. Production of the chipset will take place during 2015 http: //cern. ch/proj-gbt Paulo. Moreira@cern. ch 3

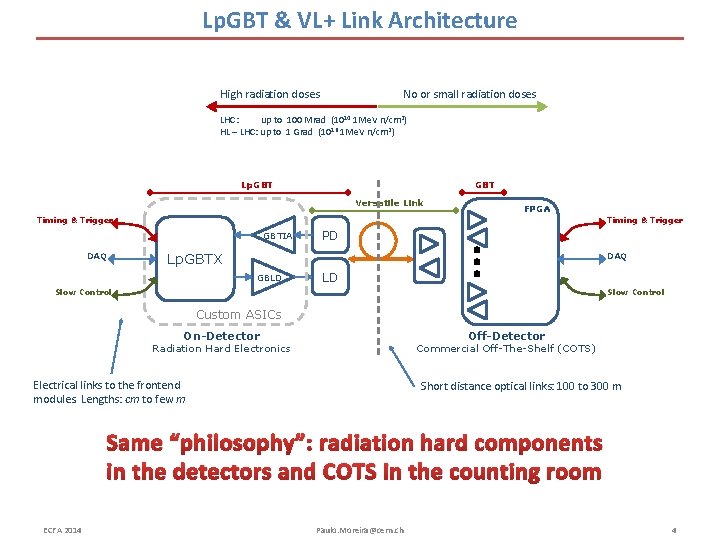

Lp. GBT & VL+ Link Architecture High radiation doses No or small radiation doses LHC: up to 100 Mrad (1014 1 Me. V n/cm 2) HL – LHC: up to 1 Grad (1016 1 Me. V n/cm 2) Lp. GBT Versatile Link FPGA Timing & Trigger GBTIA PD Lp. GBTX DAQ GBLD LD Slow Control Custom ASICs On-Detector Radiation Hard Electronics Off-Detector Commercial Off-The-Shelf (COTS) Electrical links to the frontend modules. Lengths: cm to few m Short distance optical links: 100 to 300 m Same “philosophy”: radiation hard components in the detectors and COTS in the counting room ECFA 2014 Paulo. Moreira@cern. ch 4

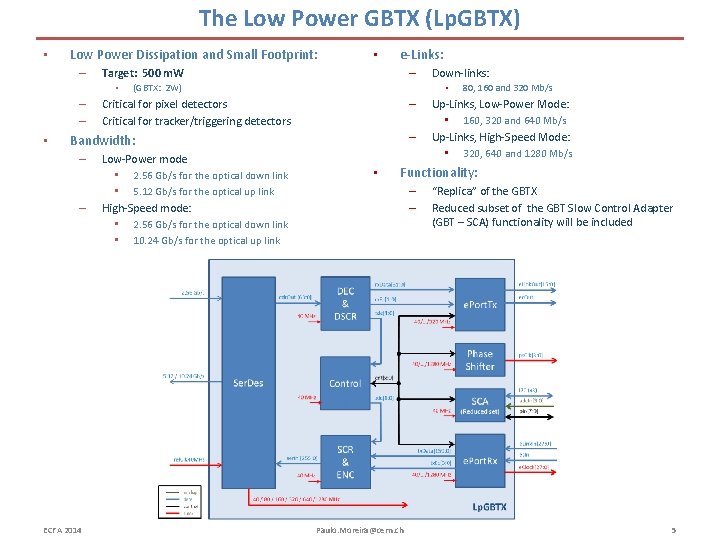

The Low Power GBTX (Lp. GBTX) • Low Power Dissipation and Small Footprint: – • e-Links: Target: 500 m. W • – – • – (GBTX: 2 W) • Critical for pixel detectors Critical for tracker/triggering detectors – – Bandwidth: – – ECFA 2014 Low-Power mode • 2. 56 Gb/s for the optical down link • 5. 12 Gb/s for the optical up link High-Speed mode: • 2. 56 Gb/s for the optical down link • 10. 24 Gb/s for the optical up link Down-links: • 80, 160 and 320 Mb/s Up-Links, Low-Power Mode: • 160, 320 and 640 Mb/s Up-Links, High-Speed Mode: • 320, 640 and 1280 Mb/s Functionality: – – Paulo. Moreira@cern. ch “Replica” of the GBTX Reduced subset of the GBT Slow Control Adapter (GBT – SCA) functionality will be included 5

Achieving Low Power Operation Technology • 130 nm → 65 nm • Vdd: 1. 5 V → 1. 2 V Architecture • Serializer / CDR circuits “merged” • Rationalization of the clock frequencies: – Single PLL will be used to generate all the clock frequencies needed • PLL shared by all the functional blocks – Binary counter generates all the required frequencies: • 5. 12 GHz down to 80 MHz (all with 50% duty cycle) – Transmit and receive frequencies are binary multiples of 40 MHz: • Down-link frame: 64 – bits (× 40 MHz) • Up-link frame: 128 or 256 – bits (× 40 MHz) • FPGA vendors documentation supports the use of these frame sizes: – Examples are: » Xilinx: Family 7 » Altera: Family V and 10 » Achronix: Speedster 22 i. HD – Successful LAB demo made with XILINX Virtex 7 http: //cern. ch/proj-gbt Paulo. Moreira@cern. ch 6

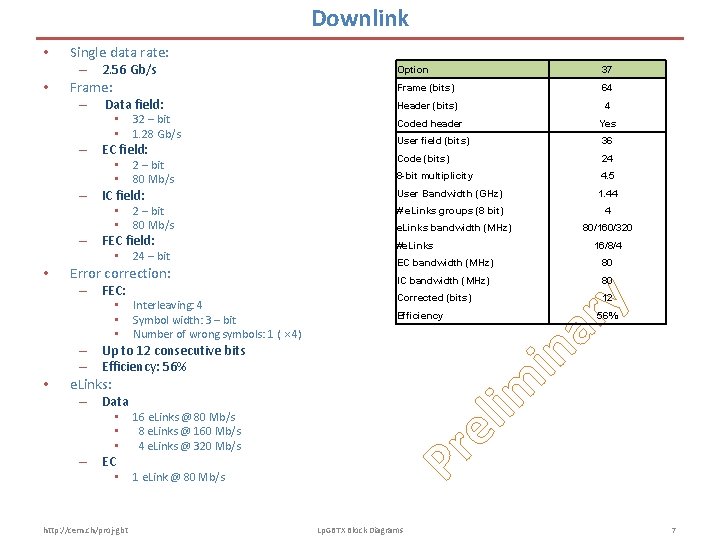

Downlink – EC field: • • 2 – bit 80 Mb/s – IC field: • • 2 – bit 80 Mb/s – FEC field: • Error correction: – FEC: • • • 64 Header (bits) 4 Coded header Yes User field (bits) 36 Code (bits) 24 8 -bit multiplicity 4. 5 User Bandwidth (GHz) 1. 44 # e. Links groups (8 bit) 4 e. Links bandwidth (MHz) #e. Links – EC • http: //cern. ch/proj-gbt 16 e. Links @ 80 Mb/s 8 e. Links @ 160 Mb/s 4 e. Links @ 320 Mb/s 1 e. Link @ 80 Mb/s 16/8/4 EC bandwidth (MHz) 80 IC bandwidth (MHz) 80 Corrected (bits) Efficiency – Up to 12 consecutive bits – Efficiency: 56% e. Links: – Data • • • 80/160/320 12 56% in • Interleaving: 4 Symbol width: 3 – bit Number of wrong symbols: 1 ( × 4) Frame (bits) im • 24 – bit 37 y 32 – bit 1. 28 Gb/s ar • • Option el • Single data rate: – 2. 56 Gb/s Frame: – Data field: Pr • Lp. GBTX Block Diagrams 7

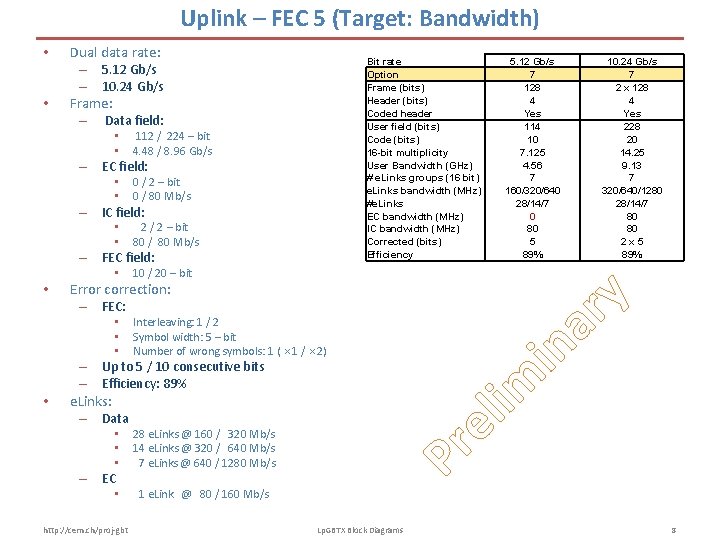

Uplink – FEC 5 (Target: Bandwidth) • • Bit rate Option Frame (bits) Header (bits) Coded header User field (bits) Code (bits) 16 -bit multiplicity User Bandwidth (GHz) # e. Links groups (16 bit) e. Links bandwidth (MHz) #e. Links EC bandwidth (MHz) IC bandwidth (MHz) Corrected (bits) Efficiency 112 / 224 – bit 4. 48 / 8. 96 Gb/s – EC field: • • 0 / 2 – bit 0 / 80 Mb/s – IC field: • • 2 / 2 – bit 80 / 80 Mb/s – FEC field: • y Interleaving: 1 / 2 Symbol width: 5 – bit Number of wrong symbols: 1 ( × 1 / × 2) • • • – EC • http: //cern. ch/proj-gbt 28 e. Links @ 160 / 320 Mb/s 14 e. Links @ 320 / 640 Mb/s 7 e. Links @ 640 / 1280 Mb/s im – Up to 5 / 10 consecutive bits – Efficiency: 89% e. Links: – Data el • 10 / 20 – bit Error correction: – FEC: • • • 10. 24 Gb/s 7 2 x 128 4 Yes 228 20 14. 25 9. 13 7 320/640/1280 28/14/7 80 80 2 x 5 89% Pr • 5. 12 Gb/s 7 128 4 Yes 114 10 7. 125 4. 56 7 160/320/640 28/14/7 0 80 5 89% ar • Dual data rate: – 5. 12 Gb/s – 10. 24 Gb/s Frame: – Data field: in • 1 e. Link @ 80 / 160 Mb/s Lp. GBTX Block Diagrams 8

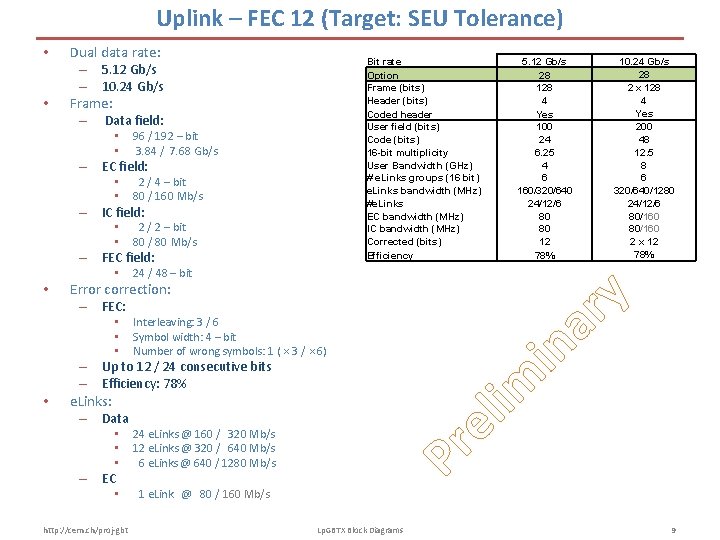

Uplink – FEC 12 (Target: SEU Tolerance) • • Bit rate Option Frame (bits) Header (bits) Coded header User field (bits) Code (bits) 16 -bit multiplicity User Bandwidth (GHz) # e. Links groups (16 bit) e. Links bandwidth (MHz) #e. Links EC bandwidth (MHz) IC bandwidth (MHz) Corrected (bits) Efficiency 96 / 192 – bit 3. 84 / 7. 68 Gb/s – EC field: • • 2 / 4 – bit 80 / 160 Mb/s – IC field: • • 2 / 2 – bit 80 / 80 Mb/s – FEC field: • y Interleaving: 3 / 6 Symbol width: 4 – bit Number of wrong symbols: 1 ( × 3 / × 6) • • • – EC • http: //cern. ch/proj-gbt 24 e. Links @ 160 / 320 Mb/s 12 e. Links @ 320 / 640 Mb/s 6 e. Links @ 640 / 1280 Mb/s im – Up to 12 / 24 consecutive bits – Efficiency: 78% e. Links: – Data el • 24 / 48 – bit Error correction: – FEC: • • • 10. 24 Gb/s 28 2 x 128 4 Yes 200 48 12. 5 8 6 320/640/1280 24/12/6 80/160 2 x 12 78% Pr • 5. 12 Gb/s 28 128 4 Yes 100 24 6. 25 4 6 160/320/640 24/12/6 80 80 12 78% ar • Dual data rate: – 5. 12 Gb/s – 10. 24 Gb/s Frame: – Data field: in • 1 e. Link @ 80 / 160 Mb/s Lp. GBTX Block Diagrams 9

“SC” Functionality Slow Control Functionality • Three I 2 C masters: – One dedicated to the Versatile Link • 8 - bit ADC: – 4 inputs • Temperature: – On chip: yes – Sensor: yes y • Voltage monitoring ar – DC/DC input voltage Pr el im in • 8 x DIO (programmable parallel port) http: //cern. ch/proj-gbt Lp. GBTX Block Diagrams 10

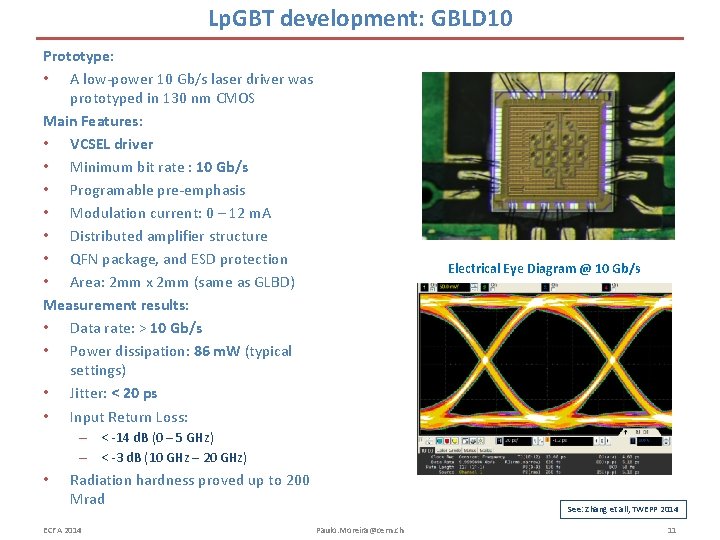

Lp. GBT development: GBLD 10 Prototype: • A low-power 10 Gb/s laser driver was prototyped in 130 nm CMOS Main Features: • VCSEL driver • Minimum bit rate : 10 Gb/s • Programable pre-emphasis • Modulation current: 0 – 12 m. A • Distributed amplifier structure • QFN package, and ESD protection • Area: 2 mm x 2 mm (same as GLBD) Measurement results: • Data rate: > 10 Gb/s • Power dissipation: 86 m. W (typical settings) • Jitter: < 20 ps • Input Return Loss: Electrical Eye Diagram @ 10 Gb/s – < -14 d. B (0 – 5 GHz) – < -3 d. B (10 GHz – 20 GHz) • Radiation hardness proved up to 200 Mrad ECFA 2014 See: Zhang et all, TWEPP 2014 Paulo. Moreira@cern. ch 11

New Developments Lp. GBLD • 10 Gb/s laser driver • Very low power consumption: < 70 m. W – Including VCSEL bias and modulation currents • Falling edge pre-emphasis • Directly bonded to the VCSEL – Single ended output – Merged modulation and bias currents • Compatible with the VL+ project (See Jan Troska’s presentation): – Size: 1. 9 mm × 0. 4 mm • Supply: 1. 2 and 2. 5 V • Technology: 65 nm CMOS Prototyping • May 2015 Collaboration • SMU / KU LEUVEN / CERN http: //cern. ch/proj-gbt Paulo. Moreira@cern. ch 12

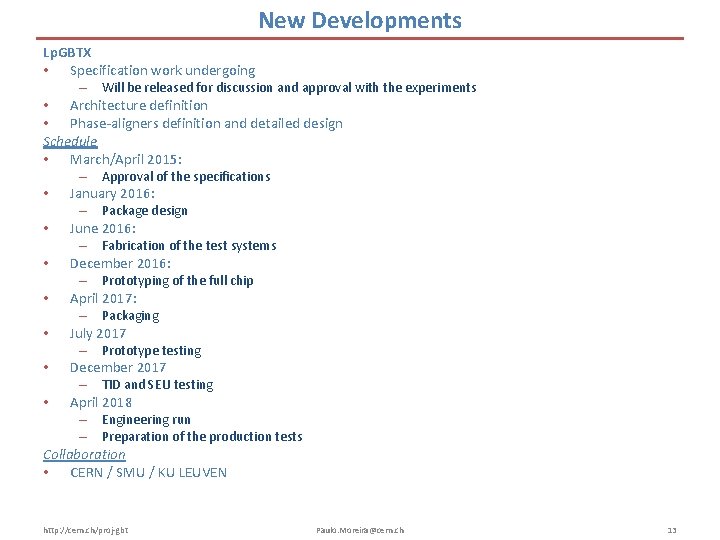

New Developments Lp. GBTX • Specification work undergoing – Will be released for discussion and approval with the experiments • Architecture definition • Phase-aligners definition and detailed design Schedule • March/April 2015: – Approval of the specifications • January 2016: – Package design • June 2016: – Fabrication of the test systems • December 2016: – Prototyping of the full chip • April 2017: – Packaging • July 2017 – Prototype testing • December 2017 – TID and SEU testing • April 2018 – Engineering run – Preparation of the production tests Collaboration • CERN / SMU / KU LEUVEN http: //cern. ch/proj-gbt Paulo. Moreira@cern. ch 13

Backup Slides on the GBT Project http: //cern. ch/proj-gbt Paulo. Moreira@cern. ch 14

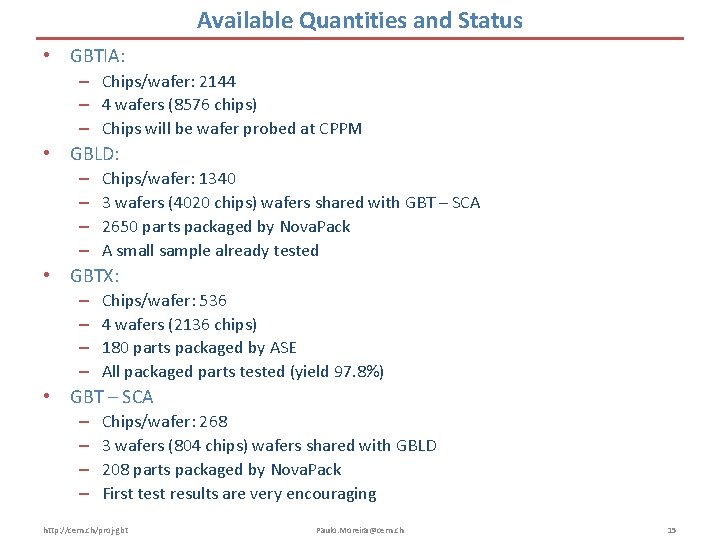

Available Quantities and Status • GBTIA: – Chips/wafer: 2144 – 4 wafers (8576 chips) – Chips will be wafer probed at CPPM • GBLD: – – Chips/wafer: 1340 3 wafers (4020 chips) wafers shared with GBT – SCA 2650 parts packaged by Nova. Pack A small sample already tested • GBTX: – – Chips/wafer: 536 4 wafers (2136 chips) 180 parts packaged by ASE All packaged parts tested (yield 97. 8%) • GBT – SCA – – Chips/wafer: 268 3 wafers (804 chips) wafers shared with GBLD 208 parts packaged by Nova. Pack First test results are very encouraging http: //cern. ch/proj-gbt Paulo. Moreira@cern. ch 15

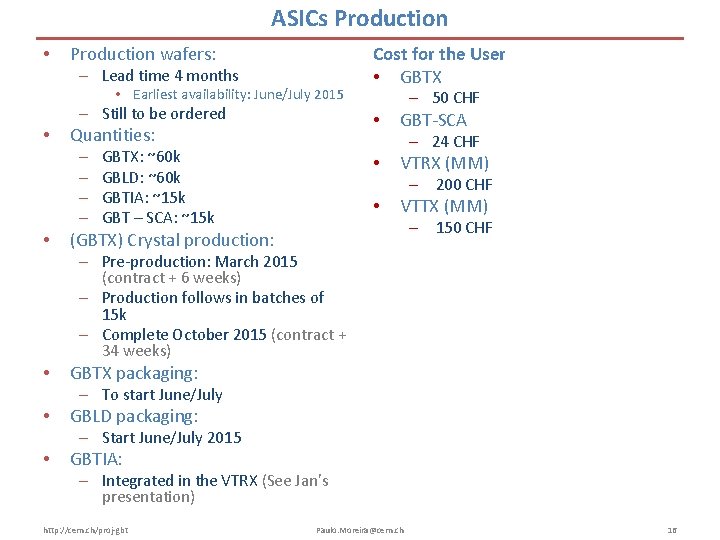

ASICs Production • Production wafers: – Lead time 4 months • Earliest availability: June/July 2015 – Still to be ordered • • – 50 CHF • Quantities: – – Cost for the User • GBTX GBT-SCA – 24 CHF GBTX: ~60 k GBLD: ~60 k GBTIA: ~15 k GBT – SCA: ~15 k • VTRX (MM) – 200 CHF • VTTX (MM) – 150 CHF (GBTX) Crystal production: – Pre-production: March 2015 (contract + 6 weeks) – Production follows in batches of 15 k – Complete October 2015 (contract + 34 weeks) • GBTX packaging: – To start June/July • GBLD packaging: – Start June/July 2015 • GBTIA: – Integrated in the VTRX (See Jan’s presentation) http: //cern. ch/proj-gbt Paulo. Moreira@cern. ch 16

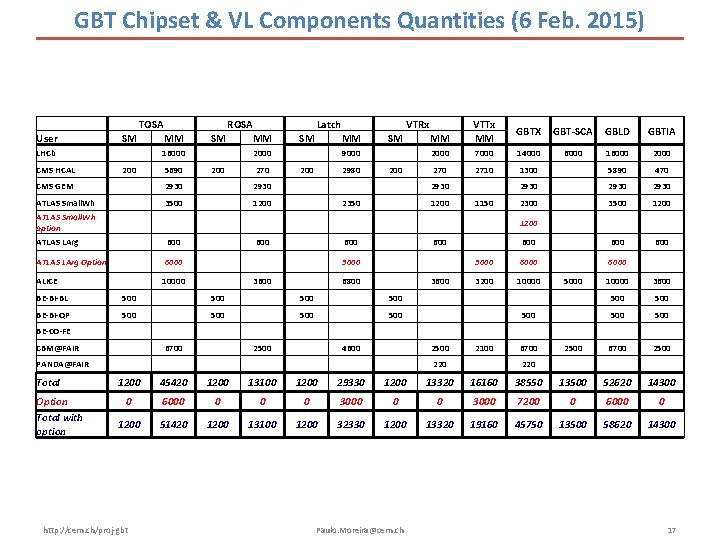

GBT Chipset & VL Components Quantities (6 Feb. 2015) User SM MM VTTx MM SM MM LHCb 16000 2000 9000 2000 7000 14000 6000 16000 2000 CMS HCAL 200 5690 200 270 200 2980 200 2710 1300 5890 470 CMS GEM 2930 2930 ATLAS Small. Wh 3500 1200 2350 1200 1150 2300 3500 1200 ATLAS Small. Wh option 1200 ATLAS LArg 600 600 ATLAS LArg Option 6000 3000 6000 ALICE 10000 3600 6800 3600 3200 10000 5000 10000 3600 BE-BI-BL 500 500 BE-BI-QP 500 500 BE-CO-FE CBM@FAIR 6700 2500 4600 2500 2100 6700 2500 PANDA@FAIR 220 1200 45420 1200 13100 1200 29330 1200 13320 16160 38550 13500 52620 14300 0 6000 0 3000 7200 0 6000 0 1200 51420 1200 13100 1200 32330 1200 13320 19160 45750 13500 58620 14300 Total Option Total with option TOSA http: //cern. ch/proj-gbt ROSA SM MM Latch VTRx Paulo. Moreira@cern. ch GBTX GBT-SCA GBLD GBTIA 17

Backup Slides on the Lp. GBT http: //cern. ch/proj-gbt Paulo. Moreira@cern. ch 18

Error Cross Section and Data Rate http: //cern. ch/proj-gbt Paulo. Moreira@cern. ch 19

![2. 56 Gb/s cdr. Out [63: 0] 40 MHz DEC & DSCR rx. Data[31: 2. 56 Gb/s cdr. Out [63: 0] 40 MHz DEC & DSCR rx. Data[31:](http://slidetodoc.com/presentation_image/319d8a06994eb9184c5e6458f199b2e7/image-20.jpg)

2. 56 Gb/s cdr. Out [63: 0] 40 MHz DEC & DSCR rx. Data[31: 0] e. Link. Out[15: 0] rx. Ec[1: 0] ec. Out e. Port. Tx rx. Ic[1: 0] 40/…/320 MHz 40/…/1280 MHz 5. 12 / 10. 24 Gb/s Ser. Des Control 40 MHz ser. In [255: 0] 40 MHz analog data control clock http: //cern. ch/proj-gbt ps. Clk[3: 0] cnt[x: 0] I 2 C (x 3) tx. Ic[1: 0] 40 MHz ref. Clk 40 MHz Phase Shifter SCR & ENC 40 / 80 / 160 / 320 / 640 /1280 MHz Lp. GBTX Block Diagrams SCA (Reduced set) pio[7: 0] e. Link. In[27: 0] tx. Data[159: 0] tx. Ec[3: 0] adc. In[3: 0] e. Port. Rx ec. In e. Clock[27: 0] 40/…/1280 MHz Lp. GBTX 20

- Slides: 20