The ISA Level The Instruction Set Architecture ISA

- Slides: 36

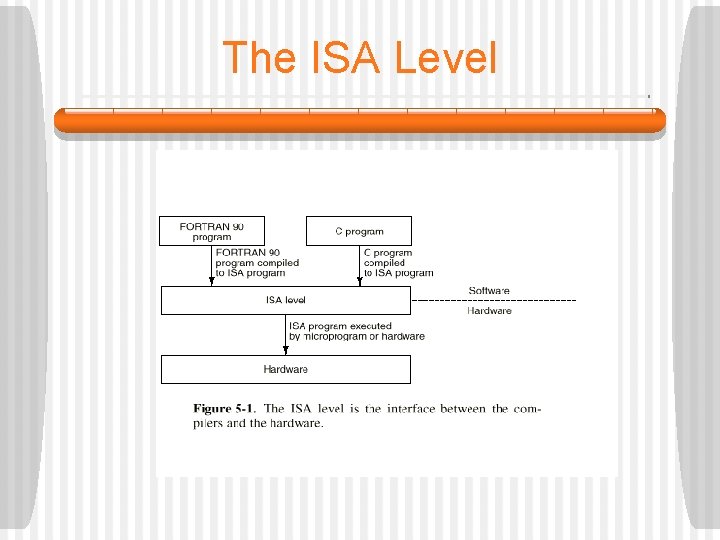

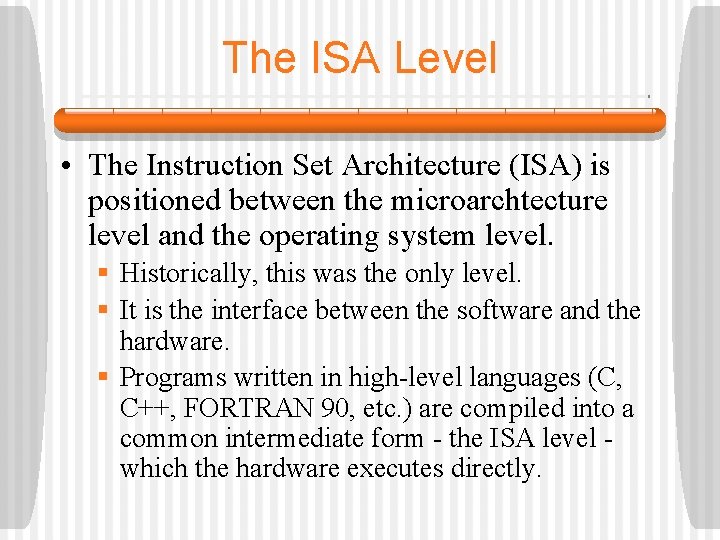

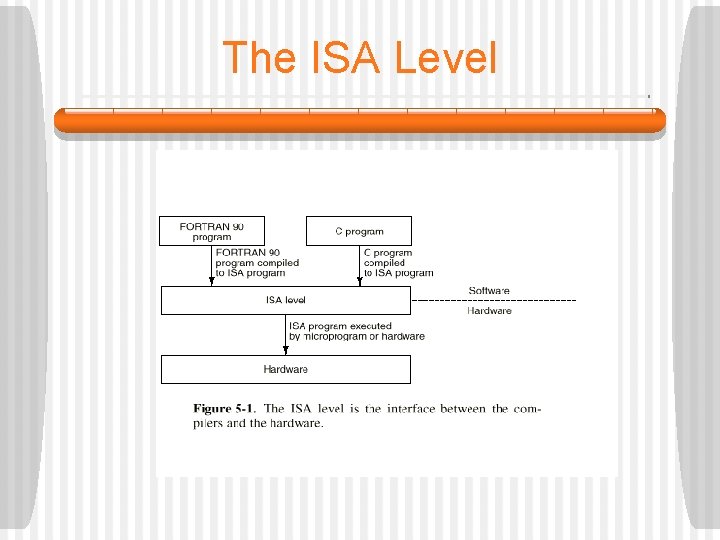

The ISA Level • The Instruction Set Architecture (ISA) is positioned between the microarchtecture level and the operating system level. § Historically, this was the only level. § It is the interface between the software and the hardware. § Programs written in high-level languages (C, C++, FORTRAN 90, etc. ) are compiled into a common intermediate form - the ISA level which the hardware executes directly.

The ISA Level

The ISA Level § How do we decide what the ISA should support? • Ideally, ask both hardware and software engineers the features they would like to have and reach a compromise. • In practice, the most important feature is backward compatibility. • A good ISA should define a set of instructions that can be implemented effectively in current and future technologies. • It should also provide a clean target for compiled code.

The ISA Level § For some architectures, the ISA level is specified by a formal defining document (e. g. both V 9 SPARC and JVM). • This allows different implementations of the same architecture. • Such defining documents contain normative sections, which impose requirements, and informative sections, that are intended to help the reader but are not part of the formal specification. • There is no formal defining document for the Pentium II.

The ISA Level § There at least two modes at the ISA level: • Kernel mode is intended to run the operating system and allows all instructions to be executed. • User mode is intended to run application programs and does not permit certain sensitive instructions to be executed. § All computers divide memory up into cells that have consecutive addresses. • The most common cell size is 8 bits (called a byte). • The reason for using 8 bits is that ASCII codes are 7 bits (add one bit for parity).

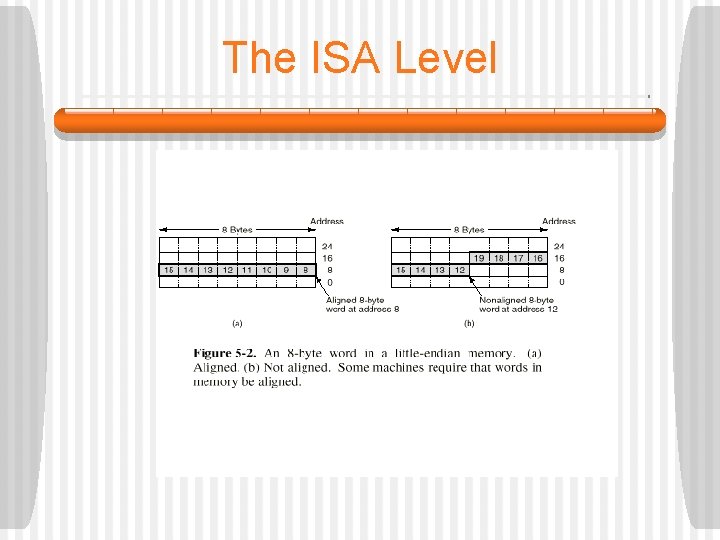

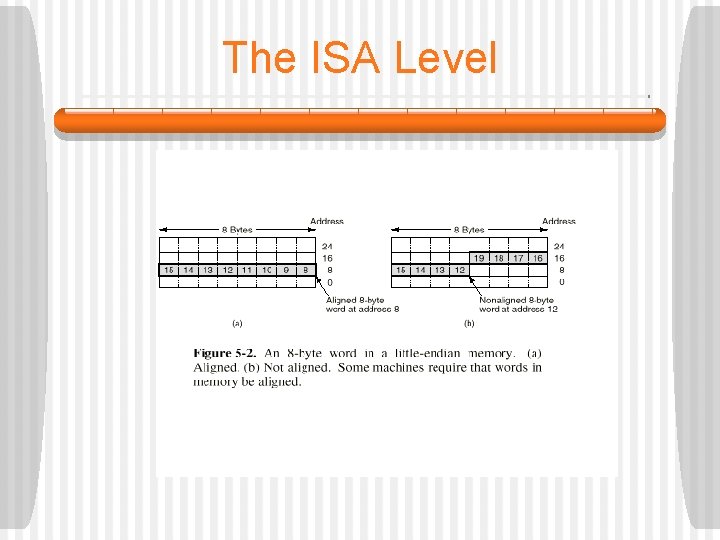

Memory Models § Bytes are grouped into 4 -byte (32 bit) or 8 -byte (64 bit) words with instructions available for manipulating entire words. § Many architectures require words to be aligned on their natural boundaries. • This allows more efficient memory operations. • Reading words at arbitrary addresses requires extra logic on the chip, making it bigger and more expensive. • The Pentium II does not require alignment in order to retain compatibility with the 8088.

The ISA Level

Registers • All computers have some registers visible at the ISA level. These § control execution of the program § hold temporary results § are used for other purposes • ISA level registers can be divided into two categories: § special-purpose (PC, SP, etc. ) § general-purpose (local variables, etc. )

Registers § On some machines the general-purpose registers are completely symmetric and interchangeable. § It is common for compilers and operating systems to adopt conventions about how the general-purpose registers are used. § Many special-purpose registers are available only in kernel mode (those that control cache, I/O devices and other hardware).

Registers • One control register that is a hybrid kernel/user is the flags register or PSW (Program Status Word). This register contains various condition bits: § § N - Set when the result was Negative Z - Set when the result was Zero V - Set when the result caused an o. Verflow C - Set when the result caused a Carry out of the leftmost bit § A - Set when there was a carry out of bit 3 (Auxiliary carry) § P - Set when the result had even parity

Pentium II ISA Level § The Pentium II has three operating modes, two of which make it look like an 8088. In real mode, features added since the 8088 are turned off. • An application error causes the machine to crash. § Virtual 8086 mode makes it possible to run old 8088 programs in a protected way. • A special isolated environment that acts like an 8088 is created, except that if the program crashes, the operating system is informed. • Used when an MS-DOS window is opened.

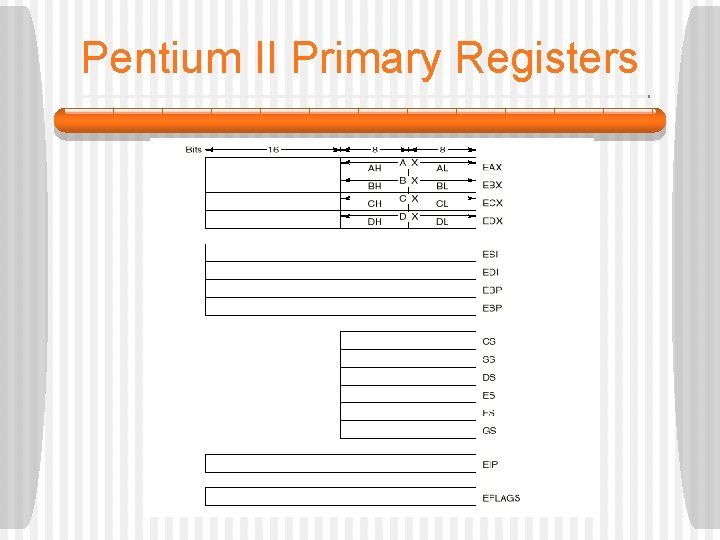

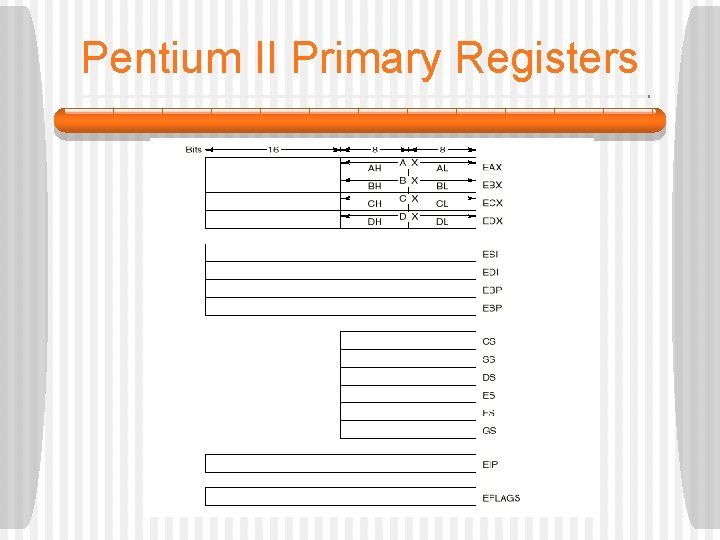

Pentium II Registers § The first four registers are general-purpose: • • EAX is the main arithmetic register. EBX is good for holding pointers ECX plays a role in looping EDX is needed for multiplication and division (holding half of the 64 -bit products and dividends) § These registers contain 8 - and 16 -bit registers in the low-order bits for manipulation of 8 - and 16 -bit quantities, respectively.

Pentium II Registers § The next three registers are general-purpose: • ESI and EDI hold pointers into memory, especially for the hardware string manipulation routines. • EBP is a pointer register (typically to the base of the current stack frame, like LV in JVM). • ESP is the stack pointer. § CS through GS are segment registers. § EIP is the program counter § EFLAGS is the PSW.

Pentium II Primary Registers

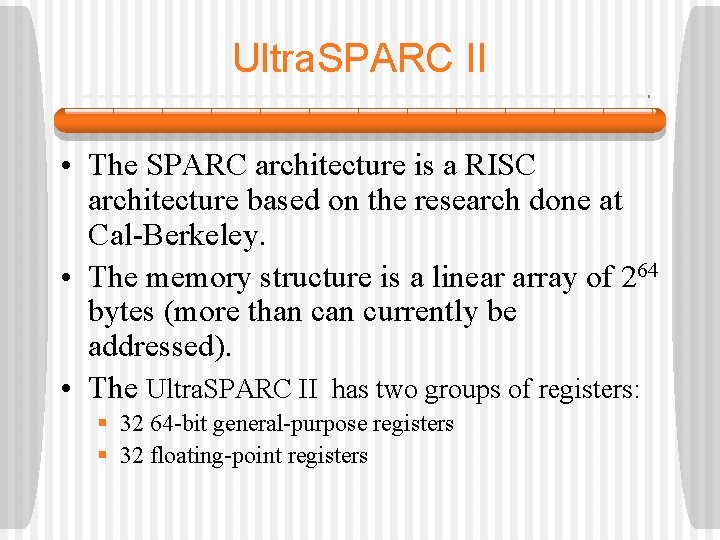

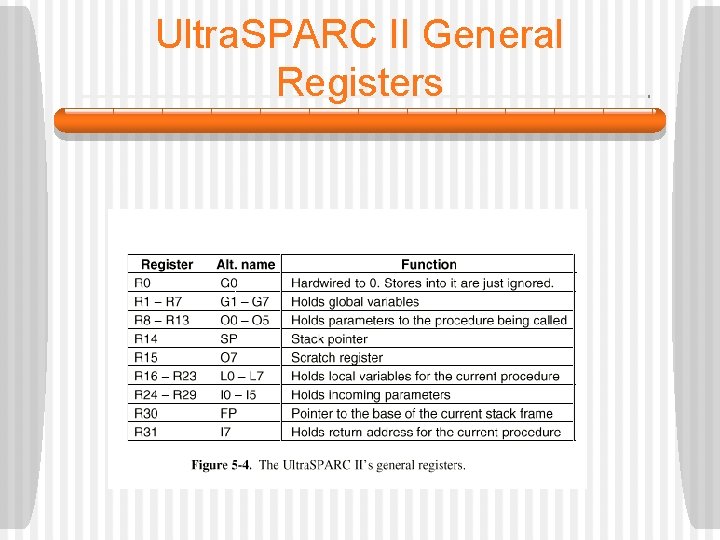

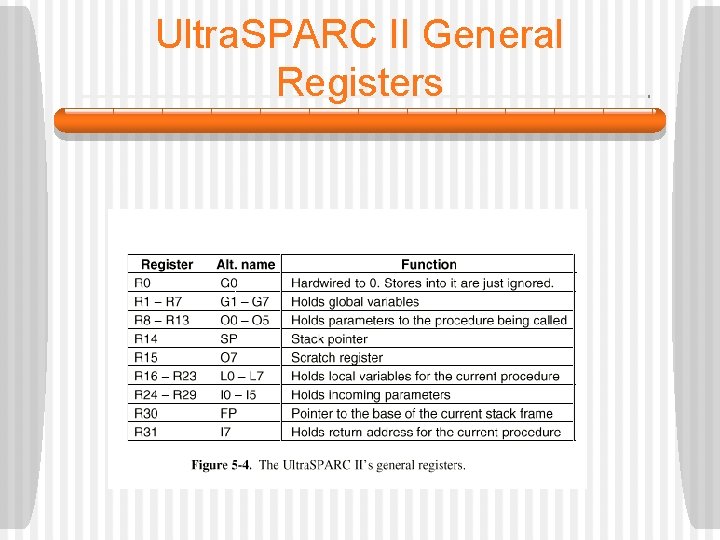

Ultra. SPARC II • The SPARC architecture is a RISC architecture based on the research done at Cal-Berkeley. • The memory structure is a linear array of 264 bytes (more than currently be addressed). • The Ultra. SPARC II has two groups of registers: § 32 64 -bit general-purpose registers § 32 floating-point registers

Ultra. SPARC II General Registers

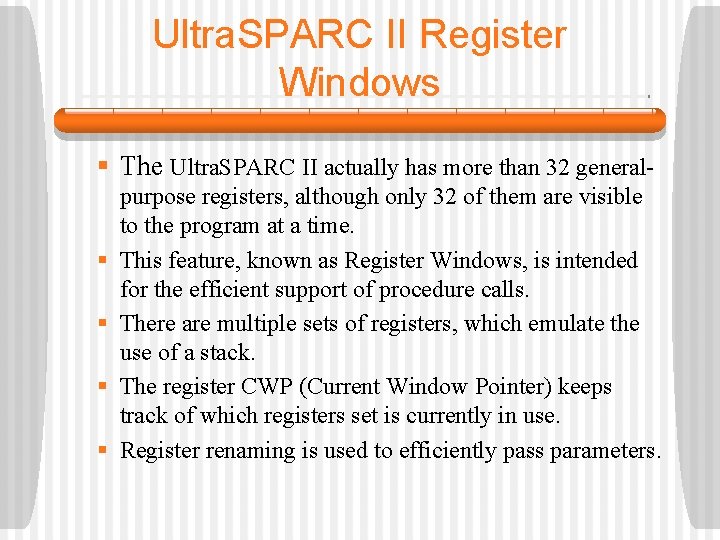

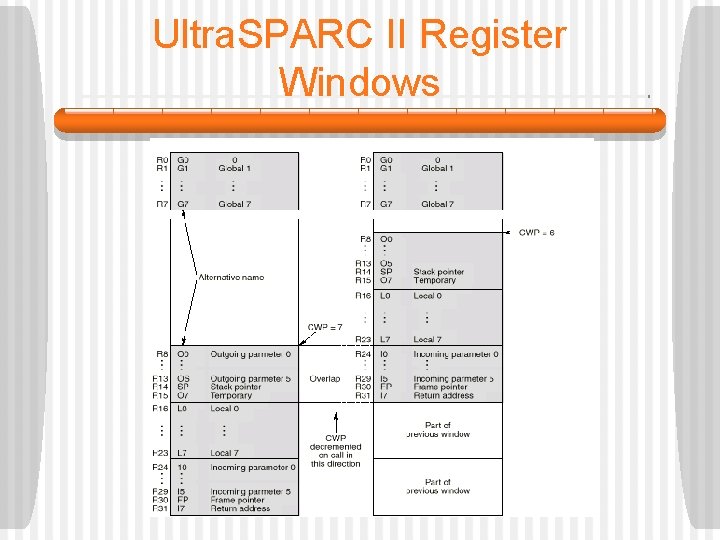

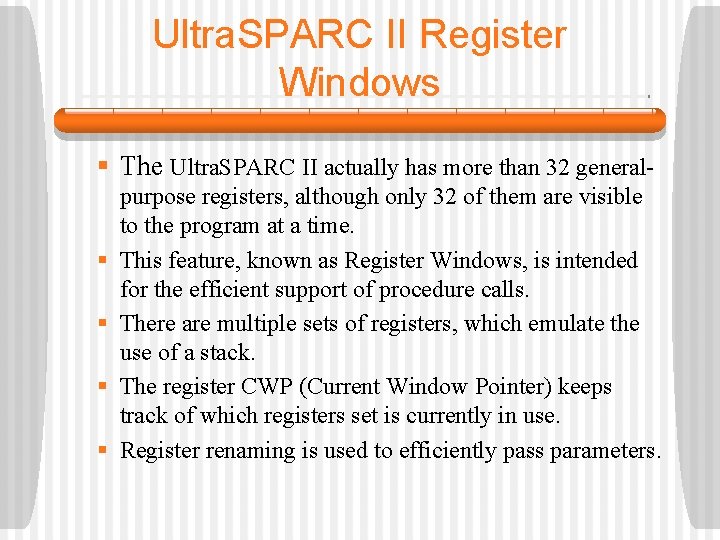

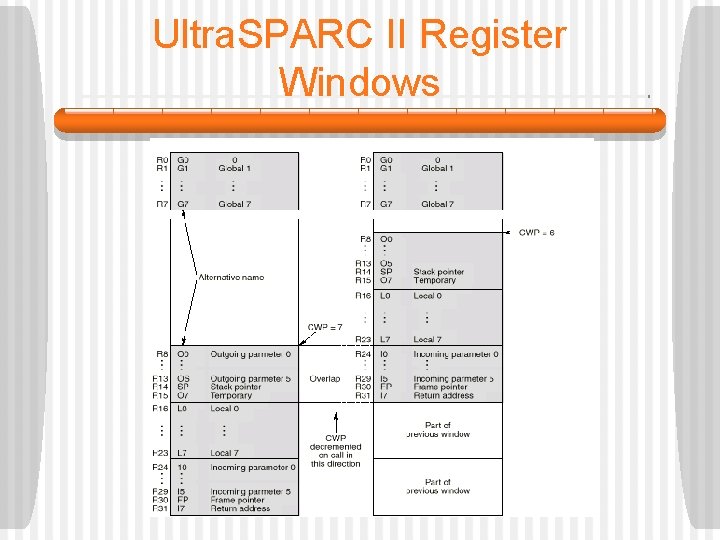

Ultra. SPARC II Register Windows § The Ultra. SPARC II actually has more than 32 general§ § purpose registers, although only 32 of them are visible to the program at a time. This feature, known as Register Windows, is intended for the efficient support of procedure calls. There are multiple sets of registers, which emulate the use of a stack. The register CWP (Current Window Pointer) keeps track of which registers set is currently in use. Register renaming is used to efficiently pass parameters.

Ultra. SPARC II Register Windows

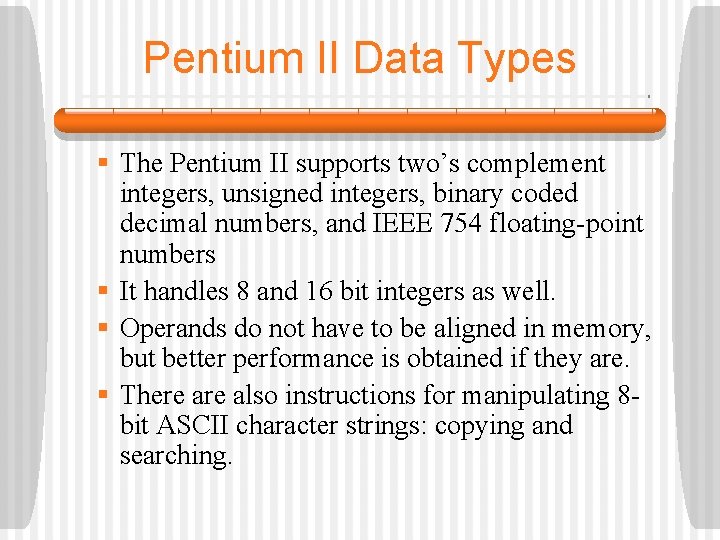

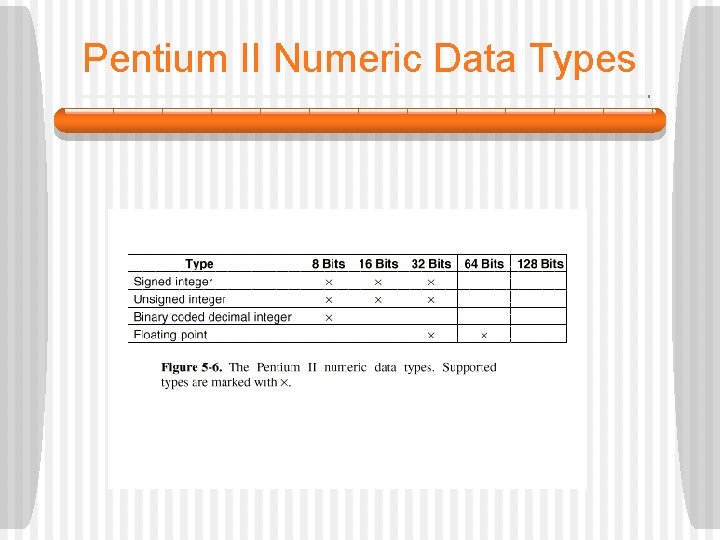

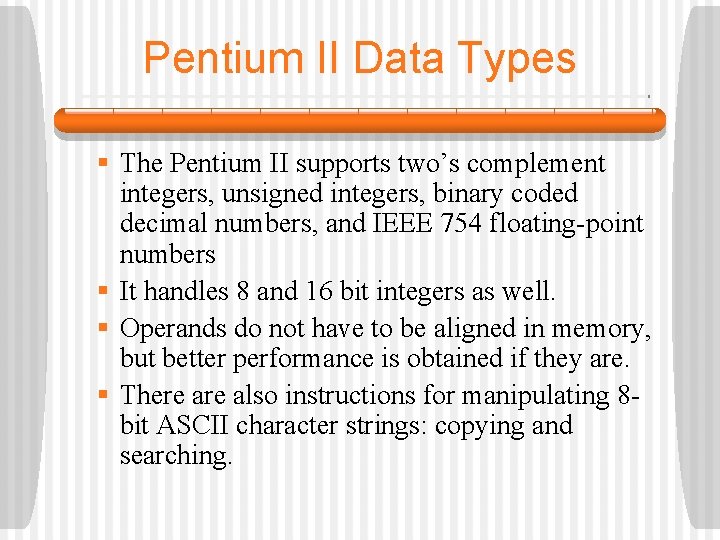

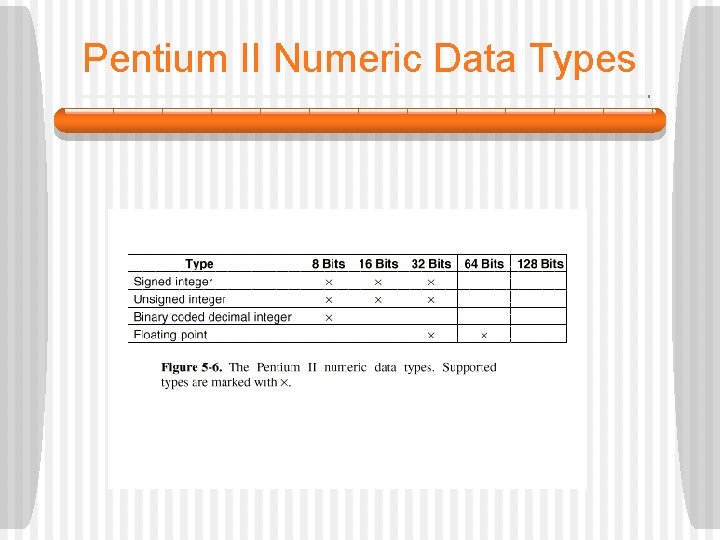

Pentium II Data Types § The Pentium II supports two’s complement integers, unsigned integers, binary coded decimal numbers, and IEEE 754 floating-point numbers § It handles 8 and 16 bit integers as well. § Operands do not have to be aligned in memory, but better performance is obtained if they are. § There also instructions for manipulating 8 bit ASCII character strings: copying and searching.

Pentium II Numeric Data Types

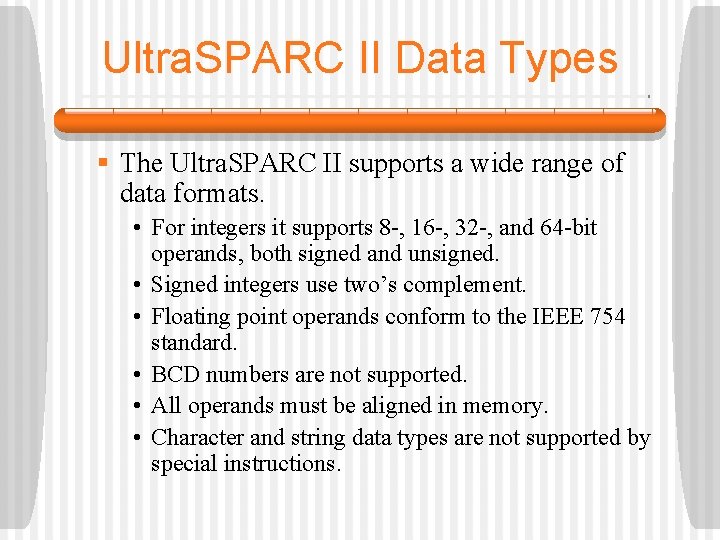

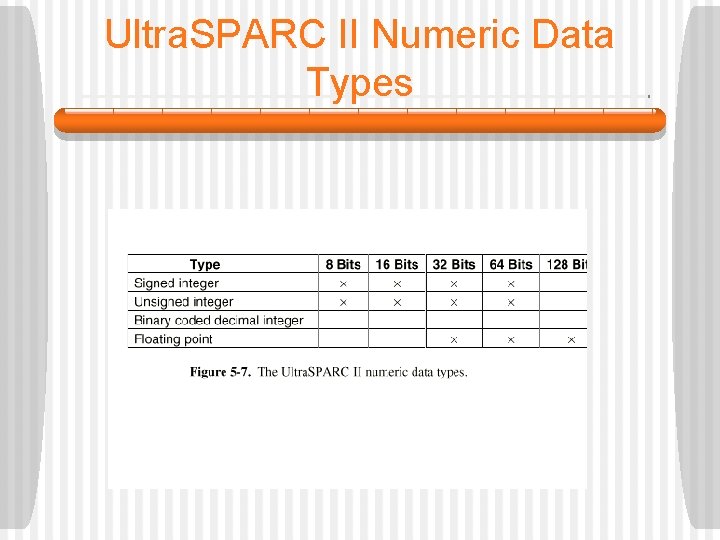

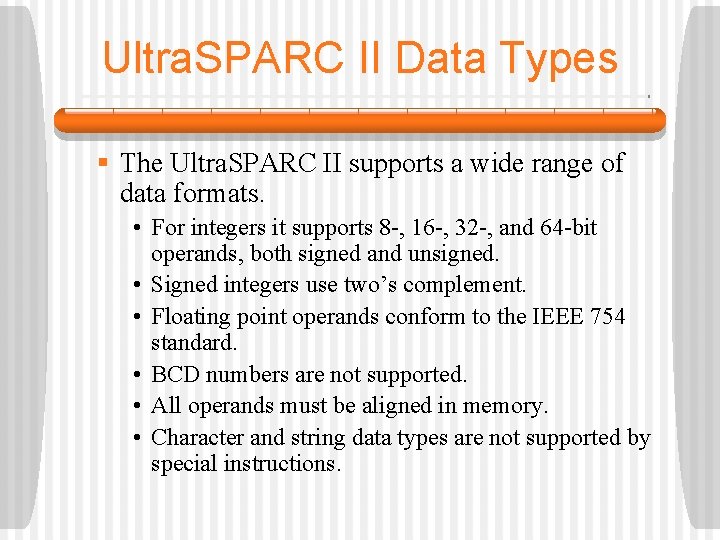

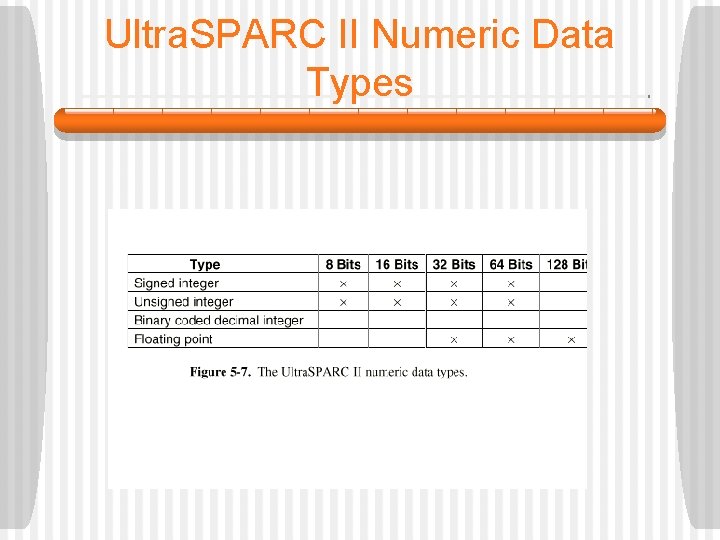

Ultra. SPARC II Data Types § The Ultra. SPARC II supports a wide range of data formats. • For integers it supports 8 -, 16 -, 32 -, and 64 -bit operands, both signed and unsigned. • Signed integers use two’s complement. • Floating point operands conform to the IEEE 754 standard. • BCD numbers are not supported. • All operands must be aligned in memory. • Character and string data types are not supported by special instructions.

Ultra. SPARC II Numeric Data Types

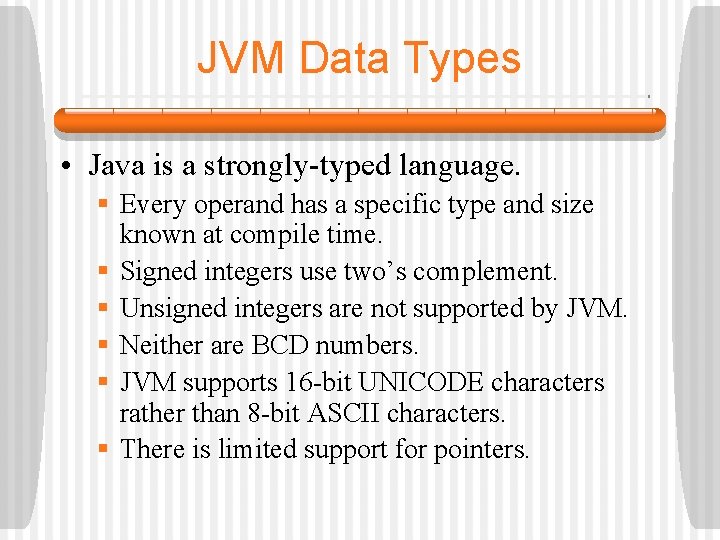

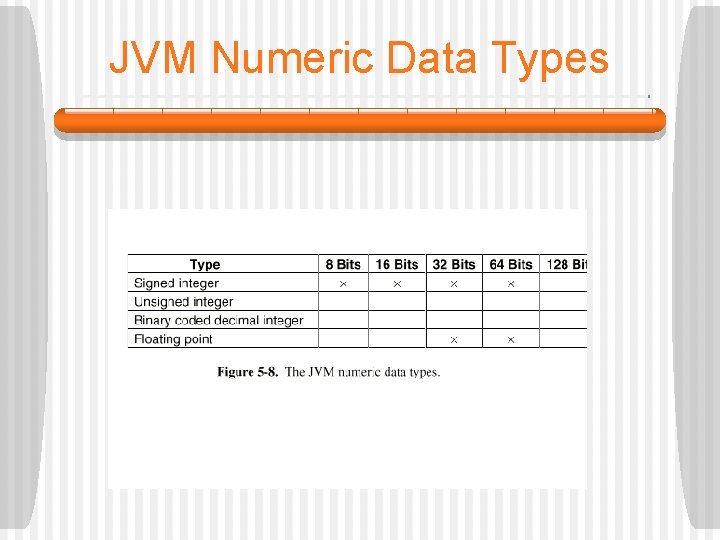

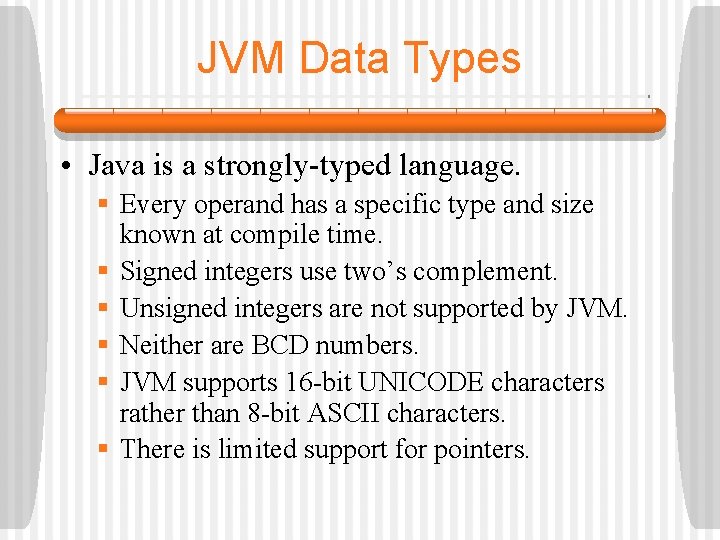

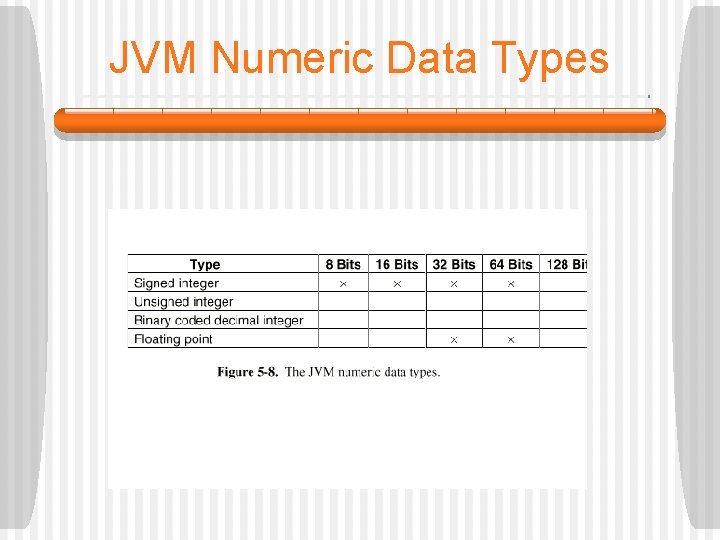

JVM Data Types • Java is a strongly-typed language. § Every operand has a specific type and size known at compile time. § Signed integers use two’s complement. § Unsigned integers are not supported by JVM. § Neither are BCD numbers. § JVM supports 16 -bit UNICODE characters rather than 8 -bit ASCII characters. § There is limited support for pointers.

JVM Numeric Data Types

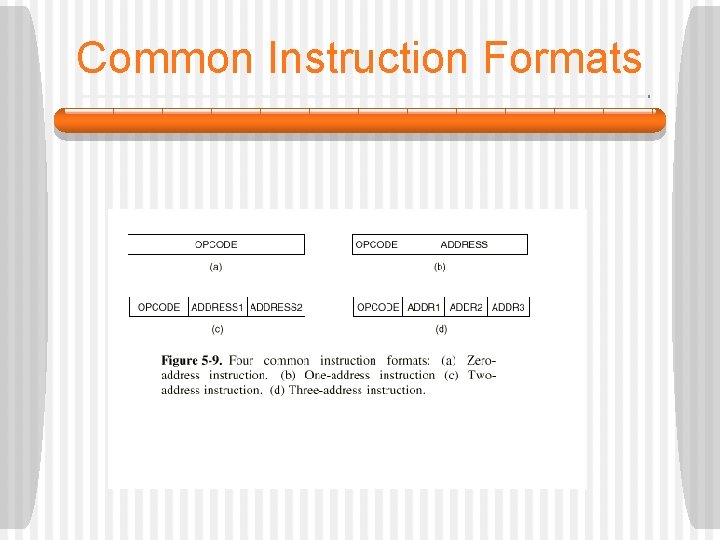

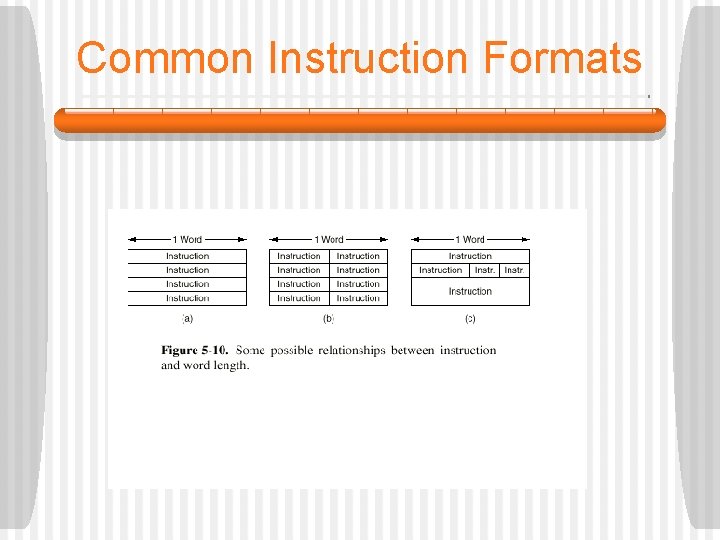

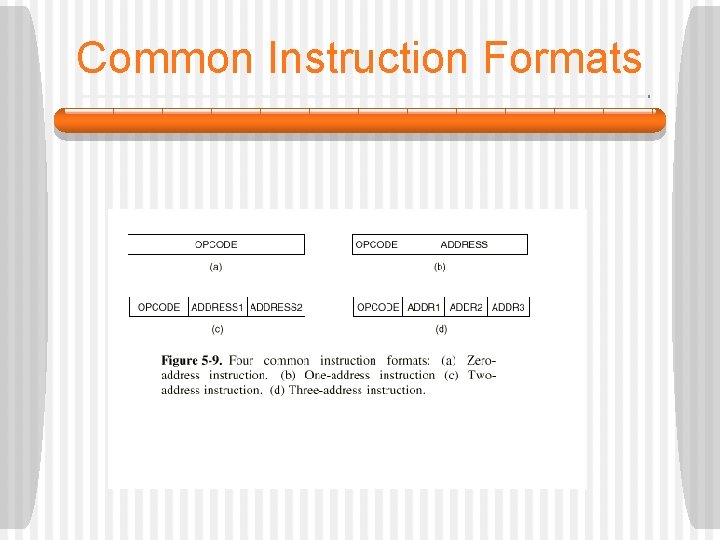

Instruction Formats • An instruction consists of an opcode, usually with some additional information such as where operands come from, and where results go. • The general subject of specifying where the operands are is called addressing. • Several possible formats for level 2 instructions are shown on the next slide.

Common Instruction Formats

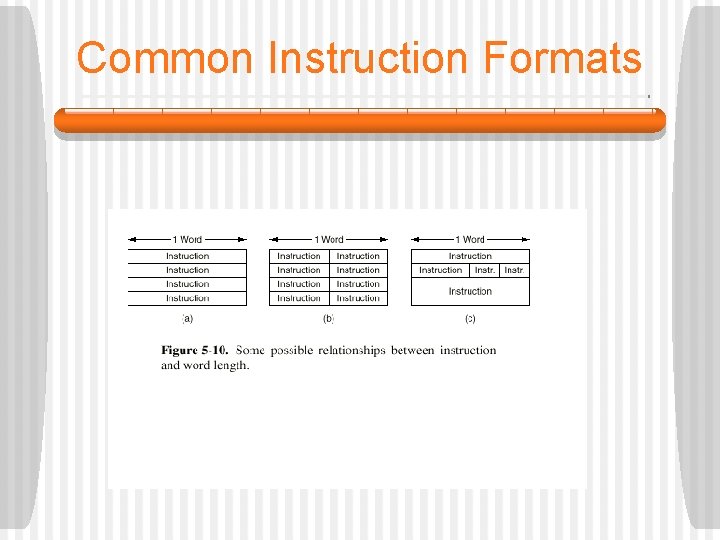

Instruction Formats • On some machines, all instructions have the same length; on others there may be many different lengths. • Instructions may be shorter than, the same length as, or longer than the word length. § Having a single instruction length is simpler and makes decoding easier, but is less efficient.

Common Instruction Formats

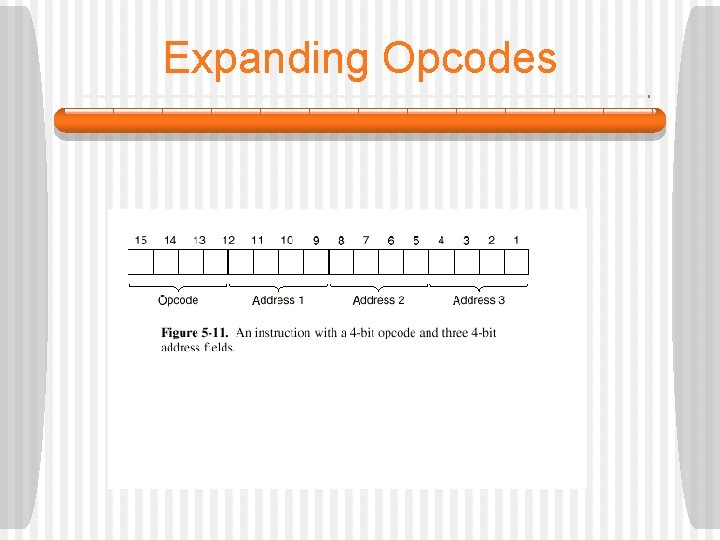

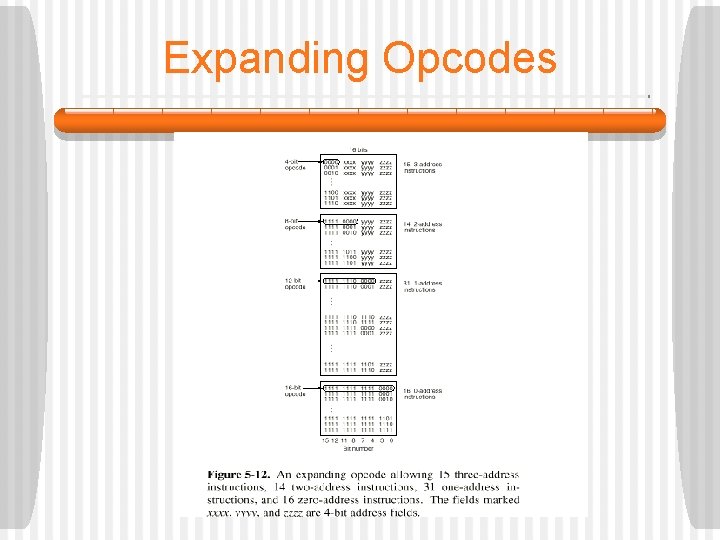

Expanding Opcodes § We will now examine tradeoffs involving both opcodes and addresses. § Consider an (n + k) bit instruction with a k-bit opcode and a single n-bit address. • This instruction allows 2 k different operations and 2 n addressable memory cells. • Alternatively, the same n + k bits could be broken up into a (k - 1) bit opcode and an (n + 1) bit address, meaning half as many instructions and either twice as much addressable memory or the same amount of memory with twice the resolution.

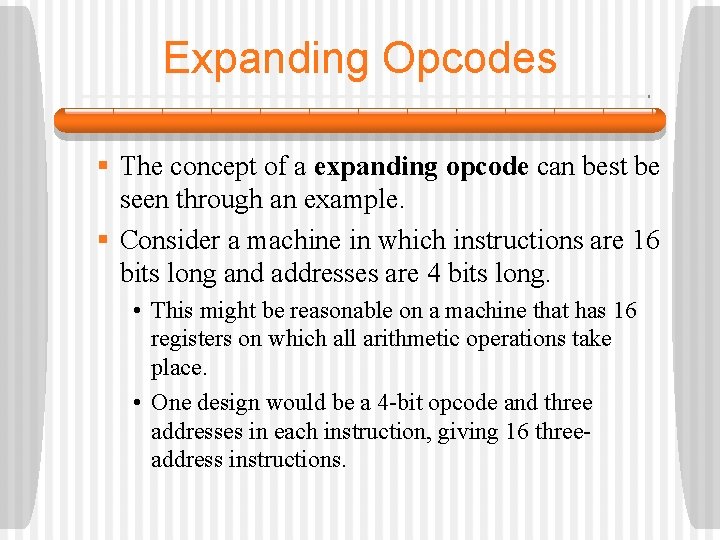

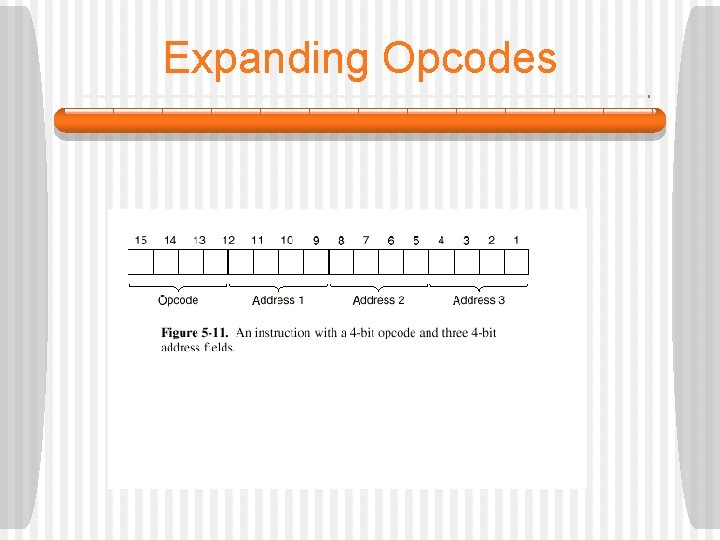

Expanding Opcodes § The concept of a expanding opcode can best be seen through an example. § Consider a machine in which instructions are 16 bits long and addresses are 4 bits long. • This might be reasonable on a machine that has 16 registers on which all arithmetic operations take place. • One design would be a 4 -bit opcode and three addresses in each instruction, giving 16 threeaddress instructions.

Expanding Opcodes

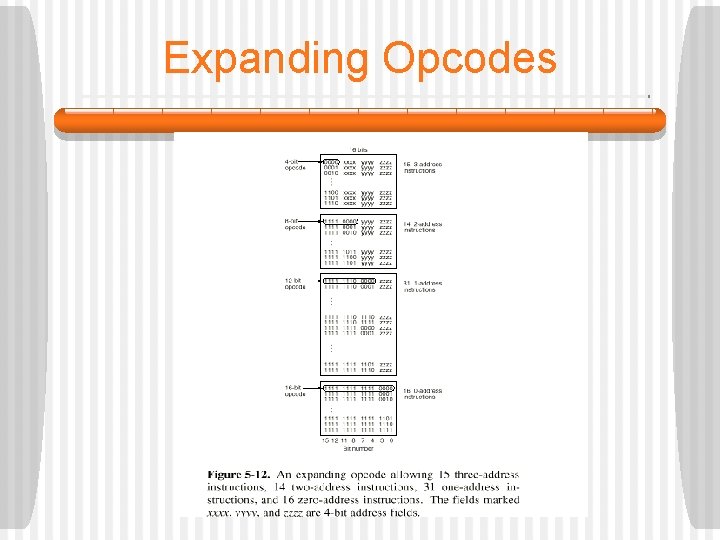

Expanding Opcodes § However, if the designers need 15 three-address instructions, 14 two-address instructions, 31 one-address instructions, and 16 instructions with no address at all, they can use opcodes 0 to 14 as three-address instructions but interpret opcode 15 differently. • Opcode 15 means that the opcode is contained in bits 8 to 15 instead of 12 to 15.

Expanding Opcodes

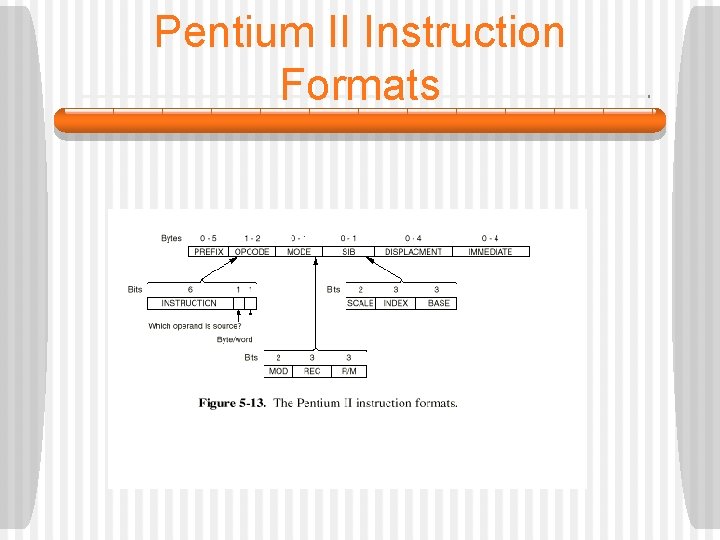

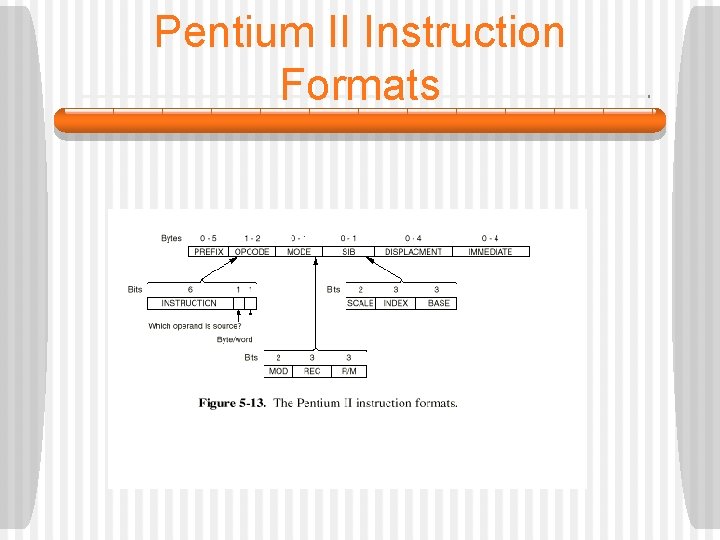

Pentium II Instruction Formats

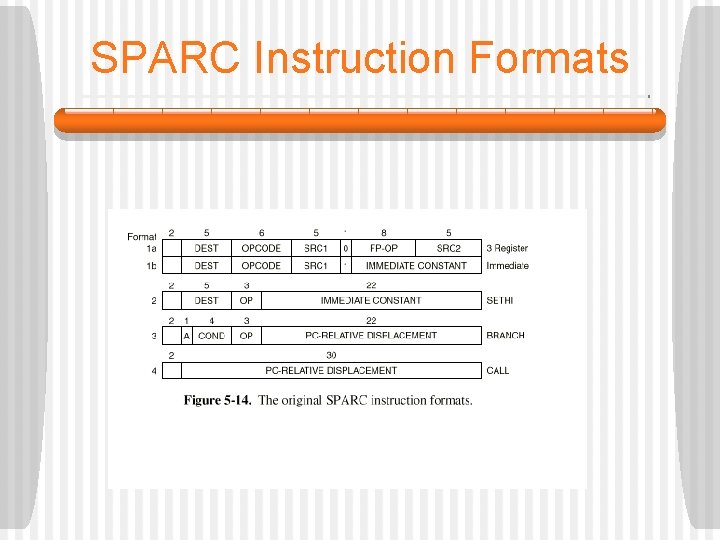

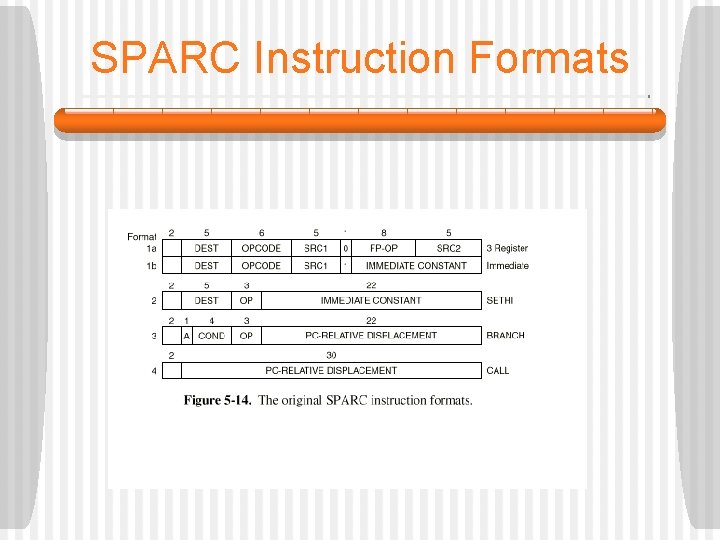

SPARC Instruction Formats

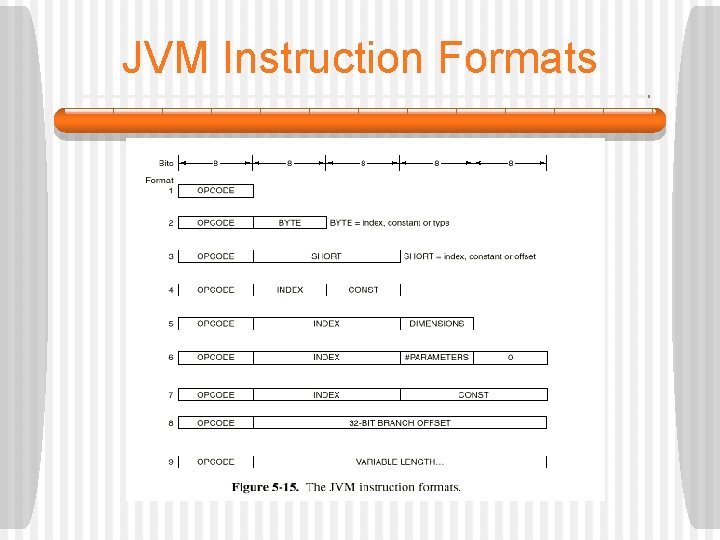

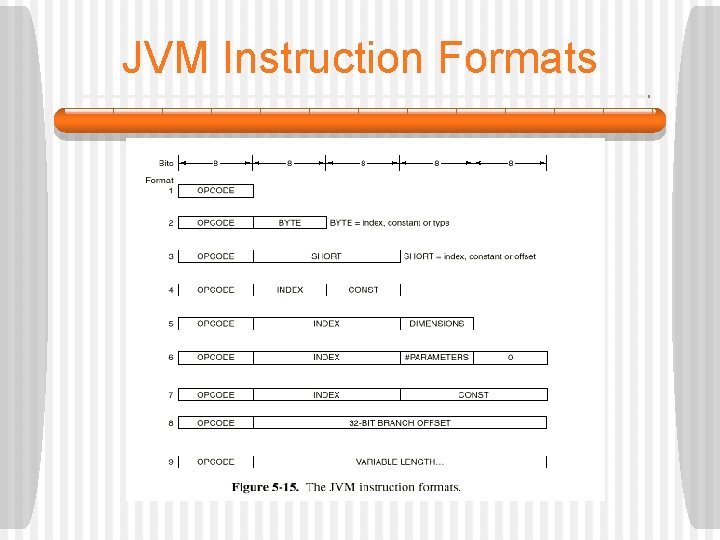

JVM Instruction Formats