The HCS 12MC 9 S 12 Microcontroller Chapter

- Slides: 25

The HCS 12/MC 9 S 12 Microcontroller Chapter 11: Inter-Integrated Circuit (I 2 C) Interface Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -1

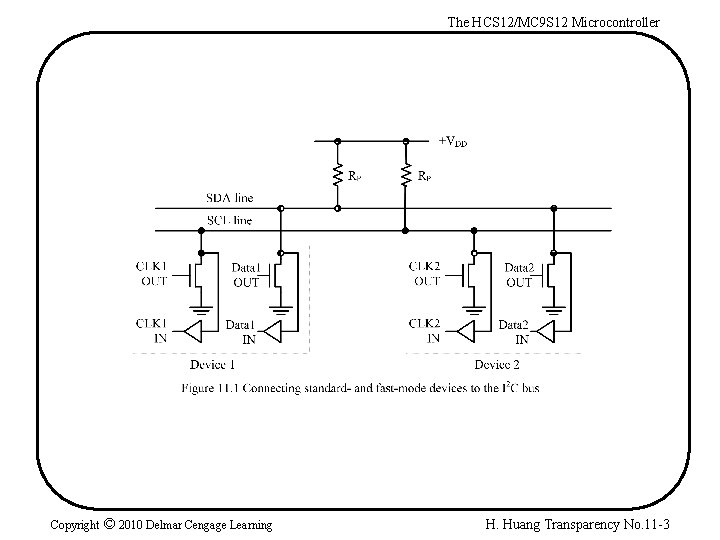

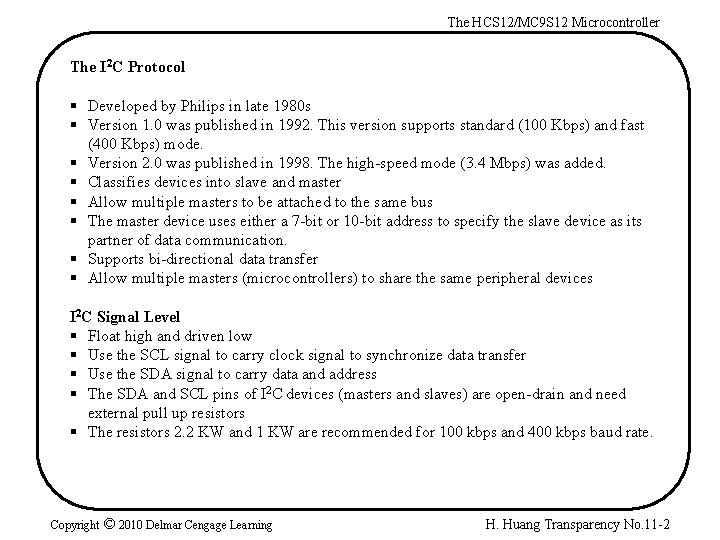

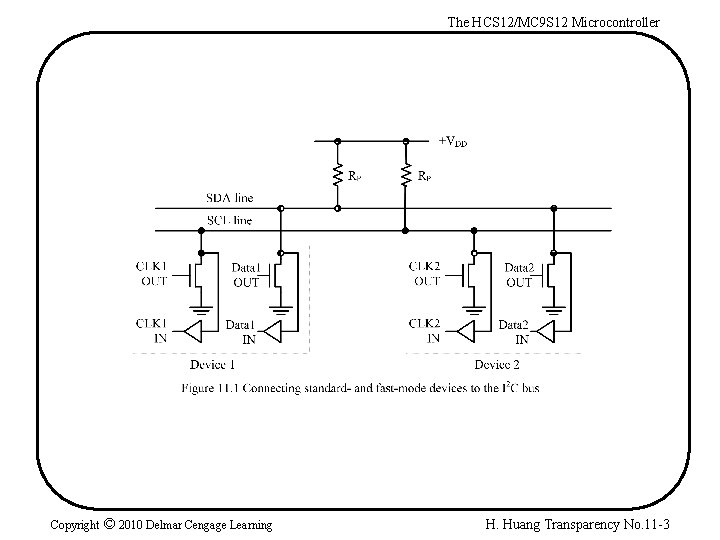

The HCS 12/MC 9 S 12 Microcontroller The I 2 C Protocol § Developed by Philips in late 1980 s § Version 1. 0 was published in 1992. This version supports standard (100 Kbps) and fast (400 Kbps) mode. § Version 2. 0 was published in 1998. The high-speed mode (3. 4 Mbps) was added. § Classifies devices into slave and master § Allow multiple masters to be attached to the same bus § The master device uses either a 7 -bit or 10 -bit address to specify the slave device as its partner of data communication. § Supports bi-directional data transfer § Allow multiple masters (microcontrollers) to share the same peripheral devices I 2 C Signal Level § Float high and driven low § Use the SCL signal to carry clock signal to synchronize data transfer § Use the SDA signal to carry data and address § The SDA and SCL pins of I 2 C devices (masters and slaves) are open-drain and need external pull up resistors § The resistors 2. 2 KW and 1 KW are recommended for 100 kbps and 400 kbps baud rate. Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -2

The HCS 12/MC 9 S 12 Microcontroller Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -3

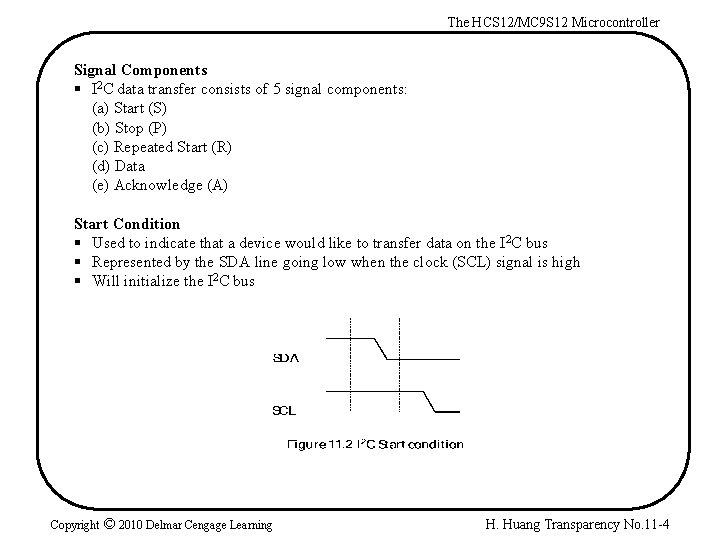

The HCS 12/MC 9 S 12 Microcontroller Signal Components § I 2 C data transfer consists of 5 signal components: (a) Start (S) (b) Stop (P) (c) Repeated Start (R) (d) Data (e) Acknowledge (A) Start Condition § Used to indicate that a device would like to transfer data on the I 2 C bus § Represented by the SDA line going low when the clock (SCL) signal is high § Will initialize the I 2 C bus Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -4

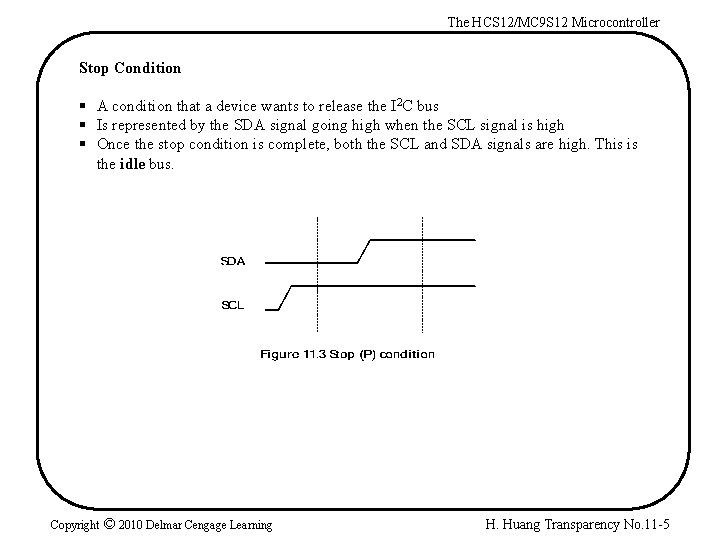

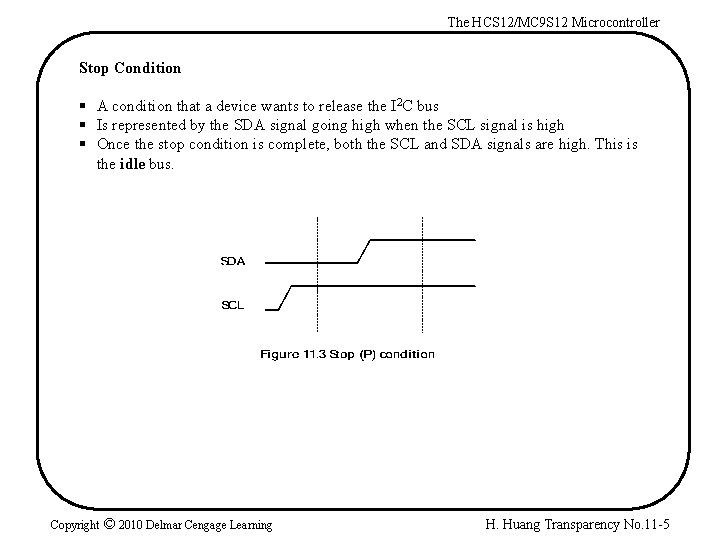

The HCS 12/MC 9 S 12 Microcontroller Stop Condition § A condition that a device wants to release the I 2 C bus § Is represented by the SDA signal going high when the SCL signal is high § Once the stop condition is complete, both the SCL and SDA signals are high. This is the idle bus. Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -5

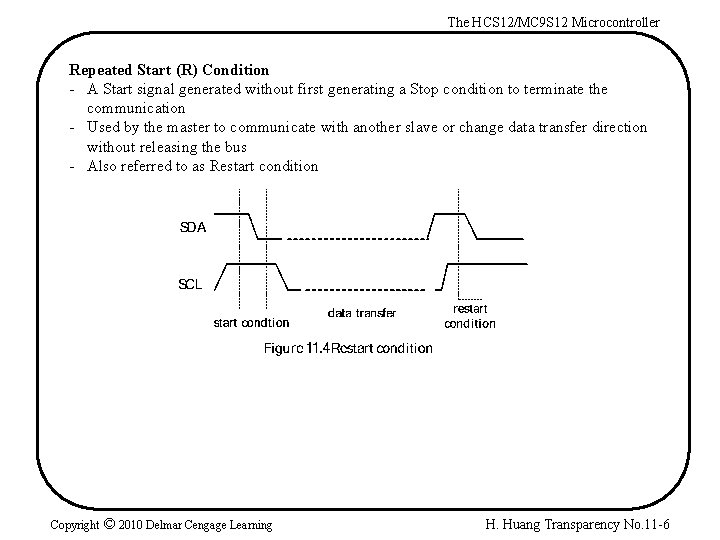

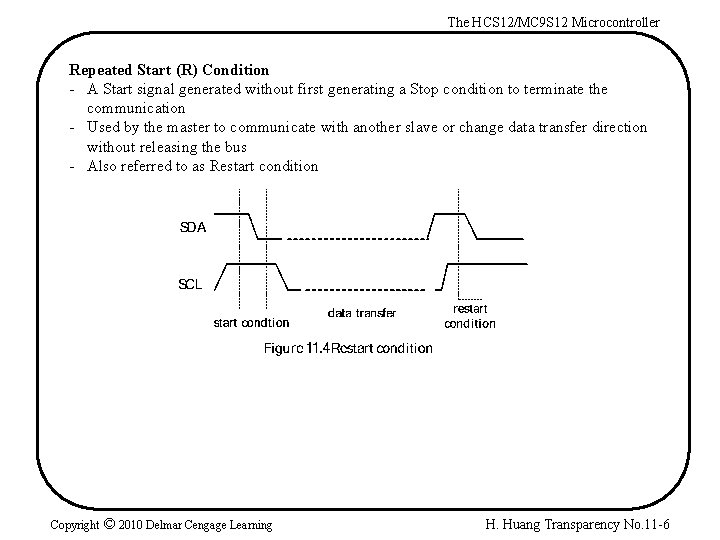

The HCS 12/MC 9 S 12 Microcontroller Repeated Start (R) Condition - A Start signal generated without first generating a Stop condition to terminate the communication - Used by the master to communicate with another slave or change data transfer direction without releasing the bus - Also referred to as Restart condition Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -6

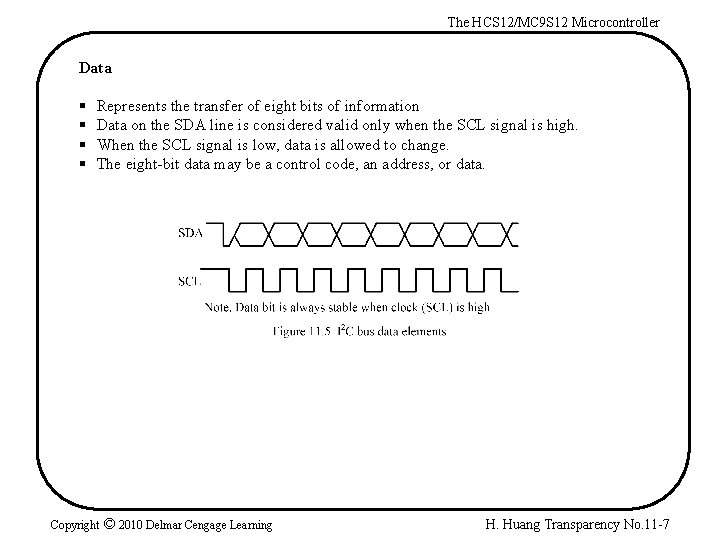

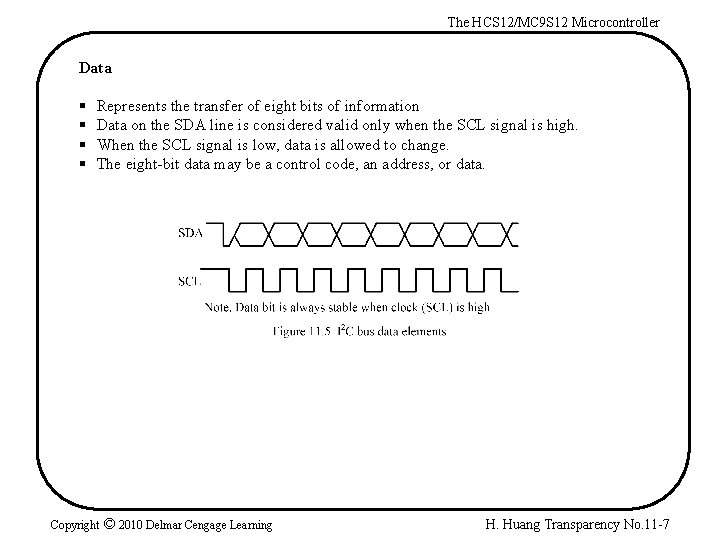

The HCS 12/MC 9 S 12 Microcontroller Data § § Represents the transfer of eight bits of information Data on the SDA line is considered valid only when the SCL signal is high. When the SCL signal is low, data is allowed to change. The eight-bit data may be a control code, an address, or data. Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -7

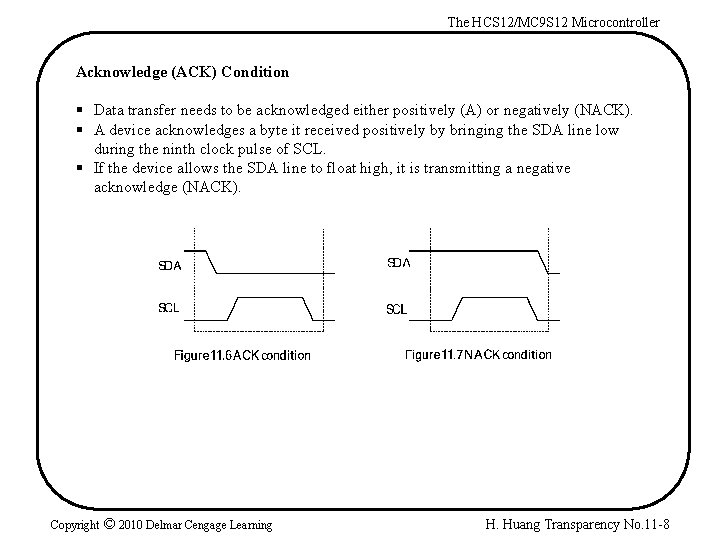

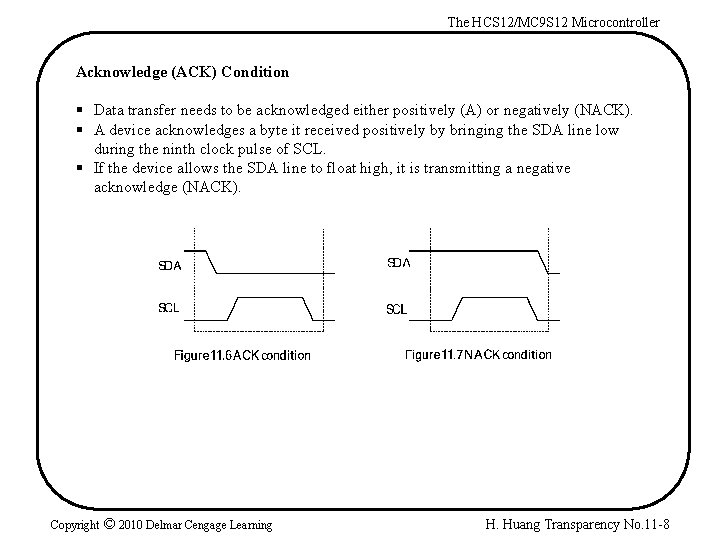

The HCS 12/MC 9 S 12 Microcontroller Acknowledge (ACK) Condition § Data transfer needs to be acknowledged either positively (A) or negatively (NACK). § A device acknowledges a byte it received positively by bringing the SDA line low during the ninth clock pulse of SCL. § If the device allows the SDA line to float high, it is transmitting a negative acknowledge (NACK). Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -8

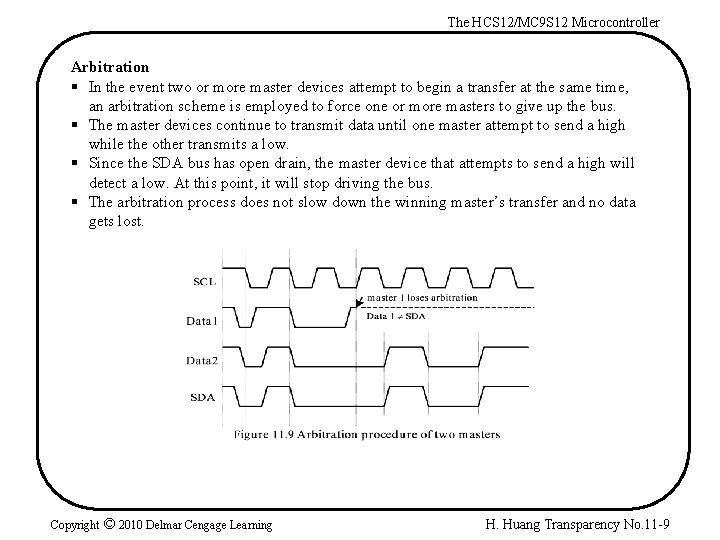

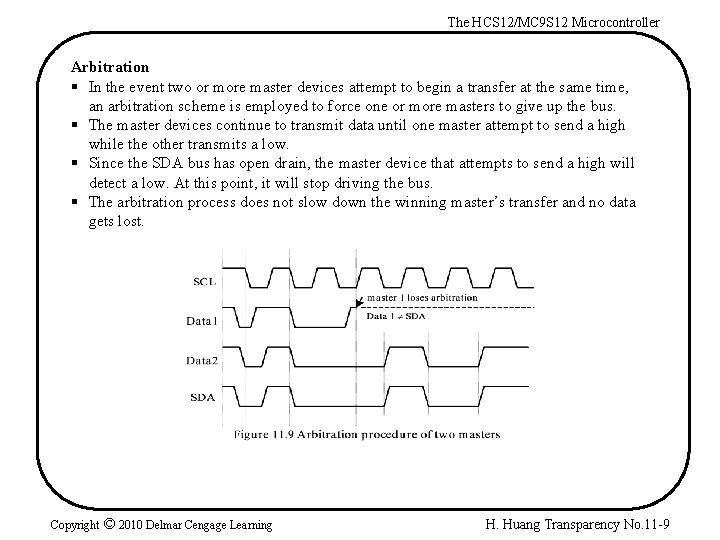

The HCS 12/MC 9 S 12 Microcontroller Arbitration § In the event two or more master devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one or more masters to give up the bus. § The master devices continue to transmit data until one master attempt to send a high while the other transmits a low. § Since the SDA bus has open drain, the master device that attempts to send a high will detect a low. At this point, it will stop driving the bus. § The arbitration process does not slow down the winning master’s transfer and no data gets lost. Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -9

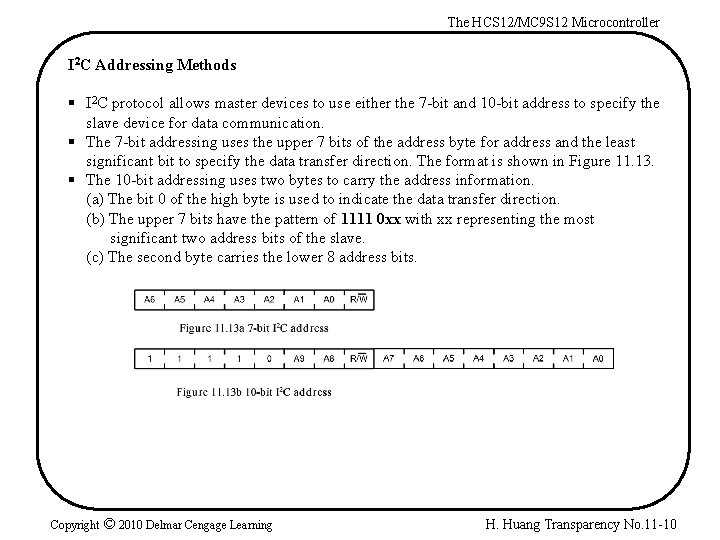

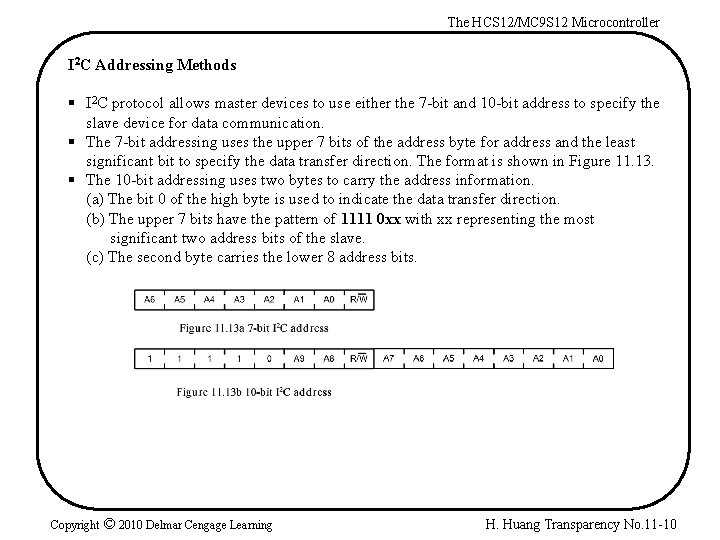

The HCS 12/MC 9 S 12 Microcontroller I 2 C Addressing Methods § I 2 C protocol allows master devices to use either the 7 -bit and 10 -bit address to specify the slave device for data communication. § The 7 -bit addressing uses the upper 7 bits of the address byte for address and the least significant bit to specify the data transfer direction. The format is shown in Figure 11. 13. § The 10 -bit addressing uses two bytes to carry the address information. (a) The bit 0 of the high byte is used to indicate the data transfer direction. (b) The upper 7 bits have the pattern of 1111 0 xx with xx representing the most significant two address bits of the slave. (c) The second byte carries the lower 8 address bits. Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -10

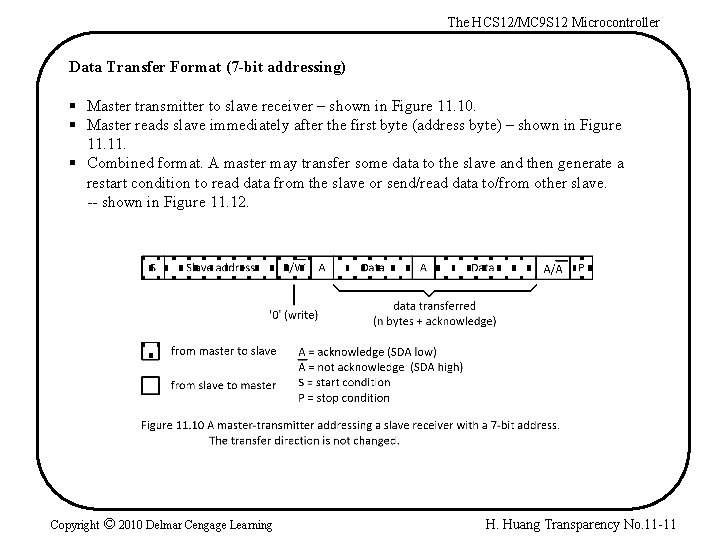

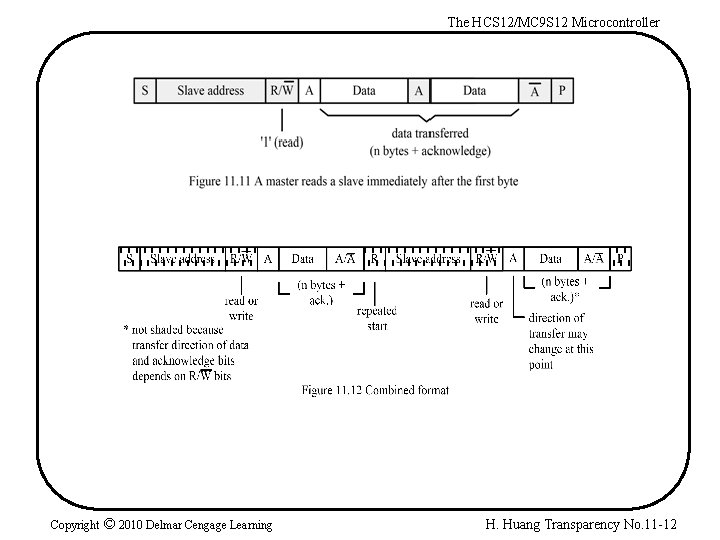

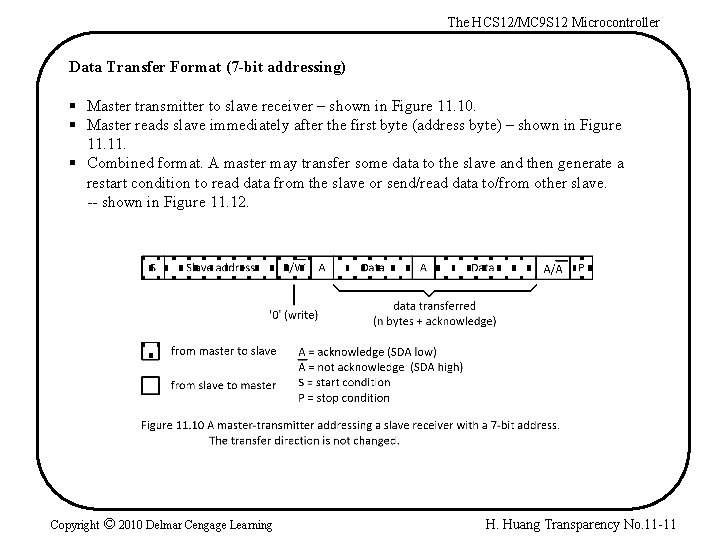

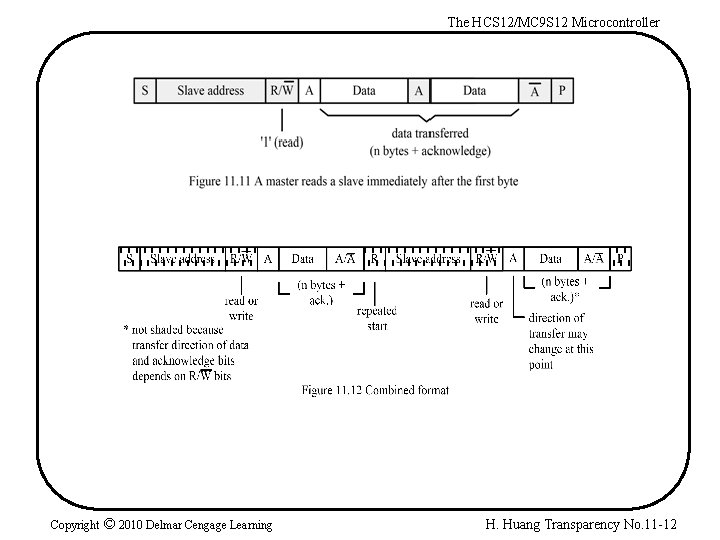

The HCS 12/MC 9 S 12 Microcontroller Data Transfer Format (7 -bit addressing) § Master transmitter to slave receiver – shown in Figure 11. 10. § Master reads slave immediately after the first byte (address byte) – shown in Figure 11. § Combined format. A master may transfer some data to the slave and then generate a restart condition to read data from the slave or send/read data to/from other slave. -- shown in Figure 11. 12. Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -11

The HCS 12/MC 9 S 12 Microcontroller Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -12

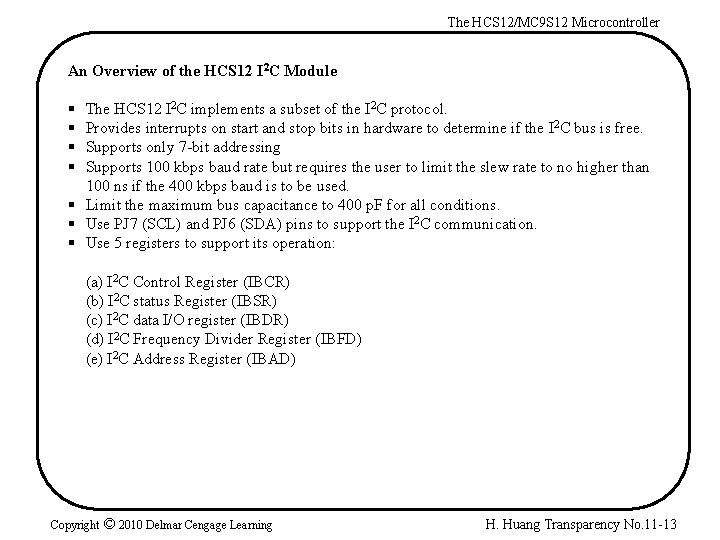

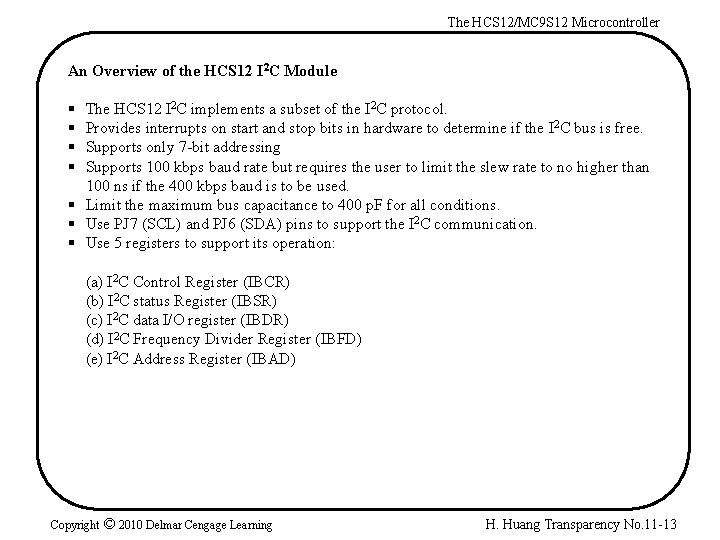

The HCS 12/MC 9 S 12 Microcontroller An Overview of the HCS 12 I 2 C Module § § The HCS 12 I 2 C implements a subset of the I 2 C protocol. Provides interrupts on start and stop bits in hardware to determine if the I 2 C bus is free. Supports only 7 -bit addressing Supports 100 kbps baud rate but requires the user to limit the slew rate to no higher than 100 ns if the 400 kbps baud is to be used. § Limit the maximum bus capacitance to 400 p. F for all conditions. § Use PJ 7 (SCL) and PJ 6 (SDA) pins to support the I 2 C communication. § Use 5 registers to support its operation: (a) I 2 C Control Register (IBCR) (b) I 2 C status Register (IBSR) (c) I 2 C data I/O register (IBDR) (d) I 2 C Frequency Divider Register (IBFD) (e) I 2 C Address Register (IBAD) Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -13

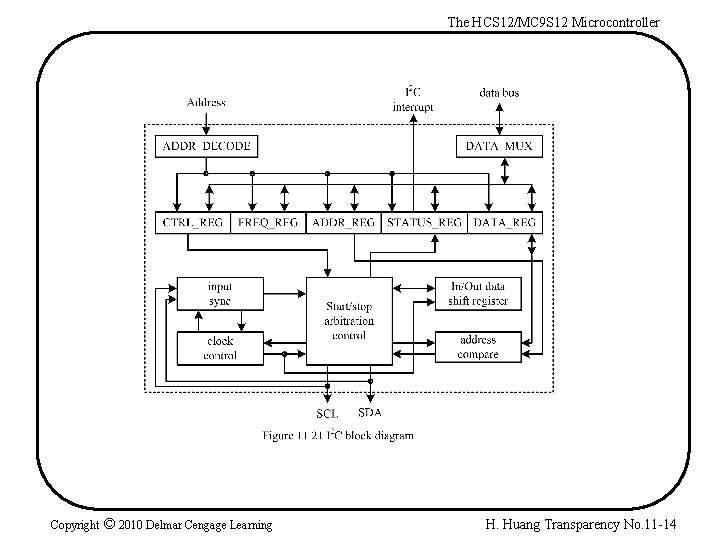

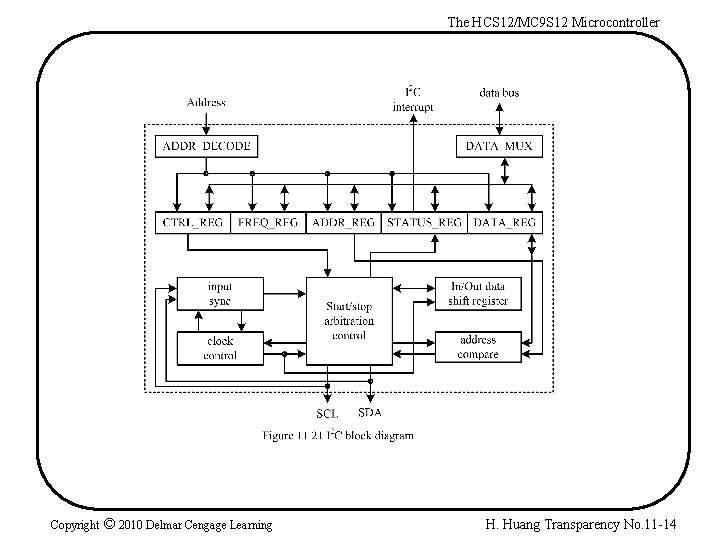

The HCS 12/MC 9 S 12 Microcontroller Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -14

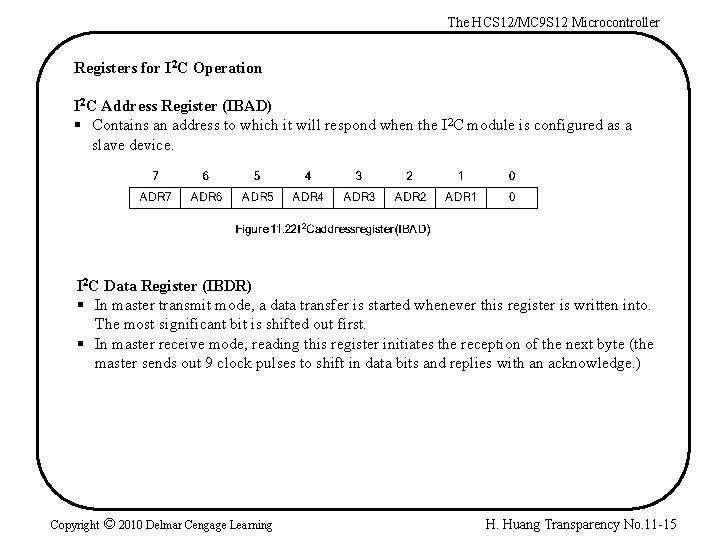

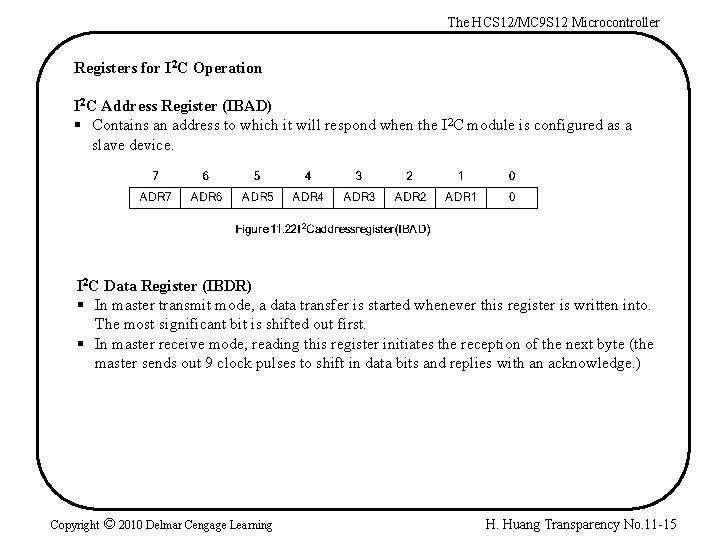

The HCS 12/MC 9 S 12 Microcontroller Registers for I 2 C Operation I 2 C Address Register (IBAD) § Contains an address to which it will respond when the I 2 C module is configured as a slave device. I 2 C Data Register (IBDR) § In master transmit mode, a data transfer is started whenever this register is written into. The most significant bit is shifted out first. § In master receive mode, reading this register initiates the reception of the next byte (the master sends out 9 clock pulses to shift in data bits and replies with an acknowledge. ) Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -15

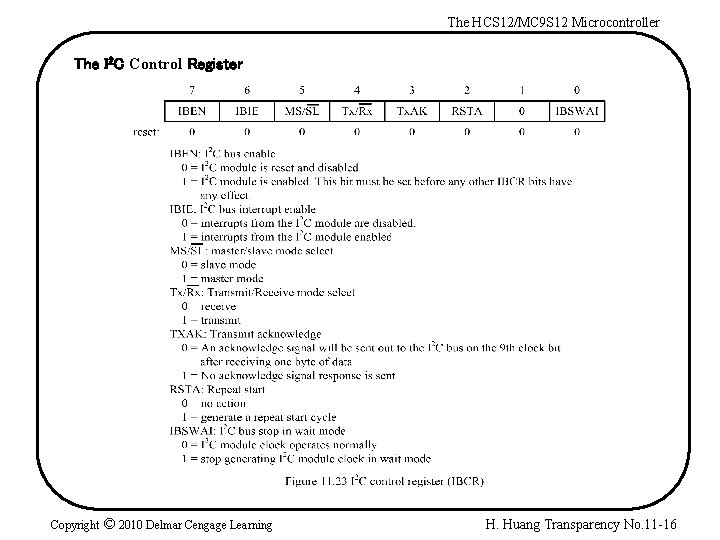

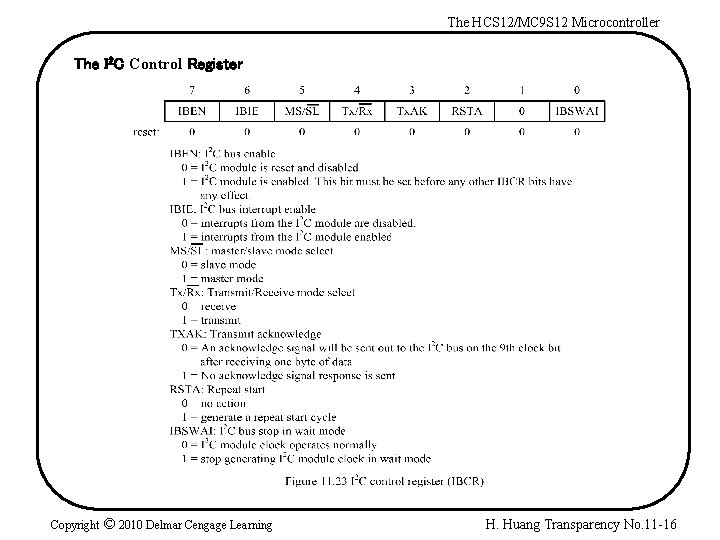

The HCS 12/MC 9 S 12 Microcontroller The I 2 C Control Register Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -16

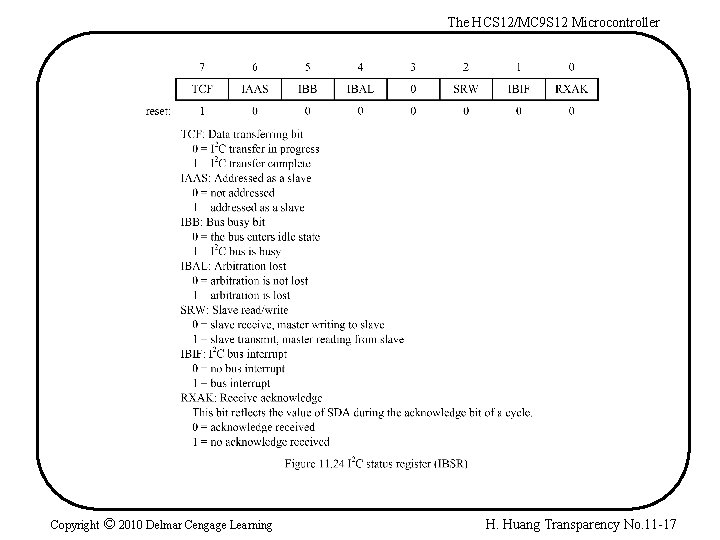

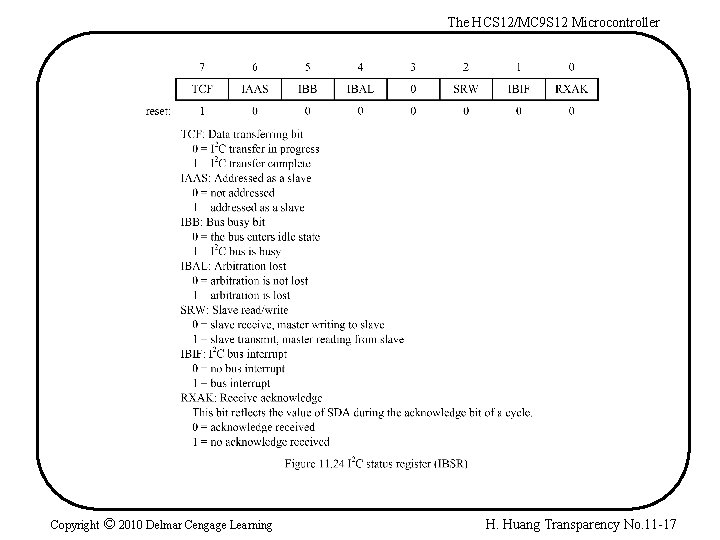

The HCS 12/MC 9 S 12 Microcontroller Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -17

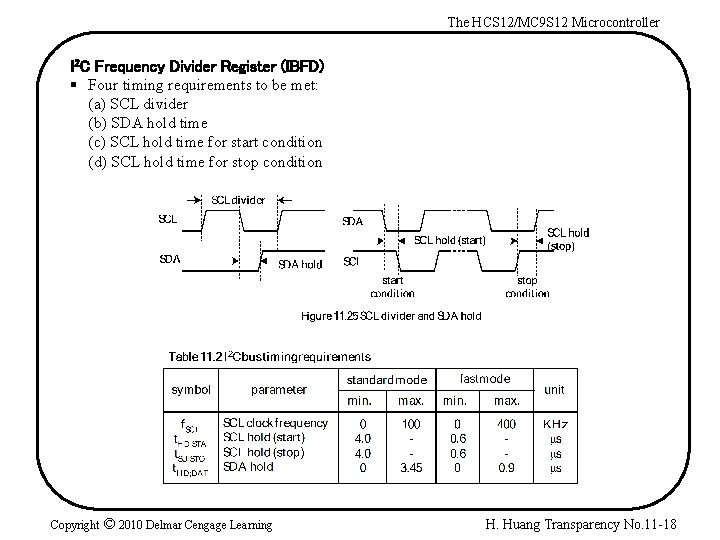

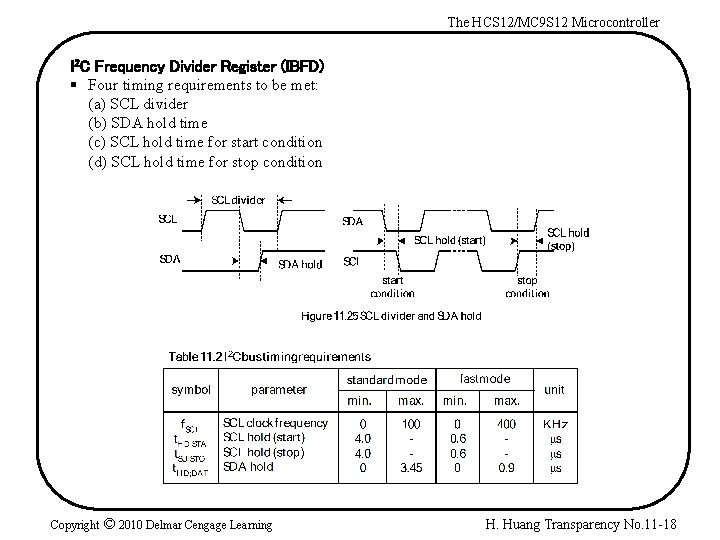

The HCS 12/MC 9 S 12 Microcontroller I 2 C Frequency Divider Register (IBFD) § Four timing requirements to be met: (a) SCL divider (b) SDA hold time (c) SCL hold time for start condition (d) SCL hold time for stop condition Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -18

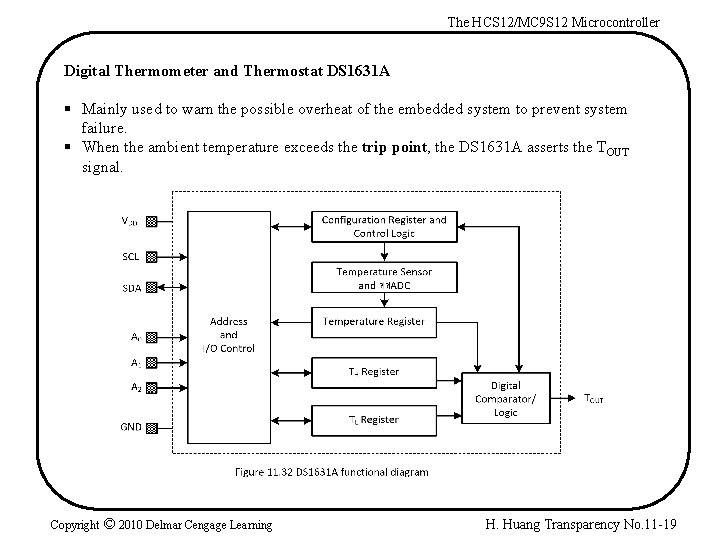

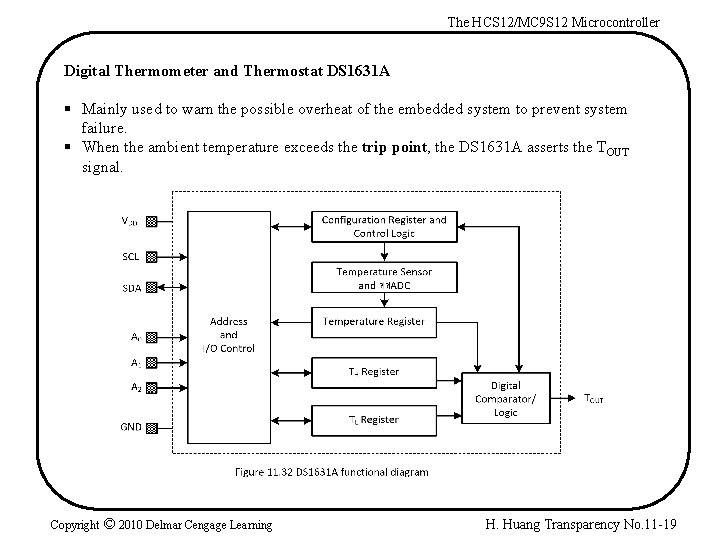

The HCS 12/MC 9 S 12 Microcontroller Digital Thermometer and Thermostat DS 1631 A § Mainly used to warn the possible overheat of the embedded system to prevent system failure. § When the ambient temperature exceeds the trip point, the DS 1631 A asserts the TOUT signal. Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -19

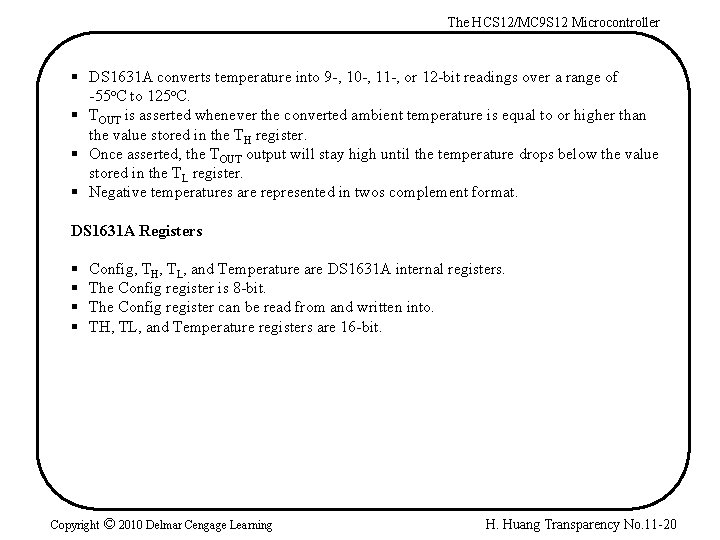

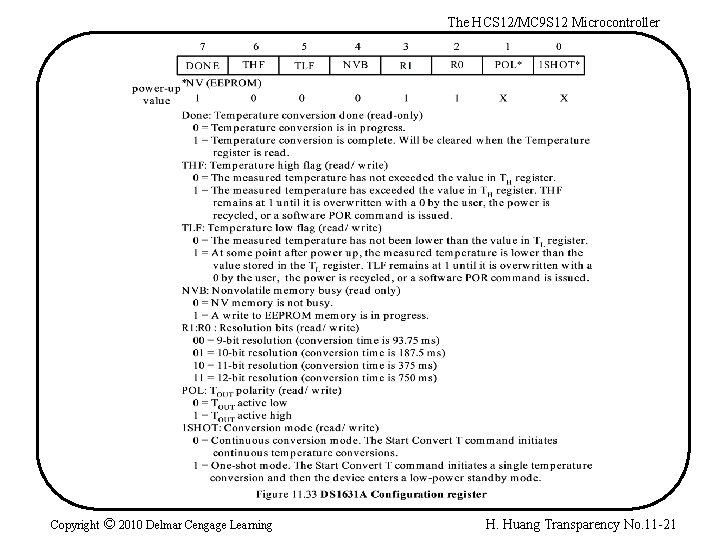

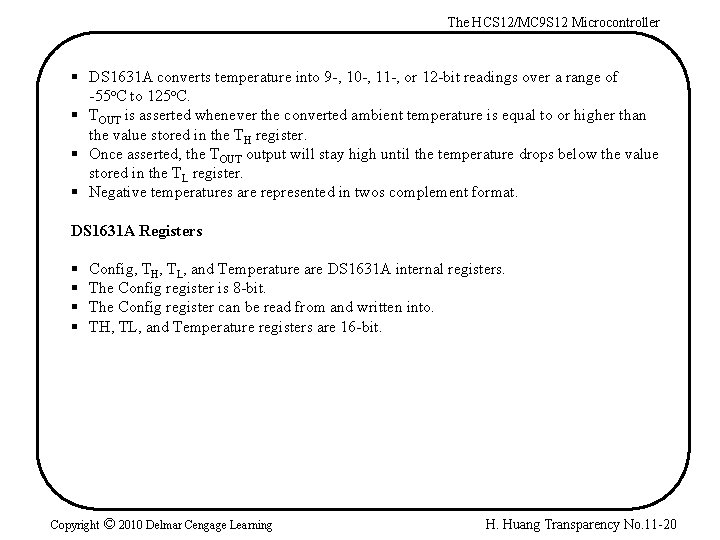

The HCS 12/MC 9 S 12 Microcontroller § DS 1631 A converts temperature into 9 -, 10 -, 11 -, or 12 -bit readings over a range of -55 o. C to 125 o. C. § TOUT is asserted whenever the converted ambient temperature is equal to or higher than the value stored in the TH register. § Once asserted, the TOUT output will stay high until the temperature drops below the value stored in the TL register. § Negative temperatures are represented in twos complement format. DS 1631 A Registers § § Config, TH, TL, and Temperature are DS 1631 A internal registers. The Config register is 8 -bit. The Config register can be read from and written into. TH, TL, and Temperature registers are 16 -bit. Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -20

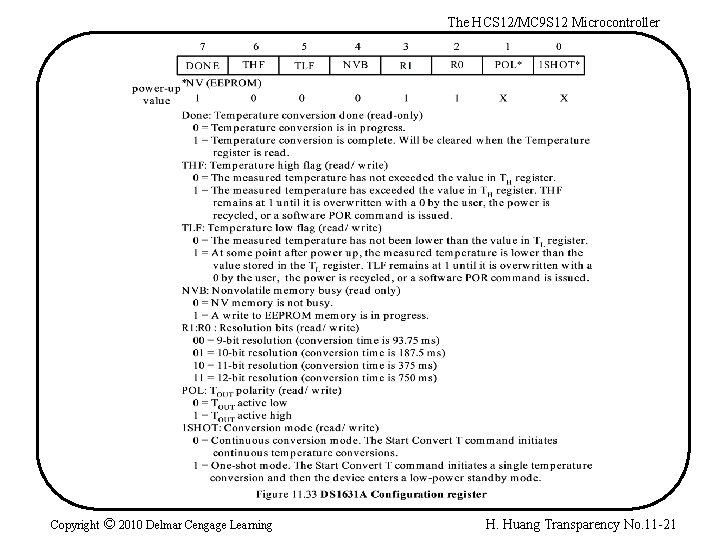

The HCS 12/MC 9 S 12 Microcontroller Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -21

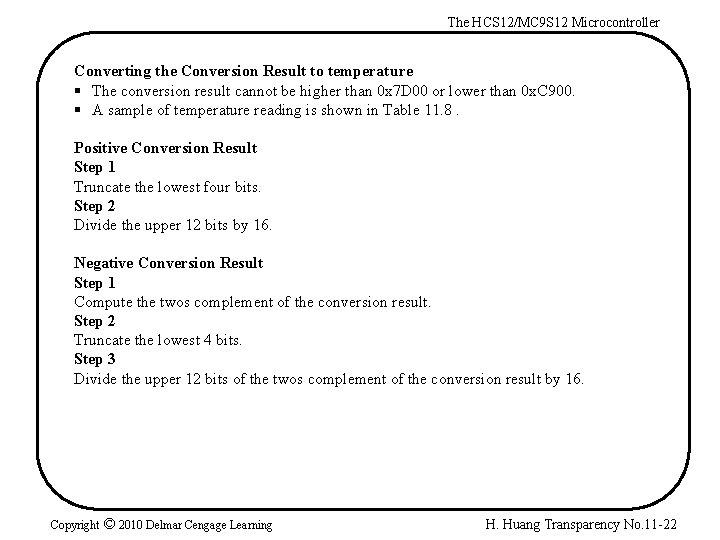

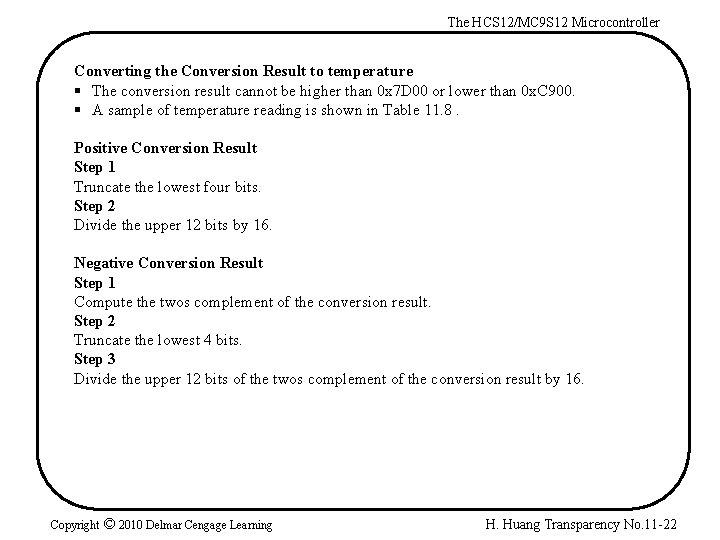

The HCS 12/MC 9 S 12 Microcontroller Converting the Conversion Result to temperature § The conversion result cannot be higher than 0 x 7 D 00 or lower than 0 x. C 900. § A sample of temperature reading is shown in Table 11. 8. Positive Conversion Result Step 1 Truncate the lowest four bits. Step 2 Divide the upper 12 bits by 16. Negative Conversion Result Step 1 Compute the twos complement of the conversion result. Step 2 Truncate the lowest 4 bits. Step 3 Divide the upper 12 bits of the twos complement of the conversion result by 16. Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -22

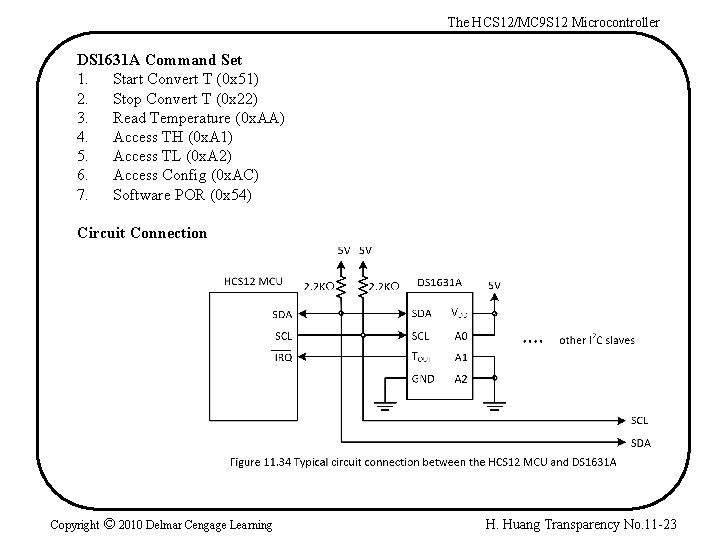

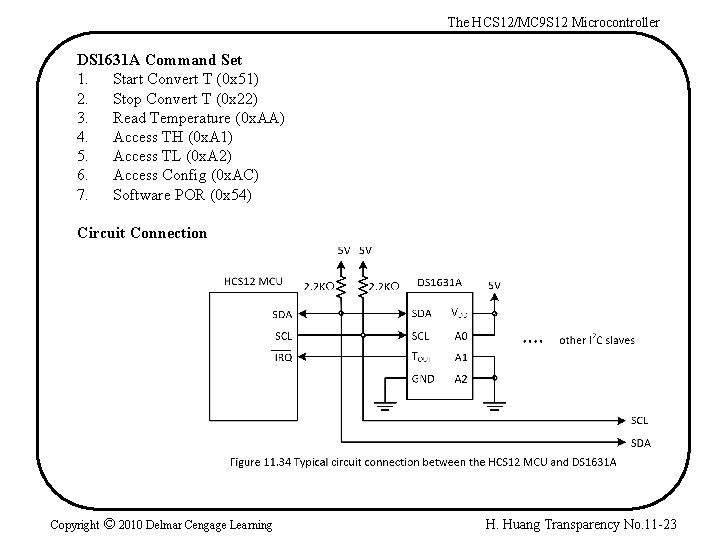

The HCS 12/MC 9 S 12 Microcontroller DS 1631 A Command Set 1. Start Convert T (0 x 51) 2. Stop Convert T (0 x 22) 3. Read Temperature (0 x. AA) 4. Access TH (0 x. A 1) 5. Access TL (0 x. A 2) 6. Access Config (0 x. AC) 7. Software POR (0 x 54) Circuit Connection Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -23

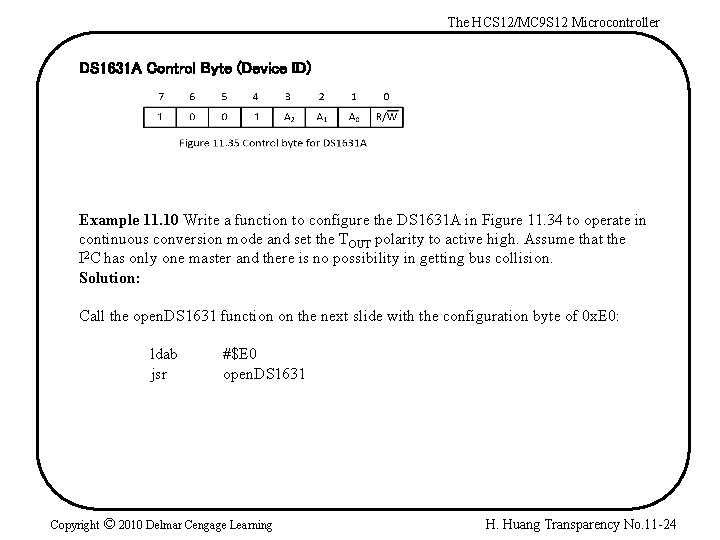

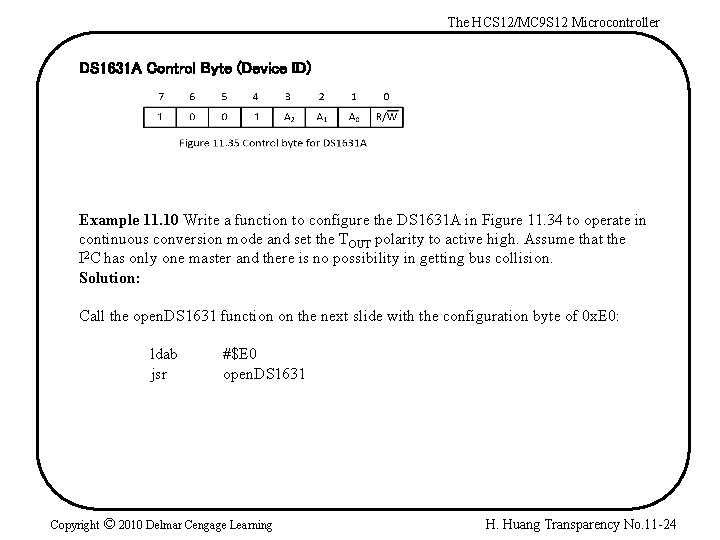

The HCS 12/MC 9 S 12 Microcontroller DS 1631 A Control Byte (Device ID) Example 11. 10 Write a function to configure the DS 1631 A in Figure 11. 34 to operate in continuous conversion mode and set the TOUT polarity to active high. Assume that the I 2 C has only one master and there is no possibility in getting bus collision. Solution: Call the open. DS 1631 function on the next slide with the configuration byte of 0 x. E 0: ldab jsr #$E 0 open. DS 1631 Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -24

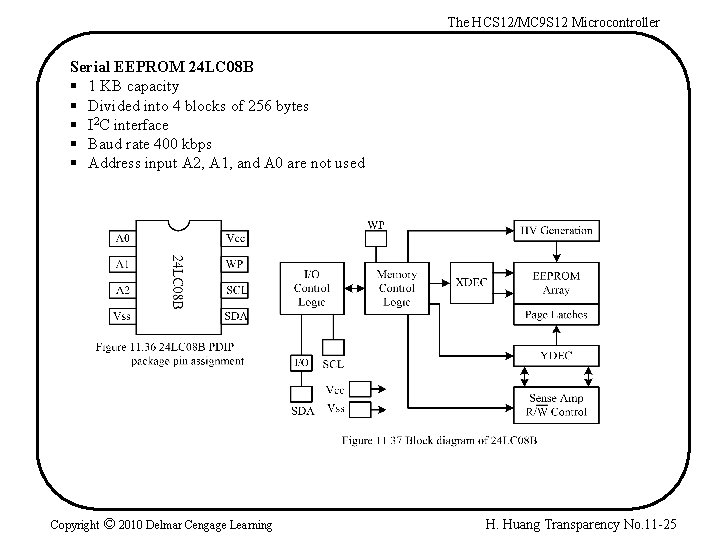

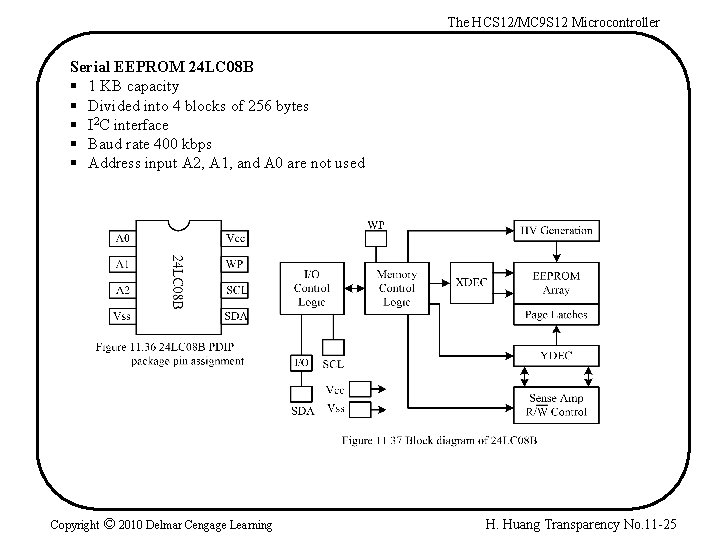

The HCS 12/MC 9 S 12 Microcontroller Serial EEPROM 24 LC 08 B § 1 KB capacity § Divided into 4 blocks of 256 bytes § I 2 C interface § Baud rate 400 kbps § Address input A 2, A 1, and A 0 are not used Copyright © 2010 Delmar Cengage Learning H. Huang Transparency No. 11 -25