The GBT A single link for Timing Trigger

The GBT A single link for Timing, Trigger, Slow Control and DAQ in experiments A. Marchioro CERN/PH-MIC A. M. GBT

Project Participants CERN: PH-MIC & ED & ATE ¢ INFN: Bari, Bologna, Torino ¢ IN 2 P 3: Marseille ¢ 2 A. M. GBT

Background & motivation For the first generation of LHC instrumentation PH -MIC has participated in three projects: l l l TTC GOL CMS Tracker & Ecal Slow Control all using different optical links. The expertise gained in these projects convinced us that a single optical link is possible and actually desirable to simplify systems, reduce costs and streamline maintenance and operation 3 A. M. GBT

Rationale ¢ ¢ ¢ Cost of optical transmission system is largely dominated by the opto components (and their installation) and NOT by the electronic components Cost changes moderately when increasing speed Therefore: increasing design cost of electronic components has small if any impact on overall system cost but can lead to many advantages in terms of: l l l 4 functionality overall cost reduction compatibility with industrial standards simplification of long term maintenance reduction of number of links A. M. GBT

Outline ¢ General Aim of the Project Architecture l Proposed TTC functionality l Some details on proposed Error Correction ¢ Proposal for interface to Slow Control ¢ Progress & Plans ¢ 5 A. M. GBT

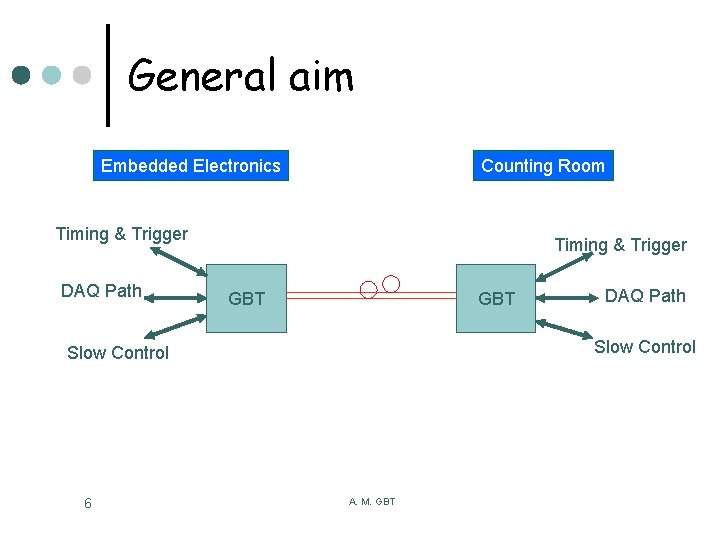

General aim Embedded Electronics Counting Room Timing & Trigger DAQ Path Timing & Trigger GBT Slow Control 6 DAQ Path A. M. GBT

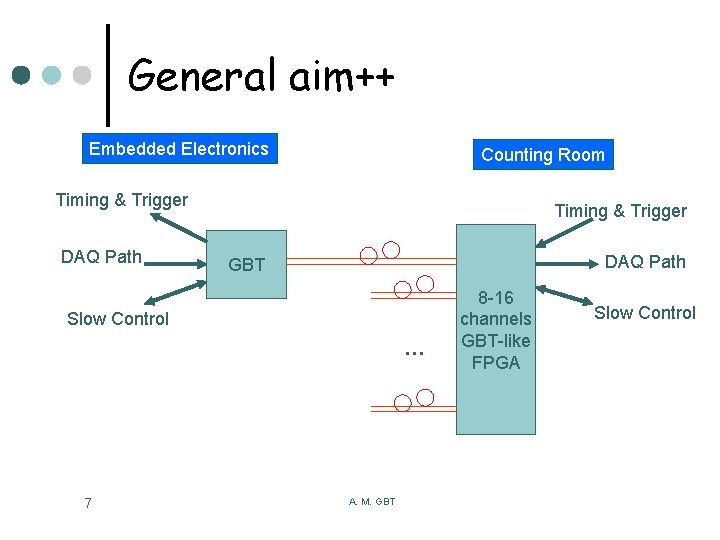

General aim++ Embedded Electronics Counting Room Timing & Trigger DAQ Path GBT Slow Control … 7 A. M. GBT 8 -16 channels GBT-like FPGA Slow Control

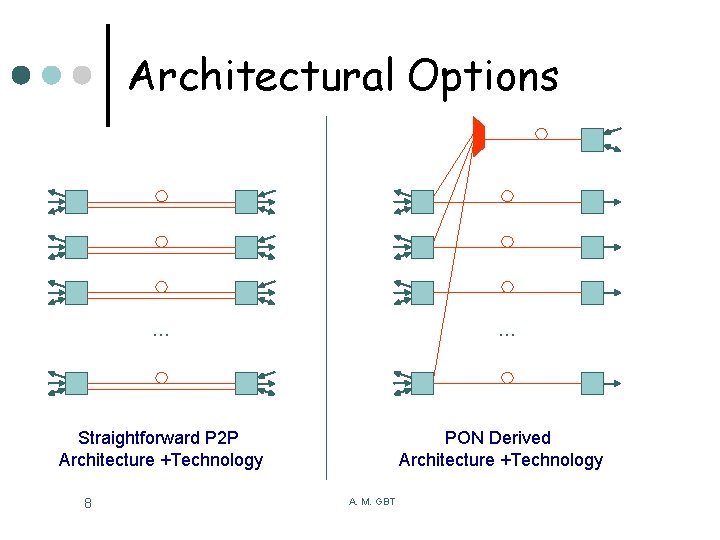

Architectural Options … … Straightforward P 2 P Architecture +Technology 8 PON Derived Architecture +Technology A. M. GBT

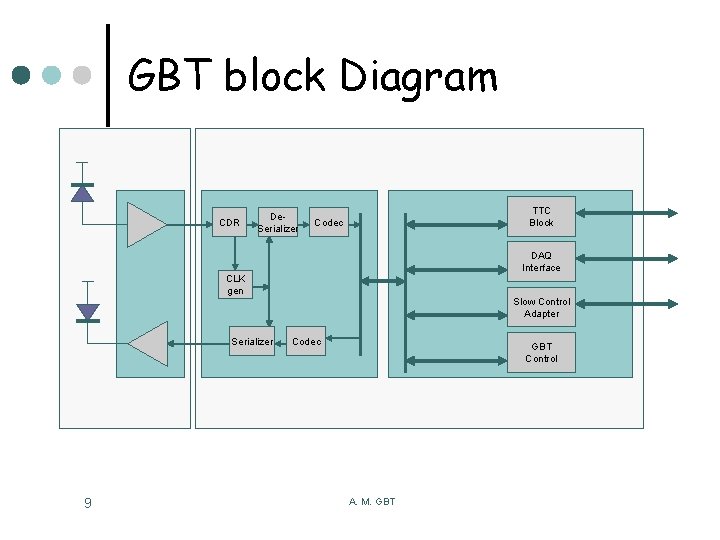

GBT block Diagram CDR De. Serializer TTC Block Codec DAQ Interface CLK gen Serializer 9 Slow Control Adapter Codec GBT Control A. M. GBT

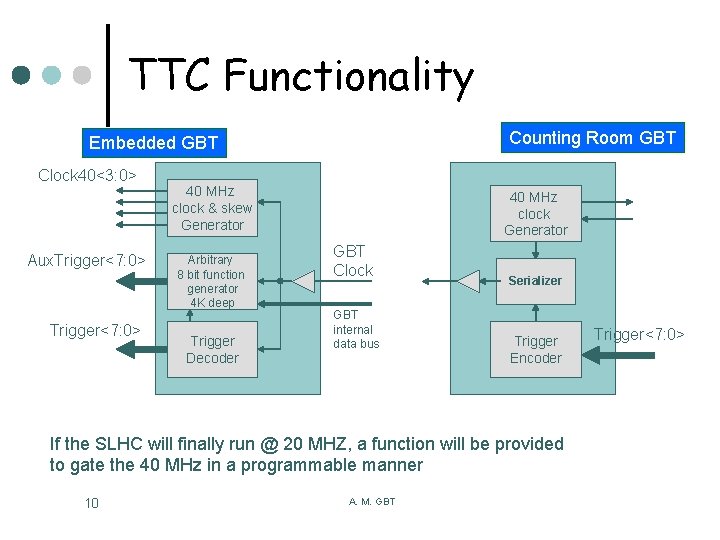

TTC Functionality Counting Room GBT Embedded GBT Clock 40<3: 0> Aux. Trigger<7: 0> 40 MHz clock & skew Generator Arbitrary 8 bit function generator 4 K deep Trigger Decoder 40 MHz clock Generator GBT Clock GBT internal data bus Serializer Trigger Encoder If the SLHC will finally run @ 20 MHZ, a function will be provided to gate the 40 MHz in a programmable manner 10 A. M. GBT Trigger<7: 0>

Error Correction in GBT A. M. GBT

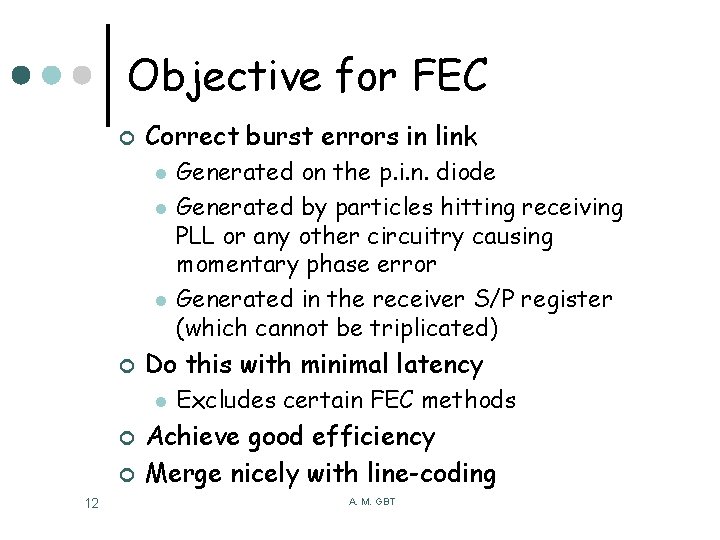

Objective for FEC ¢ Correct burst errors in link l l l ¢ Do this with minimal latency l ¢ ¢ 12 Generated on the p. i. n. diode Generated by particles hitting receiving PLL or any other circuitry causing momentary phase error Generated in the receiver S/P register (which cannot be triplicated) Excludes certain FEC methods Achieve good efficiency Merge nicely with line-coding A. M. GBT

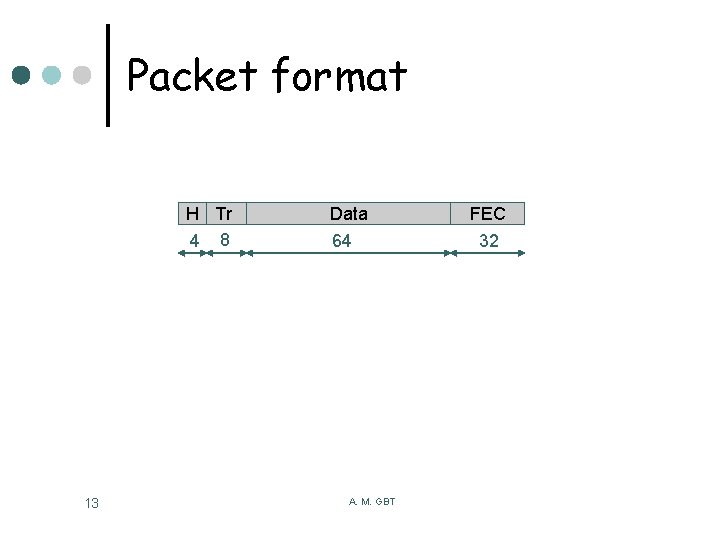

Packet format H Tr 4 8 13 Data 64 A. M. GBT FEC 32

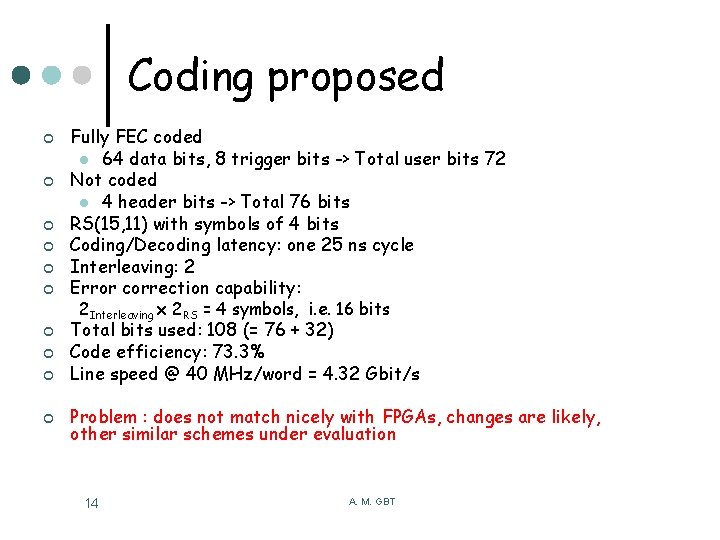

Coding proposed ¢ ¢ ¢ ¢ ¢ Fully FEC coded l 64 data bits, 8 trigger bits -> Total user bits 72 Not coded l 4 header bits -> Total 76 bits RS(15, 11) with symbols of 4 bits Coding/Decoding latency: one 25 ns cycle Interleaving: 2 Error correction capability: 2 Interleaving x 2 RS = 4 symbols, i. e. 16 bits Total bits used: 108 (= 76 + 32) Code efficiency: 73. 3% Line speed @ 40 MHz/word = 4. 32 Gbit/s Problem : does not match nicely with FPGAs, changes are likely, other similar schemes under evaluation 14 A. M. GBT

Interface to Slow Control A. M. GBT

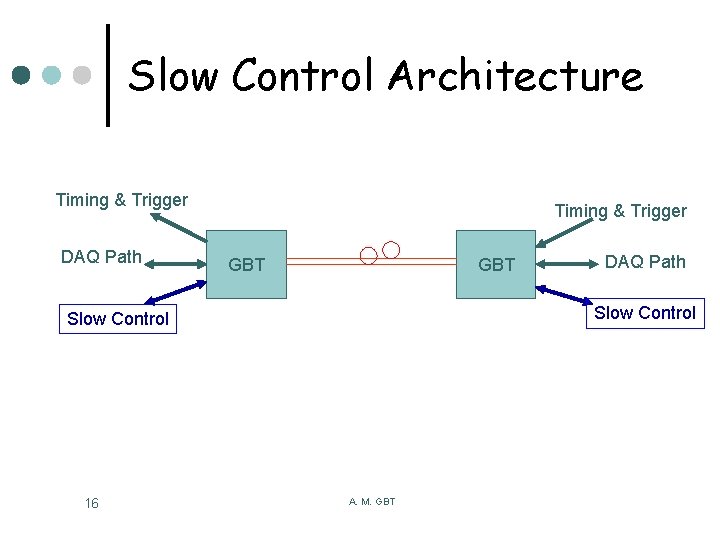

Slow Control Architecture Timing & Trigger DAQ Path Timing & Trigger GBT Slow Control 16 DAQ Path A. M. GBT

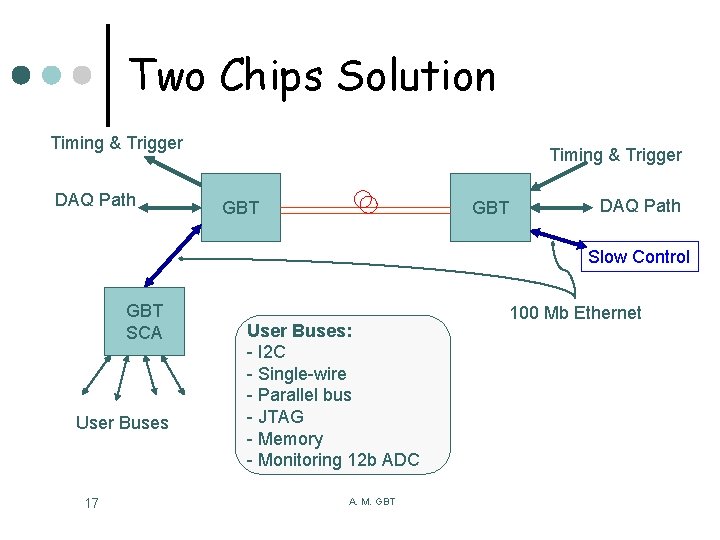

Two Chips Solution Timing & Trigger DAQ Path Timing & Trigger GBT DAQ Path Slow Control GBT SCA User Buses 17 User Buses: - I 2 C - Single-wire - Parallel bus - JTAG - Memory - Monitoring 12 b ADC A. M. GBT 100 Mb Ethernet

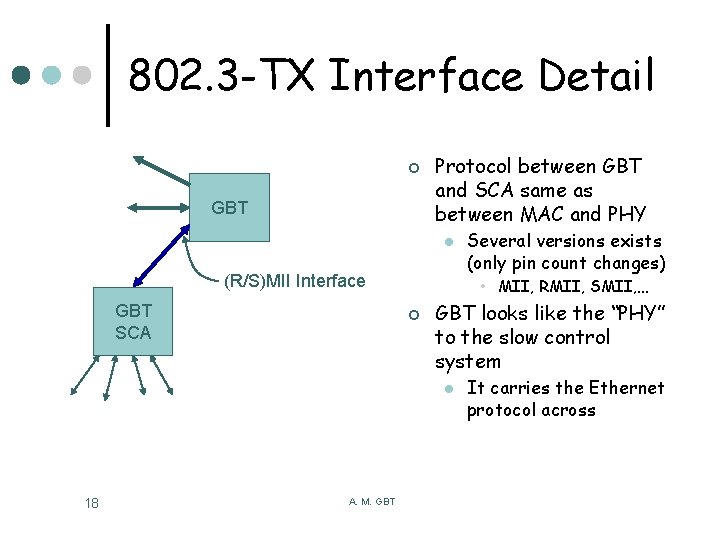

802. 3 -TX Interface Detail ¢ GBT Protocol between GBT and SCA same as between MAC and PHY l (R/S)MII Interface GBT SCA • MII, RMII, SMII, … ¢ GBT looks like the “PHY” to the slow control system l 18 A. M. GBT Several versions exists (only pin count changes) It carries the Ethernet protocol across

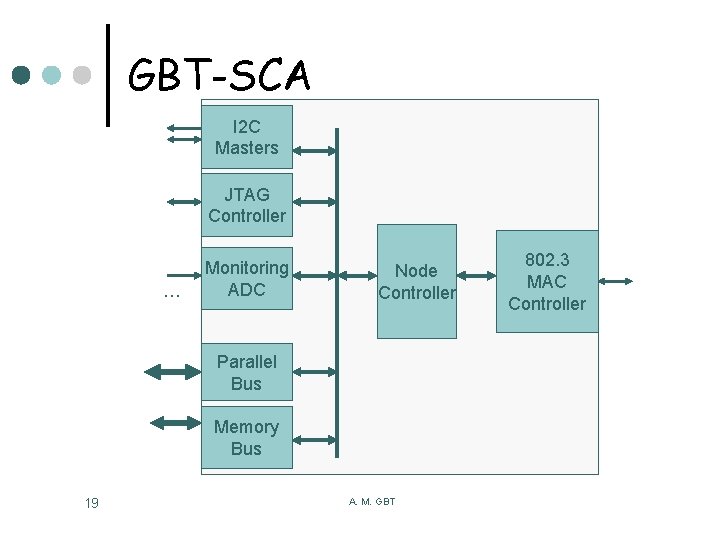

GBT-SCA I 2 C Masters JTAG Controller … Monitoring ADC Node Controller Parallel Bus Memory Bus 19 A. M. GBT 802. 3 MAC Controller

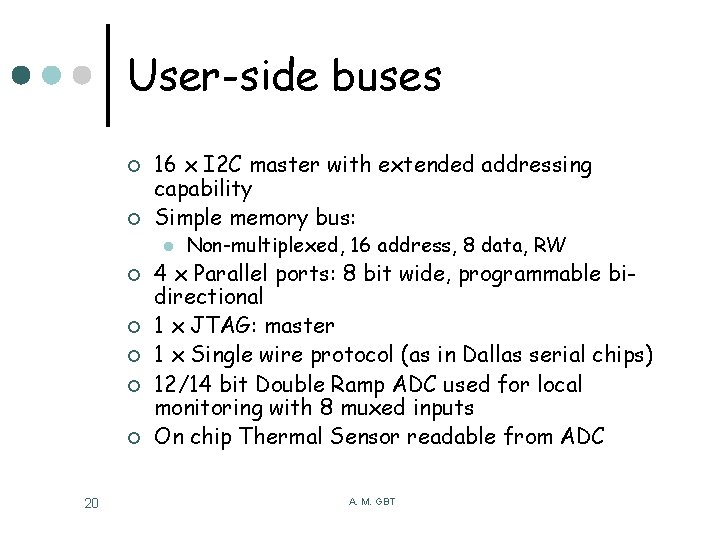

User-side buses ¢ ¢ 16 x I 2 C master with extended addressing capability Simple memory bus: l ¢ ¢ ¢ 20 Non-multiplexed, 16 address, 8 data, RW 4 x Parallel ports: 8 bit wide, programmable bidirectional 1 x JTAG: master 1 x Single wire protocol (as in Dallas serial chips) 12/14 bit Double Ramp ADC used for local monitoring with 8 muxed inputs On chip Thermal Sensor readable from ADC A. M. GBT

User side ports ¢ ¢ ¢ 21 Each bus adapter is seen under the same philosophy of a “port” Slow control system sends “commands” to ports Buffering is foreseen for one command per port Ports acknowledge operation by replying with an ACK Same model applied successfully to CMS tracker and Ecal slow control system (more than 5, 000 chips in operation) A. M. GBT

Why 100 Mb Ethernet? ¢ ¢ Well documented and extremely popular standard Easy to connect to PC (requires PHY interface only) l l ¢ Easy protocol implementation l ¢ ¢ 22 GBT to PC GBT-SCA to PC GBT will transparently carry the 802. 3 protocol Development of GBT and GBT-SCA can go on in parallel with a minimum of interference Almost ‘all-digital’ chip for the GBT-SCA A. M. GBT

Progress ¢ Overall architecture: l ¢ Transceiver blocks are defined to sufficient level to allow design to start for: l l ¢ 23 P 2 P vs. Mixed P 2 P+Passive Optical Distribution are being evaluated Clock and Data Recovery Circuit Trans. Impedance Amplifier Laser Driver Full Coded First version of FEC chip was presented at LECC 2006 A. M. GBT

Plans ¢ ¢ Phased approach is very likely By end of 2007 l l l 24 Converge on Final System Architecture and technology choice Full front end Serializer demonstrator submitted in 130 nm Modeling of complete Slow Control Chip well advanced A. M. GBT

Spare slides A. M. GBT

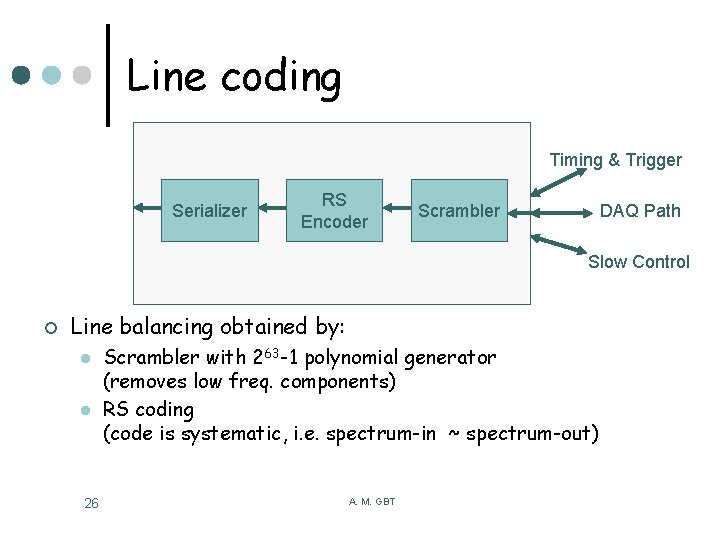

Line coding Timing & Trigger Serializer RS Encoder Scrambler DAQ Path Slow Control ¢ Line balancing obtained by: l l 26 Scrambler with 263 -1 polynomial generator (removes low freq. components) RS coding (code is systematic, i. e. spectrum-in ~ spectrum-out) A. M. GBT

Protocol for Slow Control ¢ ¢ Each GBT-SCA is seen as an Ethernet node The users sends commands (in a class of predefined commands) to the node controller l l ¢ 27 These are dispatched to the relative ports (e. g. I 2 C) The ports performs the action (typically a read or a write) The port provides the answer back to the node controller The Node controller sends a reply back to the Ethernet address who has generated the command If we are more aggressive we could thing of implementing a mini web-server in each GBT-SCA (don’t laugh, commercial chips like this do exist!) A. M. GBT

- Slides: 27