The fetchexecute cycle THE VON NEUMANN ARCHITECTURE Register

- Slides: 18

The fetch-execute cycle THE VON NEUMANN ARCHITECTURE

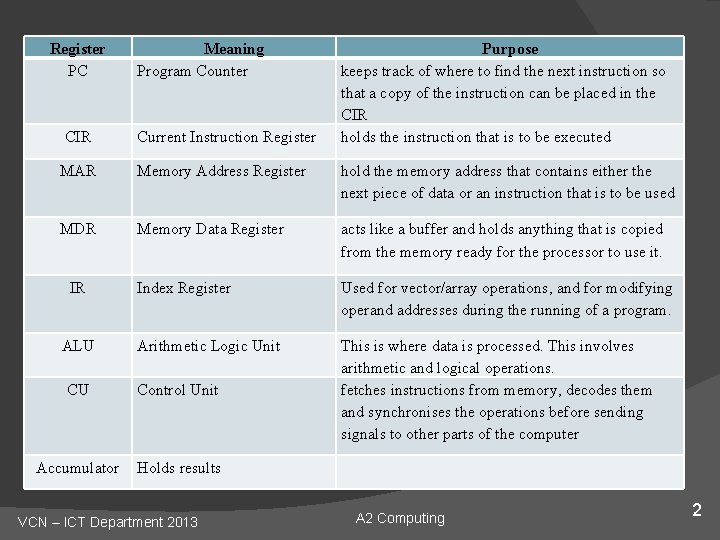

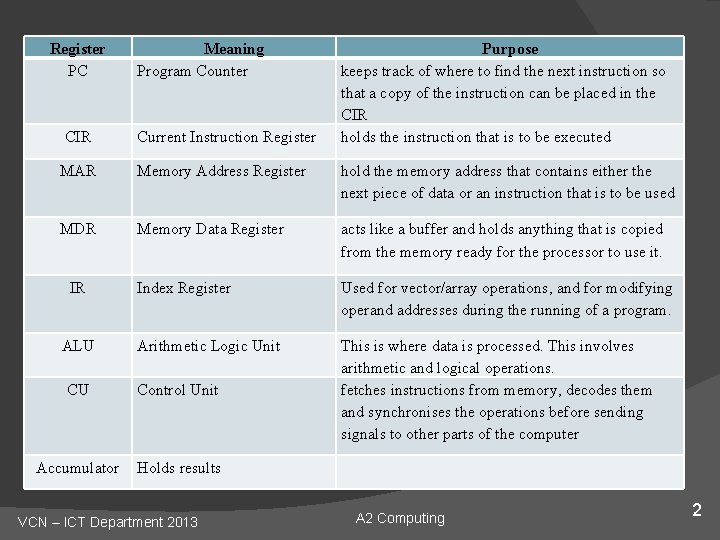

Register PC CIR Meaning Program Counter Current Instruction Register Purpose keeps track of where to find the next instruction so that a copy of the instruction can be placed in the CIR holds the instruction that is to be executed MAR Memory Address Register hold the memory address that contains either the next piece of data or an instruction that is to be used MDR Memory Data Register acts like a buffer and holds anything that is copied from the memory ready for the processor to use it. Index Register Used for vector/array operations, and for modifying operand addresses during the running of a program. Arithmetic Logic Unit This is where data is processed. This involves arithmetic and logical operations. fetches instructions from memory, decodes them and synchronises the operations before sending signals to other parts of the computer IR ALU CU Control Unit Accumulator Holds results VCN – ICT Department 2013 A 2 Computing 2

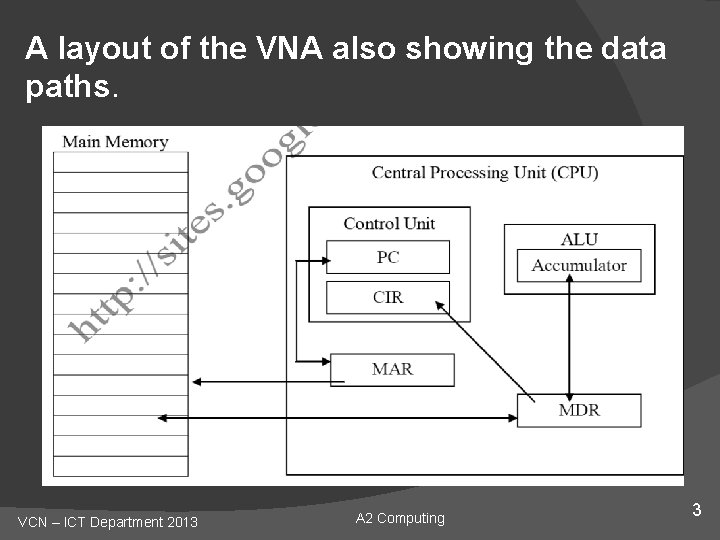

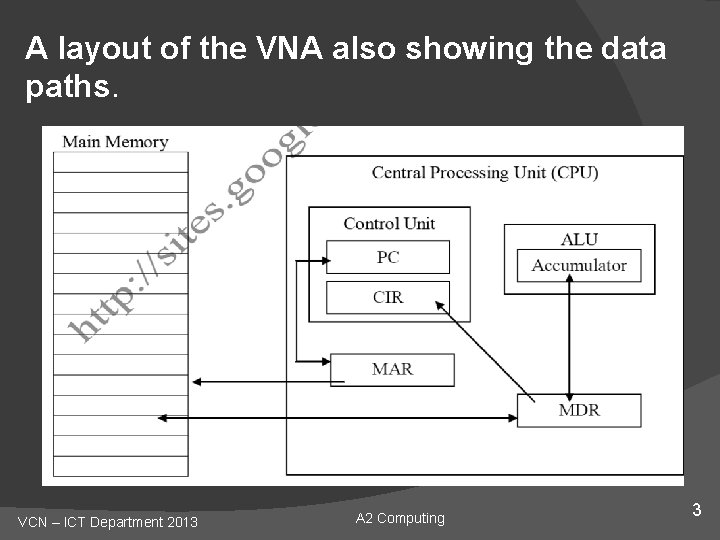

A layout of the VNA also showing the data paths. VCN – ICT Department 2013 A 2 Computing 3

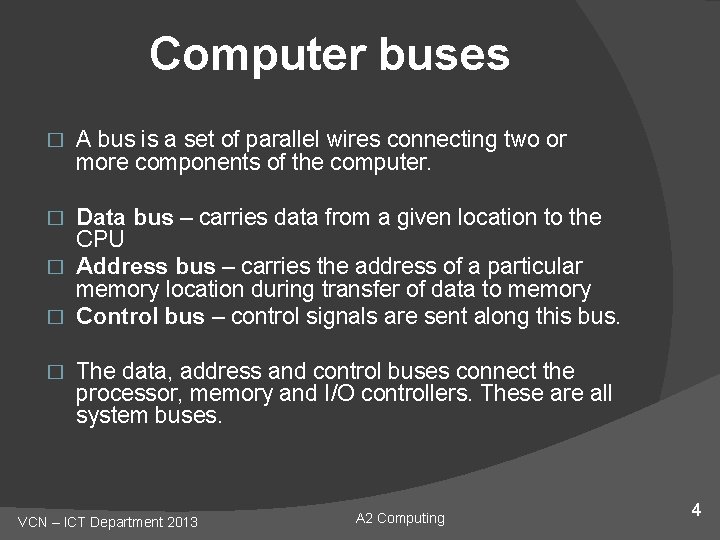

Computer buses � A bus is a set of parallel wires connecting two or more components of the computer. Data bus – carries data from a given location to the CPU � Address bus – carries the address of a particular memory location during transfer of data to memory � Control bus – control signals are sent along this bus. � � The data, address and control buses connect the processor, memory and I/O controllers. These are all system buses. VCN – ICT Department 2013 A 2 Computing 4

Failures of Von Neumann � Both data and programs share the same memory space. This is a problem because it is quite easy for a poorly written or faulty piece of code to write data into an area holding other instructions, so trashing that program. VCN – ICT Department 2013 A 2 Computing 5

� Every piece of data and instruction has to pass across the data bus in order to move from main memory into the CPU (and back again). �This is a problem because the data bus is a lot slower than the rate at which the CPU can carry out instructions. �This is called the 'Von Neumann bottleneck'. �If nothing were done, the CPU would spend most of its time waiting around for instructions. �A special kind of memory called a 'Cache' (pronounced 'cash') is used to tackle with this problem VCN – ICT Department 2013 A 2 Computing 6

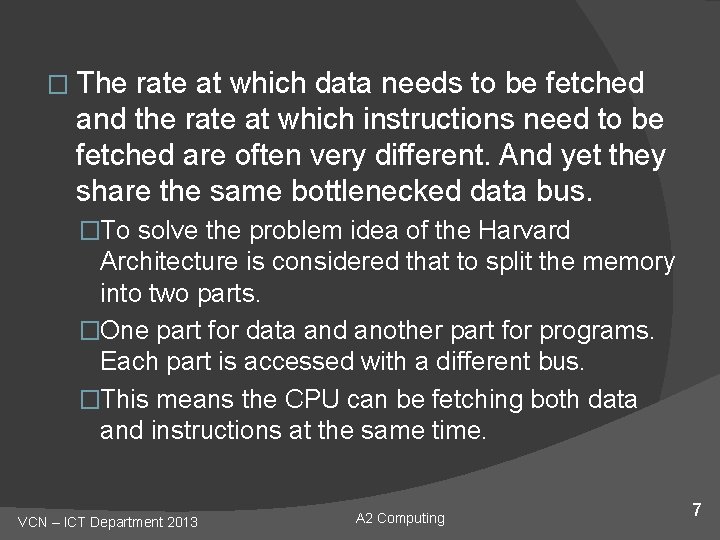

� The rate at which data needs to be fetched and the rate at which instructions need to be fetched are often very different. And yet they share the same bottlenecked data bus. �To solve the problem idea of the Harvard Architecture is considered that to split the memory into two parts. �One part for data and another part for programs. Each part is accessed with a different bus. �This means the CPU can be fetching both data and instructions at the same time. VCN – ICT Department 2013 A 2 Computing 7

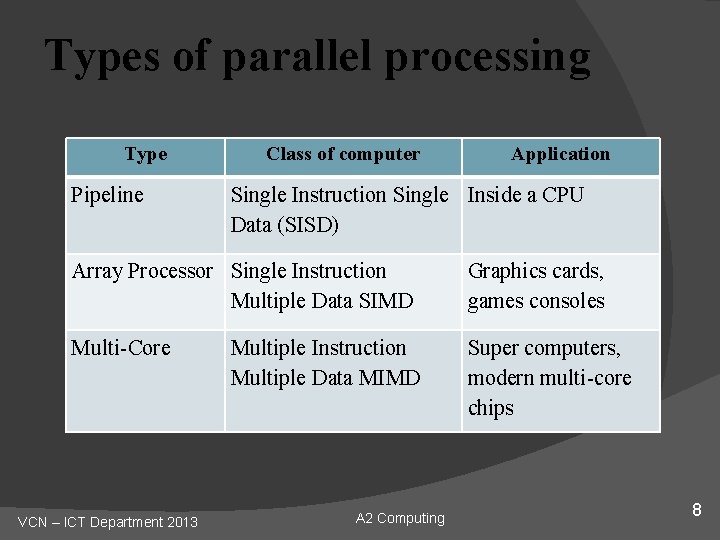

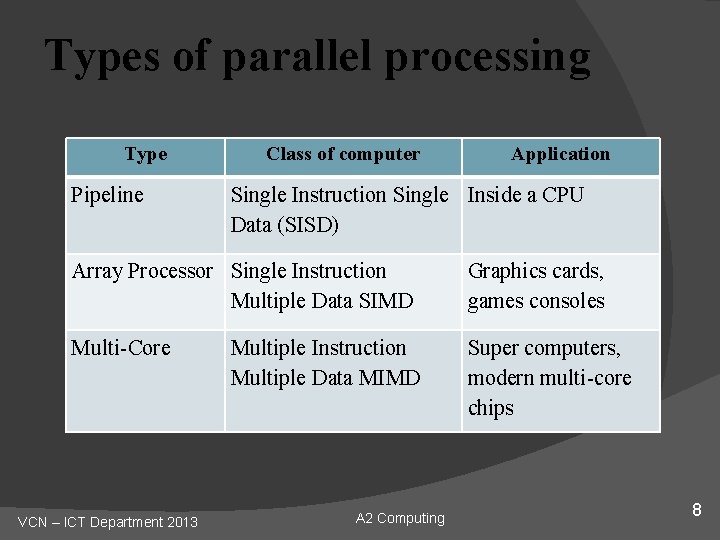

Types of parallel processing Type Pipeline Class of computer Application Single Instruction Single Inside a CPU Data (SISD) Array Processor Single Instruction Multiple Data SIMD Graphics cards, games consoles Multi-Core Super computers, modern multi-core chips VCN – ICT Department 2013 Multiple Instruction Multiple Data MIMD A 2 Computing 8

Parallel Processors � Parallel processing is the simultaneous processing of data. � The simultaneous use of more than one CPU or processor core to execute a program or multiple threads. Hence this speeds up the rate at which processing occurs. VCN – ICT Department 2013 A 2 Computing 9

Advantages of parallel processing � Faster when handling large amounts of data � Is not limited by the bus transfer rate (the Von Neumann bottleneck) � Can make maximum use of the CPU (pipeline method) in spite of the bottleneck VCN – ICT Department 2013 A 2 Computing 10

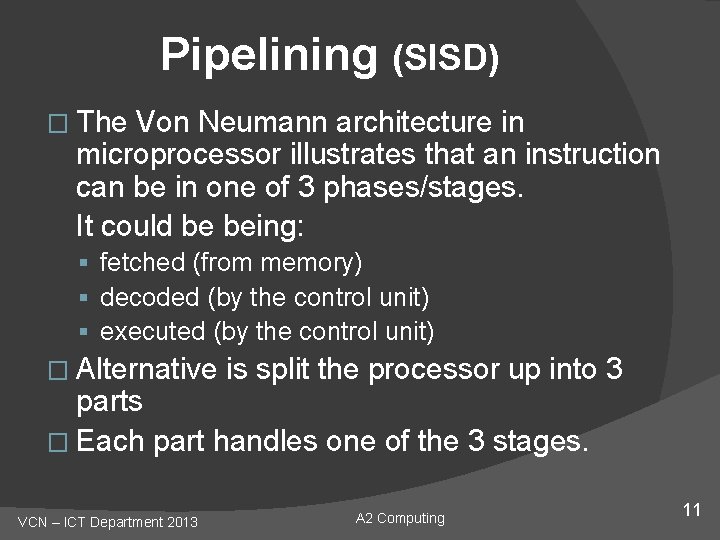

Pipelining (SISD) � The Von Neumann architecture in microprocessor illustrates that an instruction can be in one of 3 phases/stages. It could be being: § fetched (from memory) § decoded (by the control unit) § executed (by the control unit) � Alternative is split the processor up into 3 parts � Each part handles one of the 3 stages. VCN – ICT Department 2013 A 2 Computing 11

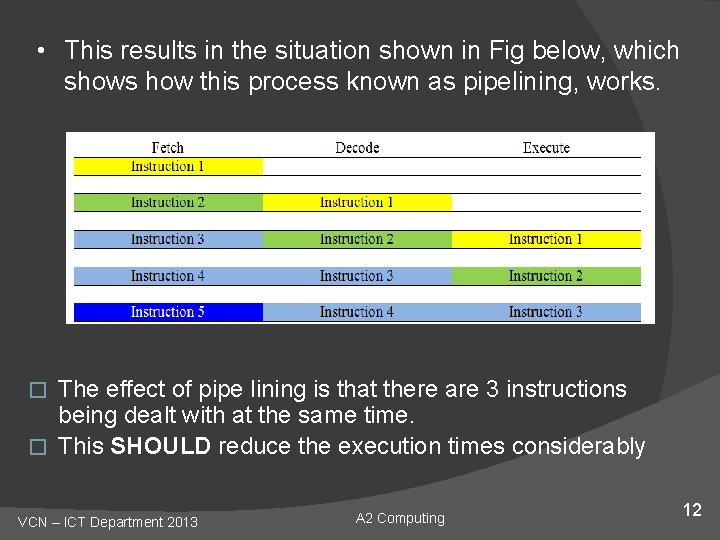

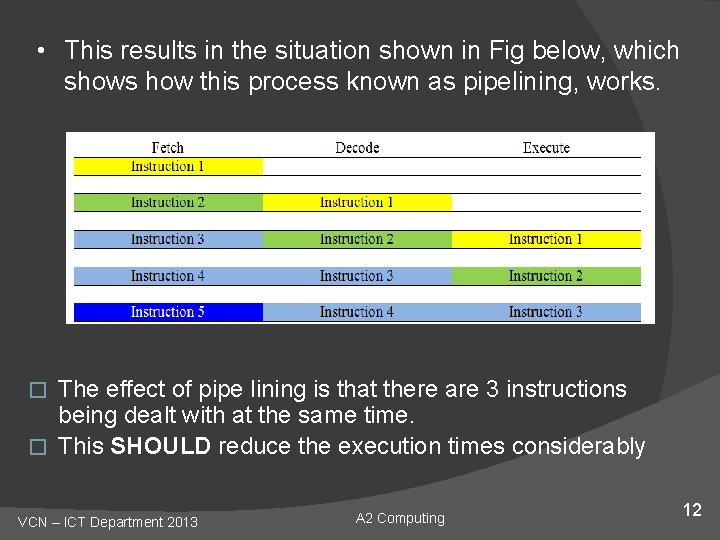

• This results in the situation shown in Fig below, which shows how this process known as pipelining, works. The effect of pipe lining is that there are 3 instructions being dealt with at the same time. � This SHOULD reduce the execution times considerably � VCN – ICT Department 2013 A 2 Computing 12

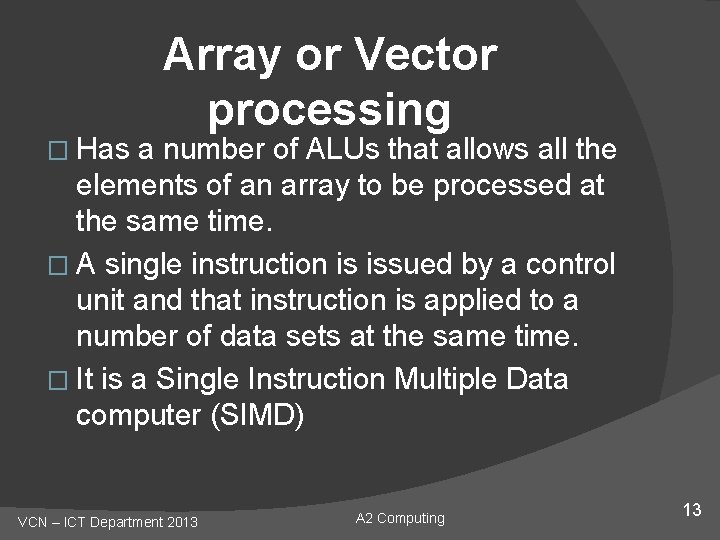

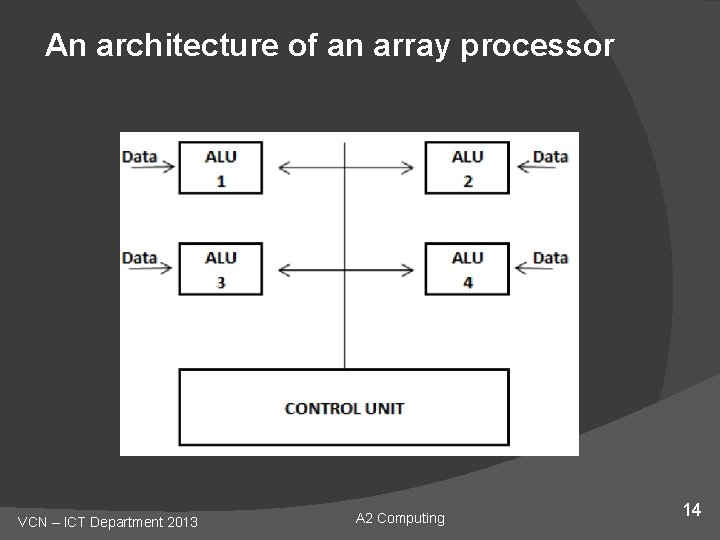

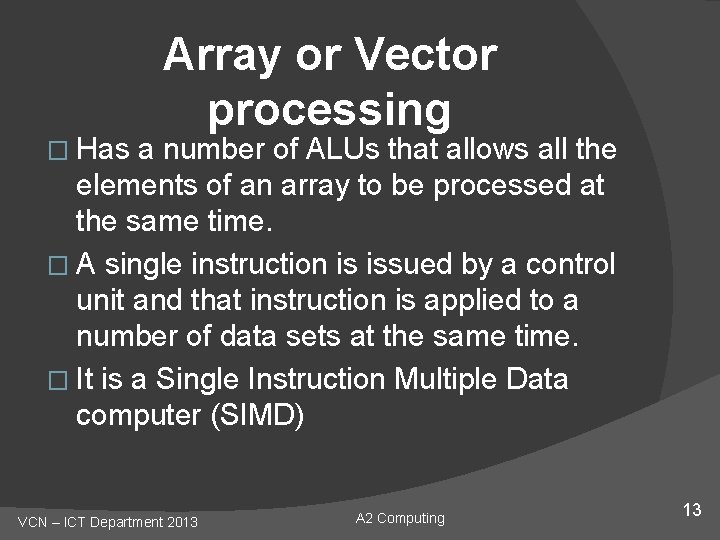

� Has Array or Vector processing a number of ALUs that allows all the elements of an array to be processed at the same time. � A single instruction is issued by a control unit and that instruction is applied to a number of data sets at the same time. � It is a Single Instruction Multiple Data computer (SIMD) VCN – ICT Department 2013 A 2 Computing 13

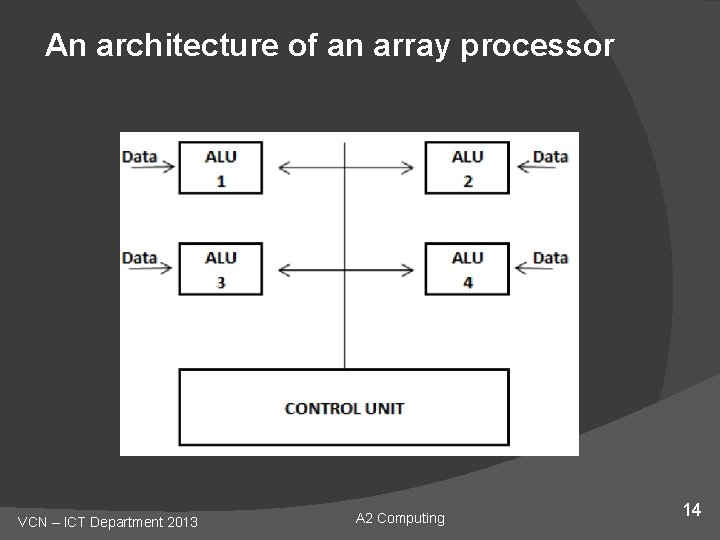

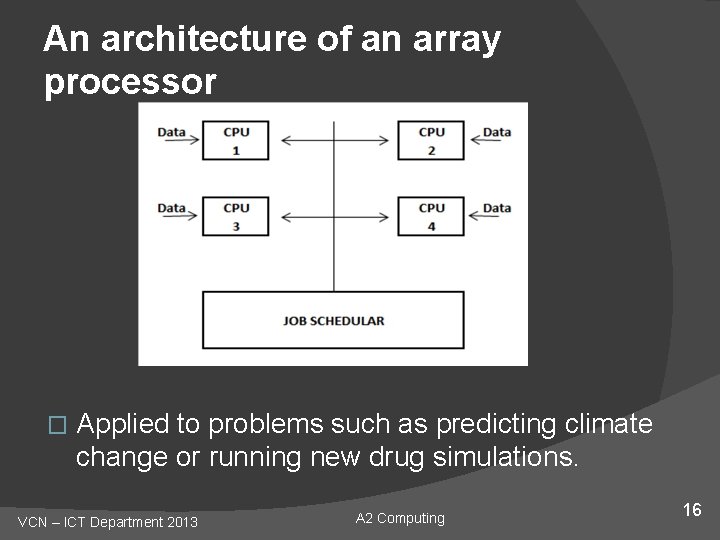

An architecture of an array processor VCN – ICT Department 2013 A 2 Computing 14

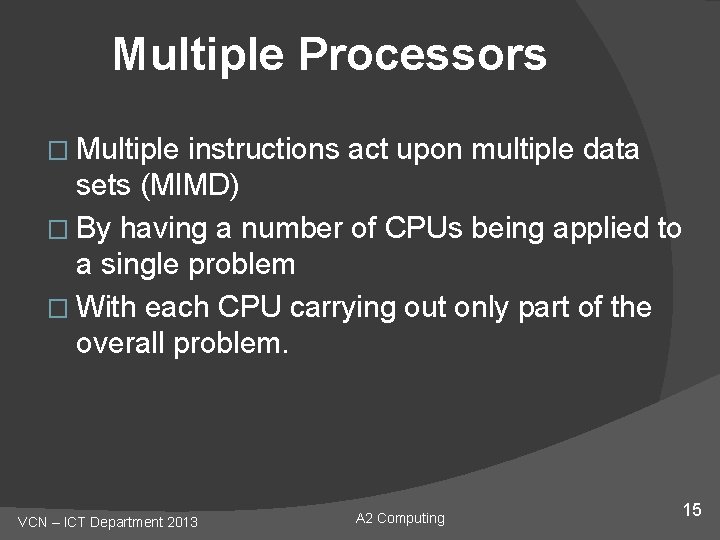

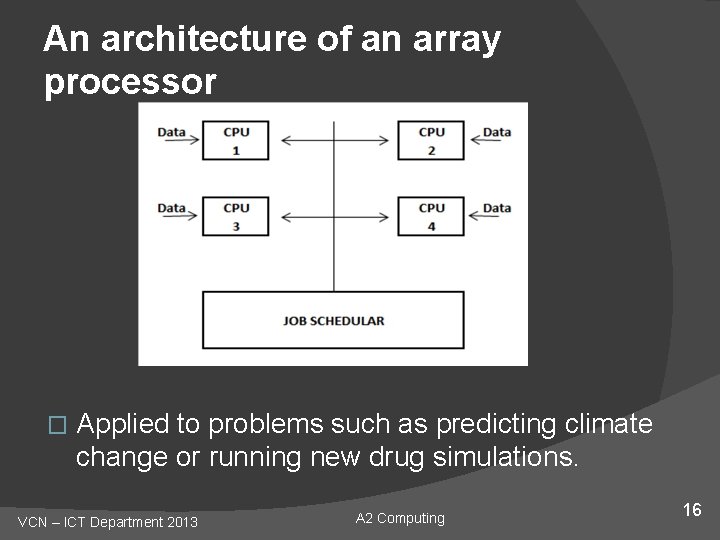

Multiple Processors � Multiple instructions act upon multiple data sets (MIMD) � By having a number of CPUs being applied to a single problem � With each CPU carrying out only part of the overall problem. VCN – ICT Department 2013 A 2 Computing 15

An architecture of an array processor � Applied to problems such as predicting climate change or running new drug simulations. VCN – ICT Department 2013 A 2 Computing 16

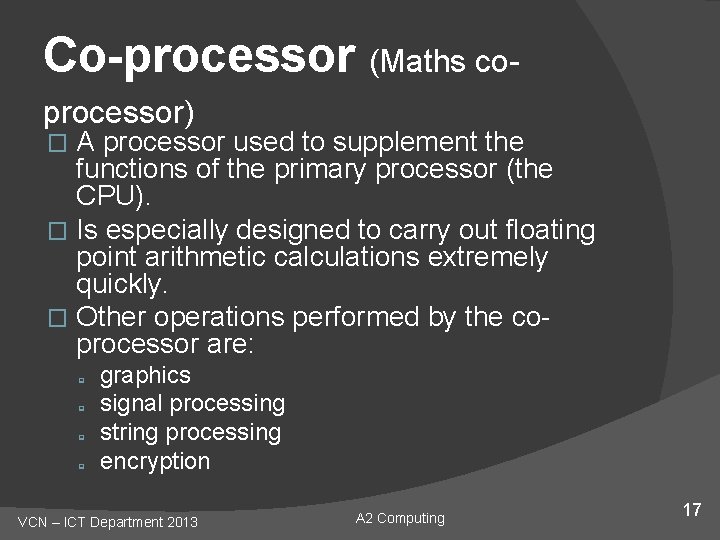

Co-processor (Maths coprocessor) A processor used to supplement the functions of the primary processor (the CPU). � Is especially designed to carry out floating point arithmetic calculations extremely quickly. � Other operations performed by the coprocessor are: � q q graphics signal processing string processing encryption VCN – ICT Department 2013 A 2 Computing 17

Assignment 2 � Qn 1: What are the disadvantages of parallel processing? � Qn 2: What are the applications and limitations of array, multiple and pipeline processors? VCN – ICT Department 2013 A 2 Computing 18