The Fetch Decode Execute Cycle The History of

- Slides: 29

The Fetch Decode Execute Cycle The History of Computing © London Grid for Learning www. HOC. lgfl. net

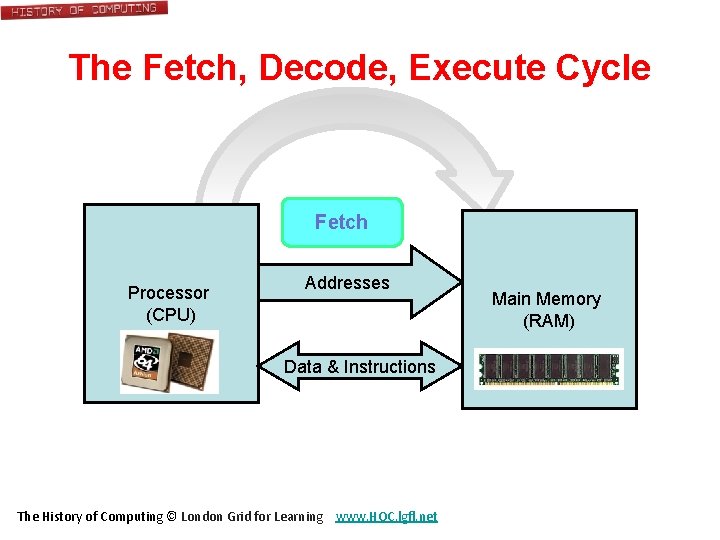

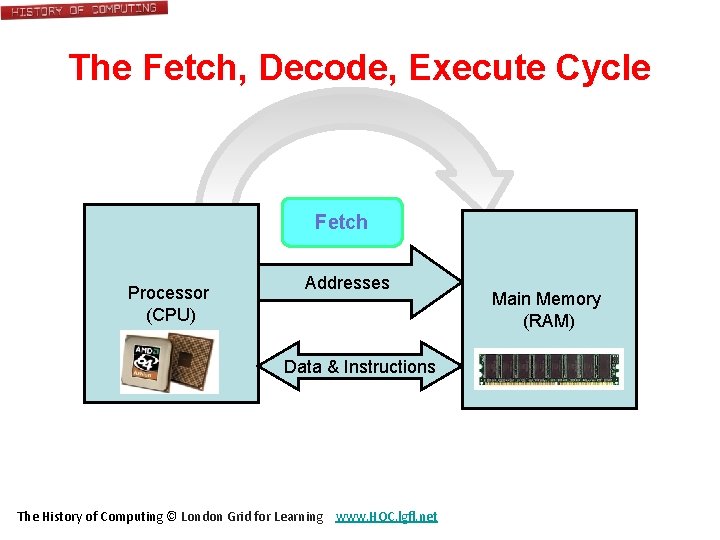

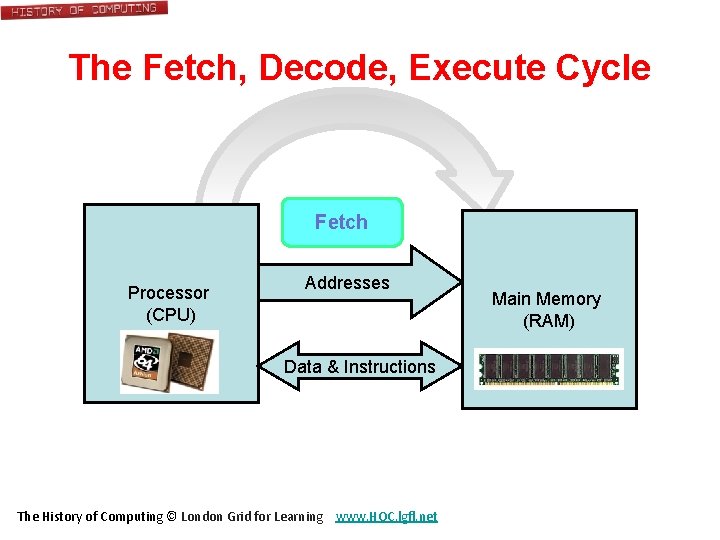

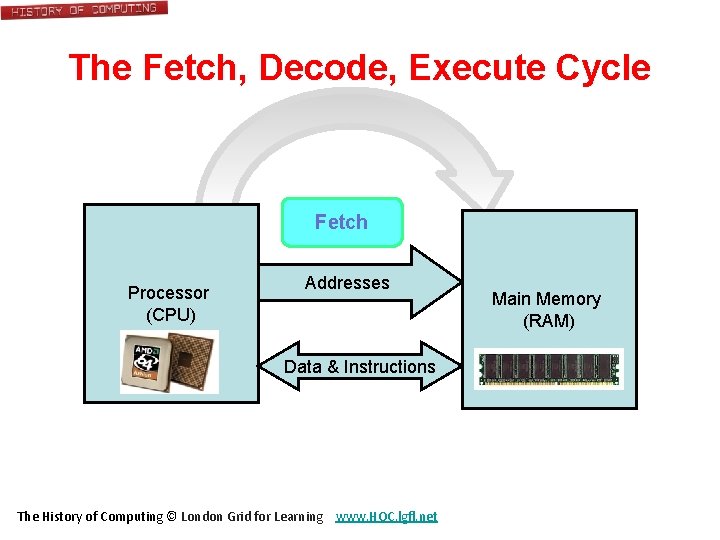

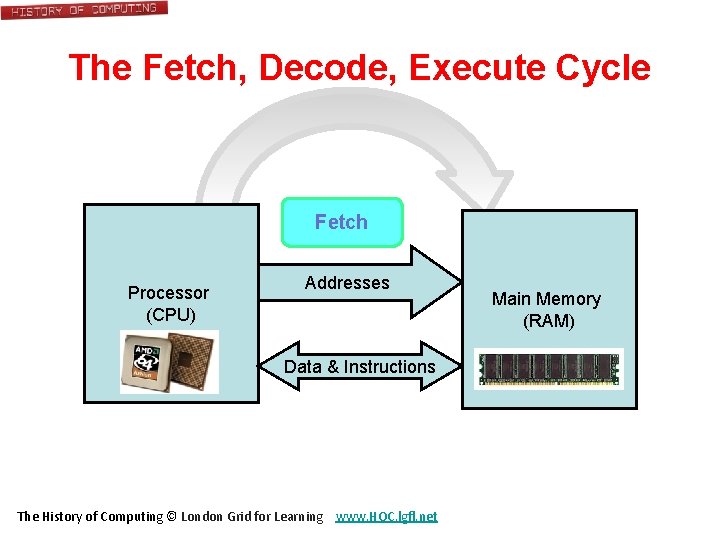

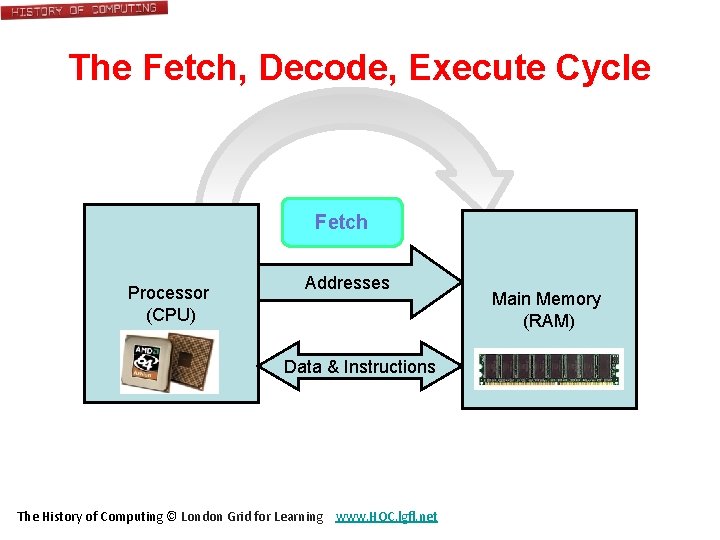

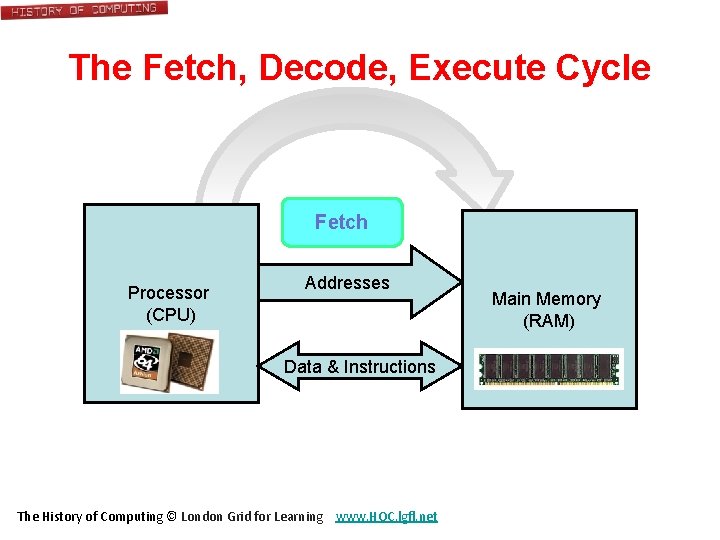

The Fetch, Decode, Execute Cycle Fetch Processor (CPU) Addresses Data & Instructions The History of Computing © London Grid for Learning www. HOC. lgfl. net Main Memory (RAM)

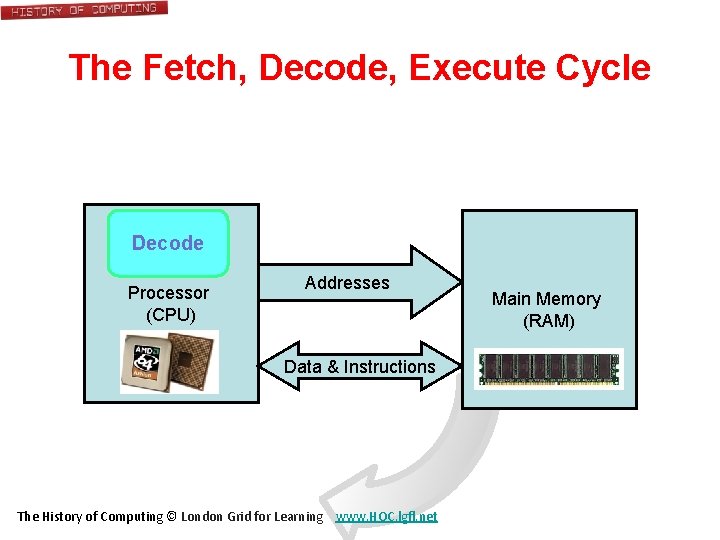

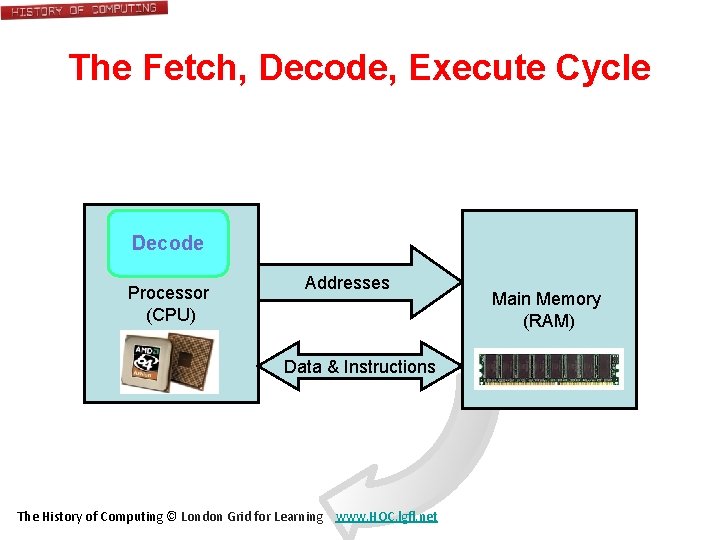

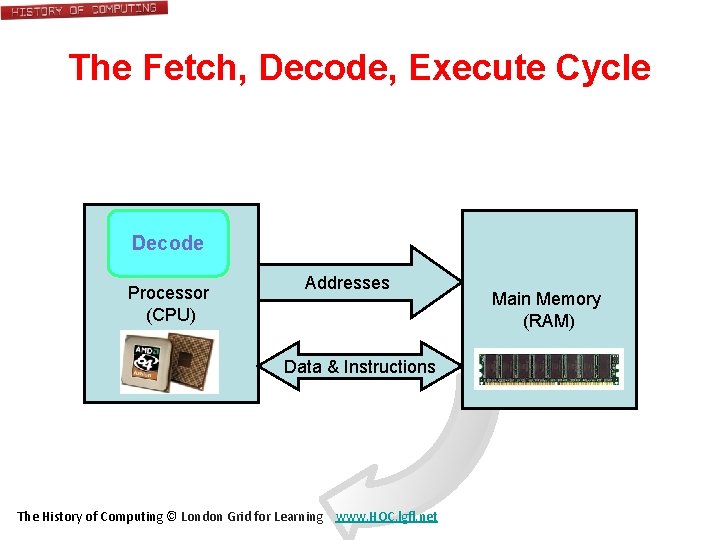

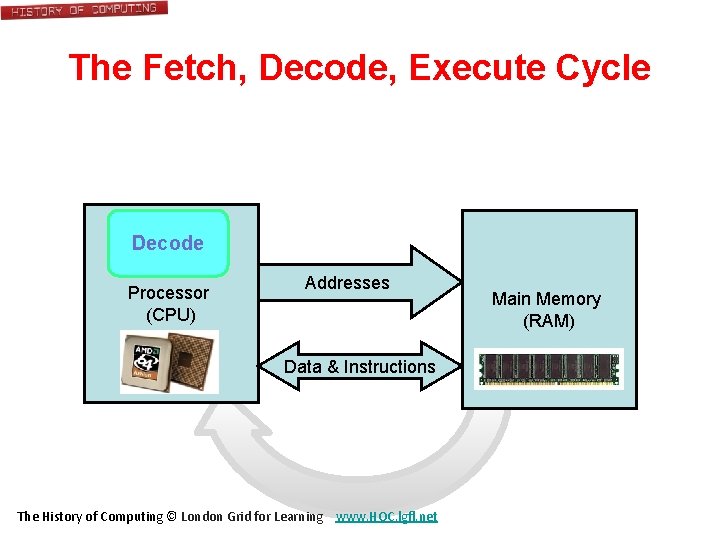

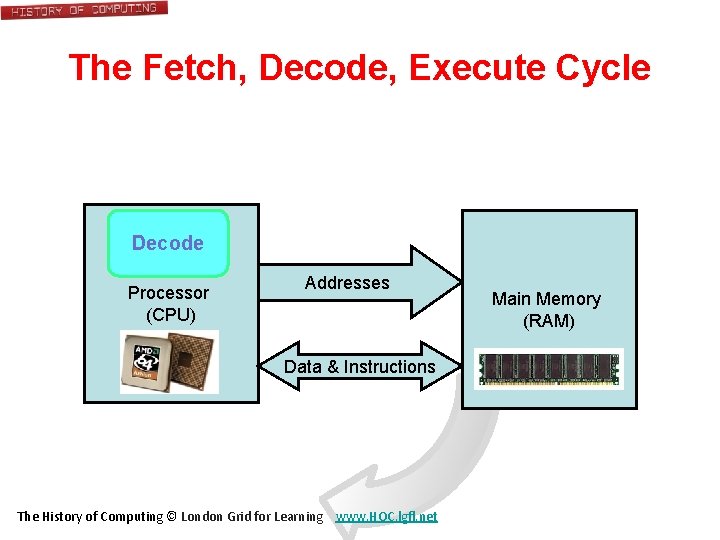

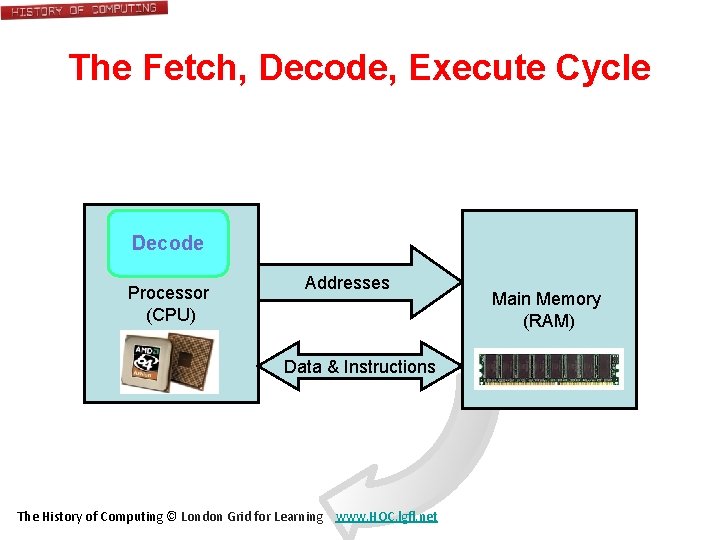

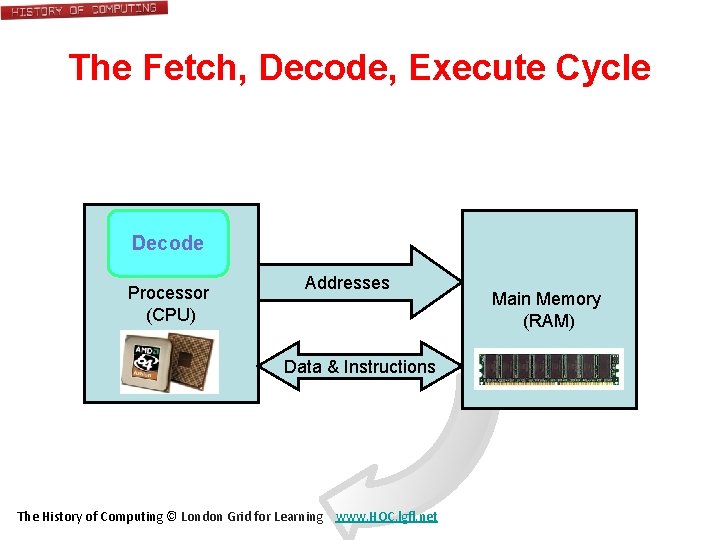

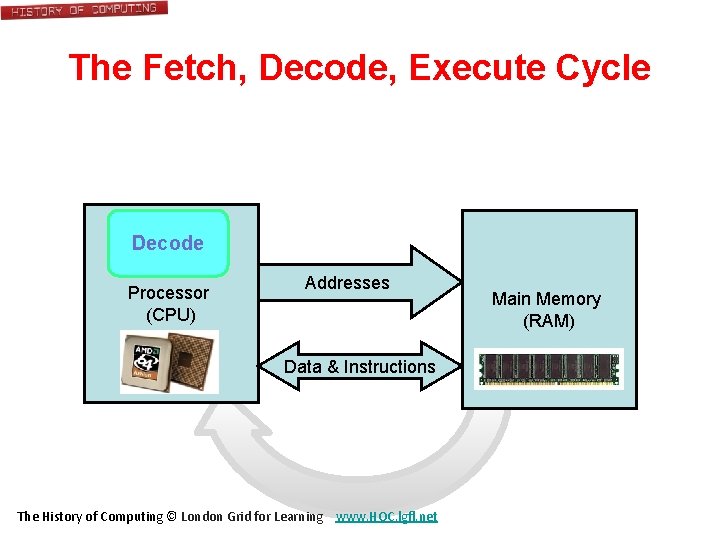

The Fetch, Decode, Execute Cycle Decode Processor (CPU) Addresses Data & Instructions The History of Computing © London Grid for Learning www. HOC. lgfl. net Main Memory (RAM)

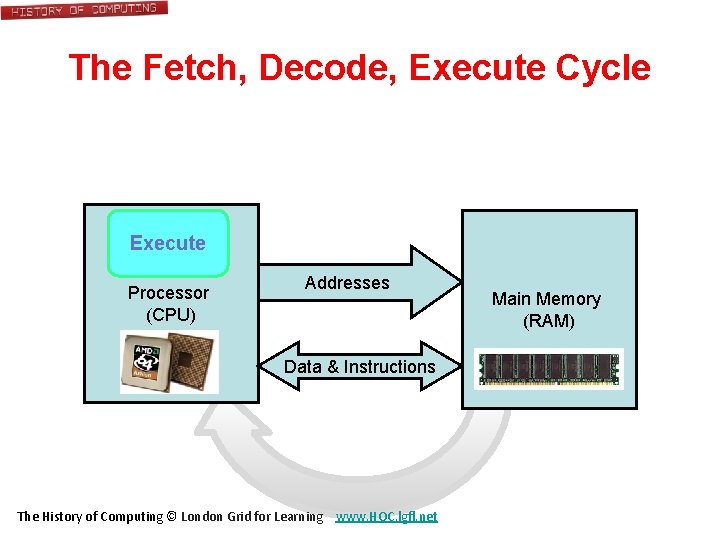

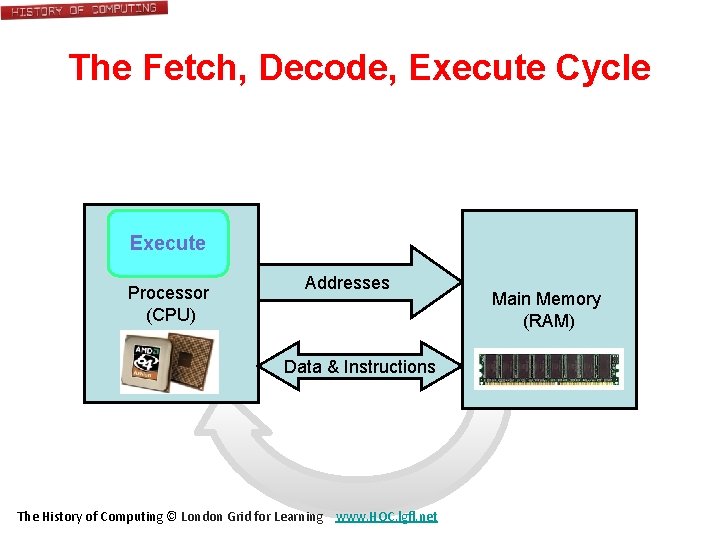

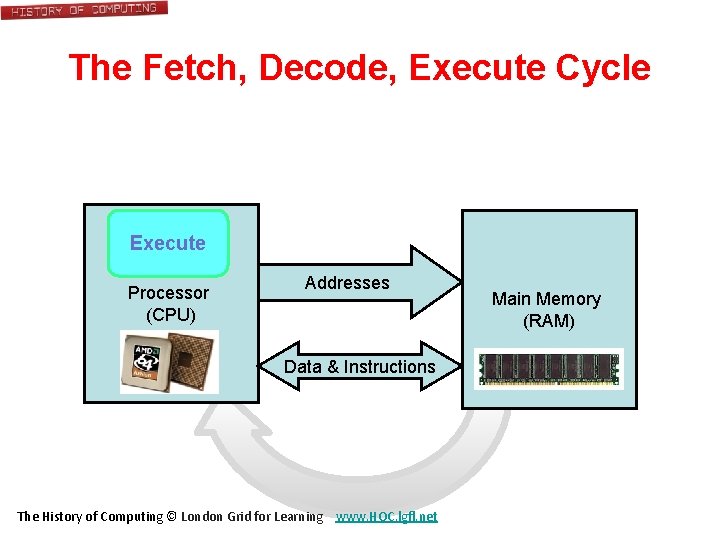

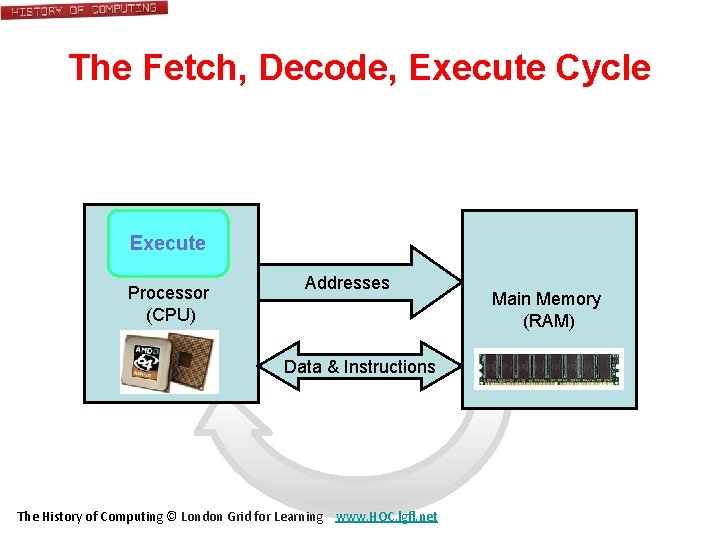

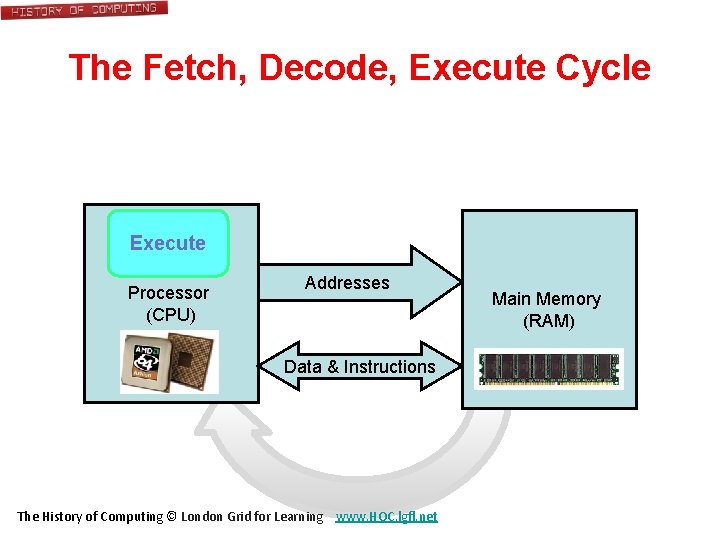

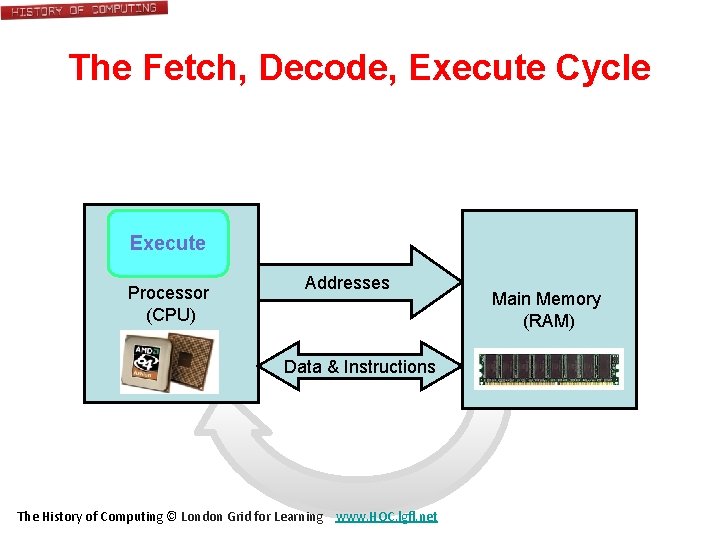

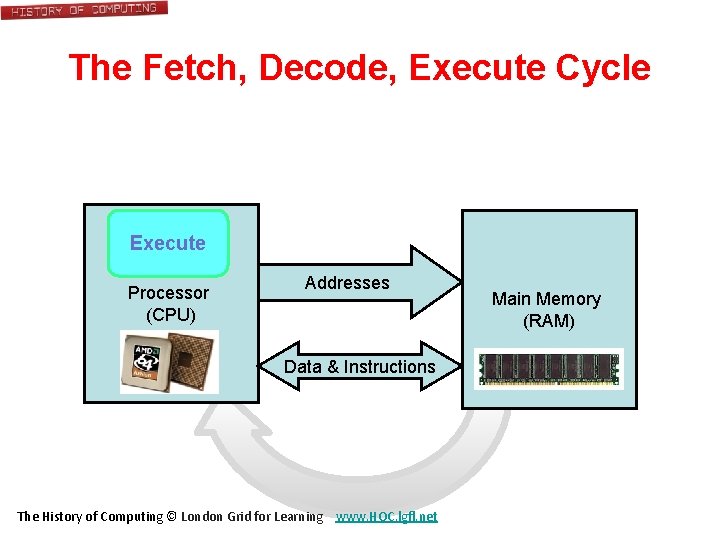

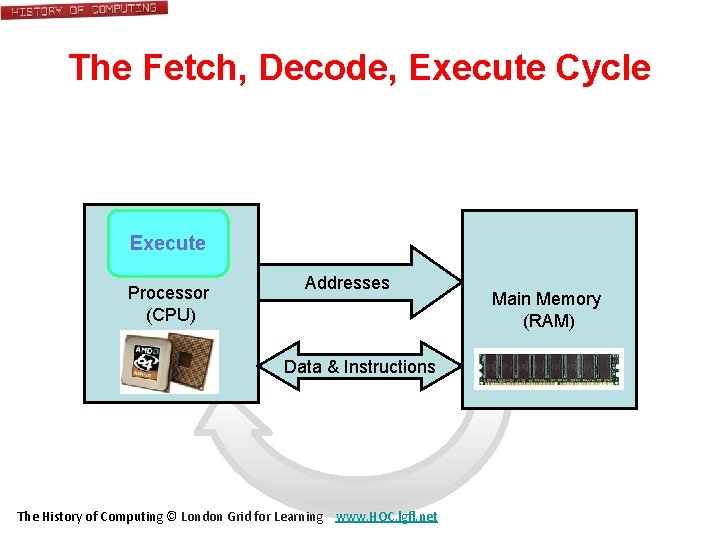

The Fetch, Decode, Execute Cycle Execute Processor (CPU) Addresses Data & Instructions The History of Computing © London Grid for Learning www. HOC. lgfl. net Main Memory (RAM)

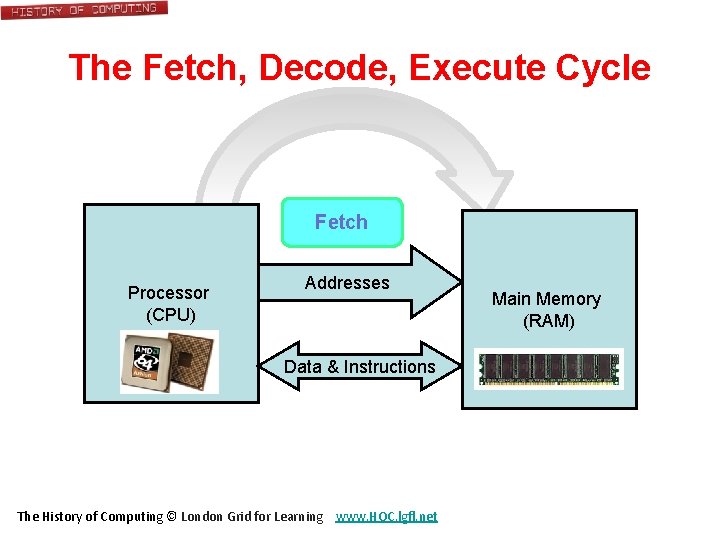

The Fetch, Decode, Execute Cycle Fetch Processor (CPU) Addresses Data & Instructions The History of Computing © London Grid for Learning www. HOC. lgfl. net Main Memory (RAM)

The Fetch, Decode, Execute Cycle Decode Processor (CPU) Addresses Data & Instructions The History of Computing © London Grid for Learning www. HOC. lgfl. net Main Memory (RAM)

The Fetch, Decode, Execute Cycle Execute Processor (CPU) Addresses Data & Instructions The History of Computing © London Grid for Learning www. HOC. lgfl. net Main Memory (RAM)

The Fetch, Decode, Execute Cycle Fetch Processor (CPU) Addresses Data & Instructions The History of Computing © London Grid for Learning www. HOC. lgfl. net Main Memory (RAM)

The Fetch, Decode, Execute Cycle Decode Processor (CPU) Addresses Data & Instructions The History of Computing © London Grid for Learning www. HOC. lgfl. net Main Memory (RAM)

The Fetch, Decode, Execute Cycle Execute Processor (CPU) Addresses Data & Instructions The History of Computing © London Grid for Learning www. HOC. lgfl. net Main Memory (RAM)

The Fetch, Decode, Execute Cycle Fetch Processor (CPU) Addresses Data & Instructions The History of Computing © London Grid for Learning www. HOC. lgfl. net Main Memory (RAM)

The Fetch, Decode, Execute Cycle Decode Processor (CPU) Addresses Data & Instructions The History of Computing © London Grid for Learning www. HOC. lgfl. net Main Memory (RAM)

The Fetch, Decode, Execute Cycle Execute Processor (CPU) Addresses Data & Instructions The History of Computing © London Grid for Learning www. HOC. lgfl. net Main Memory (RAM)

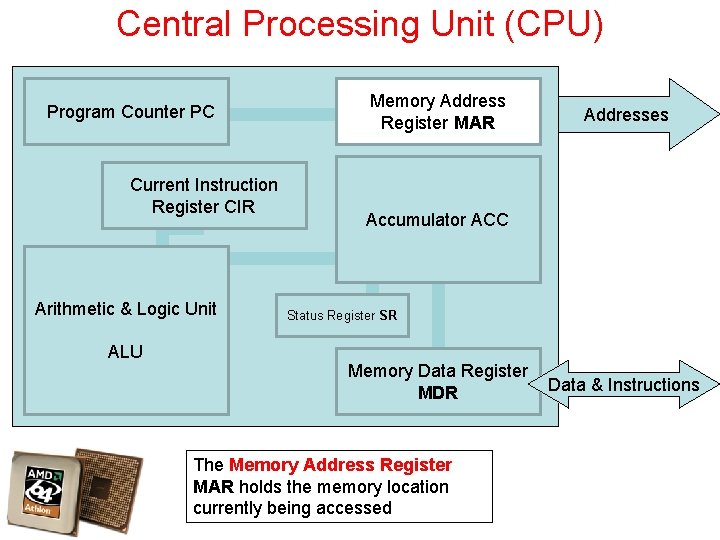

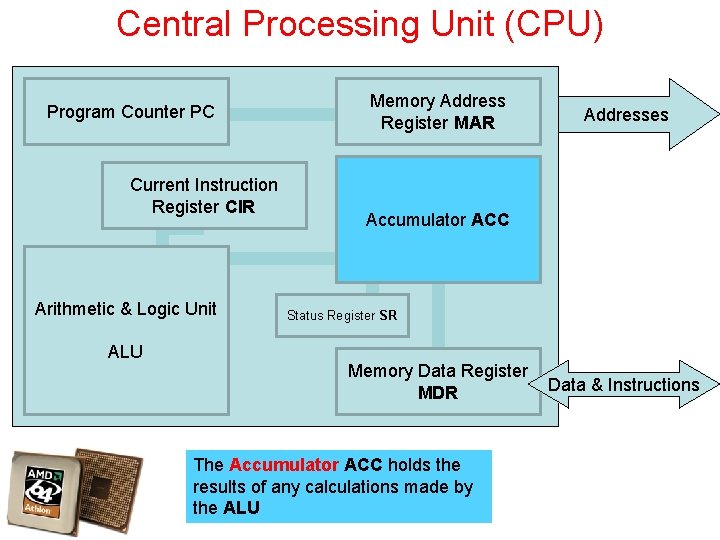

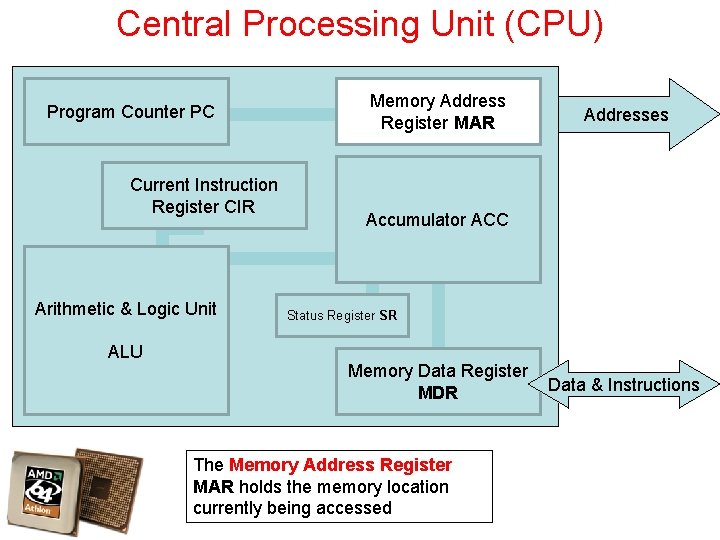

Central Processing Unit (CPU) Program Counter PC Current Instruction Register CIR Arithmetic & Logic Unit ALU Memory Address Register MAR Addresses Accumulator ACC Status Register SR Memory Data Register MDR The Memory Address Register MAR holds the memory location currently being accessed Data & Instructions

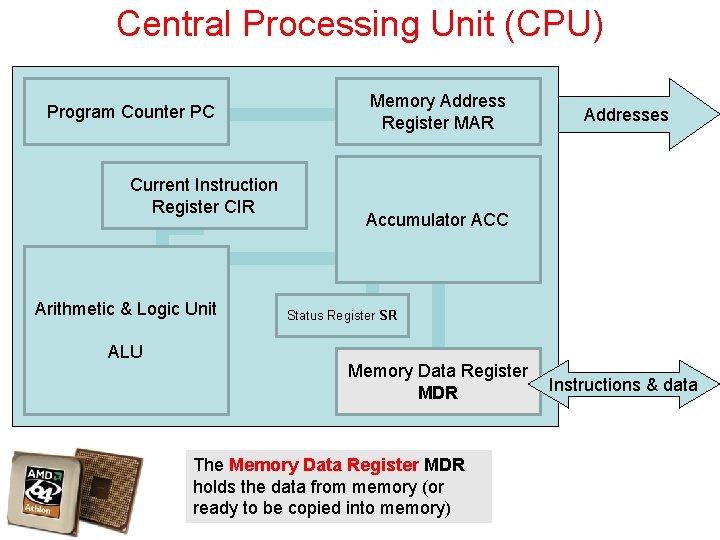

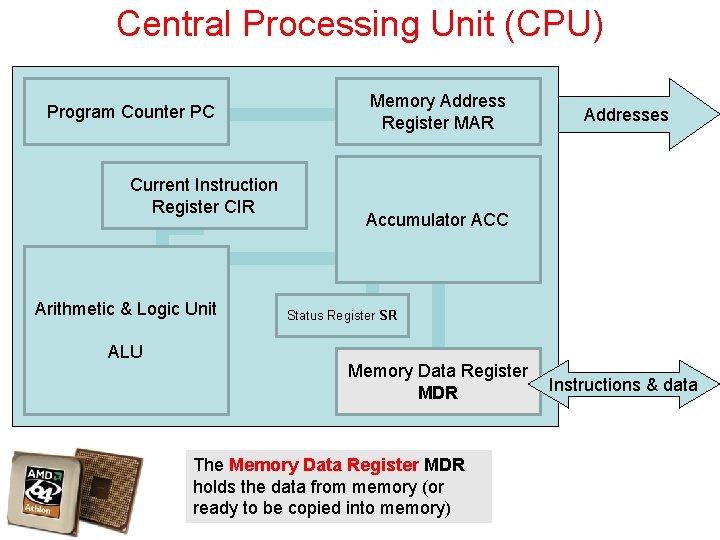

Central Processing Unit (CPU) Program Counter PC Current Instruction Register CIR Arithmetic & Logic Unit ALU Memory Address Register MAR Addresses Accumulator ACC Status Register SR Memory Data Register MDR The Memory Data Register MDR holds the data from memory (or ready to be copied into memory) Instructions & data

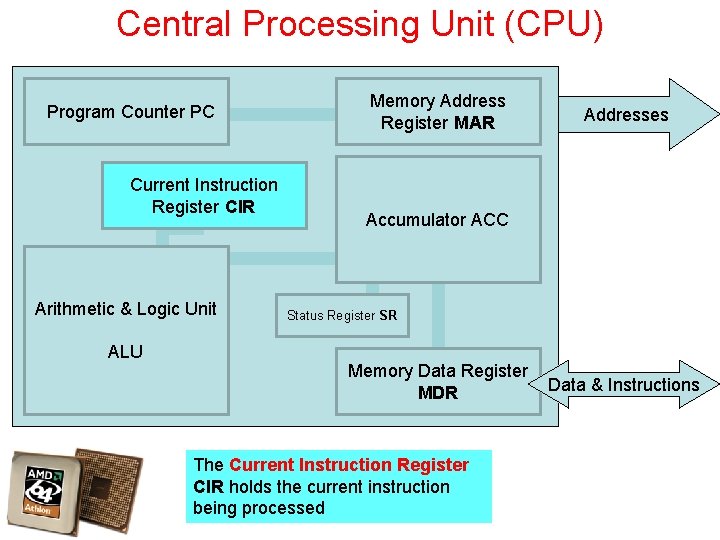

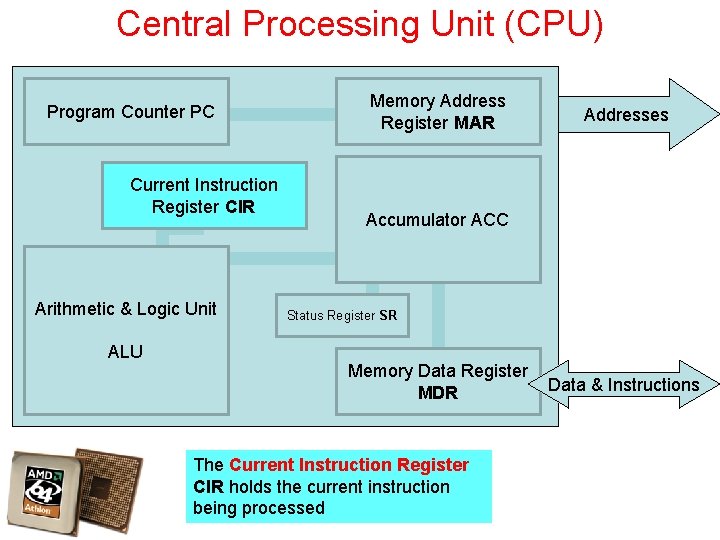

Central Processing Unit (CPU) Program Counter PC Current Instruction Register CIR Arithmetic & Logic Unit ALU Memory Address Register MAR Addresses Accumulator ACC Status Register SR Memory Data Register MDR The Current Instruction Register CIR holds the current instruction being processed Data & Instructions

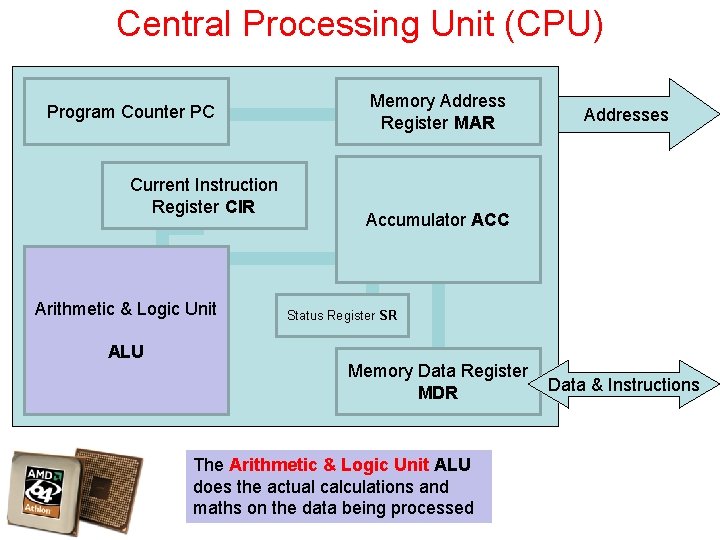

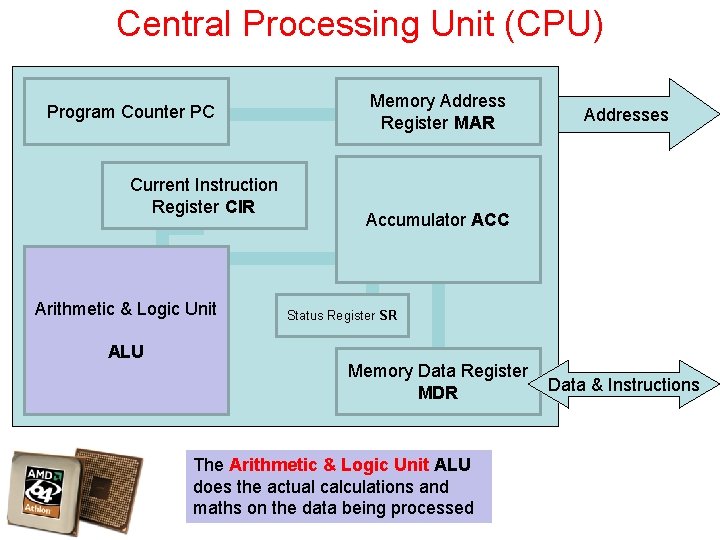

Central Processing Unit (CPU) Program Counter PC Current Instruction Register CIR Arithmetic & Logic Unit ALU Memory Address Register MAR Addresses Accumulator ACC Status Register SR Memory Data Register MDR The Arithmetic & Logic Unit ALU does the actual calculations and maths on the data being processed Data & Instructions

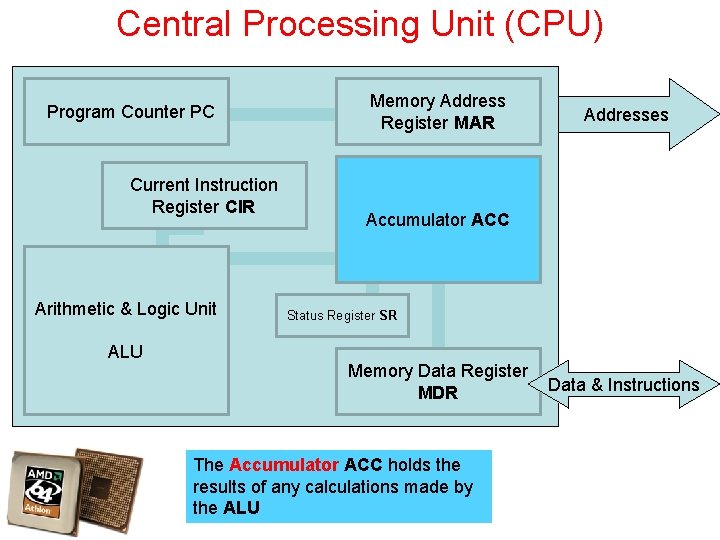

Central Processing Unit (CPU) Program Counter PC Current Instruction Register CIR Arithmetic & Logic Unit ALU Memory Address Register MAR Addresses Accumulator ACC Status Register SR Memory Data Register MDR The Accumulator ACC holds the results of any calculations made by the ALU Data & Instructions

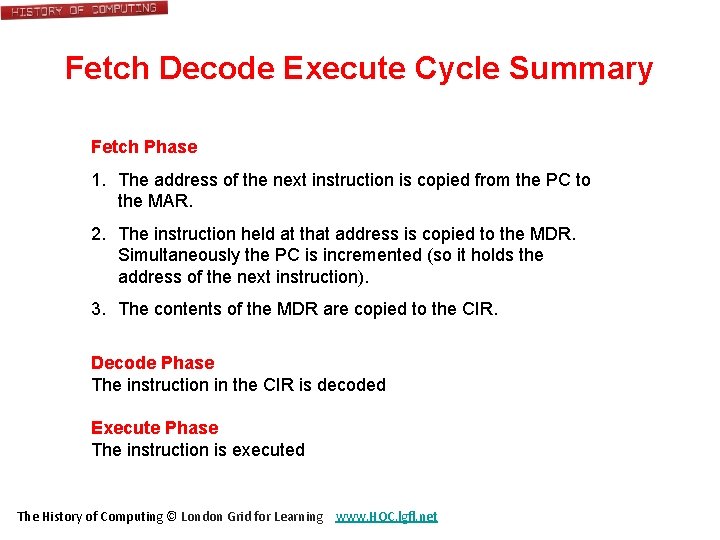

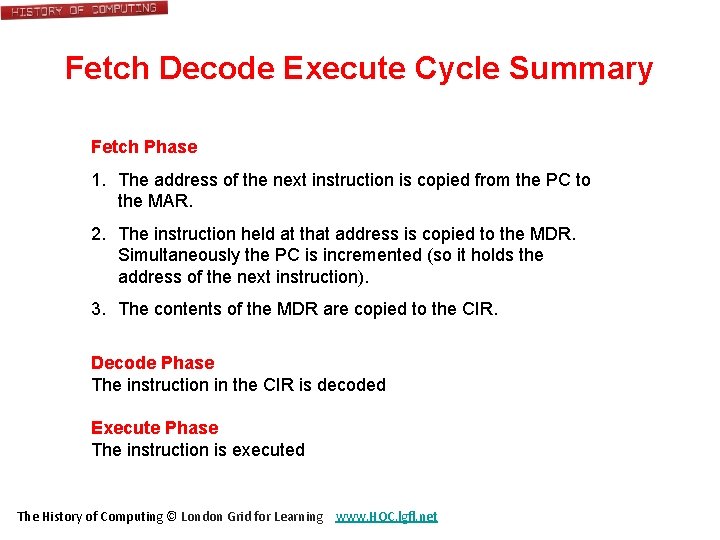

Fetch Decode Execute Cycle Summary Fetch Phase 1. The address of the next instruction is copied from the PC to the MAR. 2. The instruction held at that address is copied to the MDR. Simultaneously the PC is incremented (so it holds the address of the next instruction). 3. The contents of the MDR are copied to the CIR. Decode Phase The instruction in the CIR is decoded Execute Phase The instruction is executed The History of Computing © London Grid for Learning www. HOC. lgfl. net

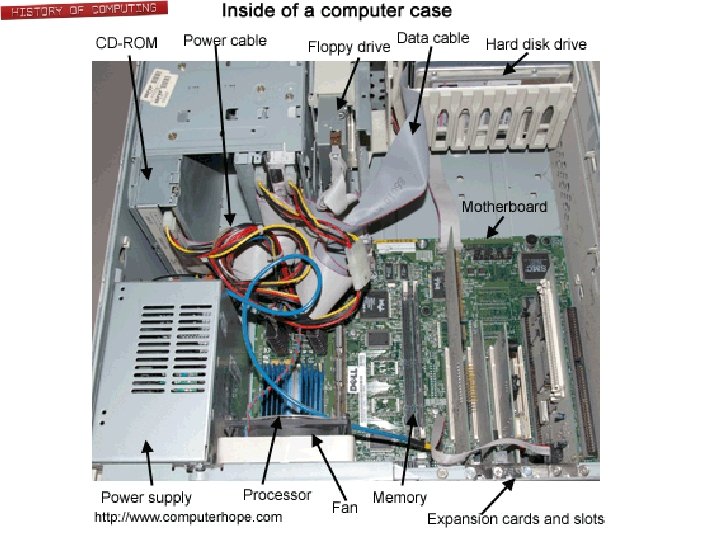

Identifying Components CPUs Central Processors The History of Computing © London Grid for Learning www. HOC. lgfl. net

Identifying Components Heat sinks and fans

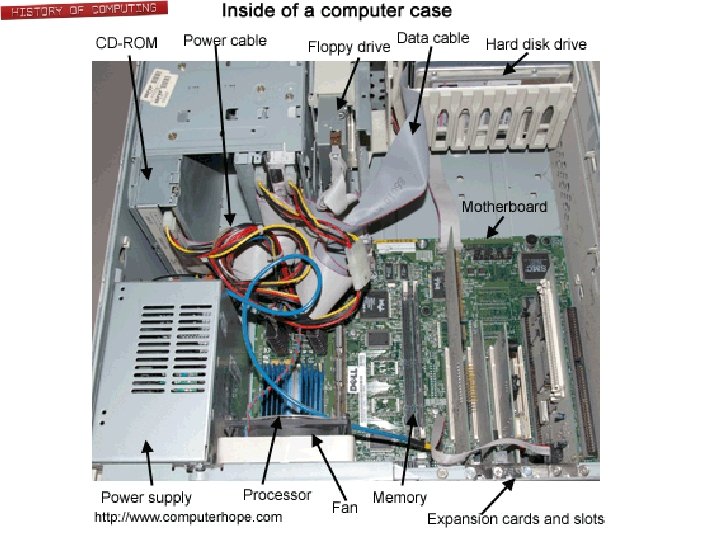

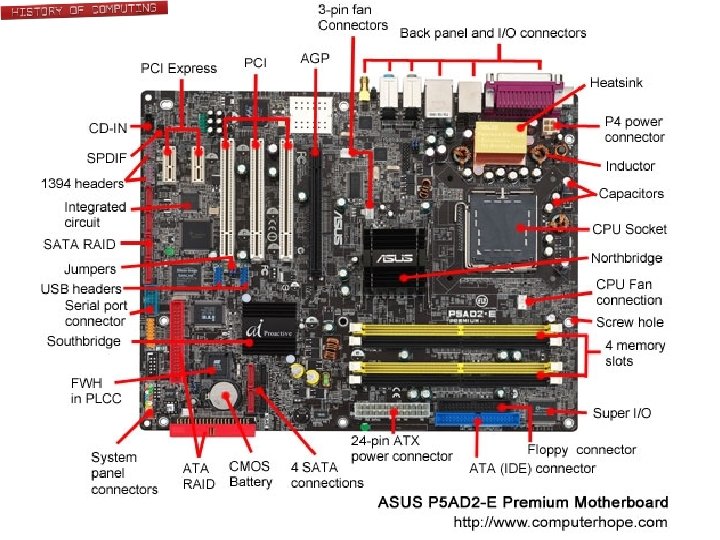

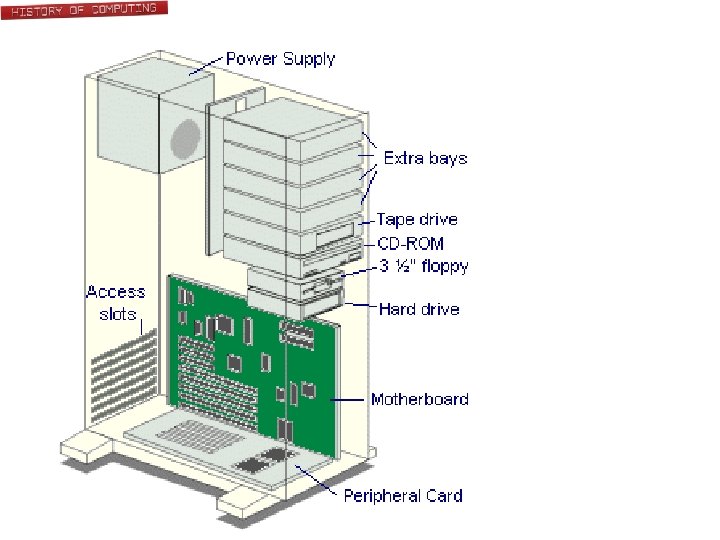

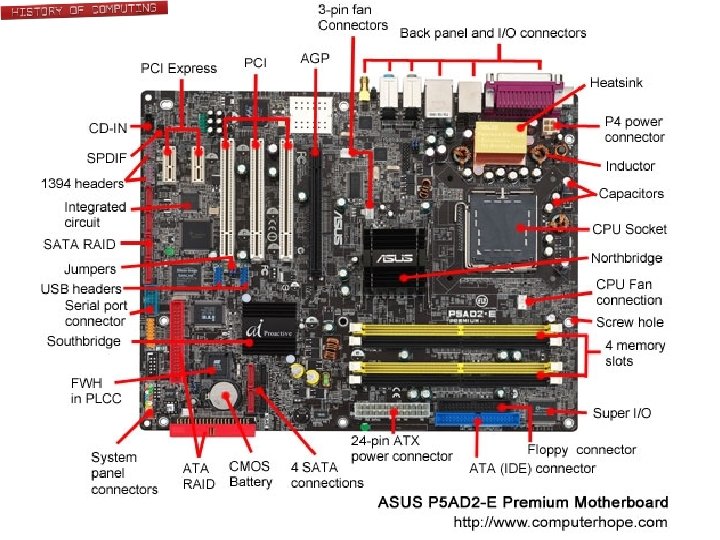

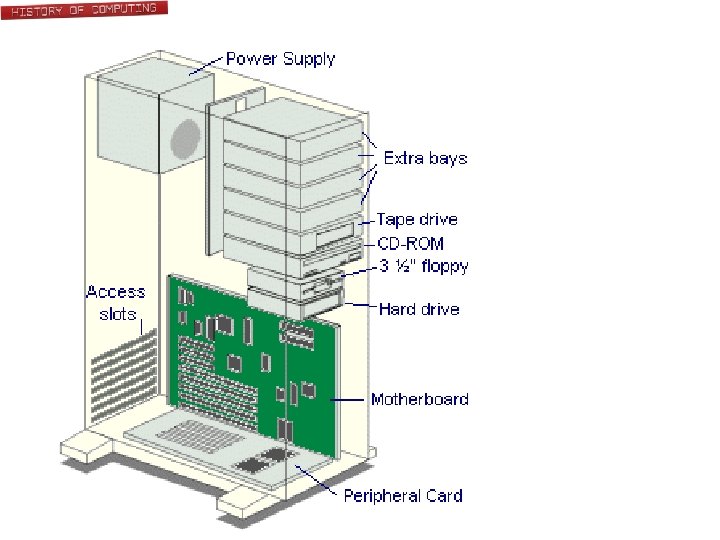

Identifying Components Motherboards

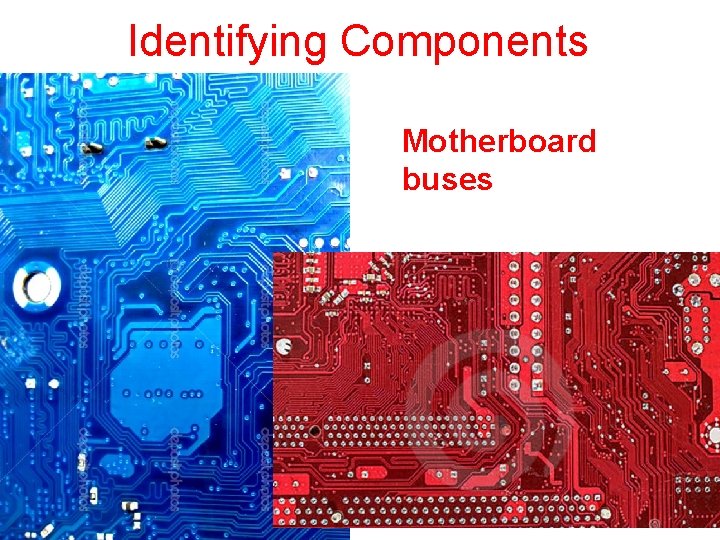

Identifying Components Motherboard buses

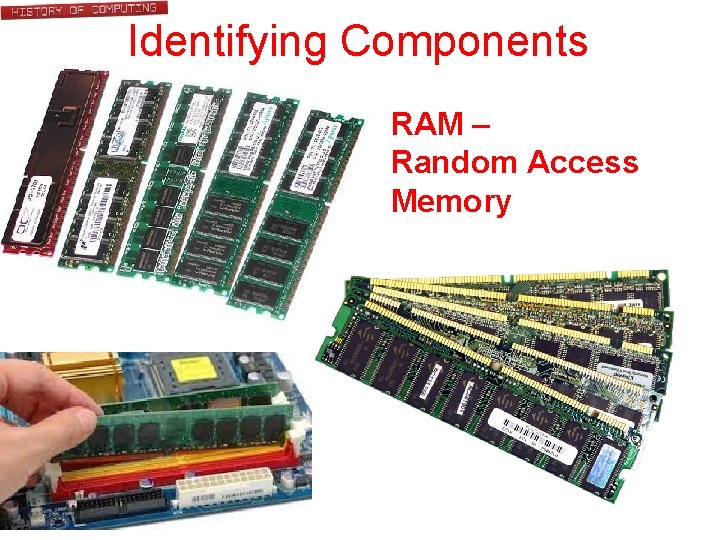

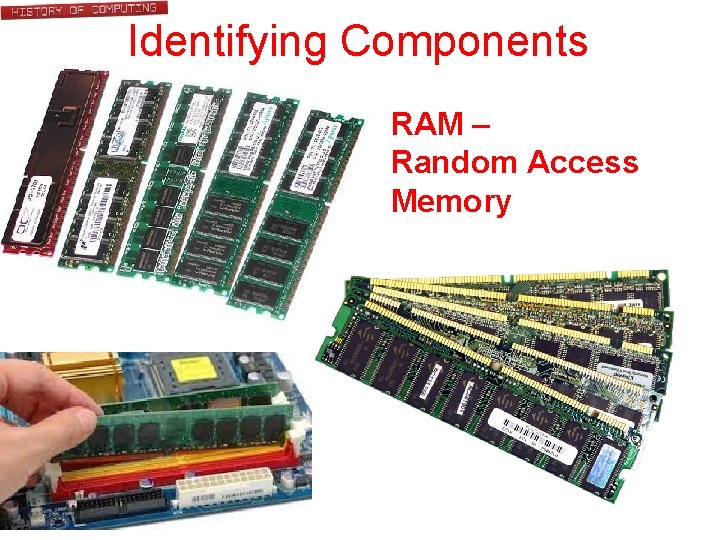

Identifying Components RAM – Random Access Memory

Identifying Components Hard Drives The History of Computing © London Grid for Learning www. HOC. lgfl. net

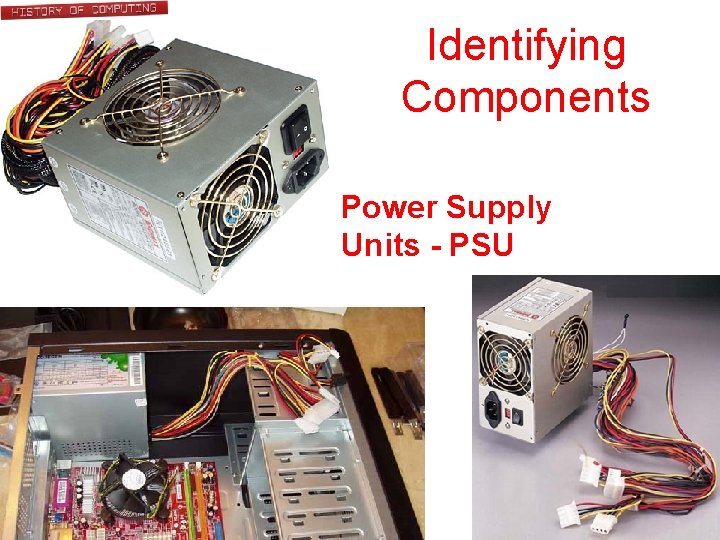

Identifying Components Power Supply Units - PSU