The DMA Controller Definition and Advantages Hardware Modes

![Closer look at Fly-By Signaling Net+ARM DRQ* DACK* DONE* R / W* DATA[31: 0] Closer look at Fly-By Signaling Net+ARM DRQ* DACK* DONE* R / W* DATA[31: 0]](https://slidetodoc.com/presentation_image_h2/3b3ef8ba01be9c30fd6b22c8f9465b6a/image-8.jpg)

- Slides: 11

The DMA Controller Definition and Advantages Hardware Modes Port A Special Function

What is DMA? • Direct Memory Access • Assists the movement of data between external memory and internal peripherals with minimal CPU intervention • An internal peripheral is assigned to one or more DMA channels. • Each channel moves data one direction. • It either receives incoming data or transmits outgoing data.

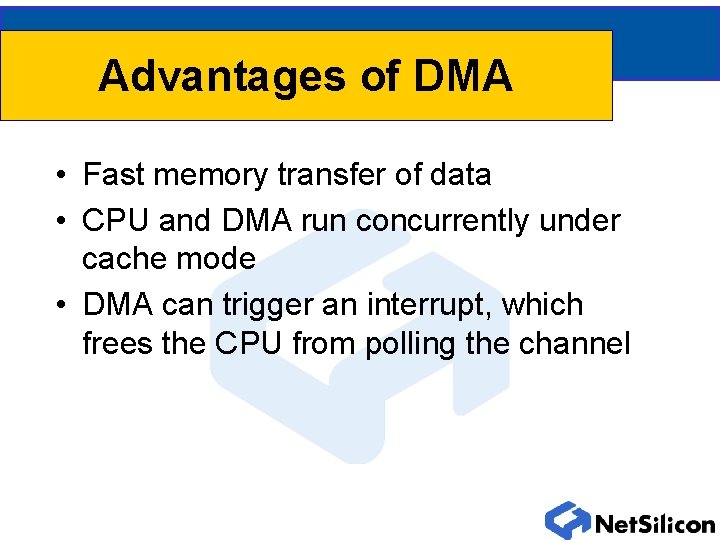

Advantages of DMA • Fast memory transfer of data • CPU and DMA run concurrently under cache mode • DMA can trigger an interrupt, which frees the CPU from polling the channel

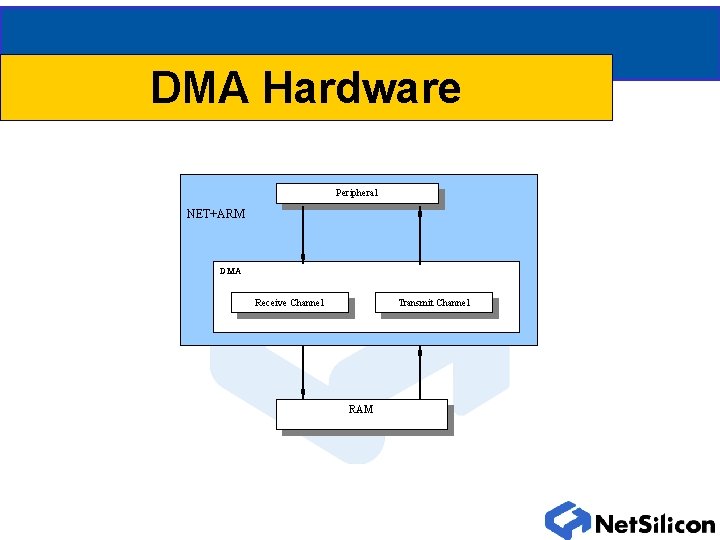

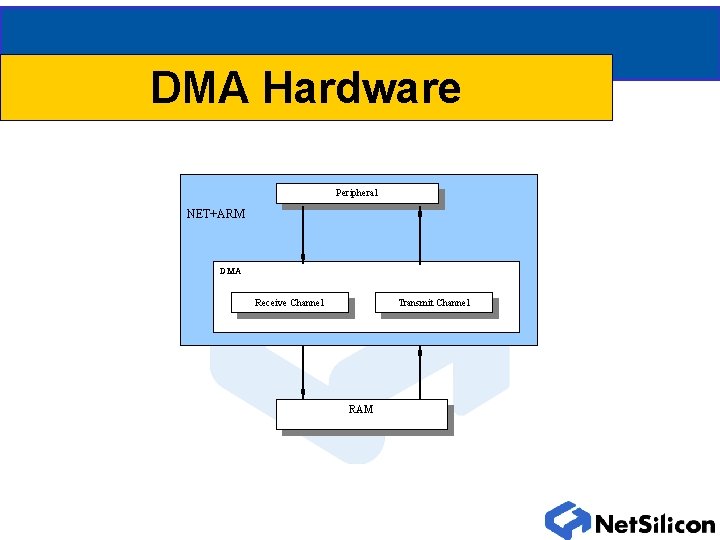

DMA Hardware Peripheral NET+ARM DMA Receive Channel Transmit Channel RAM

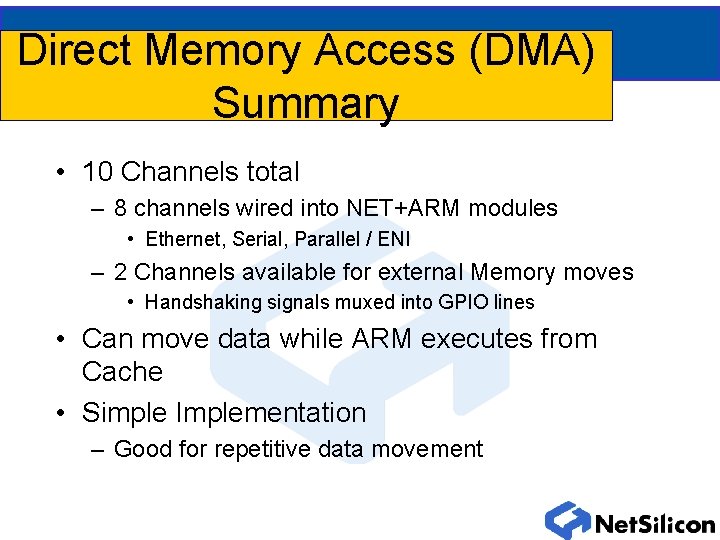

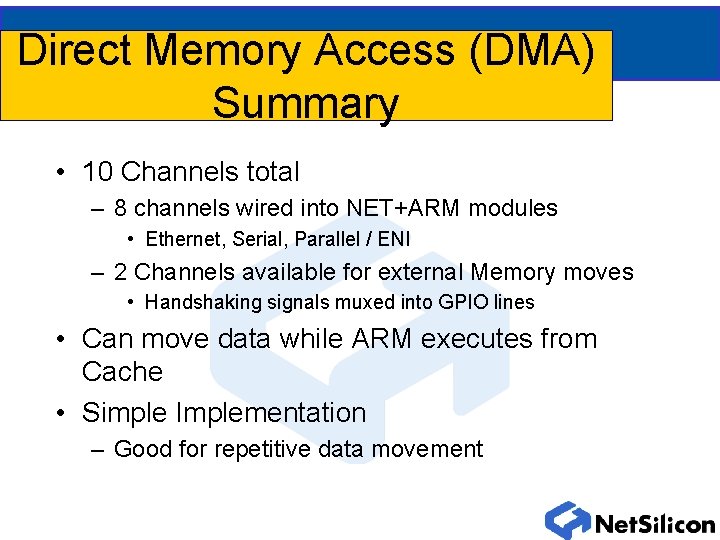

Direct Memory Access (DMA) Summary • 10 Channels total – 8 channels wired into NET+ARM modules • Ethernet, Serial, Parallel / ENI – 2 Channels available for external Memory moves • Handshaking signals muxed into GPIO lines • Can move data while ARM executes from Cache • Simple Implementation – Good for repetitive data movement

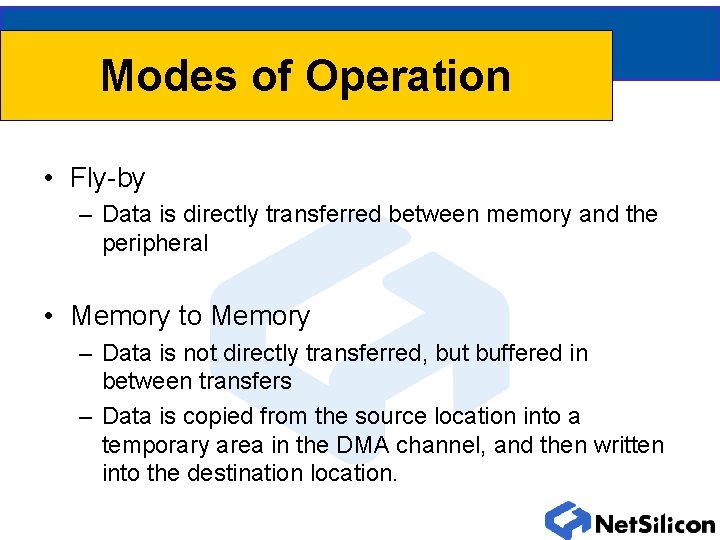

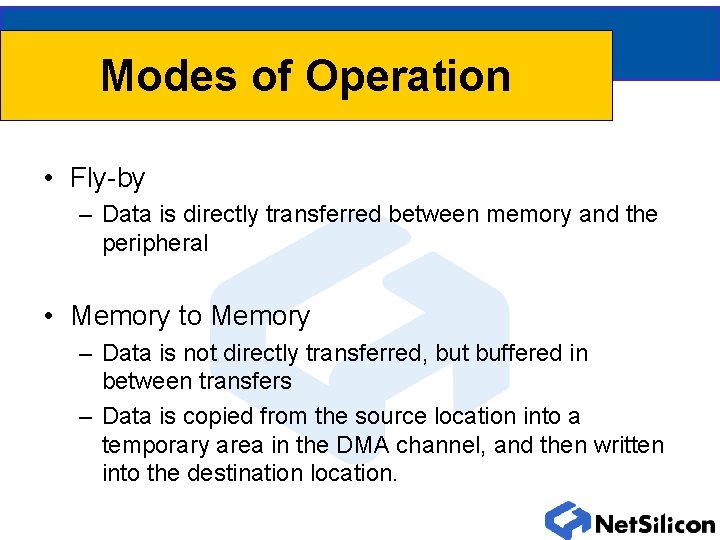

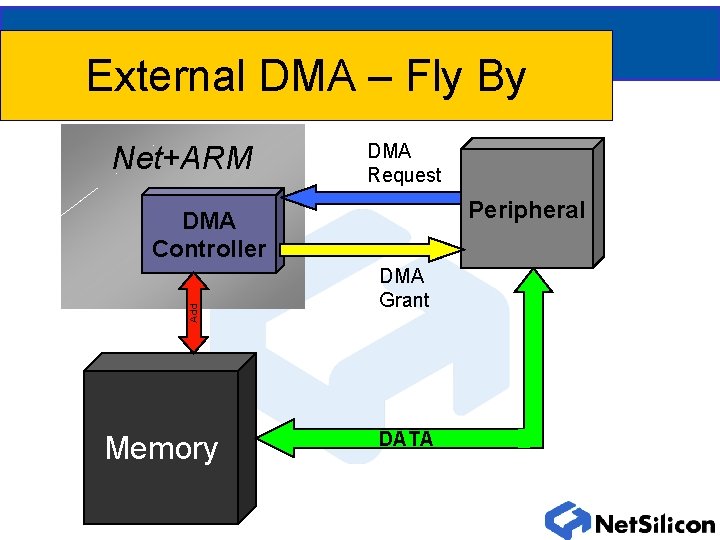

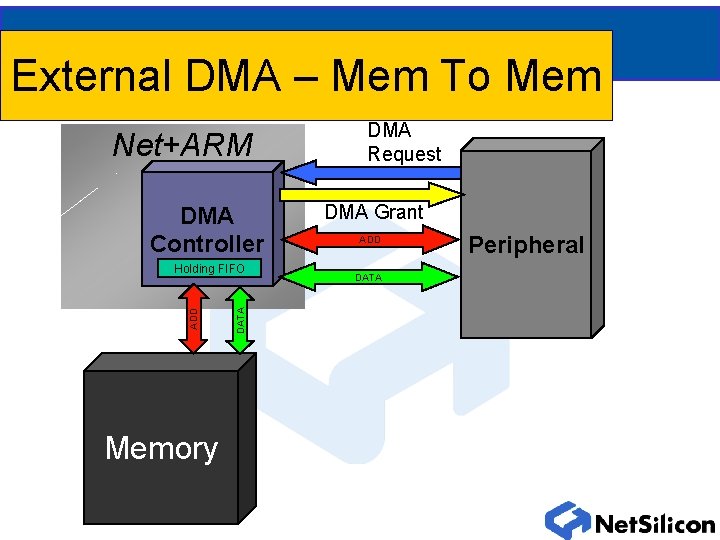

Modes of Operation • Fly-by – Data is directly transferred between memory and the peripheral • Memory to Memory – Data is not directly transferred, but buffered in between transfers – Data is copied from the source location into a temporary area in the DMA channel, and then written into the destination location.

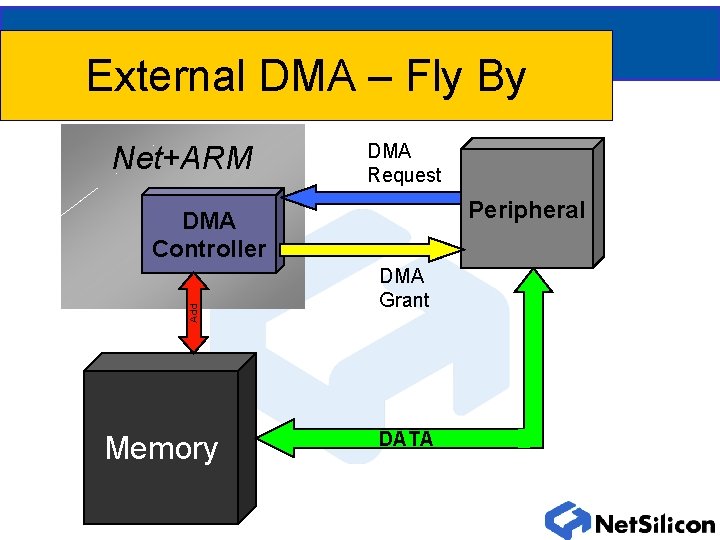

External DMA – Fly By Net+ARM DMA Request Peripheral Add DMA Controller Memory DMA Grant DATA

![Closer look at FlyBy Signaling NetARM DRQ DACK DONE R W DATA31 0 Closer look at Fly-By Signaling Net+ARM DRQ* DACK* DONE* R / W* DATA[31: 0]](https://slidetodoc.com/presentation_image_h2/3b3ef8ba01be9c30fd6b22c8f9465b6a/image-8.jpg)

Closer look at Fly-By Signaling Net+ARM DRQ* DACK* DONE* R / W* DATA[31: 0] ADDR[27: 0] CSx* Memory CS* ADDR[X: 0] DATA[31: 0] R / W* External Device DRQ* Enable Done Direction DATA[31: 0]

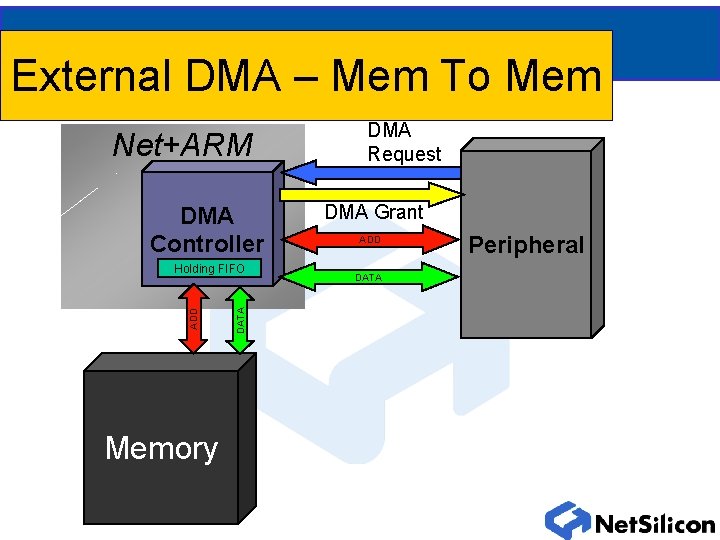

External DMA – Mem To Mem Net+ARM DMA Controller Memory DATA ADD Holding FIFO DMA Request DMA Grant ADD DATA Peripheral

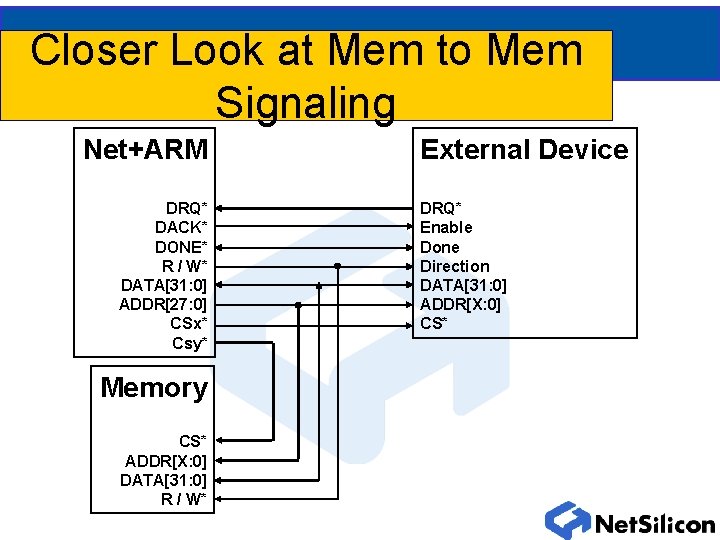

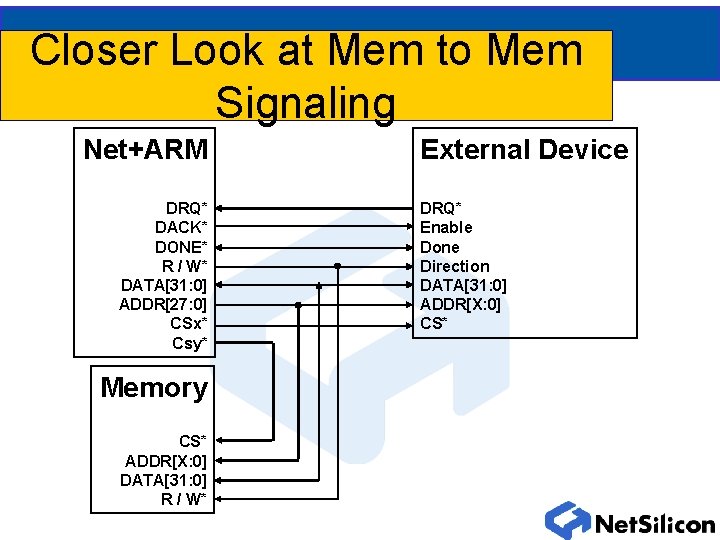

Closer Look at Mem to Mem Signaling Net+ARM DRQ* DACK* DONE* R / W* DATA[31: 0] ADDR[27: 0] CSx* Csy* Memory CS* ADDR[X: 0] DATA[31: 0] R / W* External Device DRQ* Enable Done Direction DATA[31: 0] ADDR[X: 0] CS*

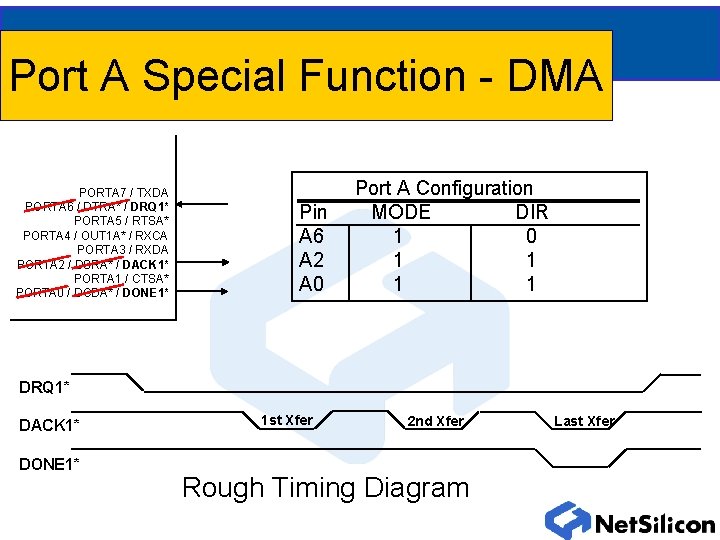

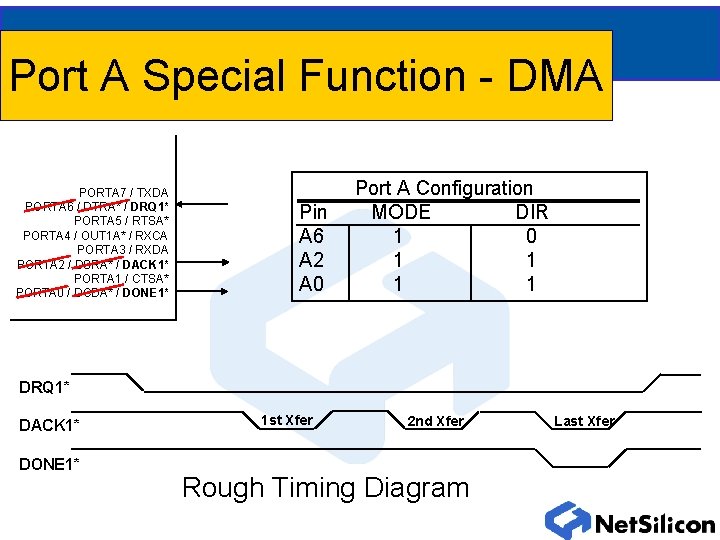

Port A Special Function - DMA PORTA 7 / TXDA PORTA 6 / DTRA* / DRQ 1* PORTA 5 / RTSA* PORTA 4 / OUT 1 A* / RXCA PORTA 3 / RXDA PORTA 2 / DSRA* / DACK 1* PORTA 1 / CTSA* PORTA 0 / DCDA* / DONE 1* Pin A 6 A 2 A 0 Port A Configuration MODE DIR 1 0 1 1 DRQ 1* DACK 1* DONE 1* 1 st Xfer 2 nd Xfer Rough Timing Diagram Last Xfer