The Data Handling Hybrid TUM Physics Department E

The Data Handling Hybrid TUM Physics Department E 18 I. Konorov

Overview • • DHH design SODA -Time Distribution system for PANDA Specification and Requirements Project schedule 8 -th March 2010 DEPFET meeting I. Konorov

DHH functionality 1. Power supplies 2. Slow control: voltages, currents, temperature, switching ON/OFF ladder power supply(? ) 3. Distribution of TRIGGER, RESET(? ) … signals 4. Generation of CLOCK signals 5. JTAG interface 6. DAQ functionality – – Receiving 4 data streams with up to 1 Gb/s Data buffering Subevent builder Data transfer to DAQ via high speed optical serial link 8 -th March 2010 DEPFET meeting I. Konorov

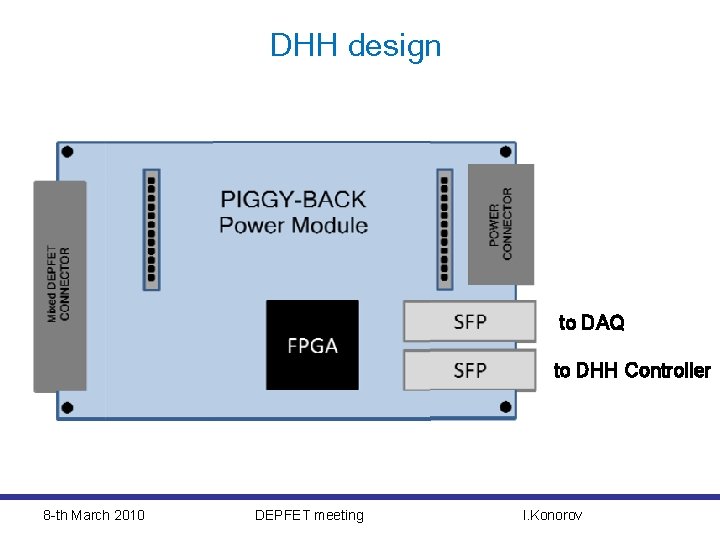

DHH design to DAQ to DHH Controller 8 -th March 2010 DEPFET meeting I. Konorov

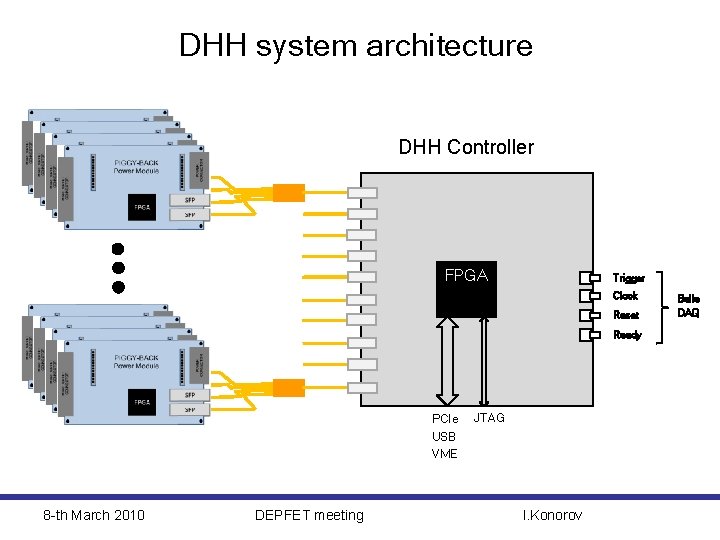

DHH system architecture DHH Controller FPGA Trigger Clock Reset Ready PCIe USB VME 8 -th March 2010 DEPFET meeting JTAG I. Konorov Belle DAQ

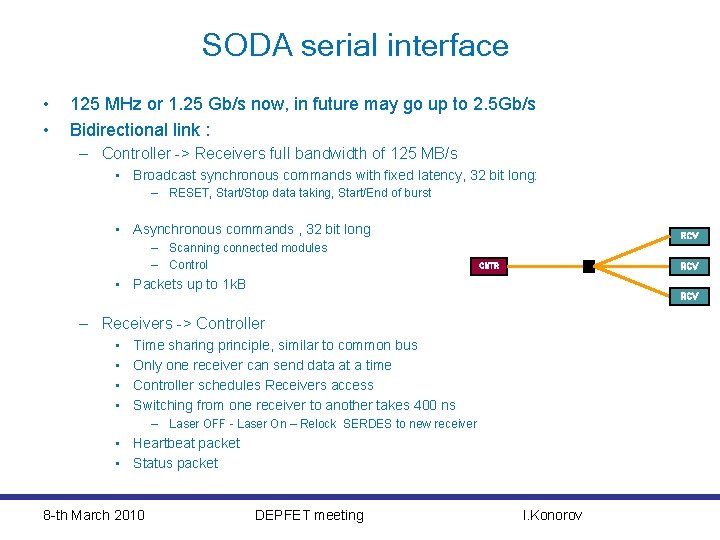

SODA serial interface • • 125 MHz or 1. 25 Gb/s now, in future may go up to 2. 5 Gb/s Bidirectional link : – Controller -> Receivers full bandwidth of 125 MB/s • Broadcast synchronous commands with fixed latency, 32 bit long: – RESET, Start/Stop data taking, Start/End of burst • Asynchronous commands , 32 bit long – Scanning connected modules – Control RCV CNTR RCV • Packets up to 1 k. B RCV – Receivers -> Controller • • Time sharing principle, similar to common bus Only one receiver can send data at a time Controller schedules Receivers access Switching from one receiver to another takes 400 ns – Laser OFF - Laser On – Relock SERDES to new receiver • Heartbeat packet • Status packet 8 -th March 2010 DEPFET meeting I. Konorov

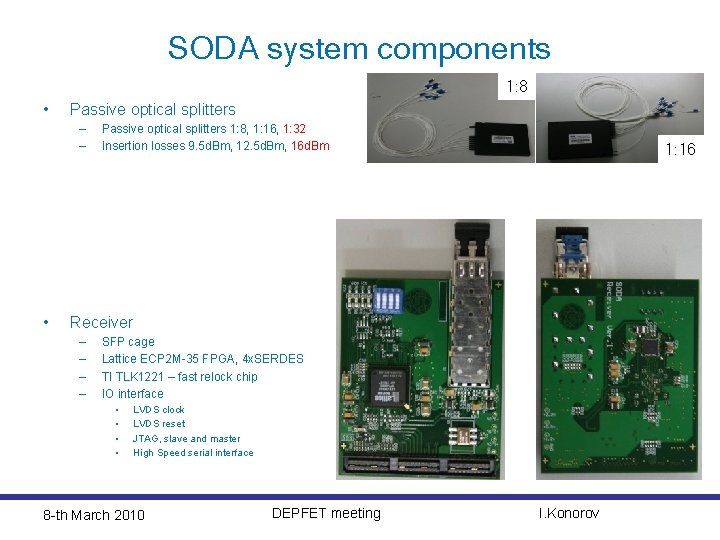

SODA system components 1: 8 • Passive optical splitters – – • Passive optical splitters 1: 8, 1: 16, 1: 32 Insertion losses 9. 5 d. Bm, 12. 5 d. Bm, 16 d. Bm 1: 16 Receiver – – SFP cage Lattice ECP 2 M-35 FPGA, 4 x. SERDES TI TLK 1221 – fast relock chip IO interface • • LVDS clock LVDS reset JTAG, slave and master High Speed serial interface 8 -th March 2010 DEPFET meeting I. Konorov

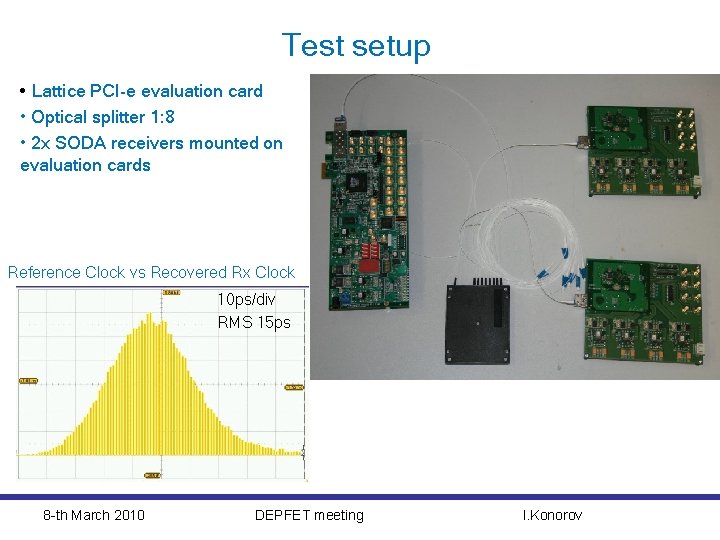

Test setup • Lattice PCI-e evaluation card • Optical splitter 1: 8 • 2 x SODA receivers mounted on evaluation cards Reference Clock vs Recovered Rx Clock 10 ps/div RMS 15 ps 8 -th March 2010 DEPFET meeting I. Konorov

DHH Requirements 1. Functionality • LV power supplies • Clock frequencies • Slow control – JTAG and monitoring • Data rate • Reliability requirements 2. Form factor and position 3. Connectors • Type • Pin assignment 4. Interface protocols 8 -th March 2010 DEPFET meeting I. Konorov

Time lines (preliminary) 1. Requirements and specification - 09. 2010 2. Prototype development - 03. 2011 3. Test, debugging, final specification - 01. 2012 4. Final prototype - 03. 2012 5. Final production - 09. 2012 8 -th March 2010 DEPFET meeting I. Konorov

- Slides: 10