The Data Handling Hybrid TUM Physics Department E

The Data Handling Hybrid TUM Physics Department E 18 I. Konorov

Overview • DHH functionality • SODA -Time Distribution system for PANDA • DHH design 22 -d April 2010 Workshop PXD-DAQ I. Konorov

DHH functionality 1. Voltage regulators 2. Slow control: Provision of JTAG interface to configure PXD Provision of slow control interface to configure DHH cards Monitoring voltages, currents, temperature 1. CLOCK synthesis from COMMON clock and distribution 2. DAQ functionality – – Synchronous distribution of TRIGGER, RESET(? ), … signals Data buffering : 4 x 1 Gb/sec Sub event building : merging 4 data blocks into one Transmission of merged data to DAQ via high speed optical serial link 22 -d April 2010 Workshop PXD-DAQ I. Konorov

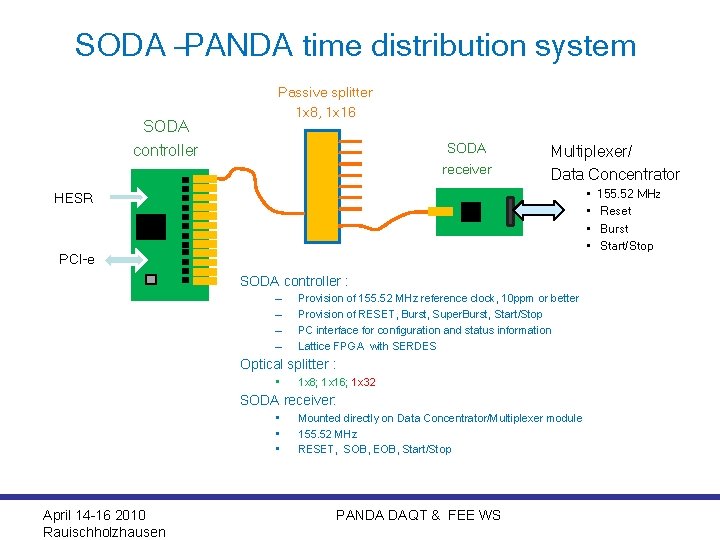

SODA –PANDA time distribution system SODA controller Passive splitter 1 x 8, 1 x 16 SODA receiver Multiplexer/ Data Concentrator • • HESR PCI-e SODA controller : – – Provision of 155. 52 MHz reference clock, 10 ppm or better Provision of RESET, Burst, Super. Burst, Start/Stop PC interface for configuration and status information Lattice FPGA with SERDES Optical splitter : • 1 x 8; 1 x 16; 1 x 32 SODA receiver: • • • April 14 -16 2010 Rauischholzhausen Mounted directly on Data Concentrator/Multiplexer module 155. 52 MHz RESET, SOB, EOB, Start/Stop PANDA DAQT & FEE WS 155. 52 MHz Reset Burst Start/Stop

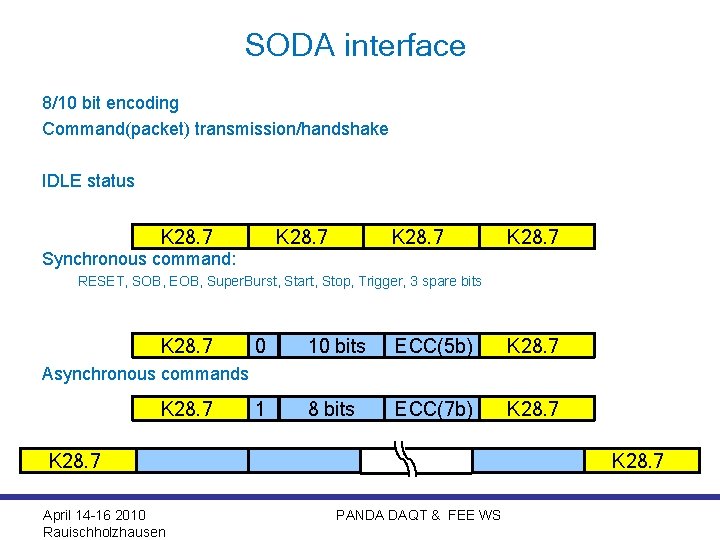

SODA interface 8/10 bit encoding Command(packet) transmission/handshake IDLE status K 28. 7 Synchronous command: RESET, SOB, EOB, Super. Burst, Start, Stop, Trigger, 3 spare bits K 28. 7 0 10 bits ECC(5 b) K 28. 7 1 8 bits ECC(7 b) K 28. 7 Asynchronous commands K 28. 7 April 14 -16 2010 Rauischholzhausen K 28. 7 PANDA DAQT & FEE WS

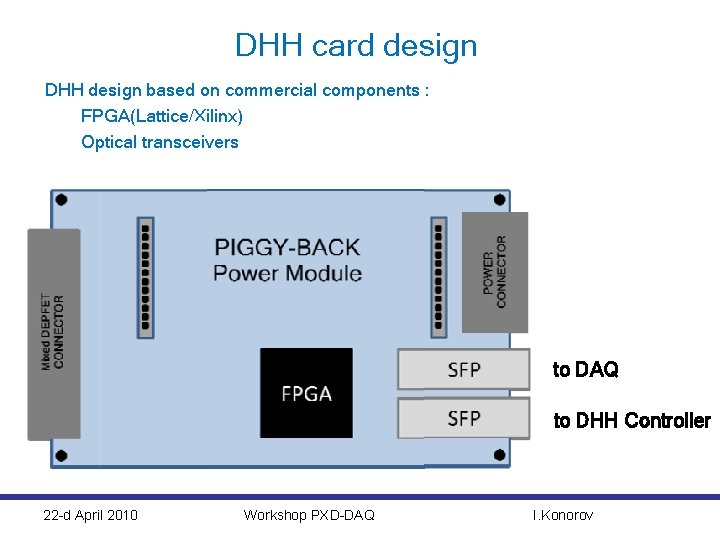

DHH card design DHH design based on commercial components : FPGA(Lattice/Xilinx) Optical transceivers to DAQ to DHH Controller 22 -d April 2010 Workshop PXD-DAQ I. Konorov

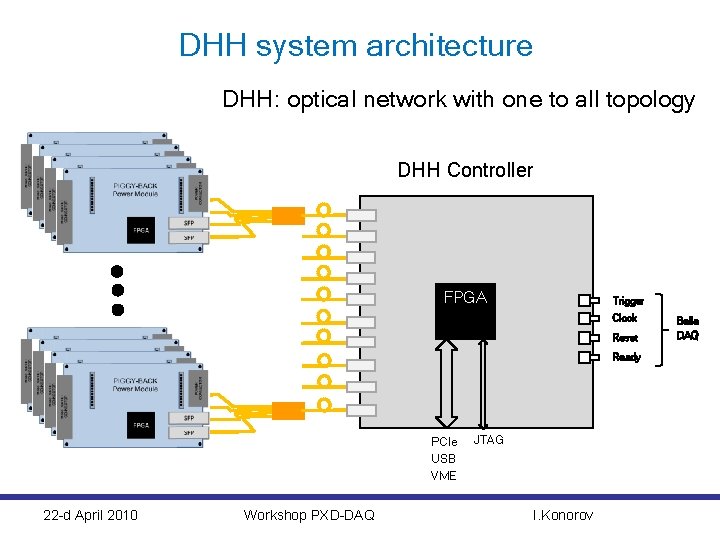

DHH system architecture DHH: optical network with one to all topology DHH Controller FPGA Trigger Clock Reset Ready PCIe USB VME 22 -d April 2010 Workshop PXD-DAQ JTAG I. Konorov Belle DAQ

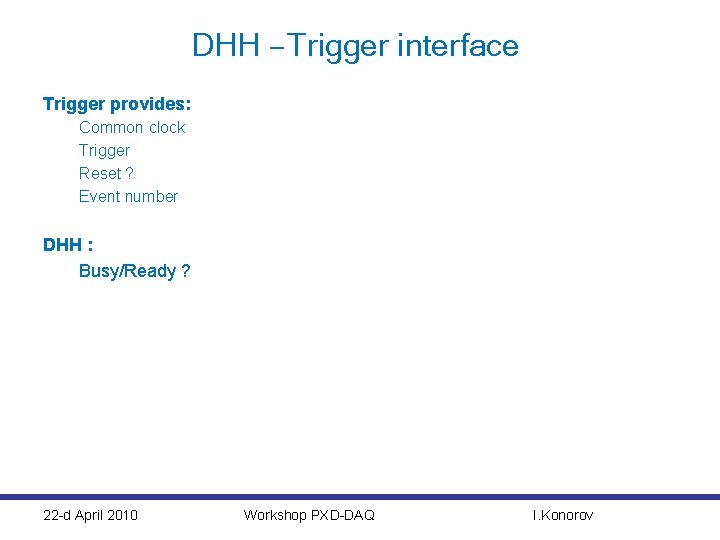

DHH – Trigger interface Trigger provides: Common clock Trigger Reset ? Event number DHH : Busy/Ready ? 22 -d April 2010 Workshop PXD-DAQ I. Konorov

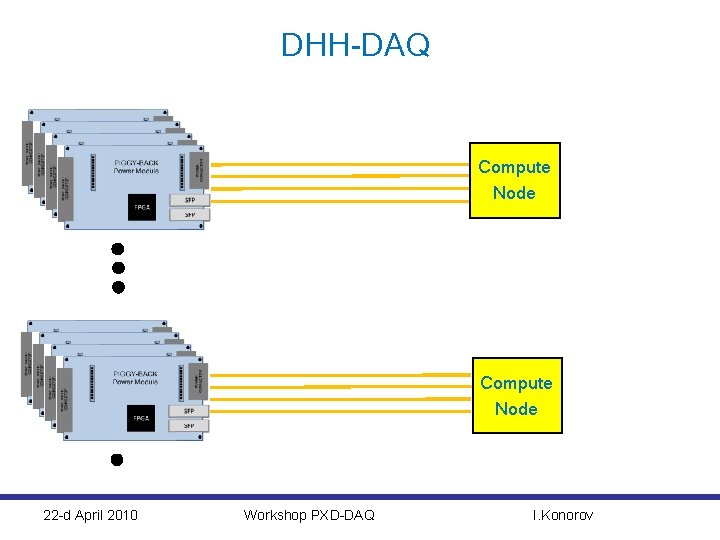

DHH-DAQ Compute Node 22 -d April 2010 Workshop PXD-DAQ I. Konorov

PXD-DHH-DAQ interface • PXD => DHH – – 4 copper serial links, 1 Gb/s each Aurora protocol, 8/10 bit encoding One data block is one or more events Average network bandwidth utilization – 80 -90% • DHH => DAQ – 4 Gb/s or 2 x 3 Gb/s – “Sub event” building 22 -d April 2010 Workshop PXD-DAQ I. Konorov

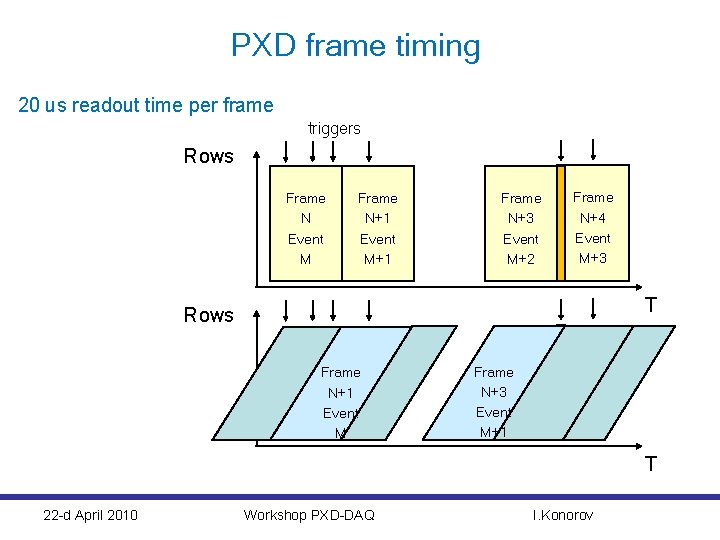

PXD frame timing 20 us readout time per frame triggers Rows Frame N Event M Frame N+1 Event M+1 Frame N+3 Event M+2 Frame N+4 Event M+3 T Rows Frame N+1 Event M Frame N+3 Event M+1 T 22 -d April 2010 Workshop PXD-DAQ I. Konorov

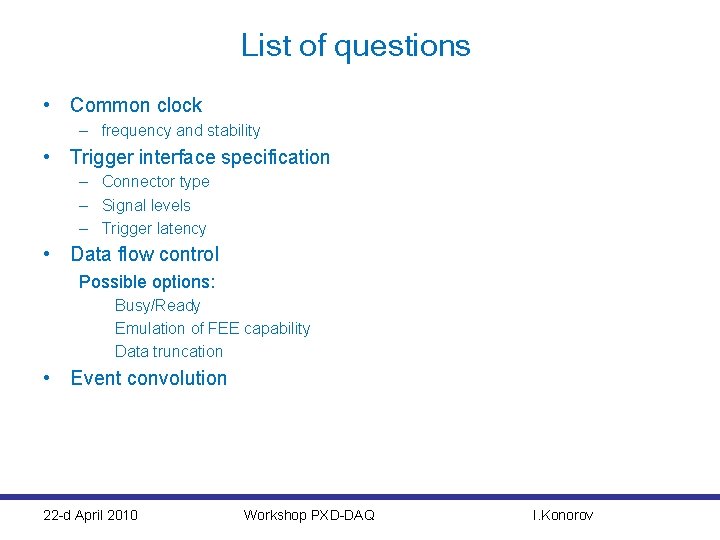

List of questions • Common clock – frequency and stability • Trigger interface specification – Connector type – Signal levels – Trigger latency • Data flow control Possible options: Busy/Ready Emulation of FEE capability Data truncation • Event convolution 22 -d April 2010 Workshop PXD-DAQ I. Konorov

- Slides: 12