The CMOS Inverter Lecture 3 Static properties VTC

- Slides: 28

The CMOS Inverter Lecture 3 Static properties (VTC and noise margins)

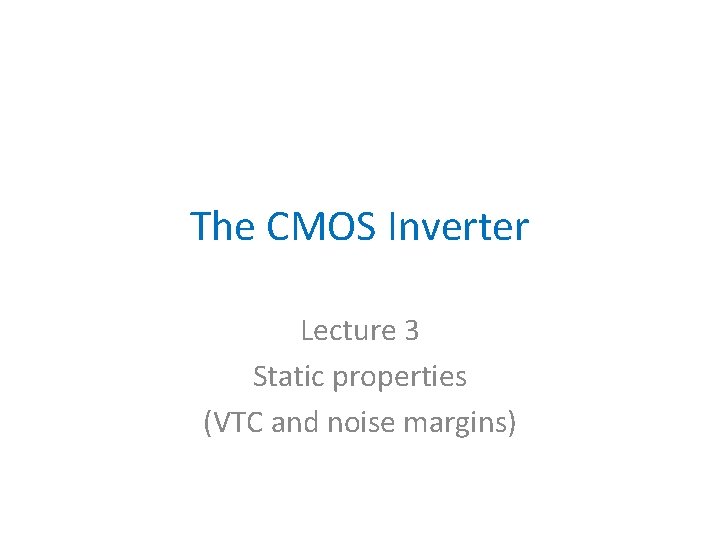

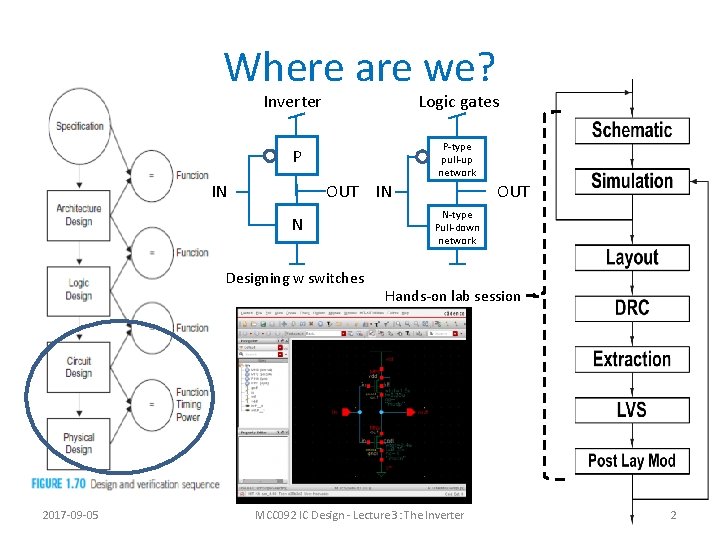

Where are we? Inverter Logic gates P-type pull-up network P OUT IN IN N Designing w switches 2017 -09 -05 OUT N-type Pull-down network Hands-on lab session MCC 092 IC Design - Lecture 3: The Inverter 2

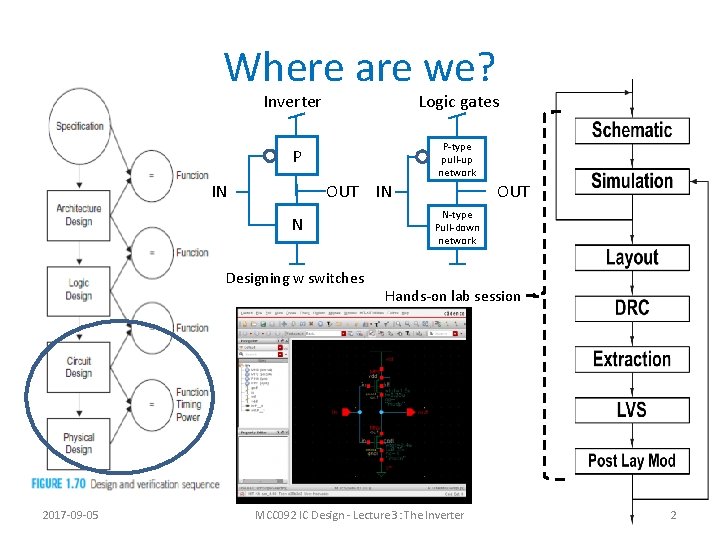

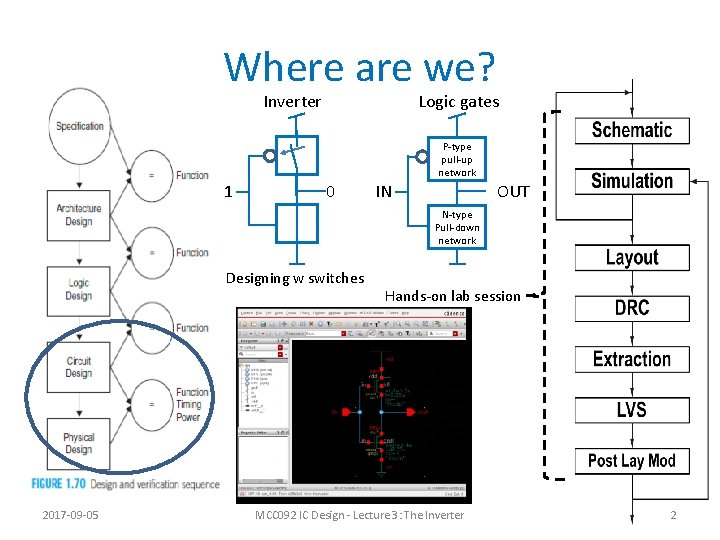

Where are we? Inverter Logic gates P-type pull-up network 1 0 OUT IN N-type Pull-down network Designing w switches 2017 -09 -05 Hands-on lab session MCC 092 IC Design - Lecture 3: The Inverter 2

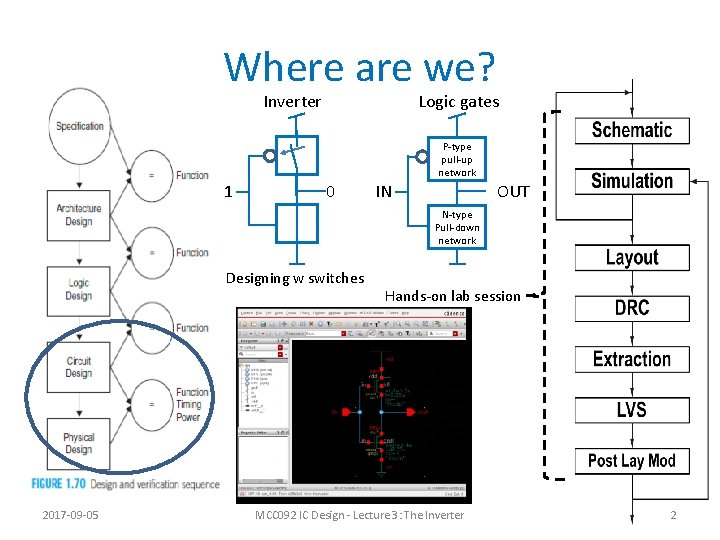

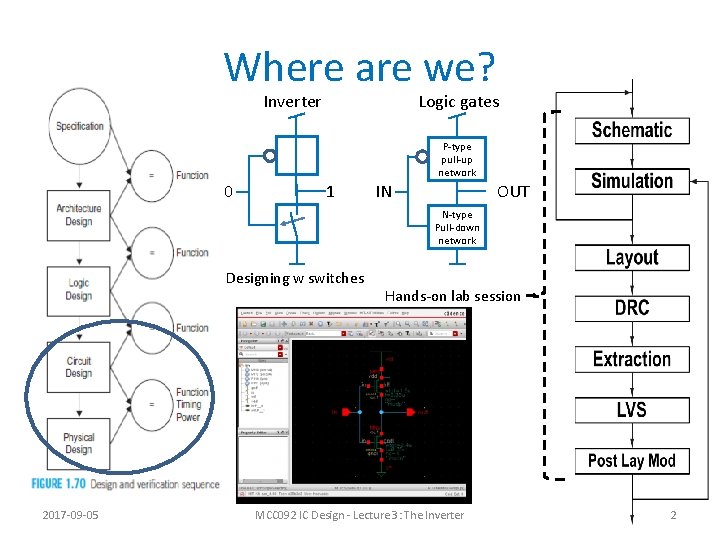

Where are we? Inverter Logic gates P-type pull-up network 0 1 OUT IN N-type Pull-down network Designing w switches 2017 -09 -05 Hands-on lab session MCC 092 IC Design - Lecture 3: The Inverter 2

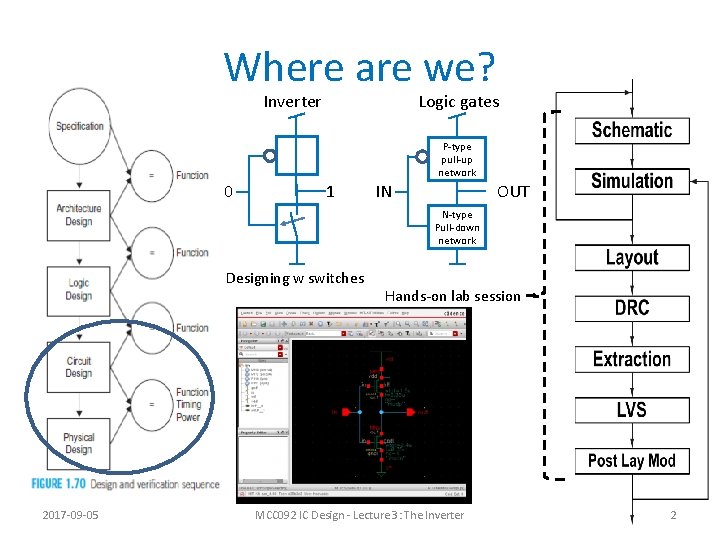

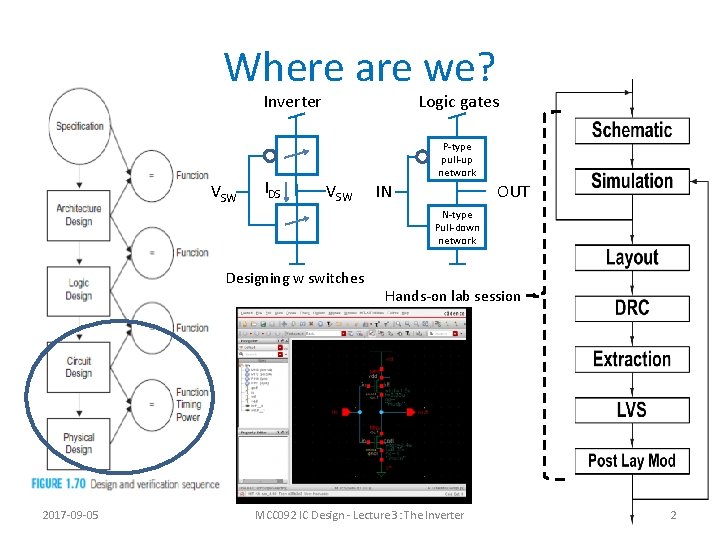

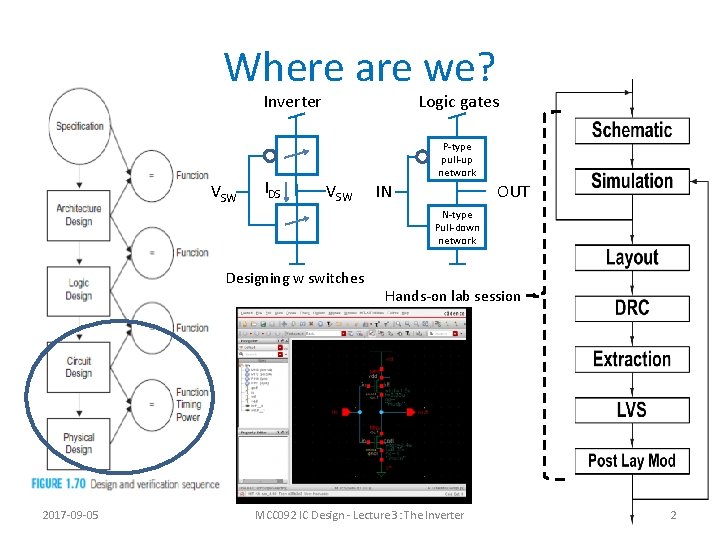

Where are we? Inverter VSW IDS Logic gates P-type pull-up network VSW OUT IN N-type Pull-down network Designing w switches 2017 -09 -05 Hands-on lab session MCC 092 IC Design - Lecture 3: The Inverter 2

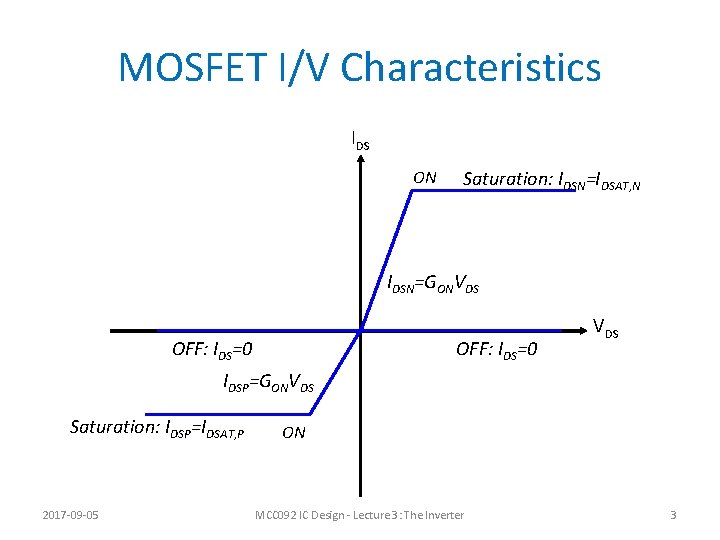

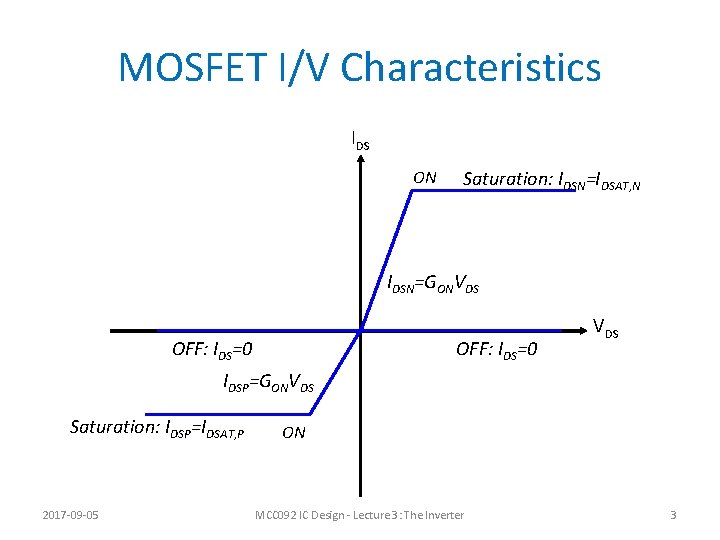

MOSFET I/V Characteristics IDS ON Saturation: IDSN=IDSAT, N IDSN=GONVDS OFF: IDS=0 VDS IDSP=GONVDS Saturation: IDSP=IDSAT, P 2017 -09 -05 ON MCC 092 IC Design - Lecture 3: The Inverter 3

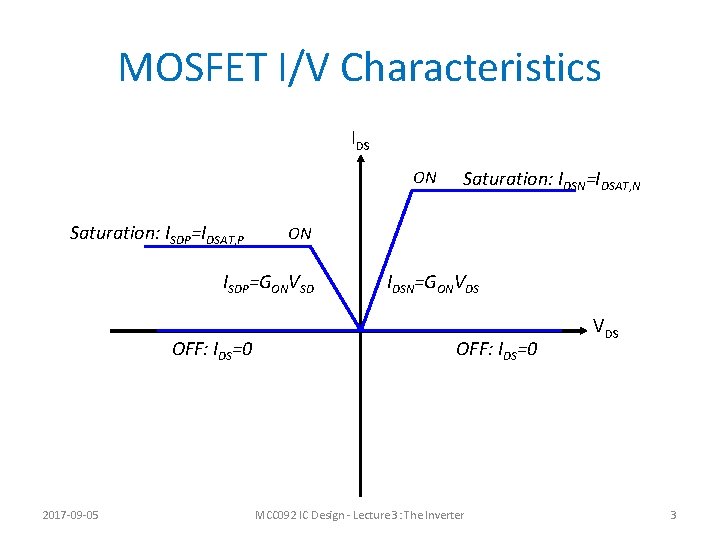

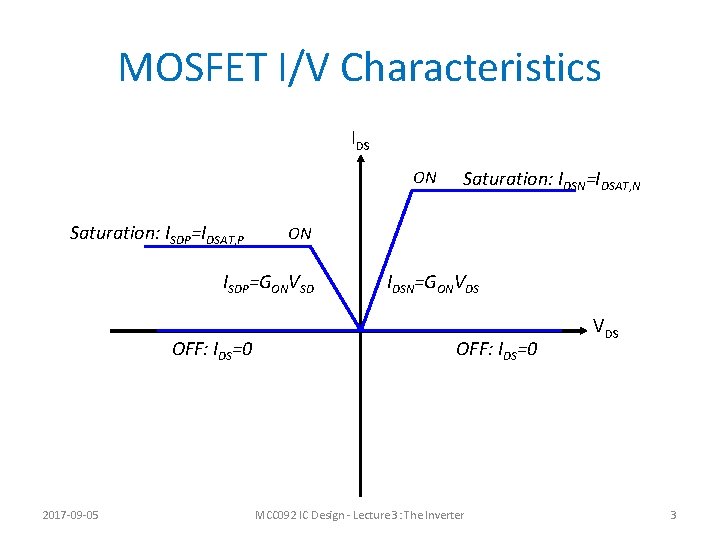

MOSFET I/V Characteristics IDS ON Saturation: ISDP=IDSAT, P ON ISDP=GONVSD OFF: IDS=0 2017 -09 -05 Saturation: IDSN=IDSAT, N IDSN=GONVDS OFF: IDS=0 MCC 092 IC Design - Lecture 3: The Inverter VDS 3

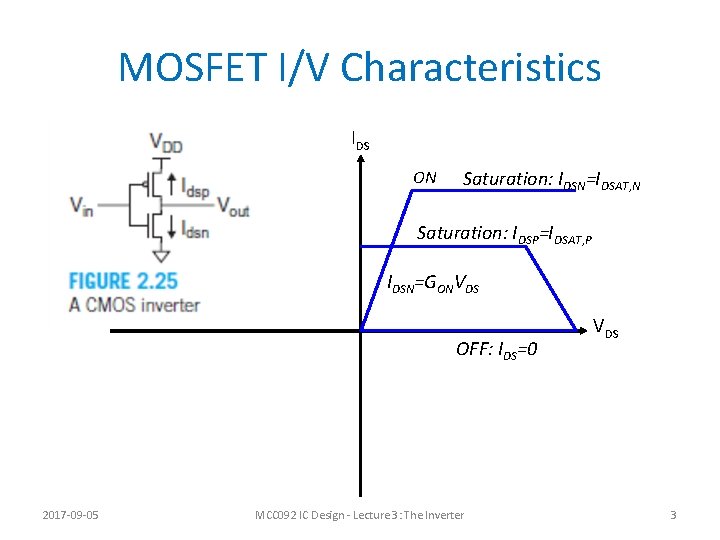

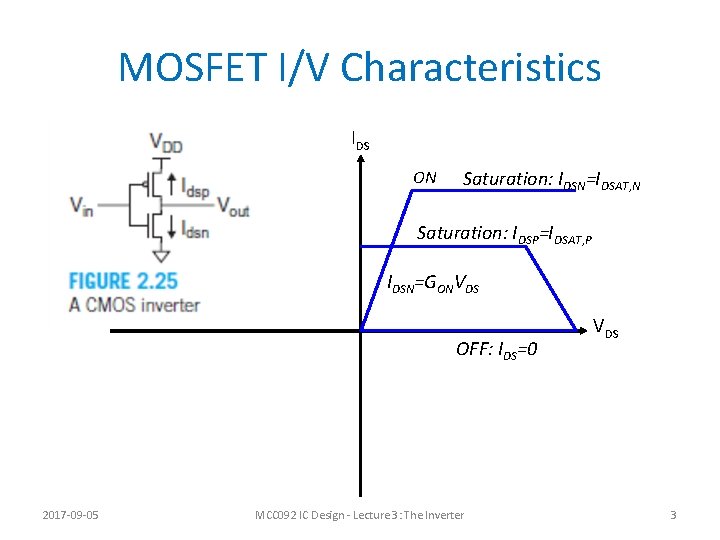

MOSFET I/V Characteristics IDS ON Saturation: IDSN=IDSAT, N Saturation: IDSP=IDSAT, P IDSN=GONVDS OFF: IDS=0 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter VDS 3

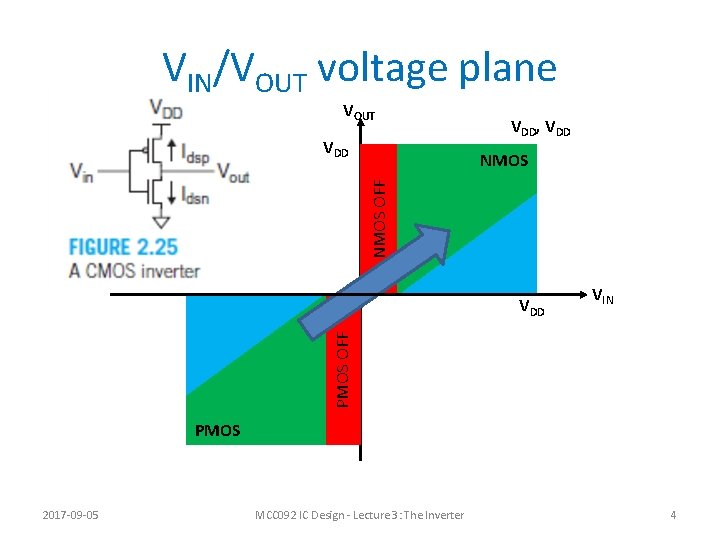

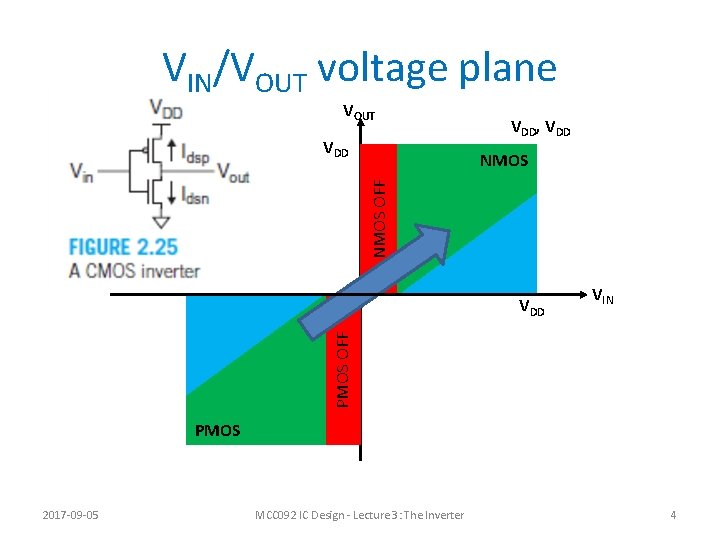

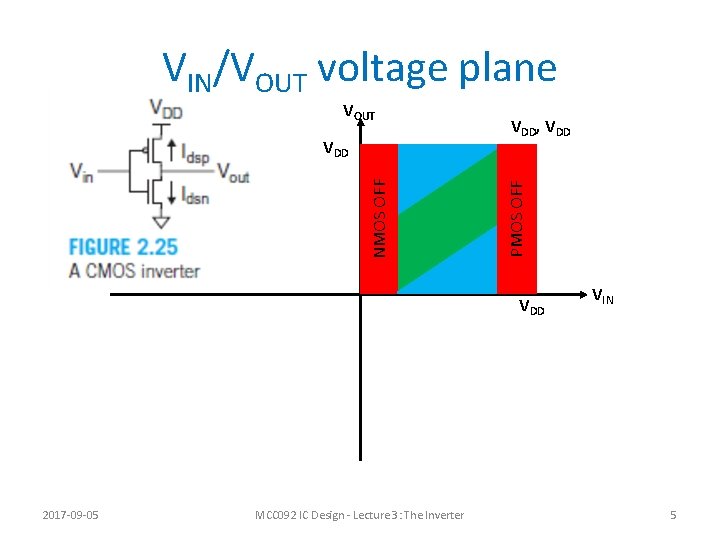

VIN/VOUT voltage plane VOUT VDD, VDD NMOS OFF NMOS VIN PMOS OFF VDD PMOS 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter 4

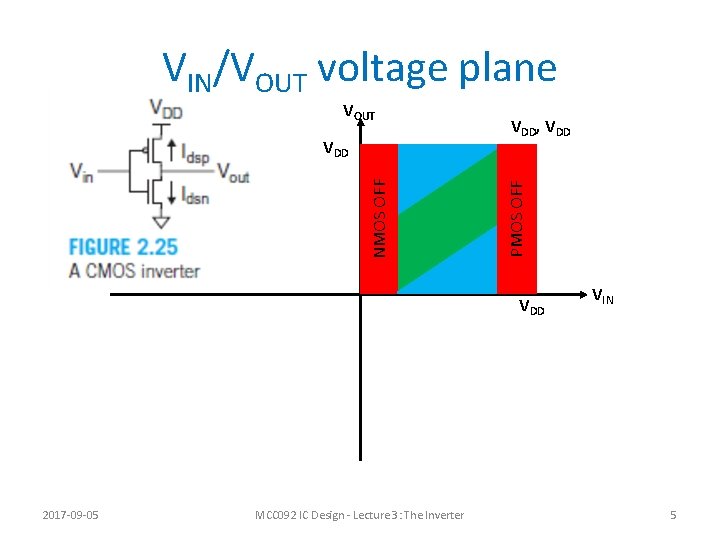

VIN/VOUT voltage plane NMOS OFF VDD, VDD PMOS OFF VOUT VDD 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter VIN 5

Voltage Transfer Characteristic - VTC Inverter VDD 0 NMOS OFF IDS, P=0 1 IDS, N=0 VDD, VDD PMOS OFF VOUT IDS VDD VIN The ON p-switch pulls the output high VDS 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter 6: 1

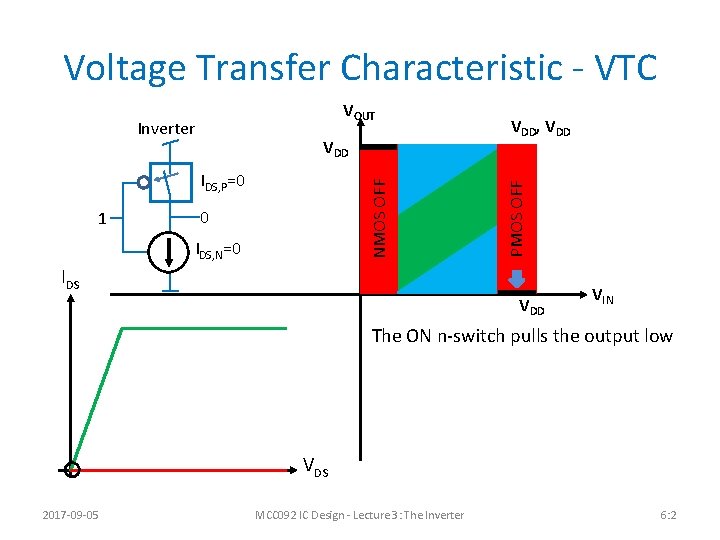

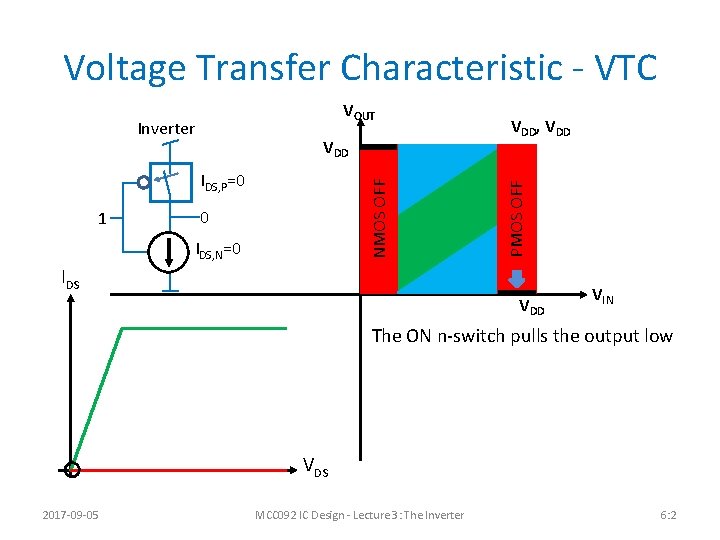

Voltage Transfer Characteristic - VTC Inverter VDD 1 NMOS OFF IDS, P=0 0 IDS, N=0 VDD, VDD PMOS OFF VOUT IDS VDD VIN The ON n-switch pulls the output low VDS 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter 6: 2

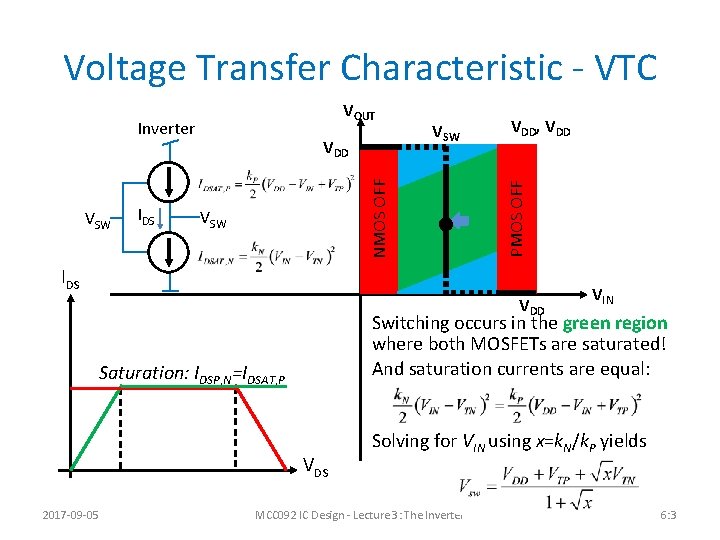

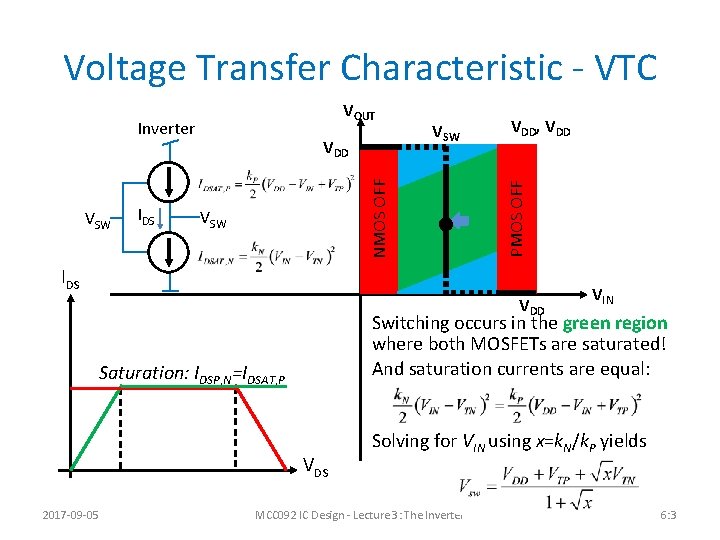

Voltage Transfer Characteristic - VTC Inverter IDS NMOS OFF VSW VDD, VDD PMOS OFF VOUT IDS VDD Switching occurs in the green region where both MOSFETs are saturated! And saturation currents are equal: Saturation: IDSP, N=IDSAT, P VDS 2017 -09 -05 VIN Solving for VIN using x=k. N/k. P yields MCC 092 IC Design - Lecture 3: The Inverter 6: 3

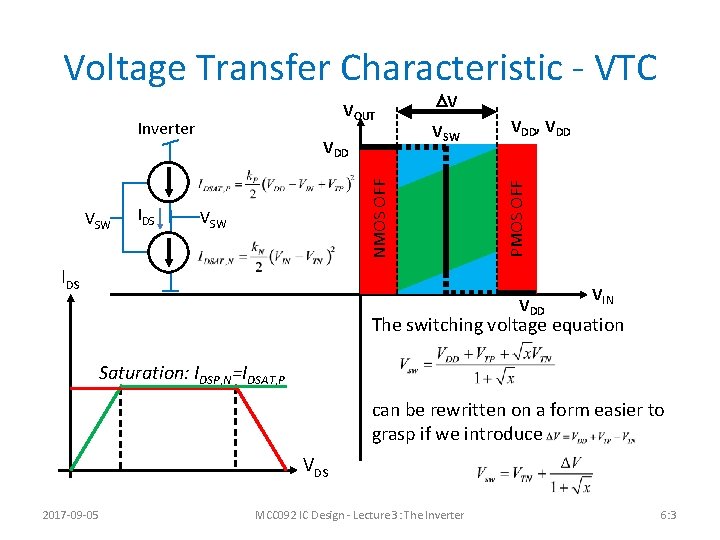

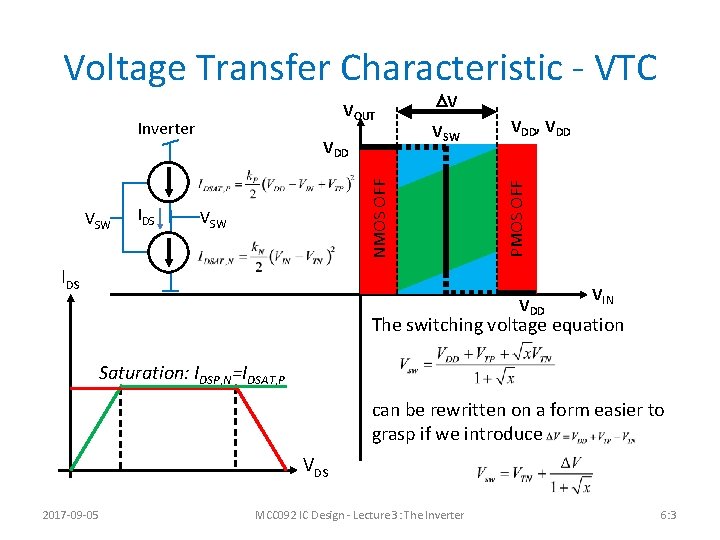

Voltage Transfer Characteristic - VTC Inverter IDS VSW NMOS OFF VSW VDD DV VSW VDD, VDD PMOS OFF VOUT IDS VDD VIN The switching voltage equation Saturation: IDSP, N=IDSAT, P can be rewritten on a form easier to grasp if we introduce VDS 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter 6: 3

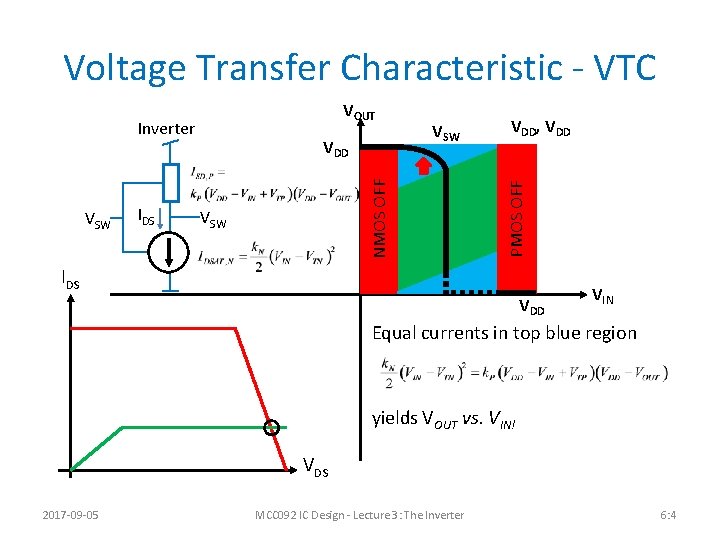

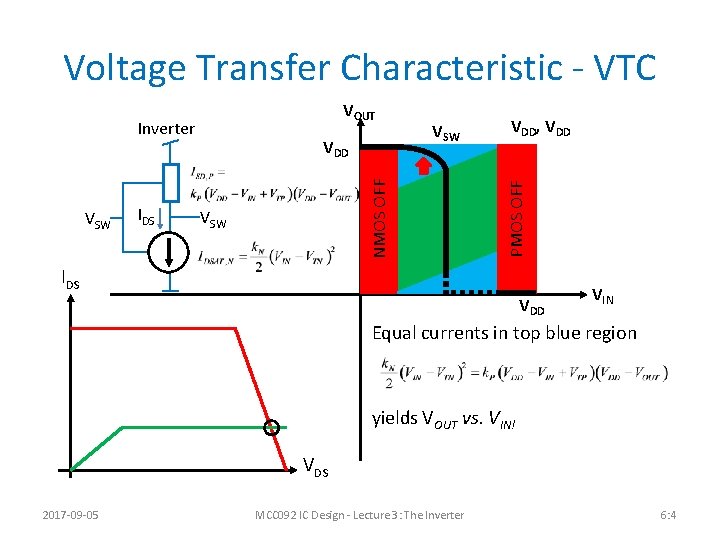

Voltage Transfer Characteristic - VTC Inverter IDS NMOS OFF VSW VDD, VDD PMOS OFF VOUT IDS VDD VIN Equal currents in top blue region yields VOUT vs. VIN! VDS 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter 6: 4

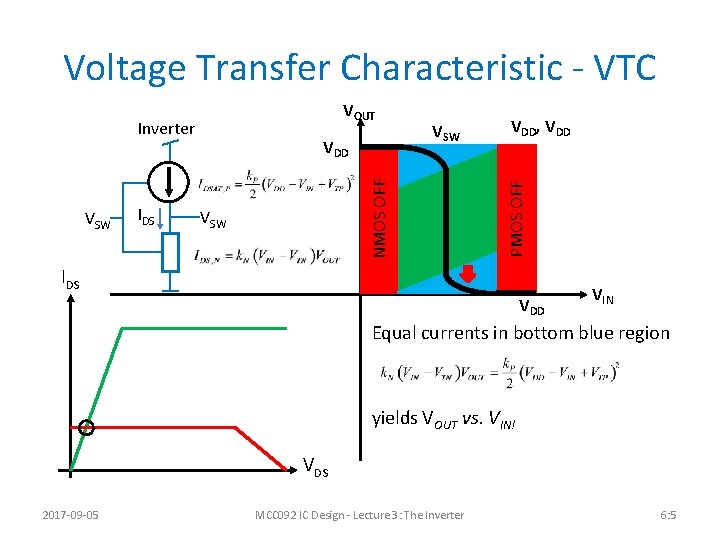

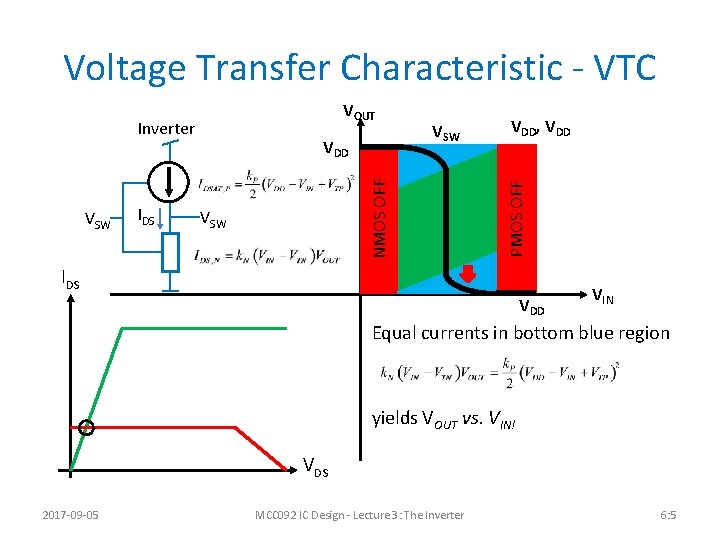

Voltage Transfer Characteristic - VTC Inverter IDS NMOS OFF VSW VDD, VDD PMOS OFF VOUT IDS VDD VIN Equal currents in bottom blue region yields VOUT vs. VIN! VDS 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter 6: 5

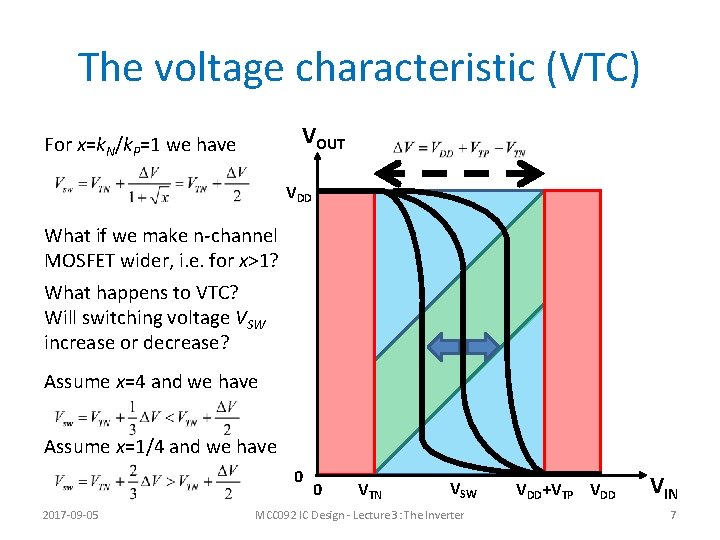

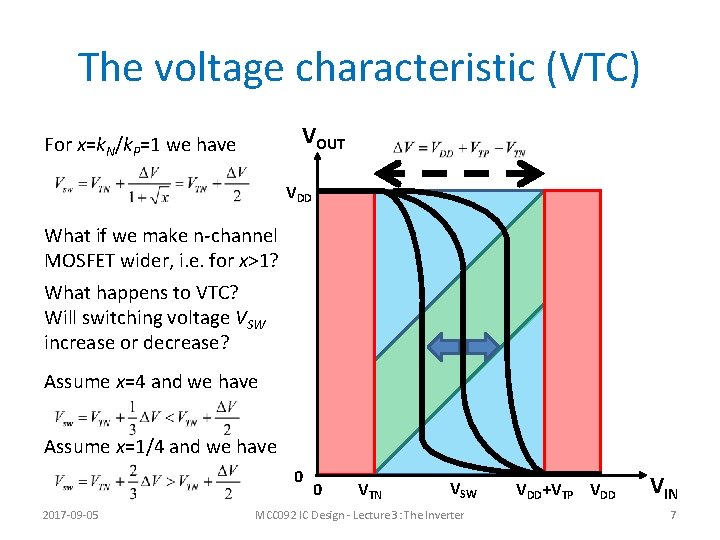

The voltage characteristic (VTC) VOUT For x=k. N/k. P=1 we have VDD What if we make n-channel MOSFET wider, i. e. for x>1? What happens to VTC? Will switching voltage VSW increase or decrease? Assume x=4 and we have Assume x=1/4 and we have 0 2017 -09 -05 0 VTN VSW MCC 092 IC Design - Lecture 3: The Inverter VDD+VTP VDD VIN 7

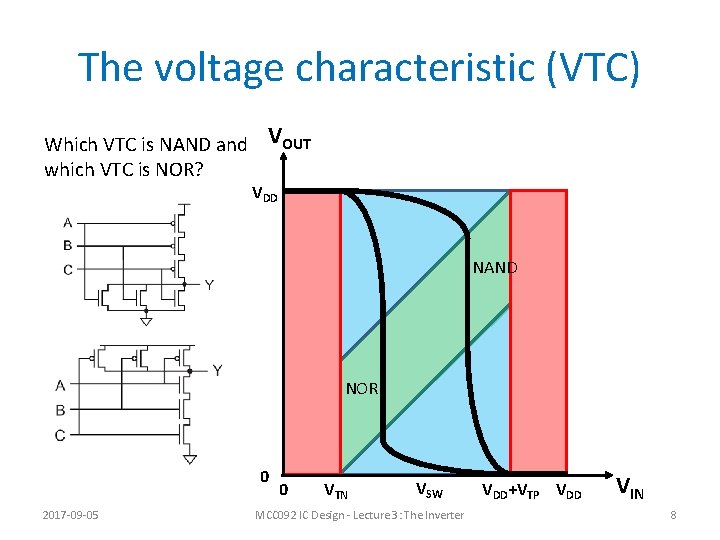

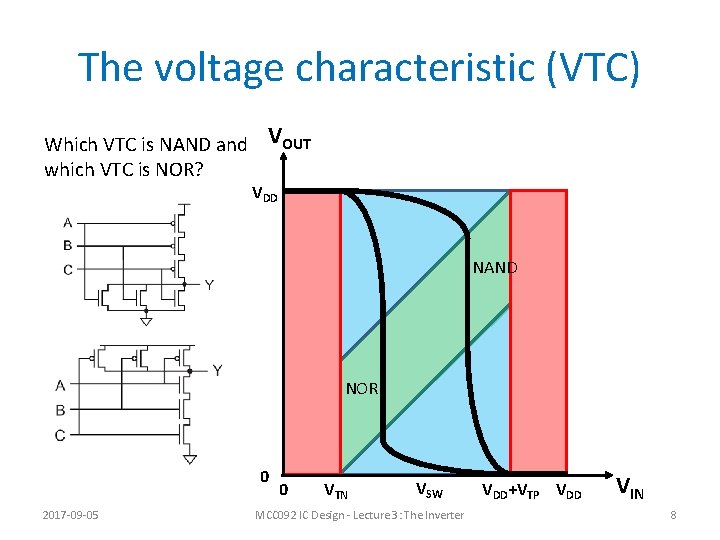

The voltage characteristic (VTC) Which VTC is NAND and VOUT which VTC is NOR? VDD NAND NOR 0 2017 -09 -05 0 VTN VSW MCC 092 IC Design - Lecture 3: The Inverter VDD+VTP VDD VIN 8

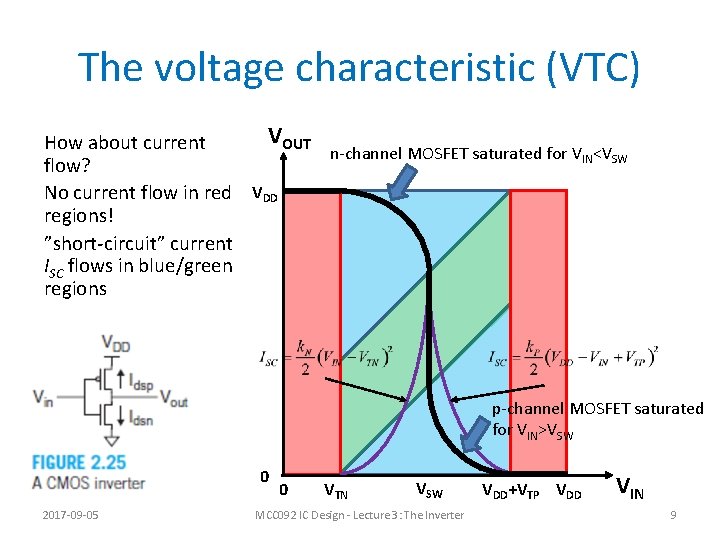

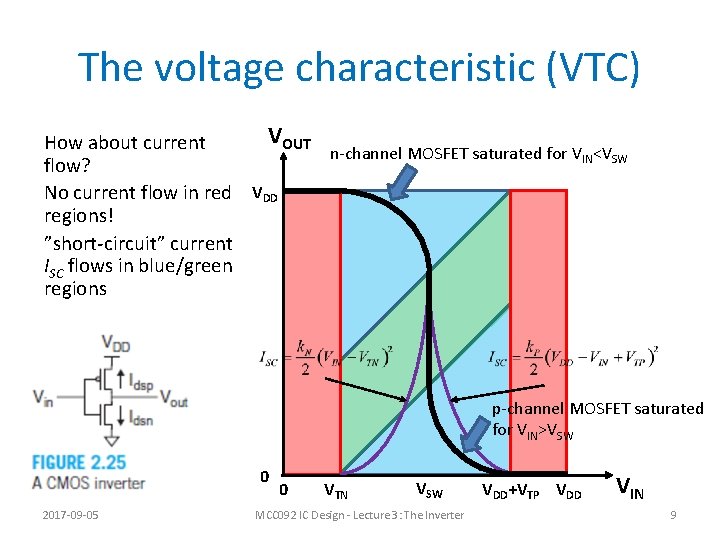

The voltage characteristic (VTC) VOUT How about current n-channel MOSFET saturated for VIN<VSW flow? No current flow in red VDD regions! ”short-circuit” current ISC flows in blue/green regions p-channel MOSFET saturated for VIN>VSW 0 2017 -09 -05 0 VTN VSW MCC 092 IC Design - Lecture 3: The Inverter VDD+VTP VDD VIN 9

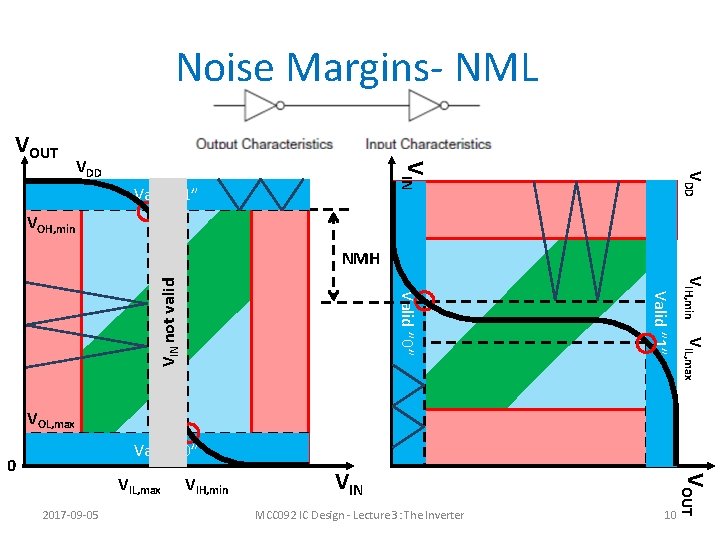

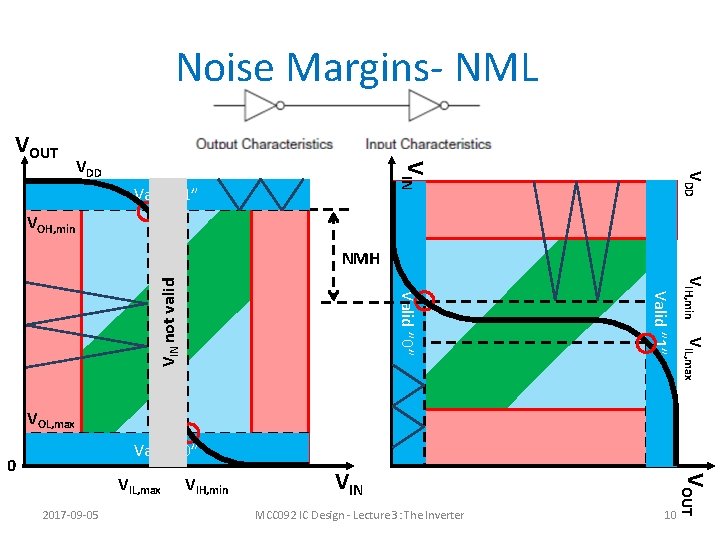

Noise Margins- NML VDD Valid ” 1” VDD VIN VOUT VOH, min VIL, max Valid ” 1” Valid ” 0” VIN not valid NMH VOL, max Valid ” 0” VIL, max 2017 -09 -05 VIH, min VIN MCC 092 IC Design - Lecture 3: The Inverter 10 VOUT 0

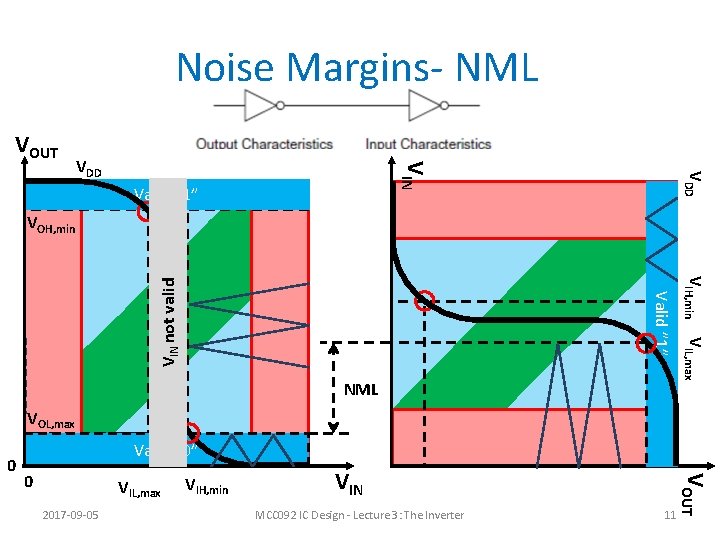

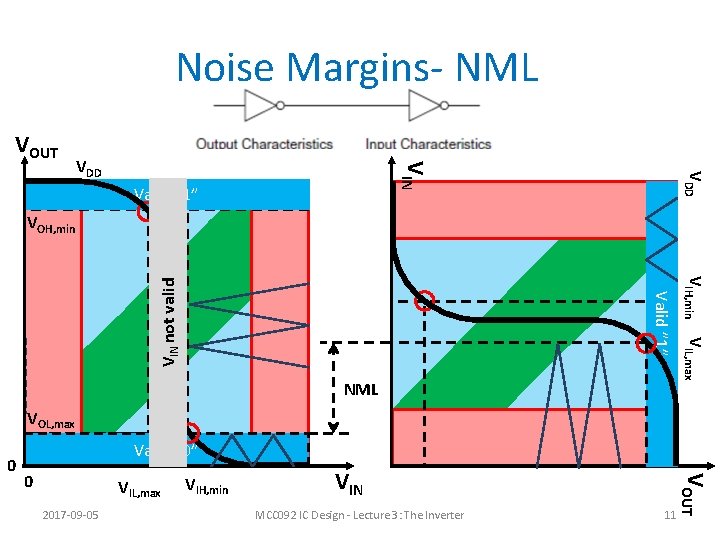

Noise Margins- NML VDD Valid ” 1” VDD VIN VOUT VIL, max NML VIH, min Valid ” 1” VIN not valid VOH, min VOL, max 0 VIL, max 2017 -09 -05 VIH, min VIN MCC 092 IC Design - Lecture 3: The Inverter 11 VOUT 0 Valid ” 0”

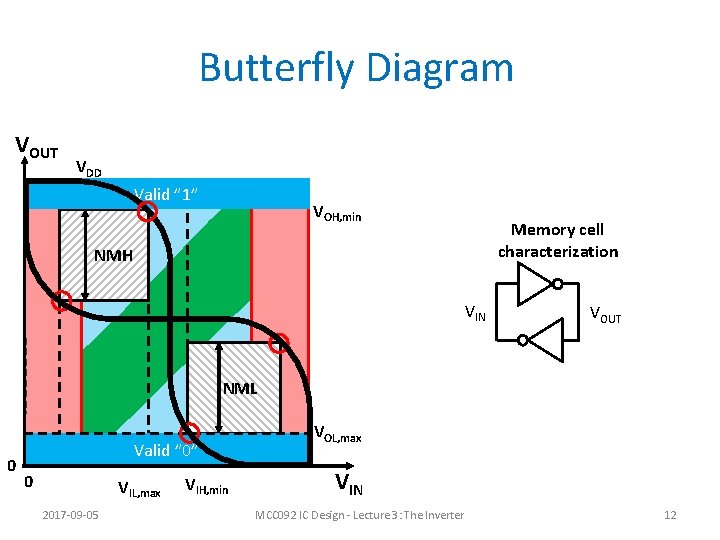

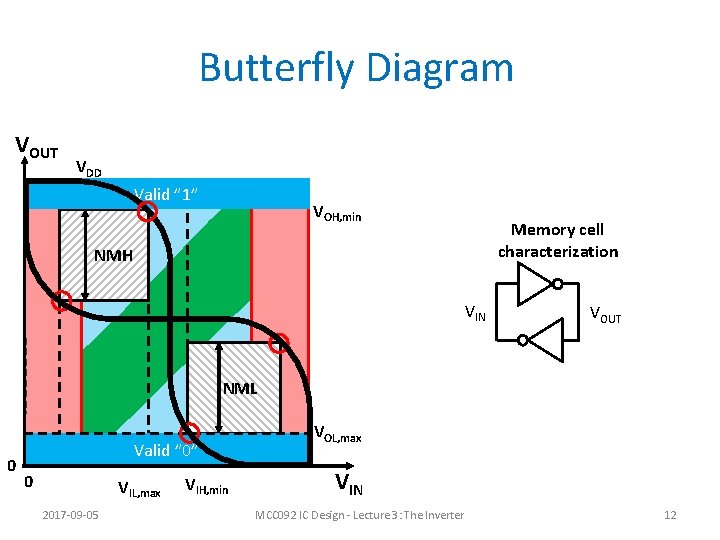

Butterfly Diagram VOUT VDD Valid ” 1” VOH, min Memory cell characterization NMH VIN VOUT NML 0 Valid ” 0” 0 VIL, max 2017 -09 -05 VIH, min VOL, max VIN MCC 092 IC Design - Lecture 3: The Inverter 12

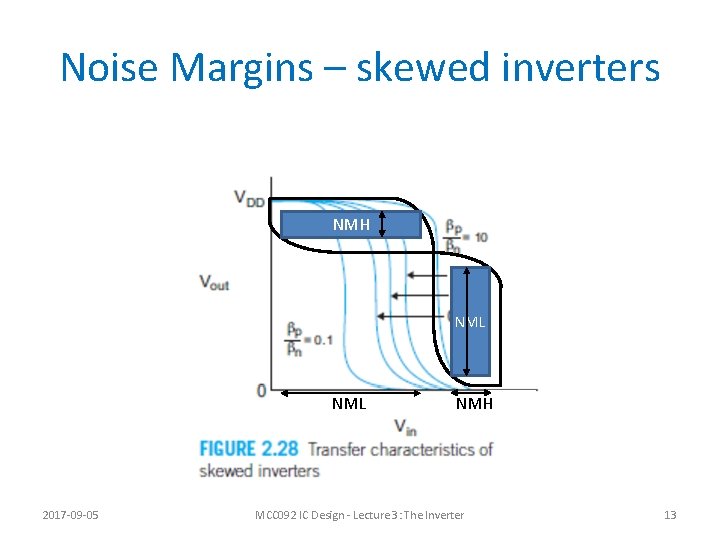

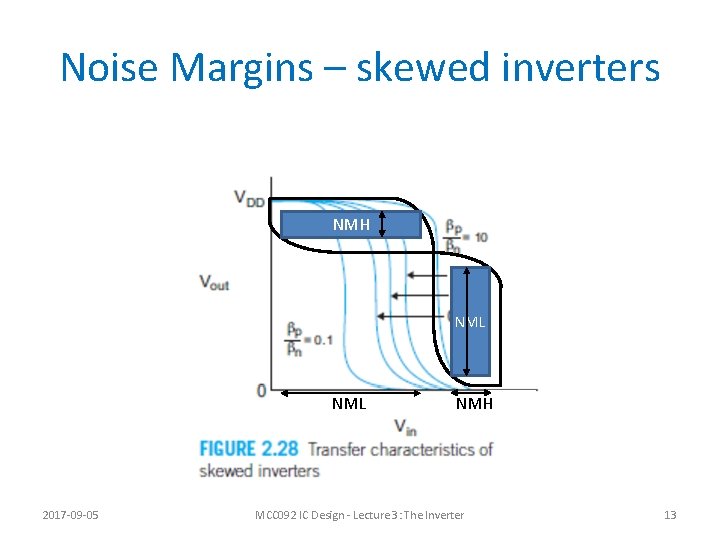

Noise Margins – skewed inverters NMH NML 2017 -09 -05 NMH MCC 092 IC Design - Lecture 3: The Inverter 13

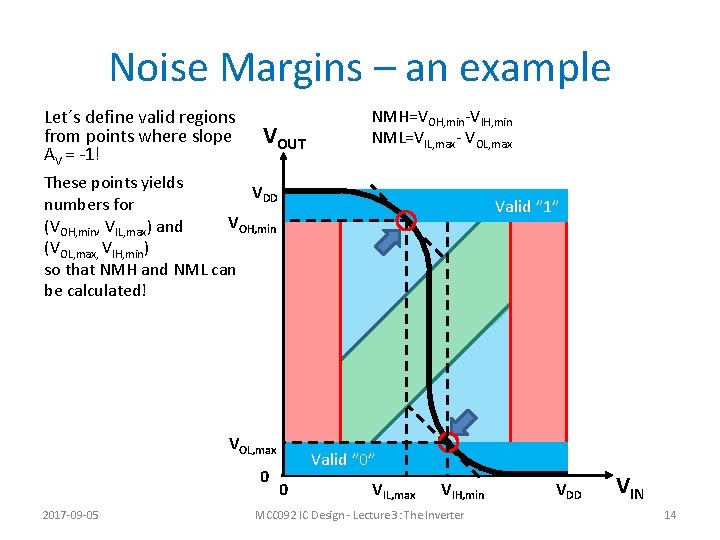

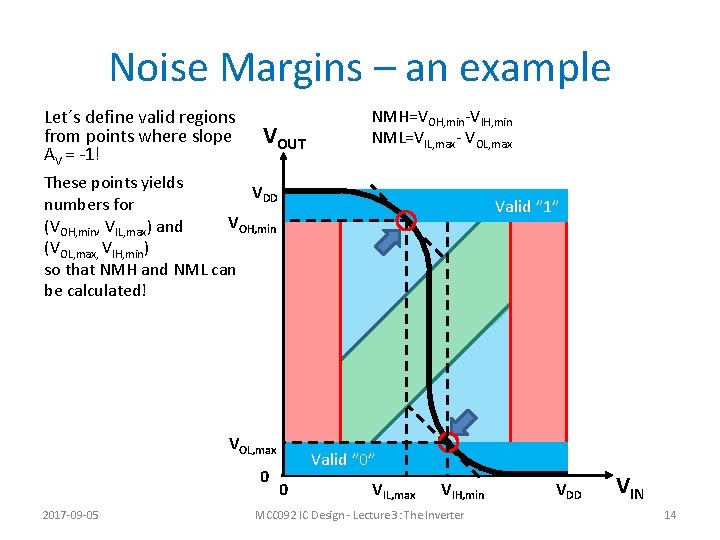

Noise Margins – an example Let´s define valid regions from points where slope AV = -1! VOUT NMH=VOH, min-VIH, min NML=VIL, max- VOL, max These points yields VDD numbers for VOH, min (VOH, min, VIL, max) and (VOL, max, VIH, min) so that NMH and NML can be calculated! Valid ” 1” VOL, max 0 2017 -09 -05 Valid ” 0” 0 VIL, max VIH, min MCC 092 IC Design - Lecture 3: The Inverter VDD VIN 14

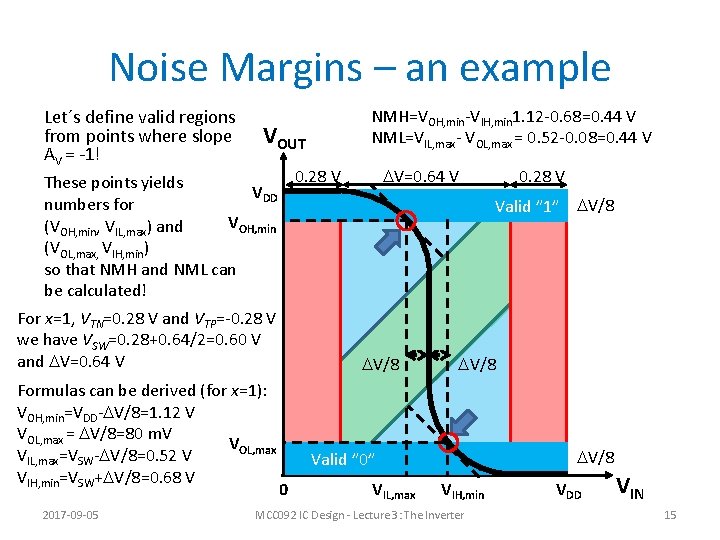

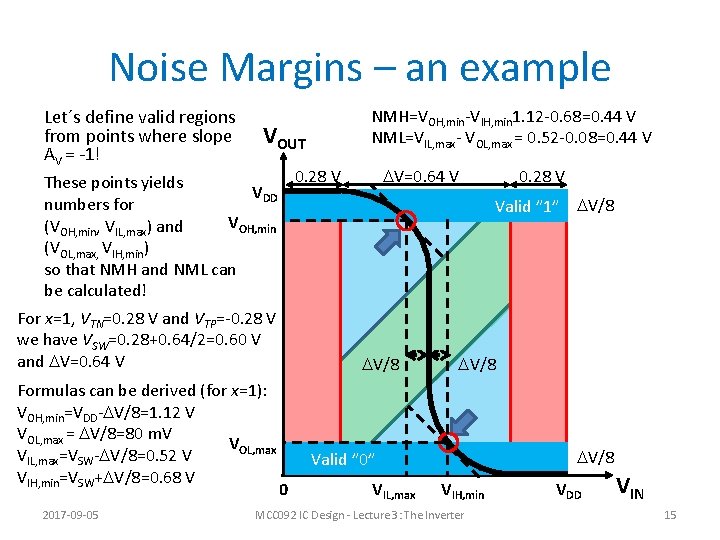

Noise Margins – an example Let´s define valid regions from points where slope AV = -1! NMH=VOH, min-VIH, min 1. 12 -0. 68=0. 44 V NML=VIL, max- VOL, max = 0. 52 -0. 08=0. 44 V VOUT DV=0. 64 V 0. 28 V These points yields VDD numbers for VOH, min (VOH, min, VIL, max) and (VOL, max, VIH, min) so that NMH and NML can be calculated! For x=1, VTN=0. 28 V and VTP=-0. 28 V we have VSW=0. 28+0. 64/2=0. 60 V and DV=0. 64 V Formulas can be derived (for x=1): VOH, min=VDD-DV/8=1. 12 -DV/8 V VOL, max = DV/8=80 DV/8 m. V VOL, max VIL, max=VSW-DV/8=0. 52 -DV/8 V 0 VIH, min=VSW+DV/8=0. 68 +DV/8 V 2017 -09 -05 Valid ” 1” DV/8 Valid ” 0” 0 0. 28 V VIL, max VIH, min MCC 092 IC Design - Lecture 3: The Inverter VDD VIN 15

Summary • • CMOS inverter – schematic Voltage transfer characteristics (VTC) How to calculate switching voltage VSW Understand VSW dependence on k. N/k. P Understand switching current (ISC) flow Noise margins NMH and NML Butterfly diagram Match current curves 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter 16

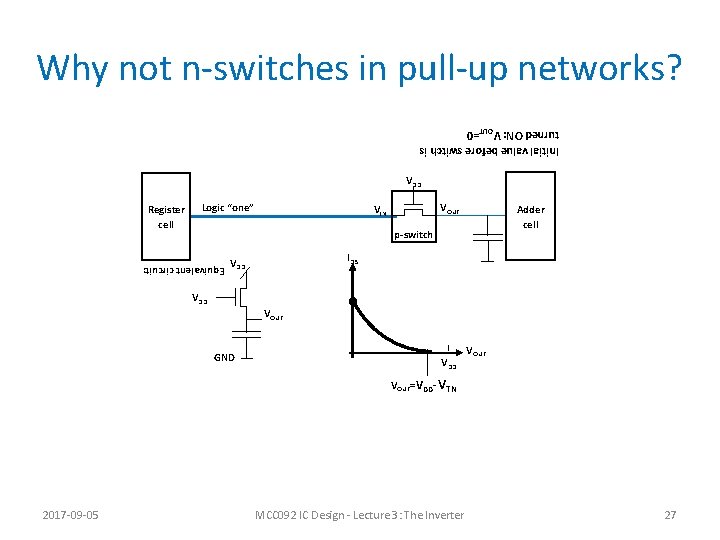

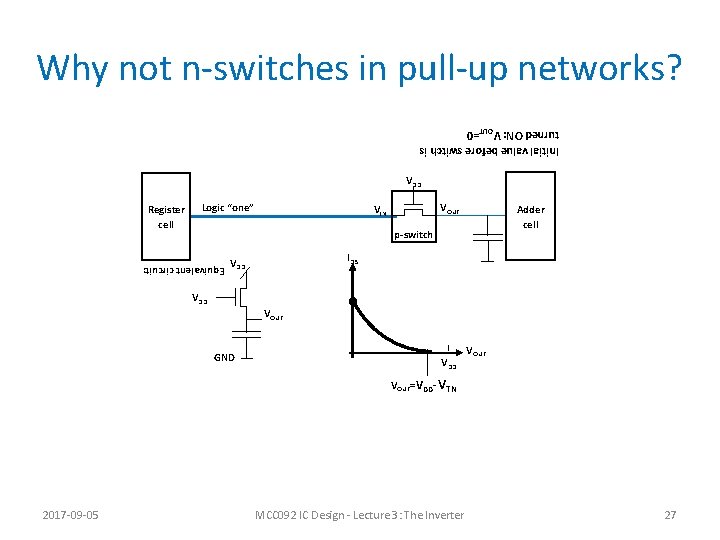

Why not n-switches in pull-up networks? Initial value before switch is turned ON: VOUT=0 VDD Register cell Logic “one” VOUT VIN Adder cell p-switch IDS VDD Equivalent circuit: VDD VOUT GND VDD VOUT=VDD-VTN 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter 27

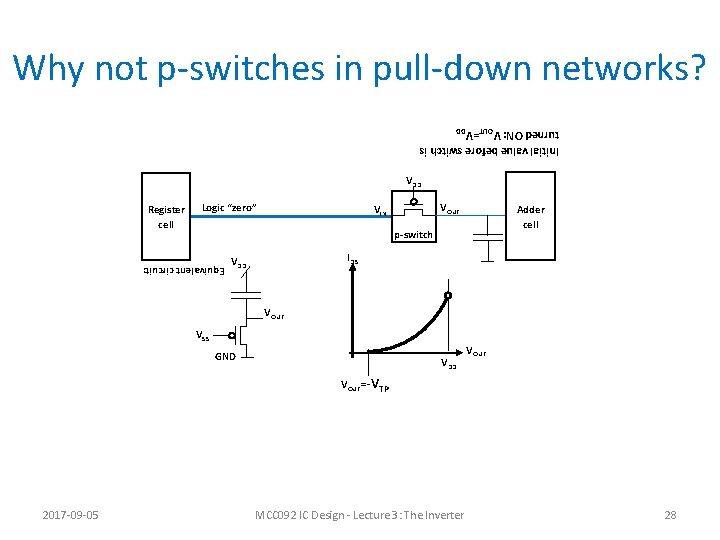

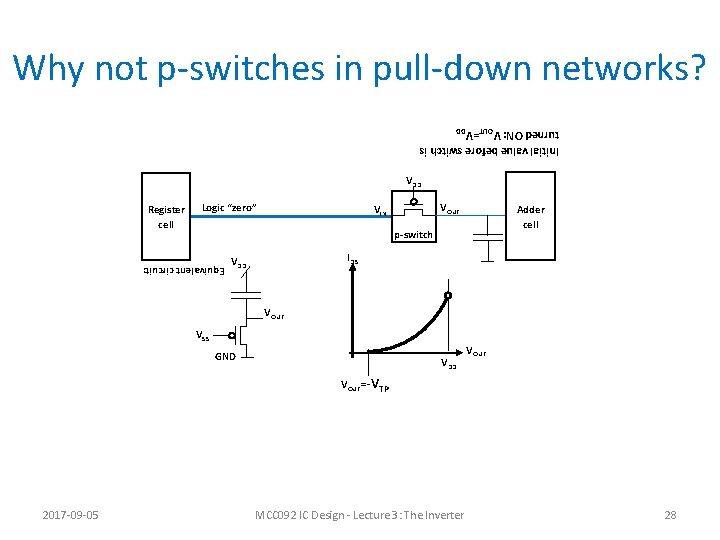

Why not p-switches in pull-down networks? Initial value before switch is turned ON: VOUT=VDD Register cell Logic “zero” VOUT VIN Adder cell p-switch IDS VDD Equivalent circuit: VOUT VSS GND VDD VOUT=-VTP 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter 28