The Belle SVD Trigger Tom Ziegler on behalf

The Belle SVD Trigger Tom Ziegler on behalf of the Belle SVD group Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 Ø The SVD 2. 0 Update Ø The Front-End Readout Electronics Ø Level 0 & 1 Trigger Ø Level 1. 5 Trigger Ø Summary The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 1

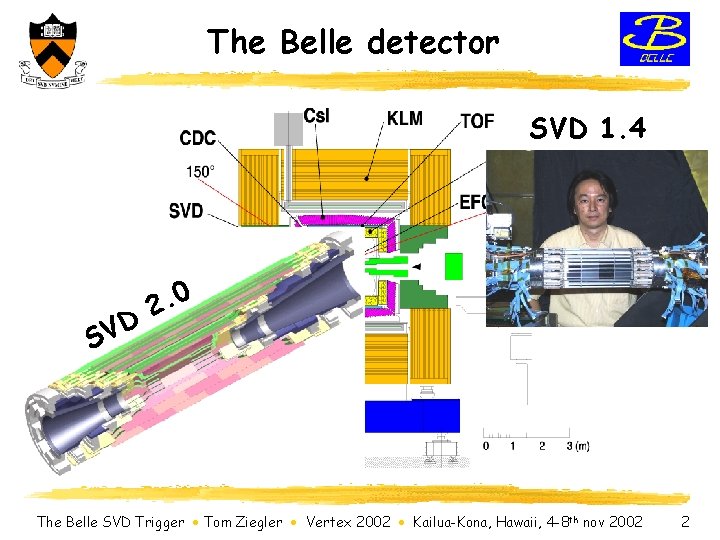

The Belle detector SVD 1. 4 D V S 0. 2 The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 2

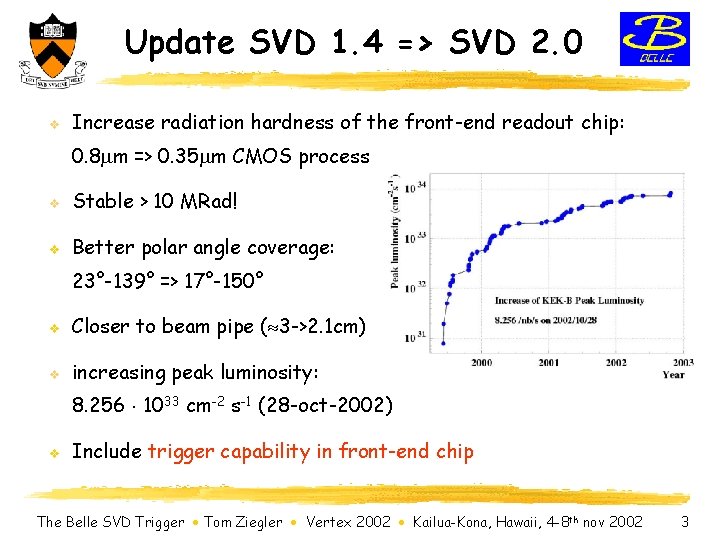

Update SVD 1. 4 => SVD 2. 0 v Increase radiation hardness of the front-end readout chip: 0. 8 m => 0. 35 m CMOS process v Stable > 10 MRad! v Better polar angle coverage: 23°-139° => 17°-150° v Closer to beam pipe ( 3 ->2. 1 cm) v increasing peak luminosity: 8. 256 1033 cm-2 s-1 (28 -oct-2002) v Include trigger capability in front-end chip The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 3

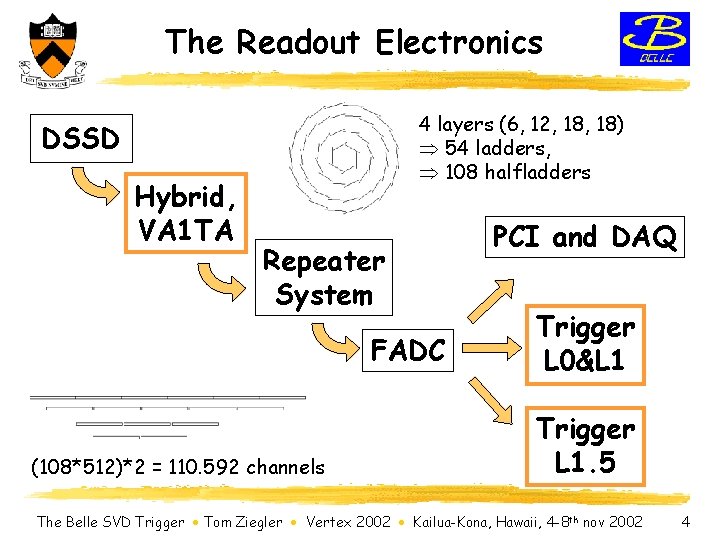

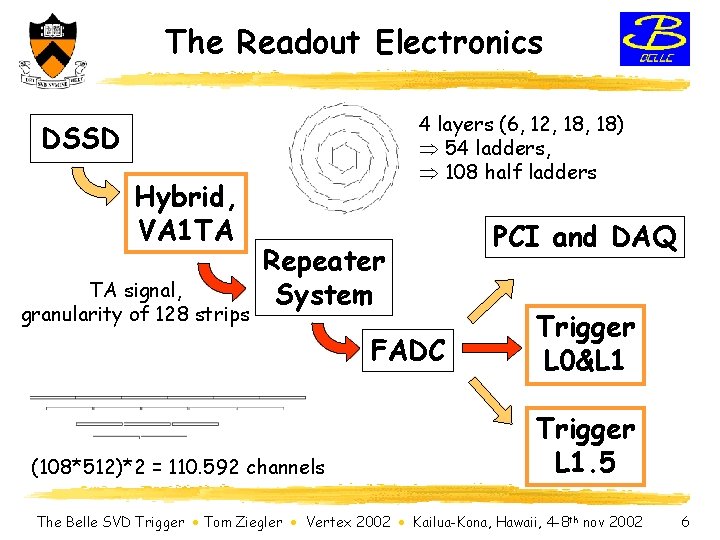

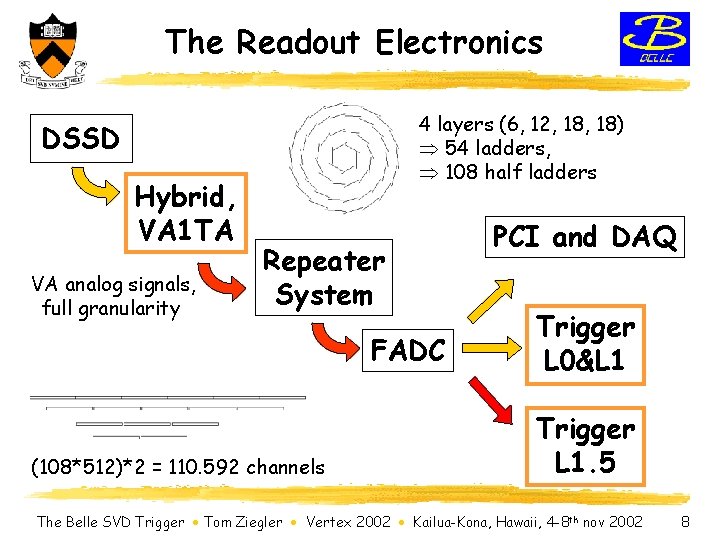

The Readout Electronics 4 layers (6, 12, 18) Þ 54 ladders, Þ 108 halfladders DSSD Hybrid, VA 1 TA Repeater System FADC (108*512)*2 = 110. 592 channels PCI and DAQ Trigger L 0&L 1 Trigger L 1. 5 The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 4

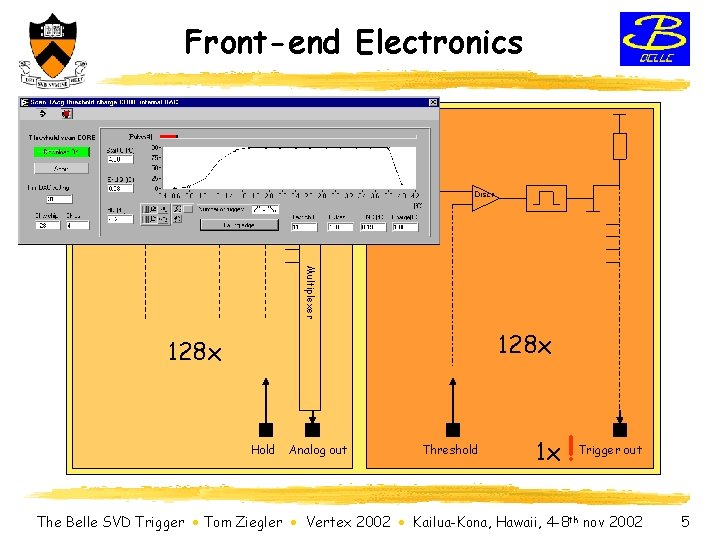

Front-end Electronics FE readout chips: VA 1 TA, IDE AS PA slow Shaper fast Shaper S/H Discr. Multiplexer 128 x Each chip reads out 128 DSSD channels. Trigger capability is included in the ASIC. Hold Analog out Threshold 1 x ! Trigger out The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 5

The Readout Electronics 4 layers (6, 12, 18) Þ 54 ladders, Þ 108 half ladders DSSD Hybrid, VA 1 TA TA signal, granularity of 128 strips Repeater System FADC (108*512)*2 = 110. 592 channels PCI and DAQ Trigger L 0&L 1 Trigger L 1. 5 The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 6

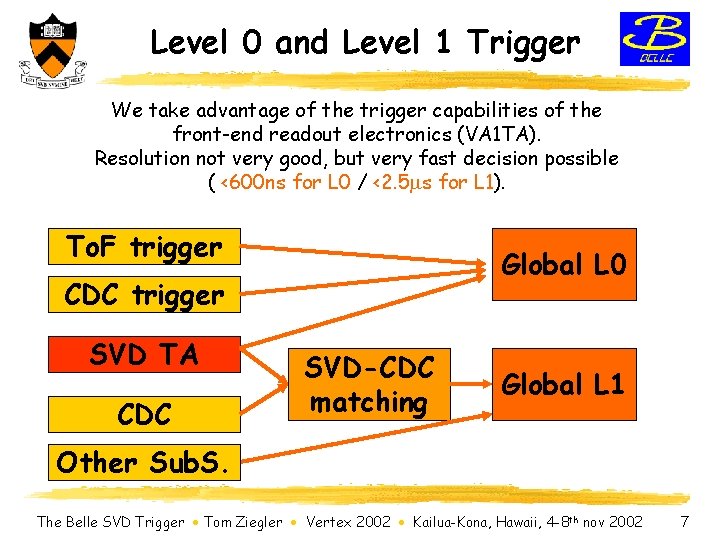

Level 0 and Level 1 Trigger We take advantage of the trigger capabilities of the front-end readout electronics (VA 1 TA). Resolution not very good, but very fast decision possible ( <600 ns for L 0 / <2. 5 s for L 1). To. F trigger Global L 0 CDC trigger SVD TA CDC SVD-CDC matching Global L 1 Other Sub. S. The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 7

The Readout Electronics 4 layers (6, 12, 18) Þ 54 ladders, Þ 108 half ladders DSSD Hybrid, VA 1 TA VA analog signals, full granularity Repeater System FADC (108*512)*2 = 110. 592 channels PCI and DAQ Trigger L 0&L 1 Trigger L 1. 5 The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 8

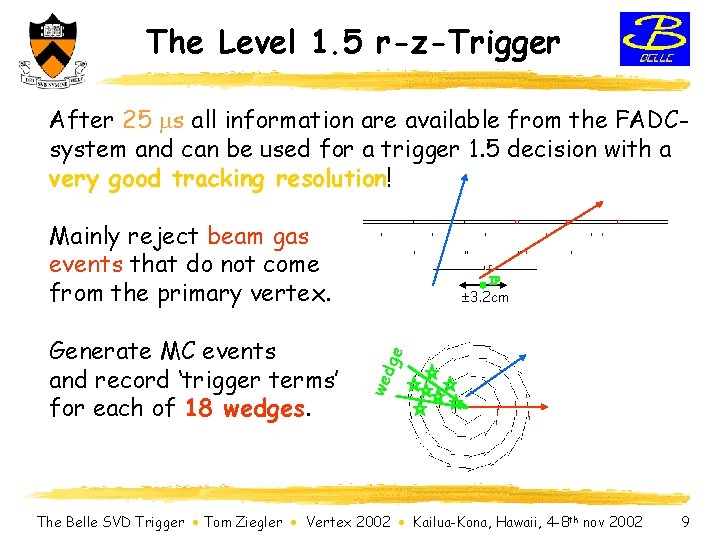

The Level 1. 5 r-z-Trigger After 25 s all information are available from the FADCsystem and can be used for a trigger 1. 5 decision with a very good tracking resolution! Mainly reject beam gas events that do not come from the primary vertex. e 3. 2 cm wed g Generate MC events and record ‘trigger terms’ for each of 18 wedges. IP The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 9

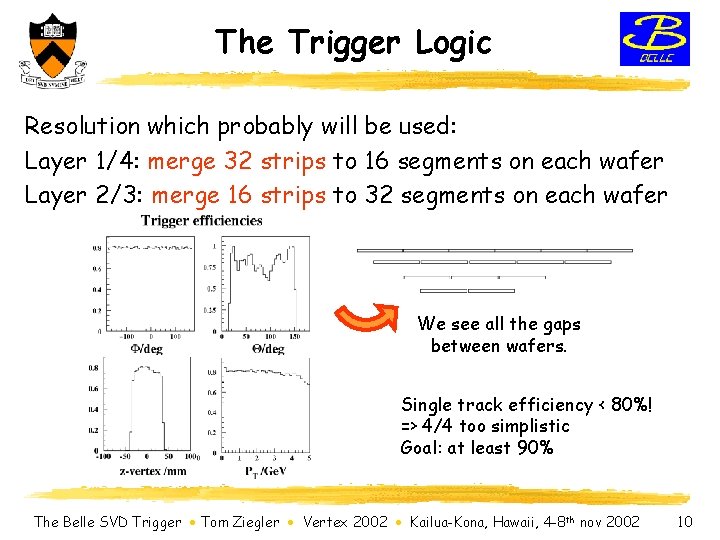

The Trigger Logic Resolution which probably will be used: Layer 1/4: merge 32 strips to 16 segments on each wafer Layer 2/3: merge 16 strips to 32 segments on each wafer We see all the gaps between wafers. Single track efficiency < 80%! => 4/4 too simplistic Goal: at least 90% The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 10

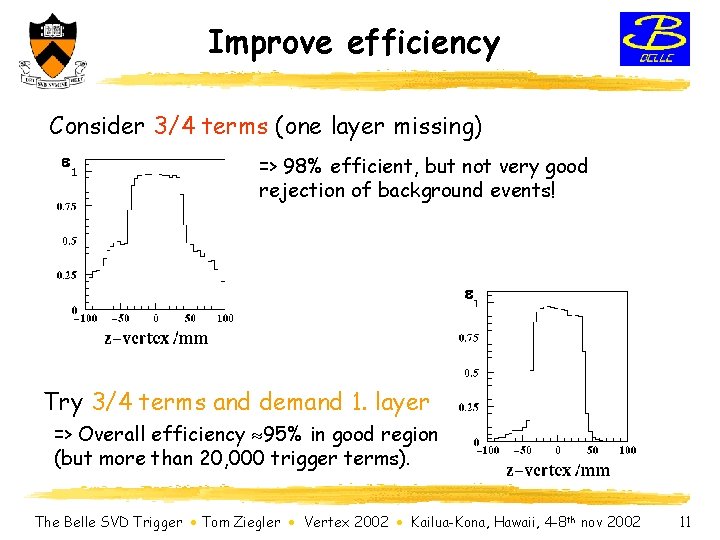

Improve efficiency Consider 3/4 terms (one layer missing) => 98% efficient, but not very good rejection of background events! Try 3/4 terms and demand 1. layer => Overall efficiency 95% in good region (but more than 20, 000 trigger terms). The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 11

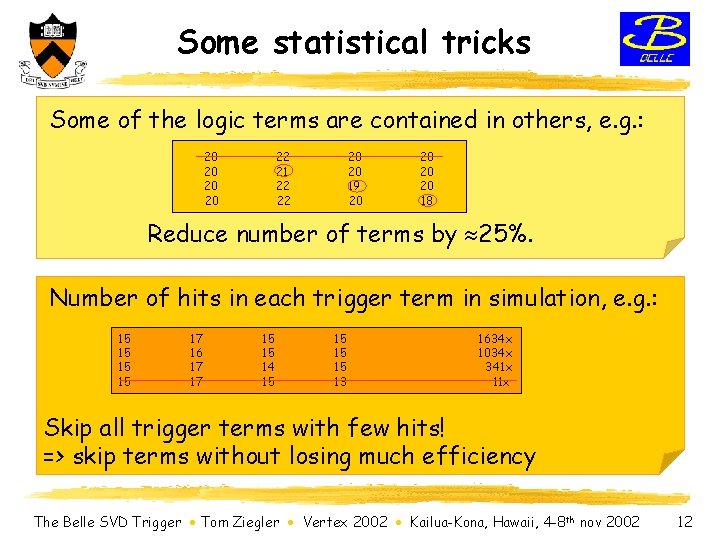

Some statistical tricks Some of the logic terms are contained in others, e. g. : 20 20 22 21 22 22 20 20 19 20 20 18 Reduce number of terms by 25%. Number of hits in each trigger term in simulation, e. g. : 15 15 17 16 17 17 15 15 14 15 15 13 1634 x 1034 x 341 x 11 x Skip all trigger terms with few hits! => skip terms without losing much efficiency The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 12

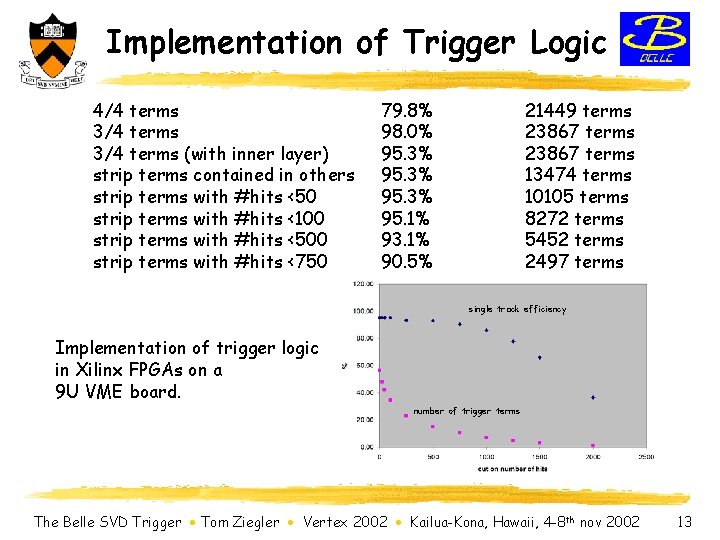

Implementation of Trigger Logic 4/4 terms 3/4 terms (with inner layer) strip terms contained in others strip terms with #hits <50 strip terms with #hits <100 strip terms with #hits <500 strip terms with #hits <750 79. 8% 98. 0% 95. 3% 95. 1% 93. 1% 90. 5% 21449 terms 23867 terms 13474 terms 10105 terms 8272 terms 5452 terms 2497 terms single track efficiency Implementation of trigger logic in Xilinx FPGAs on a 9 U VME board. number of trigger terms The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 13

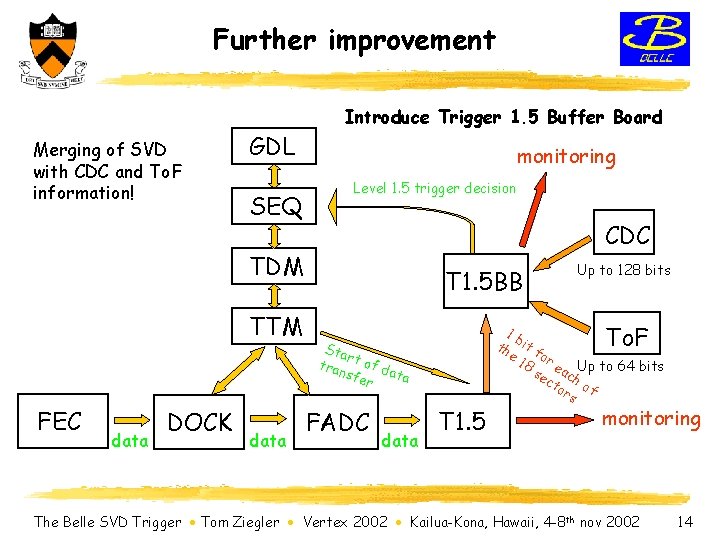

Further improvement Merging of SVD with CDC and To. F information! GDL SEQ Introduce Trigger 1. 5 Buffer Board monitoring Level 1. 5 trigger decision CDC TDM TTM FEC data DOCK data T 1. 5 BB To. F Sta r tra t of d nsf er ata FADC data Up to 128 bits T 1. 5 1 b th it f e 1 or 8 se each. Up to 64 bits ct or of s monitoring The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 14

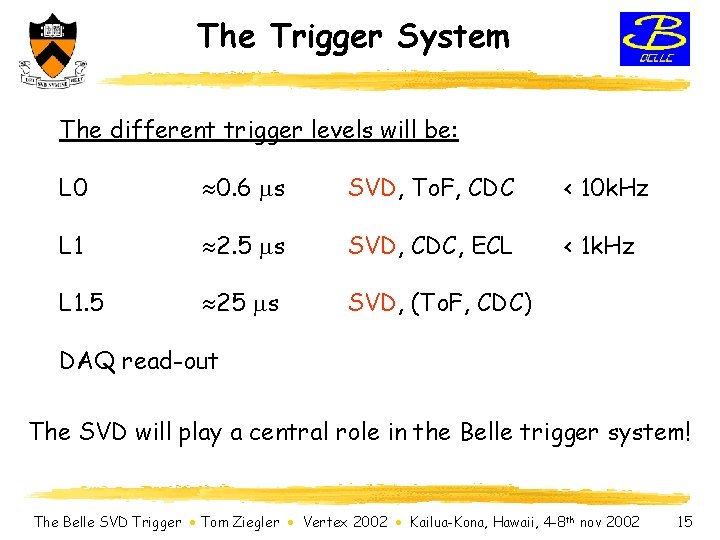

The Trigger System The different trigger levels will be: L 0 0. 6 s SVD, To. F, CDC < 10 k. Hz L 1 2. 5 s SVD, CDC, ECL < 1 k. Hz L 1. 5 25 s SVD, (To. F, CDC) DAQ read-out The SVD will play a central role in the Belle trigger system! The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 15

Summary l l l Upgrade to SVD 2. 0 allows substantial improvements in the trigger capabilities for the Belle detector! The implementation of the system with Xilinx FPGAs and overall setup is very flexible and there is still room for improvement to deal with the increasing luminosities of the KEKB accelerator. The system will be tested the next months in an overall system integration test with the rest of the SVD readout system and is ready for installation in the next shutdown. The Belle SVD Trigger Tom Ziegler Vertex 2002 Kailua-Kona, Hawaii, 4 -8 th nov 2002 16

- Slides: 16