The ARM 7 TDMI Processor Block Diagram Vector

The ARM 7 TDMI Processor Block Diagram Vector Table Exception Priorities and Interrupts JTAG Interface

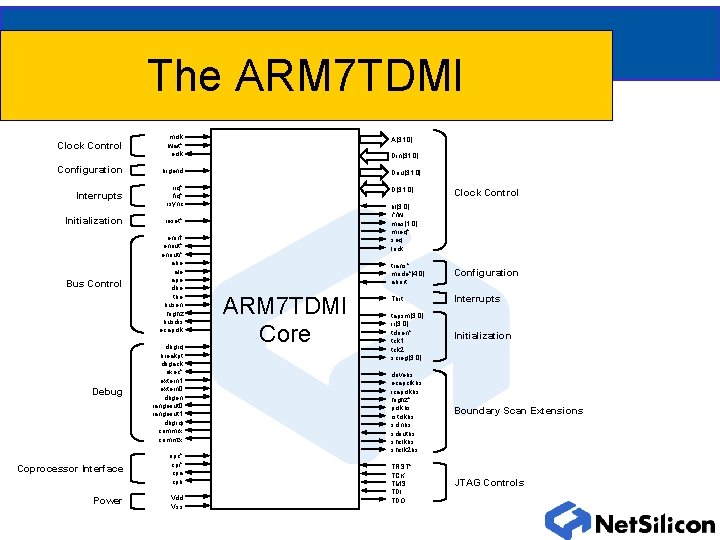

The ARM 7 TDMI Clock Control mclk wait* eclk Configuration bigend Interrupts irq* fiq* isync Initialization reset* Bus Control enin* enouti* abe ale ape dbe tbe busen highz busdis ecapclk Debug Coprocessor Interface Power dbgrq breakpt dbgack exec* extern 1 extern 0 dbgen rangeout 0 rangeout 1 dbgrqi commrx commtx opc* cpi* cpa cpb Vdd Vss A[31: 0] Din[31: 0] Dou[31: 0] D[31: 0] Clock Control bl[3: 0] r*/w mas[1: 0] mreq* seq lock ARM 7 TDMI Core trans* mode*[4: 0] abort Configuration Tbit Interrupts tapsm[3: 0] ir[3: 0] tdoen* tck 1 tck 2 screg[3: 0] Initialization drivebs ecapclkbs icapclkbs highz* pclkbs rstclkbs sdinbs sdoutbs shclk 2 bs Boundary Scan Extensions TRST* TCK TMS TDI TDO JTAG Controls

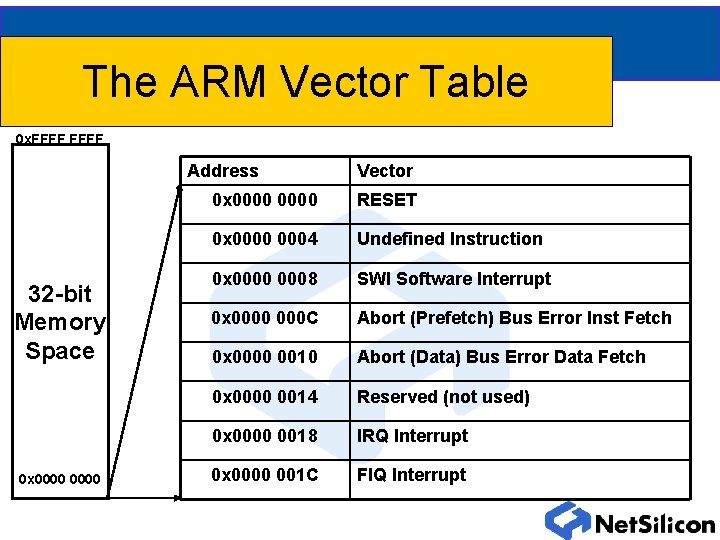

The ARM Vector Table table The 0 x. FFFF Address 32 -bit Memory Space 0 x 0000 Vector 0 x 0000 RESET 0 x 0000 0004 Undefined Instruction 0 x 0000 0008 SWI Software Interrupt 0 x 0000 000 C Abort (Prefetch) Bus Error Inst Fetch 0 x 0000 0010 Abort (Data) Bus Error Data Fetch 0 x 0000 0014 Reserved (not used) 0 x 0000 0018 IRQ Interrupt 0 x 0000 001 C FIQ Interrupt

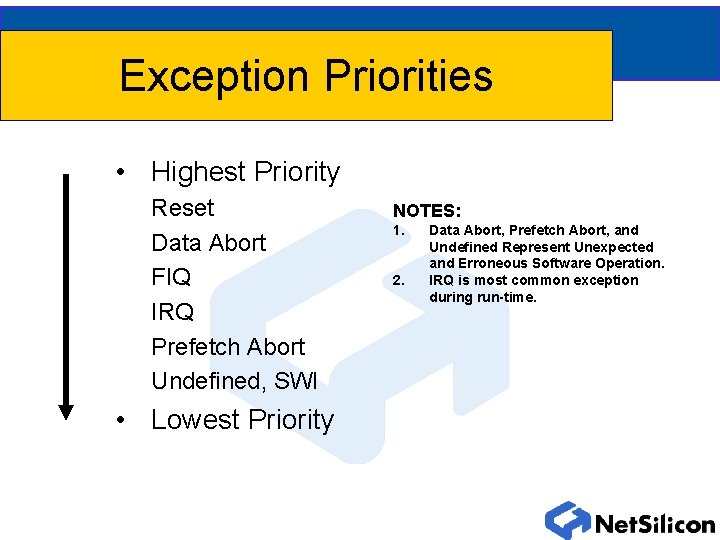

Exception Priorities • Highest Priority Reset Data Abort FIQ IRQ Prefetch Abort Undefined, SWI • Lowest Priority NOTES: 1. 2. Data Abort, Prefetch Abort, and Undefined Represent Unexpected and Erroneous Software Operation. IRQ is most common exception during run-time.

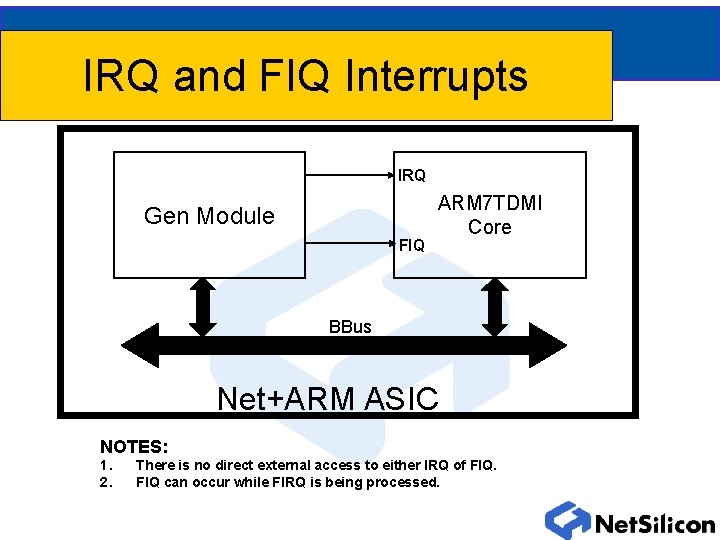

IRQ and FIQ Interrupts IRQ Gen Module FIQ ARM 7 TDMI Core BBus Net+ARM ASIC NOTES: 1. 2. There is no direct external access to either IRQ of FIQ can occur while FIRQ is being processed.

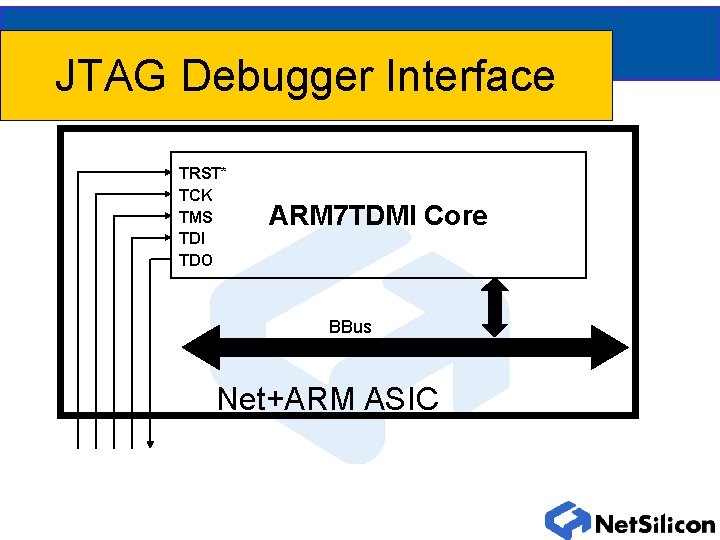

JTAG Debugger Interface TRST* TCK TMS TDI TDO ARM 7 TDMI Core BBus Net+ARM ASIC

- Slides: 6