The Architecture of Konrad Zuses Early Computers Ral

- Slides: 46

The Architecture of Konrad Zuse’s Early Computers Raúl Rojas Freie Universität Berlin

Konrad Zuse (1910 -1995)

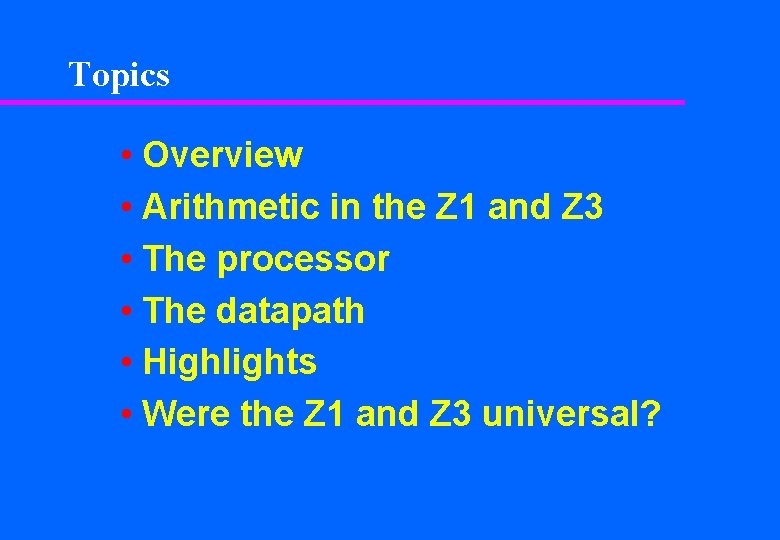

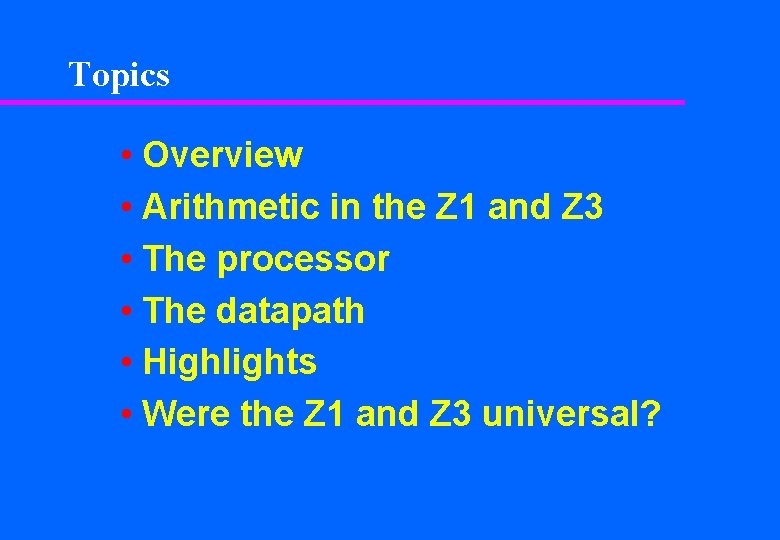

Topics • Overview • Arithmetic in the Z 1 and Z 3 • The processor • The datapath • Highlights • Were the Z 1 and Z 3 universal?

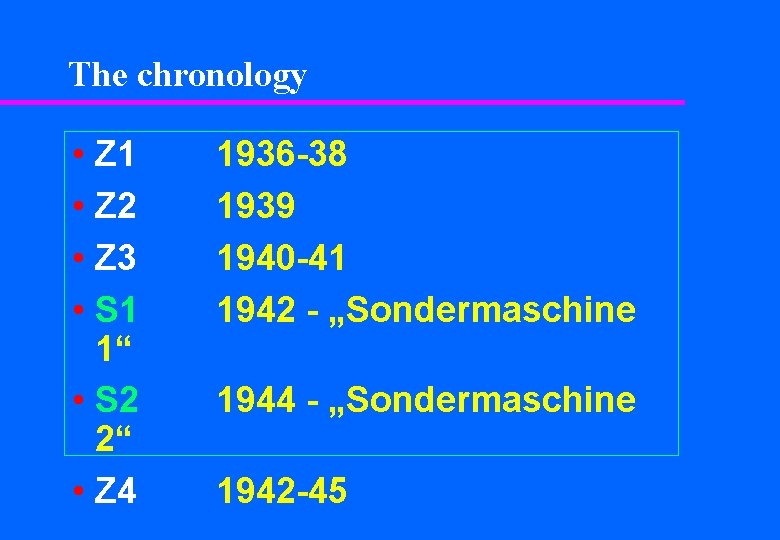

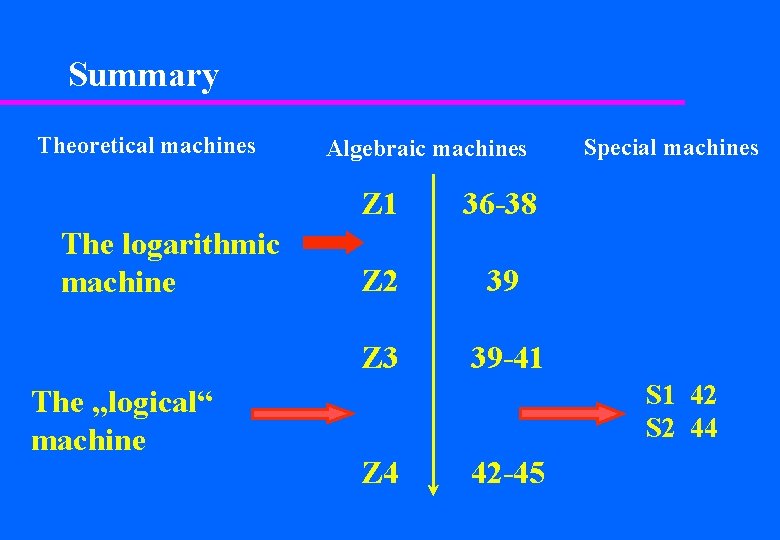

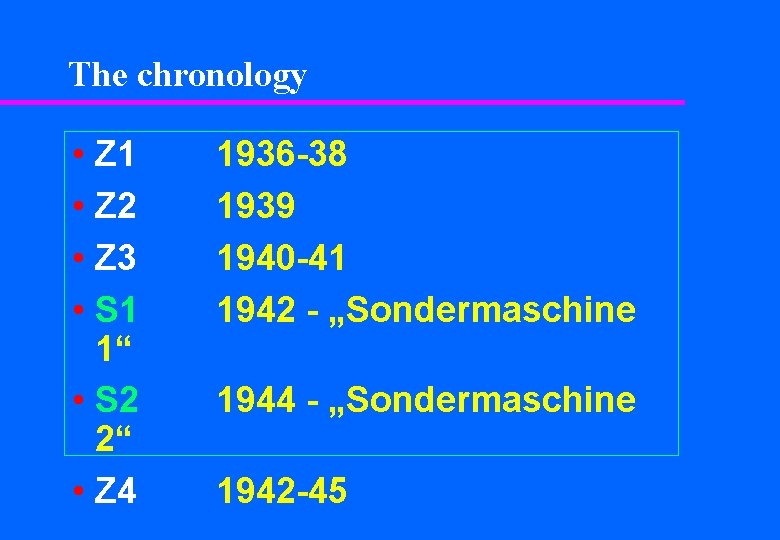

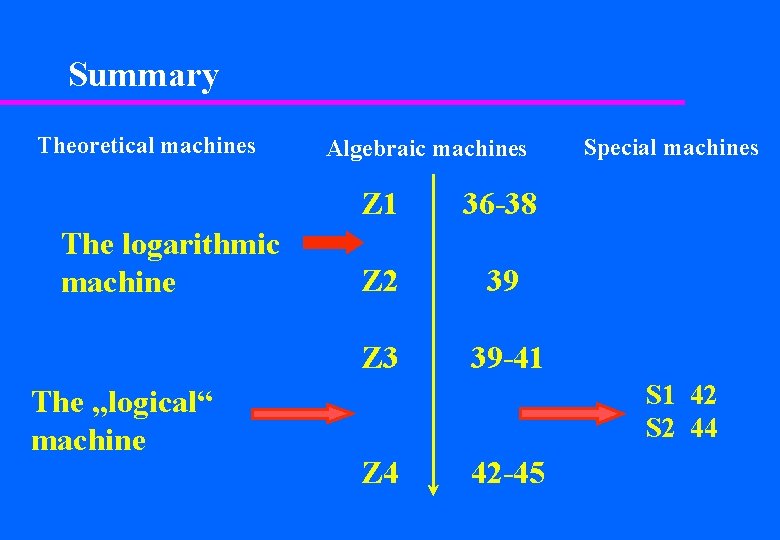

The chronology • Z 1 • Z 2 • Z 3 • S 1 1“ • S 2 2“ • Z 4 1936 -38 1939 1940 -41 1942 - „Sondermaschine 1944 - „Sondermaschine 1942 -45

The Z 1 and Z 3 Z 1 (1936 -1938) - mechanical design - programmable (punched tape) - basic arithmetic operations - completely binary - floating-point machine Z 3 (1938 -1941) - built with relays - logically equivalent to the Z 1

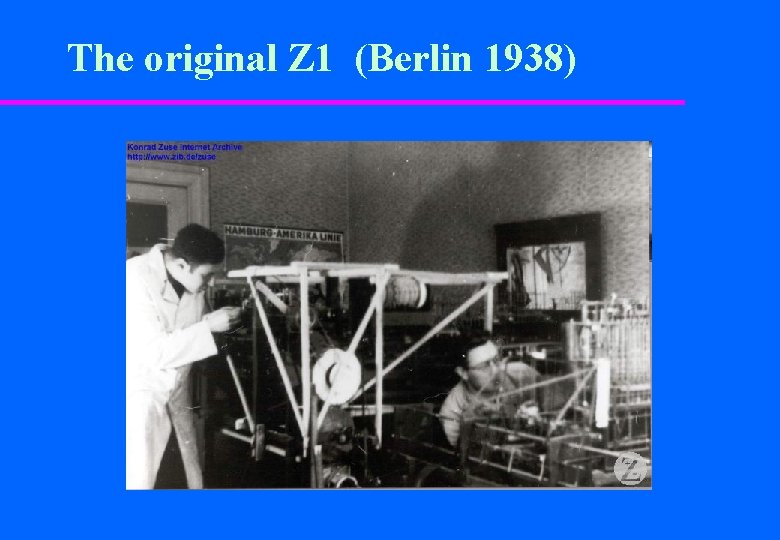

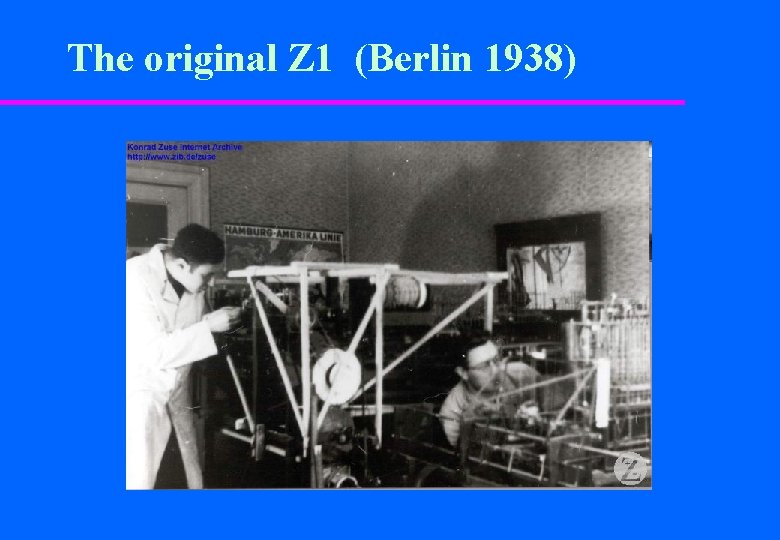

The original Z 1 (Berlin 1938)

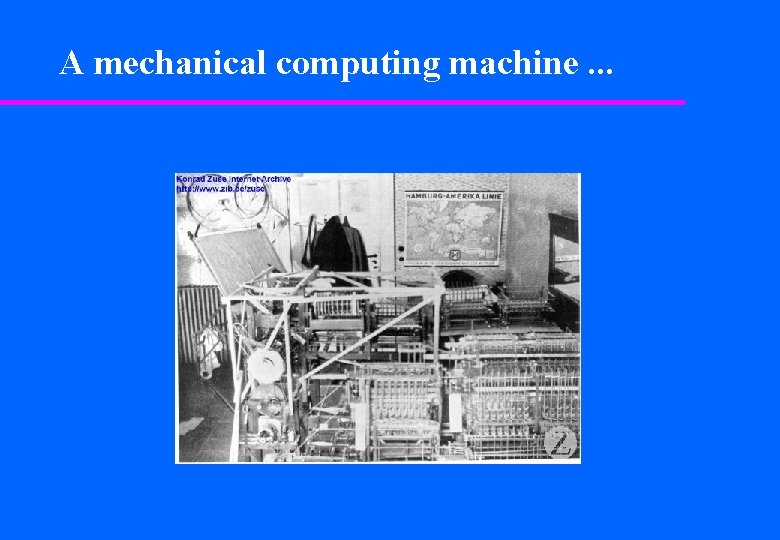

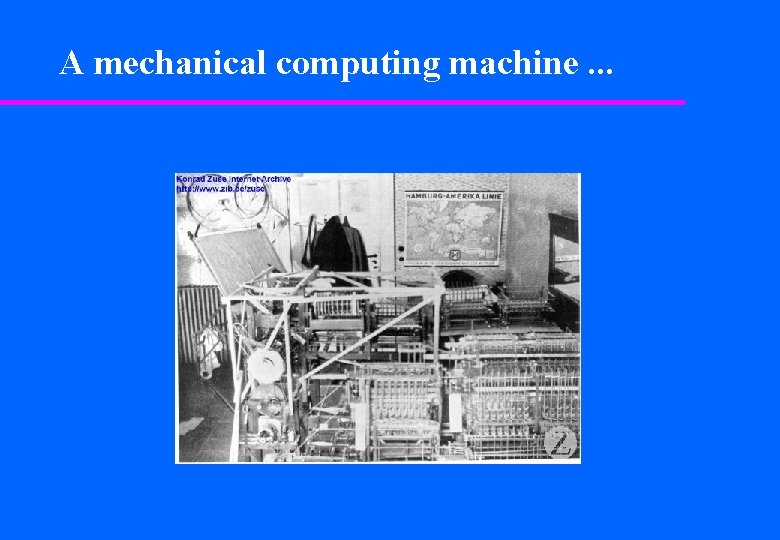

A mechanical computing machine. . .

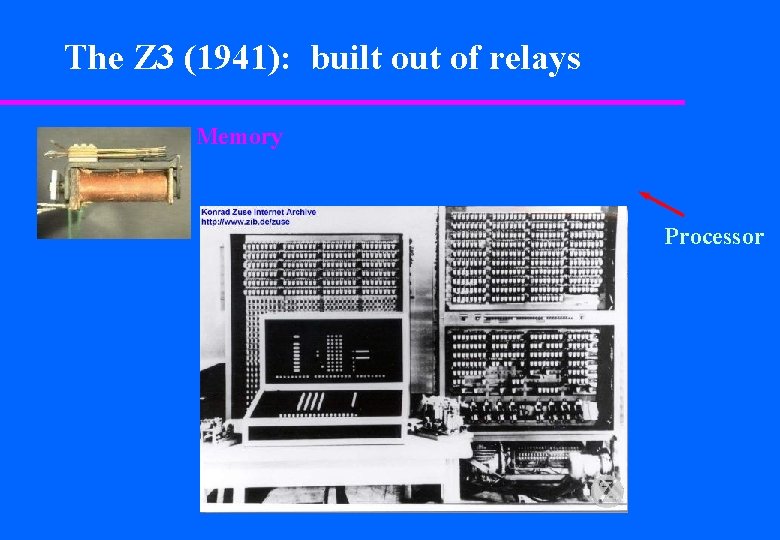

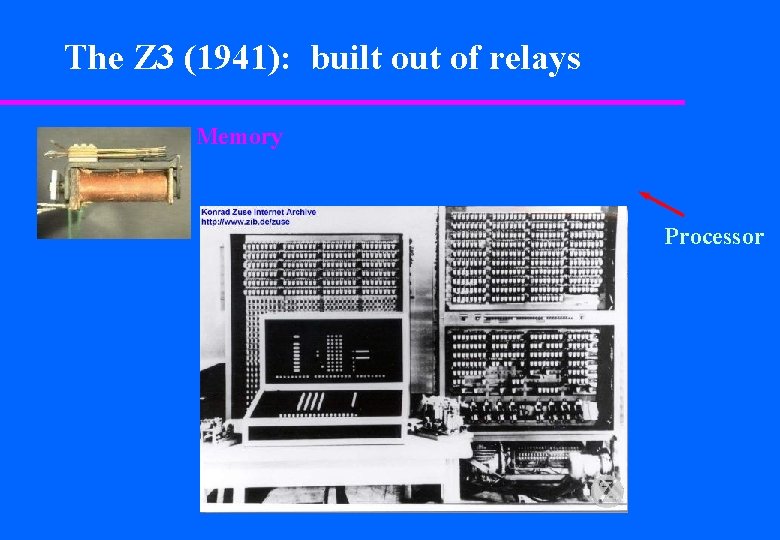

The Z 3 (1941): built out of relays Memory Processor

Light and shadow. . .

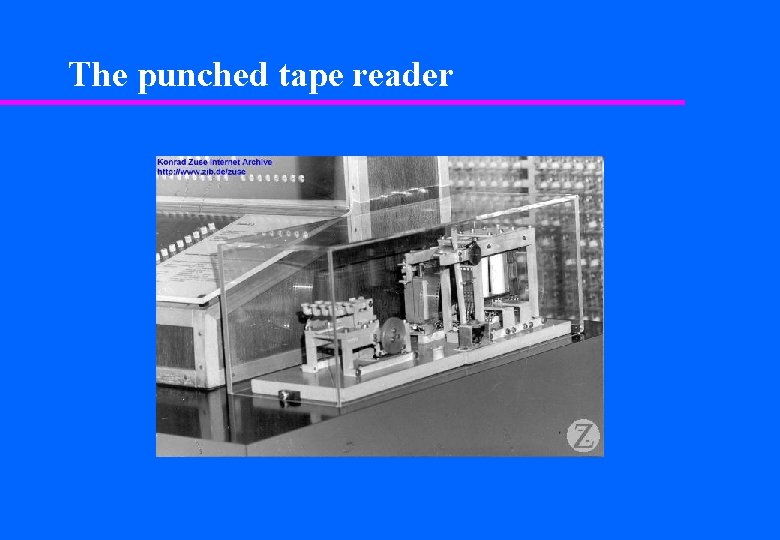

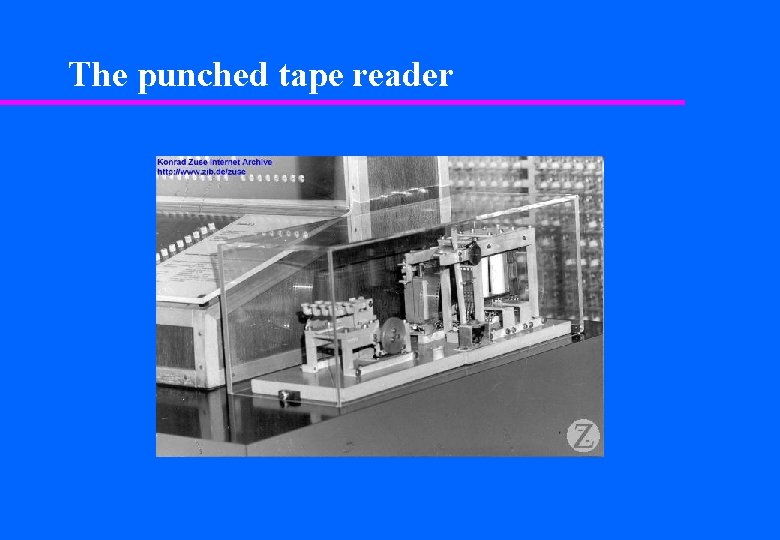

The punched tape reader

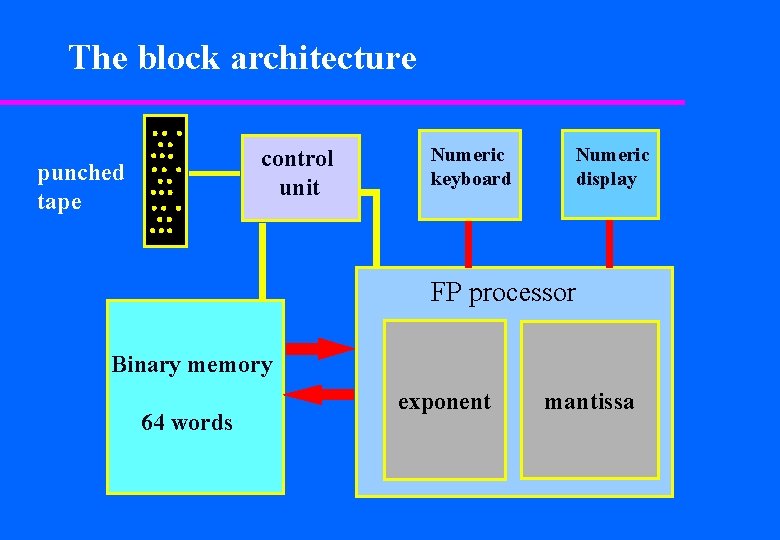

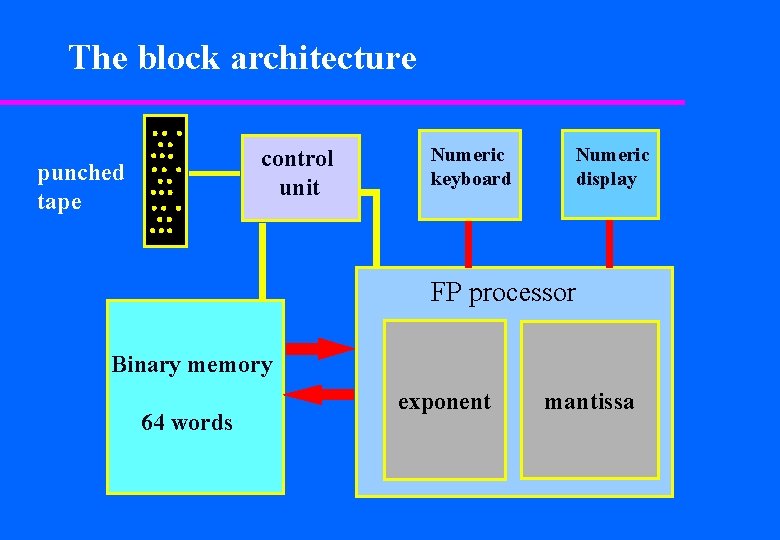

The block architecture control unit punched tape Numeric keyboard Numeric display FP processor Binary memory 64 words exponent mantissa

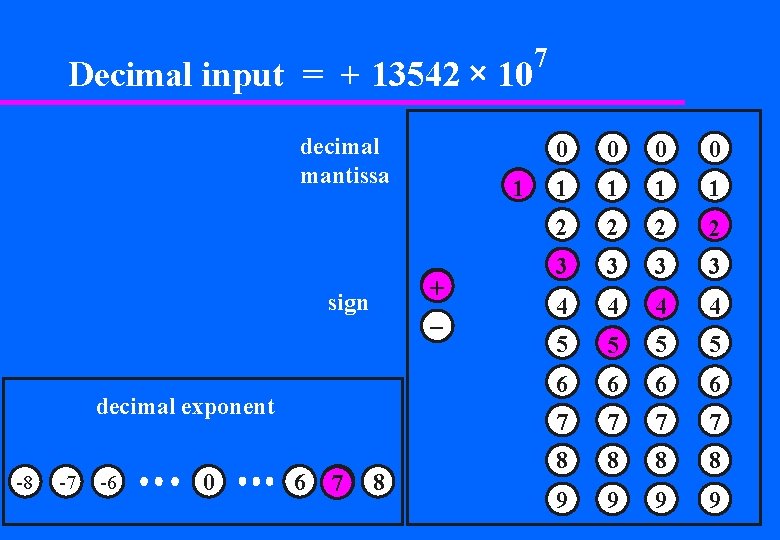

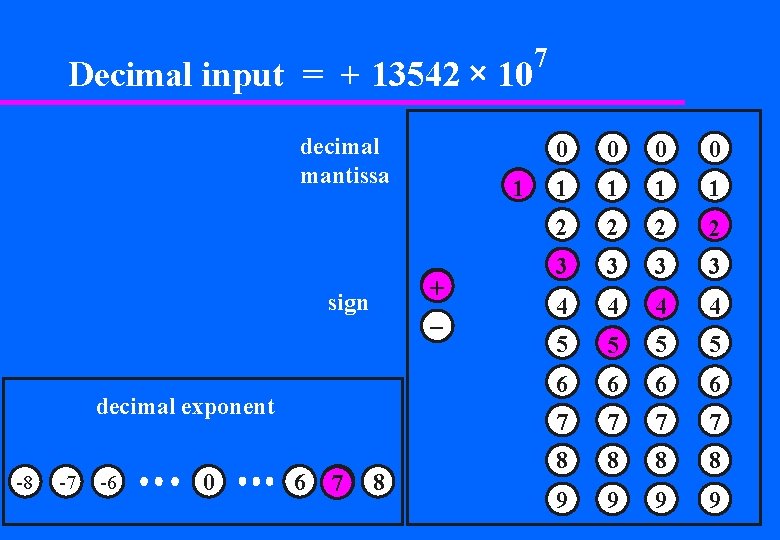

Decimal input = + 13542 decimal mantissa decimal exponent -8 -7 -6 0 6 7 1 + _ sign 8 10 7 0 0 1 1 2 2 3 3 4 4 5 5 6 6 7 7 8 8 9 9

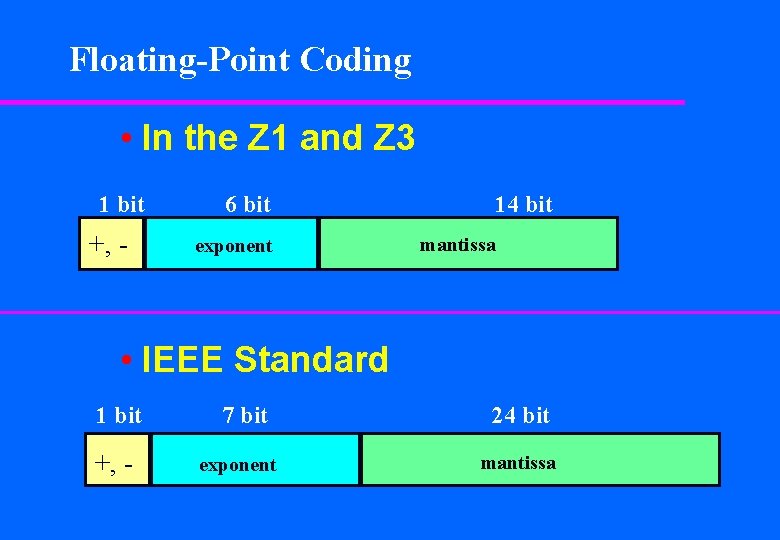

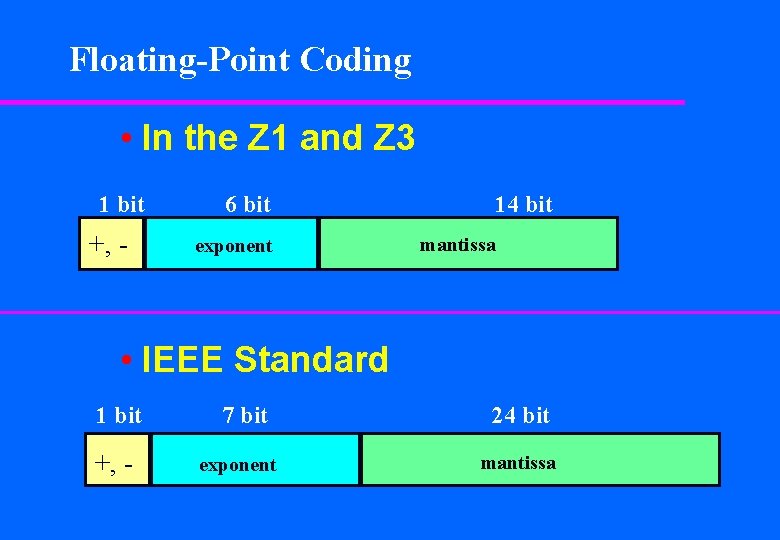

Floating-Point Coding • In the Z 1 and Z 3 1 bit +, - 6 bit exponent 14 bit mantissa • IEEE Standard 1 bit +, - 7 bit exponent 24 bit mantissa

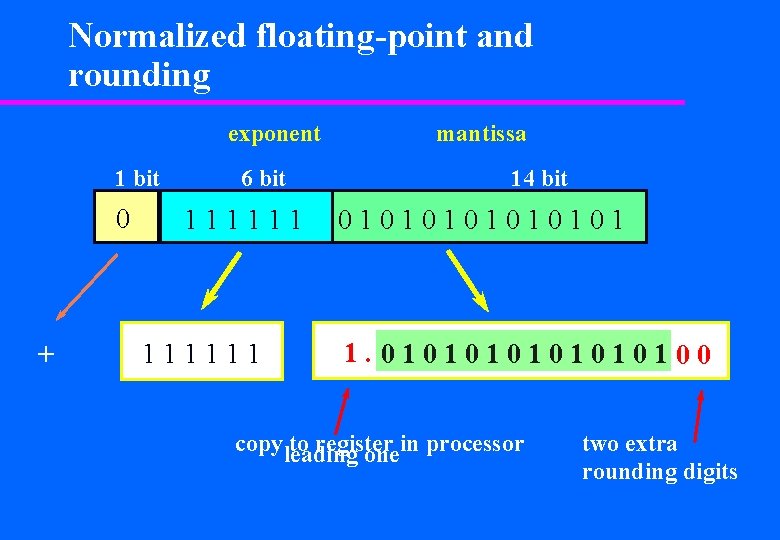

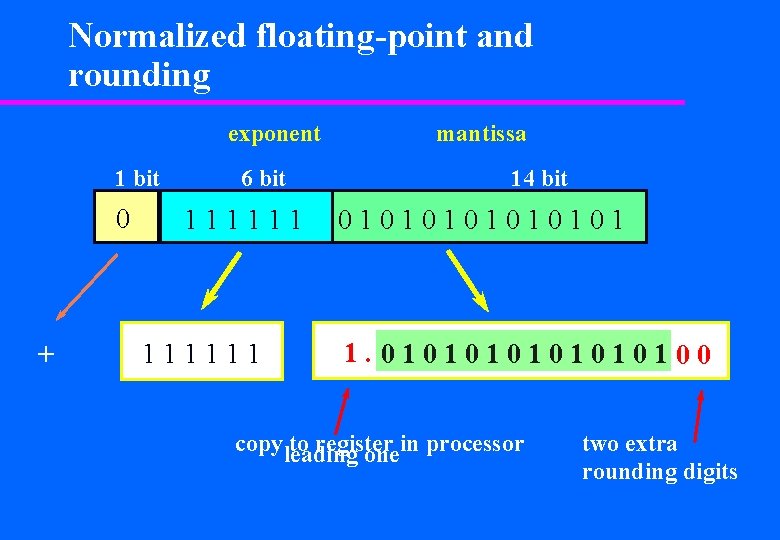

Normalized floating-point and rounding exponent 1 bit 0 + 6 bit 111111 mantissa 14 bit 01010101 1. 0101010100 copyleading to register onein processor two extra rounding digits

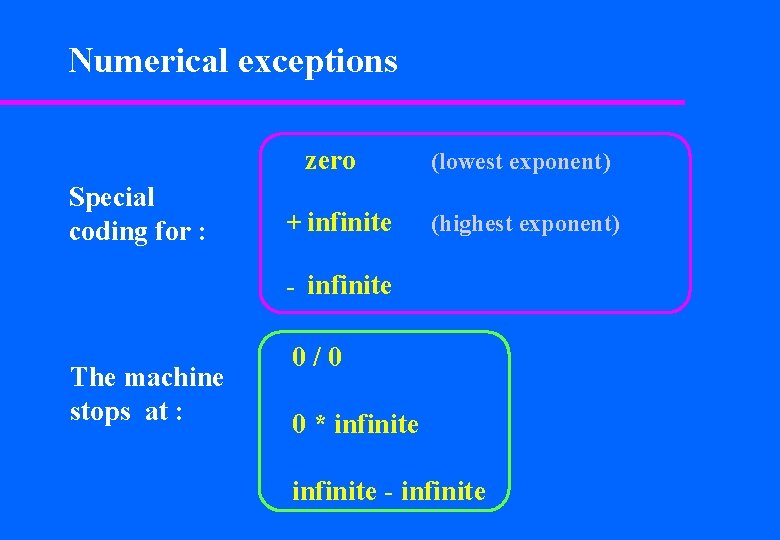

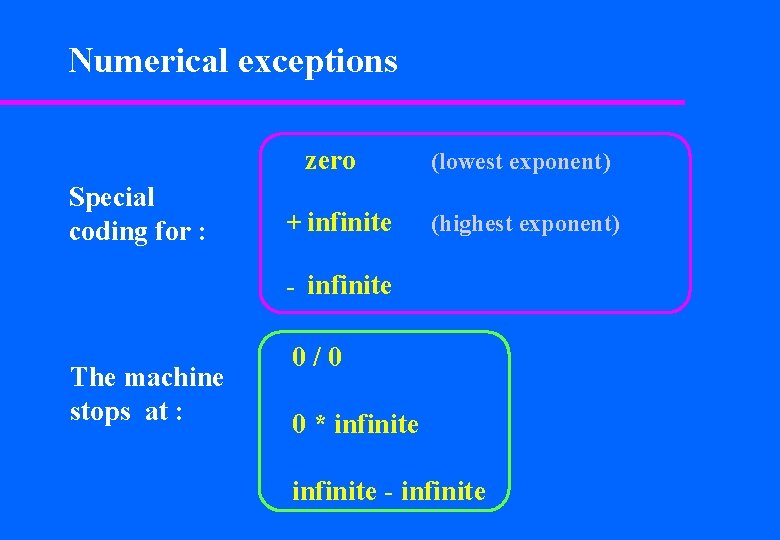

Numerical exceptions zero Special coding for : + infinite (lowest exponent) (highest exponent) - infinite The machine stops at : 0/0 0 * infinite - infinite

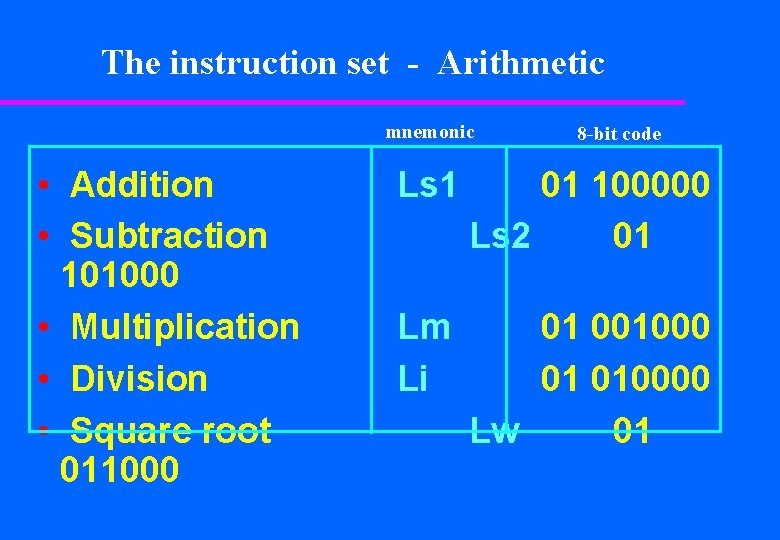

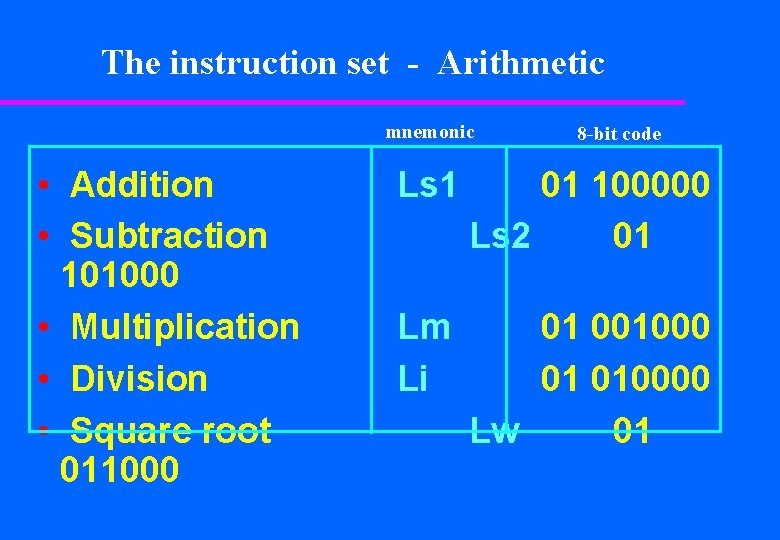

The instruction set - Arithmetic mnemonic • Addition • Subtraction 101000 • Multiplication • Division • Square root 011000 8 -bit code Ls 1 01 100000 Ls 2 01 Lm Li 01 001000 01 010000 Lw 01

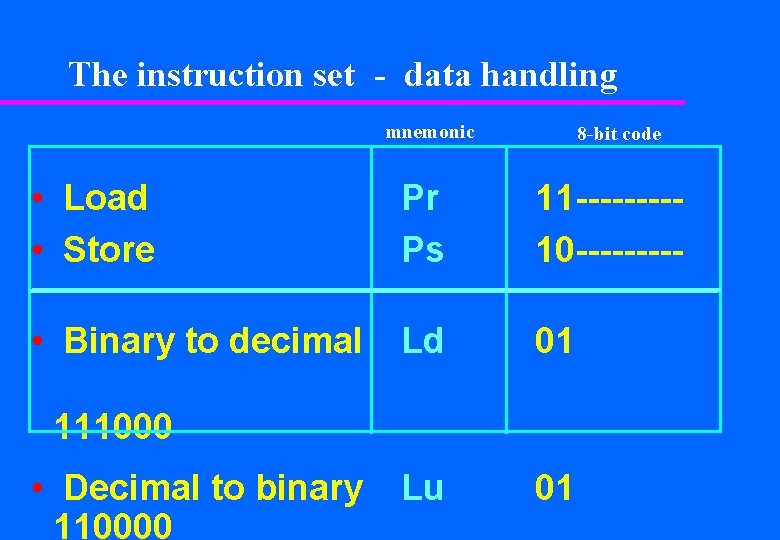

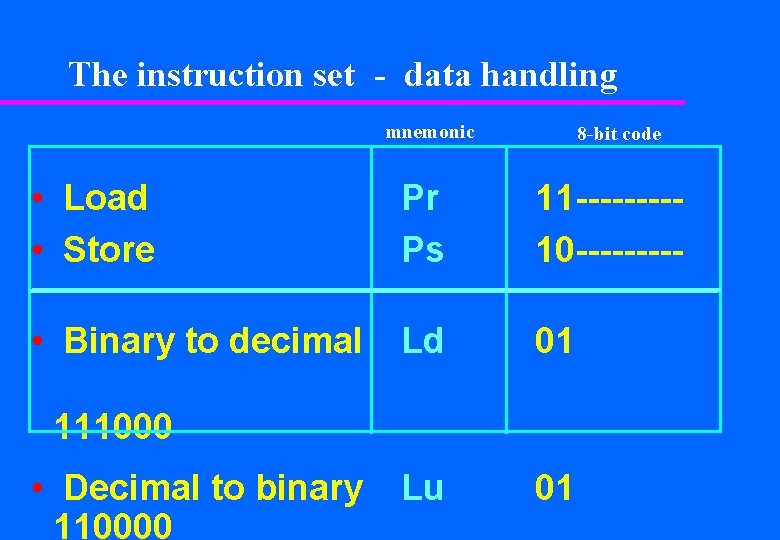

The instruction set - data handling mnemonic 8 -bit code • Load • Store Pr Ps 11 ----10 ----- • Binary to decimal Ld 01 Lu 01 111000 • Decimal to binary 110000

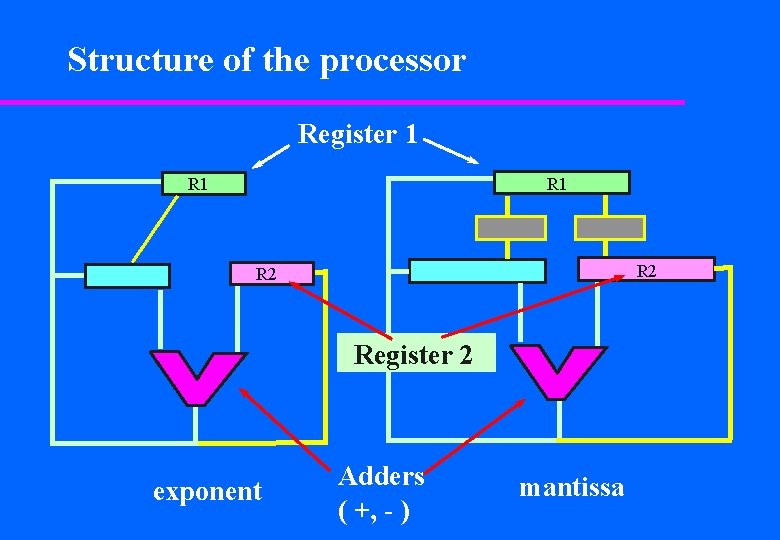

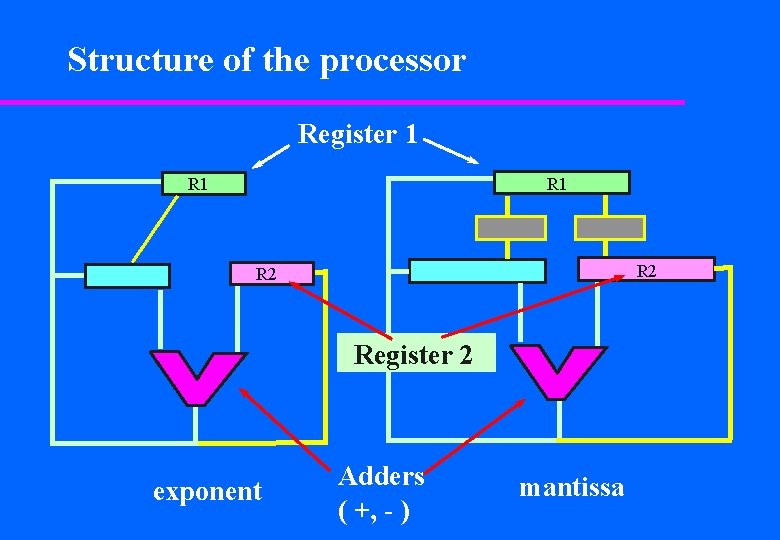

Structure of the processor Register 1 R 1 R 2 Register 2 exponent Adders ( +, - ) mantissa

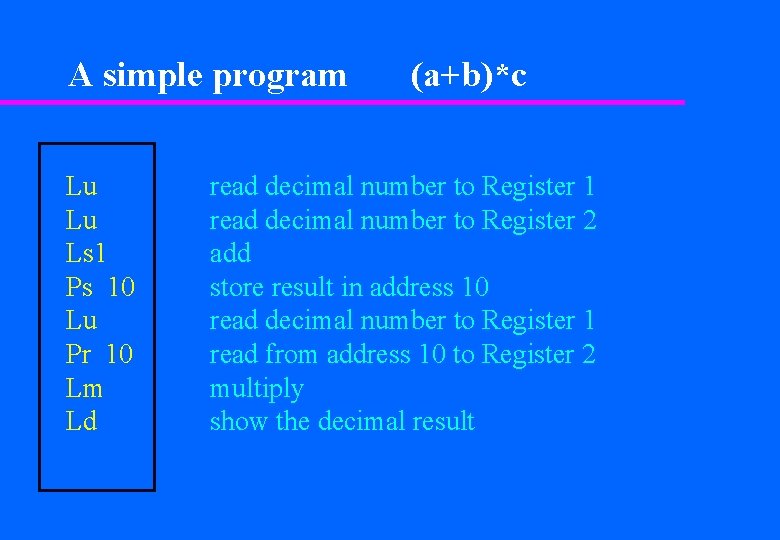

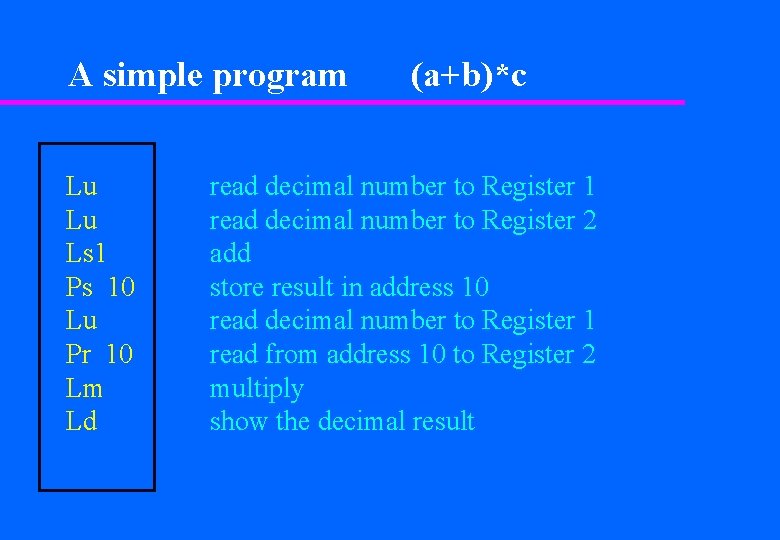

A simple program Lu Lu Ls 1 Ps 10 Lu Pr 10 Lm Ld (a+b)*c read decimal number to Register 1 read decimal number to Register 2 add store result in address 10 read decimal number to Register 1 read from address 10 to Register 2 multiply show the decimal result

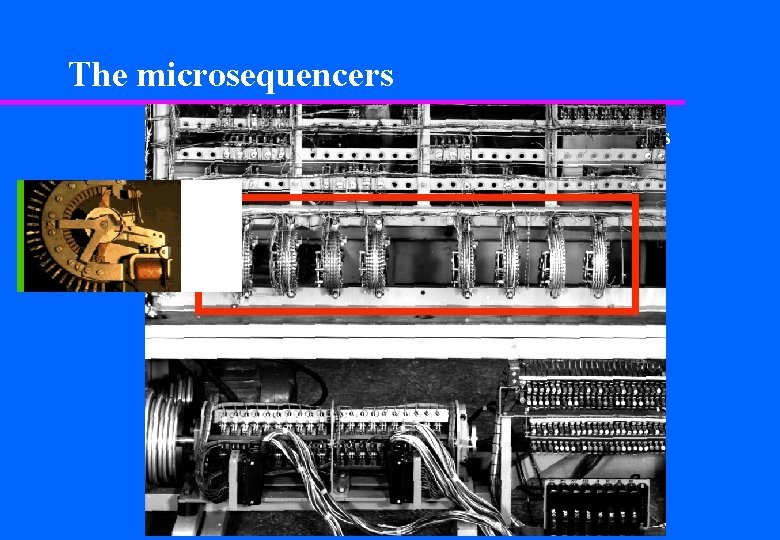

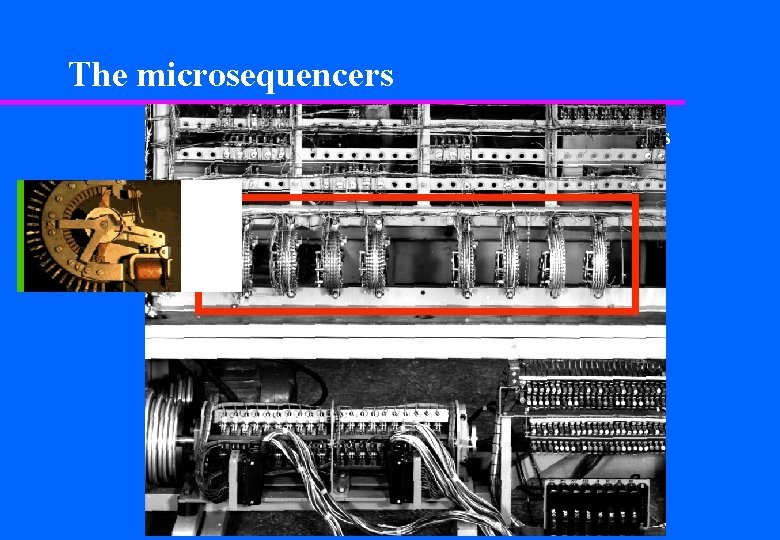

The microsequencers conducting rod: advances one position per cycle step 1 step 2 step 3 step 4 step 5

Pipelining Instruction store next instruction Store operations run in “zero” cycles

Carry look-ahead • Addition was performed in three steps: • compute sum (XOR) • compute all propagated carries • produce final result • With relays addition can be performed in constant time (not logarithmic time)

Shifting • Shifting can be done using a shifting tree (in logarithmic time) • With relays shifting can be done in constant time

Java simulation of the Z 3

The mechanical relays

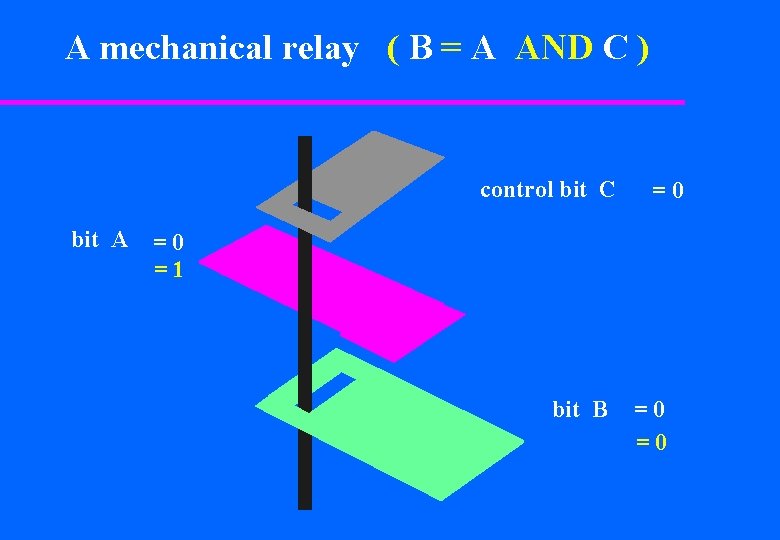

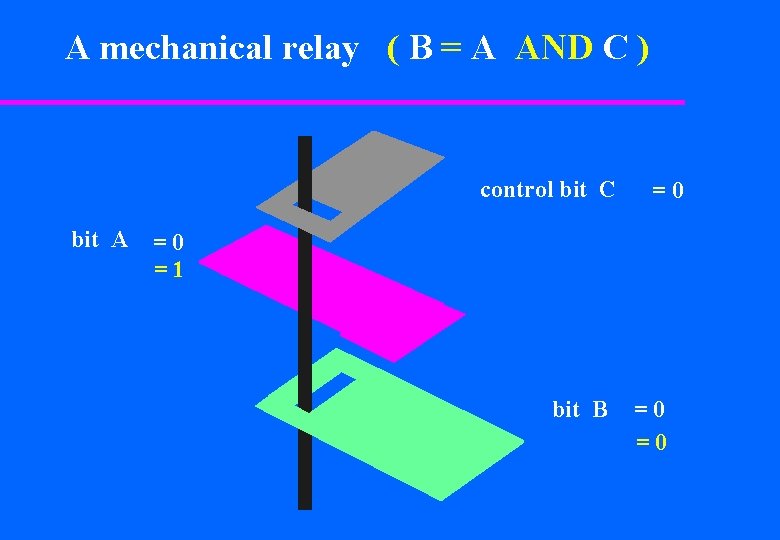

A mechanical relay ( B = A AND C ) control bit C bit A =0 =0 =1 bit B =0 =0

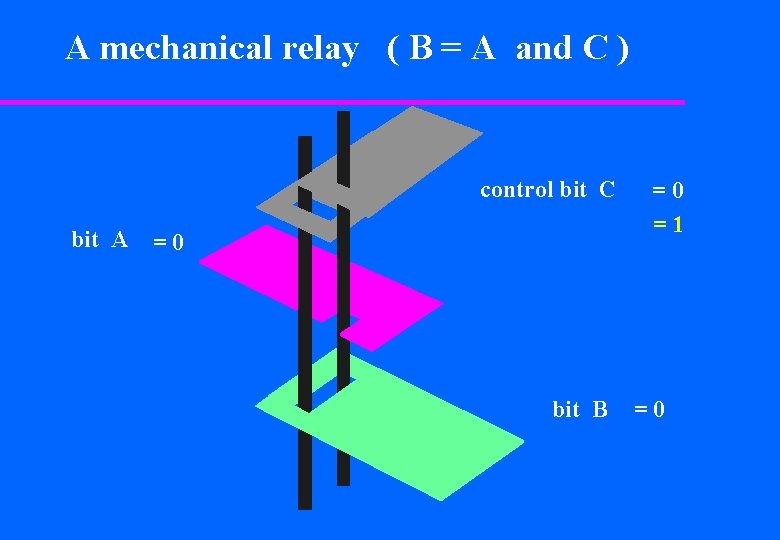

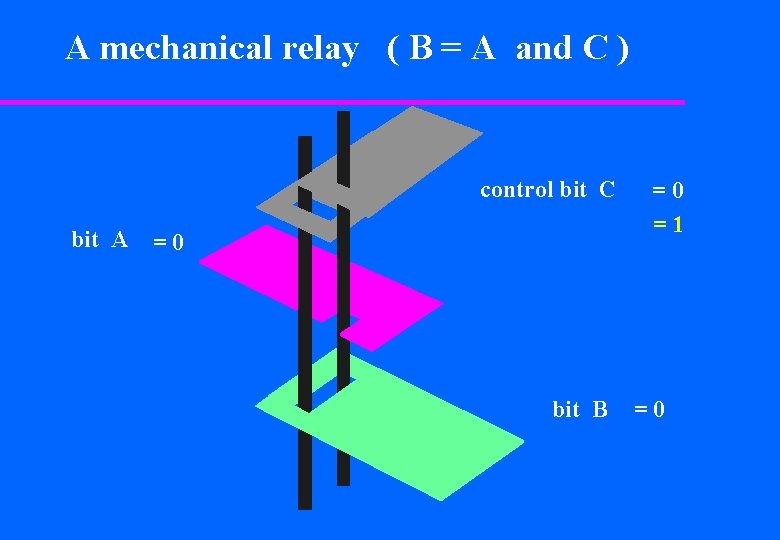

A mechanical relay ( B = A and C ) control bit C bit A =0 bit B =0 =1 =0

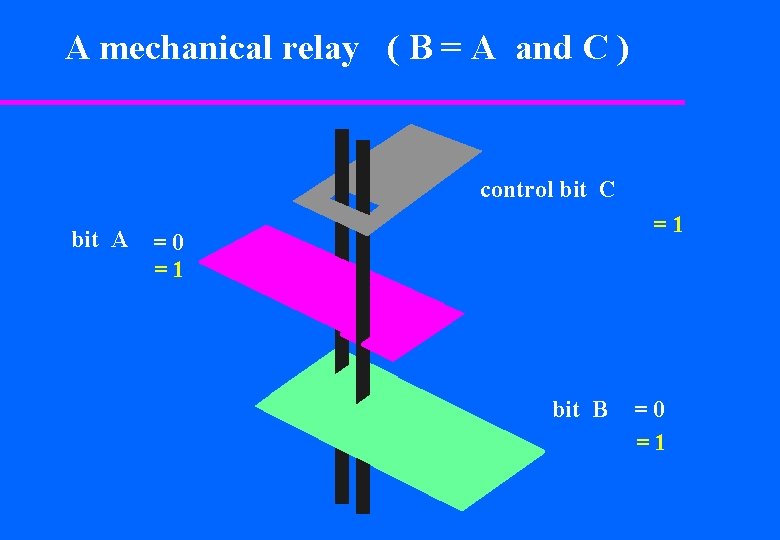

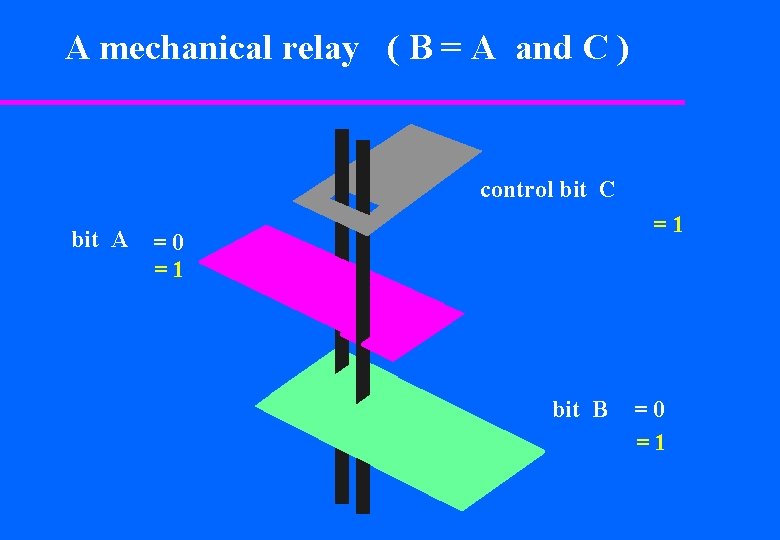

A mechanical relay ( B = A and C ) control bit C bit A =1 =0 =1 bit B =0 =1

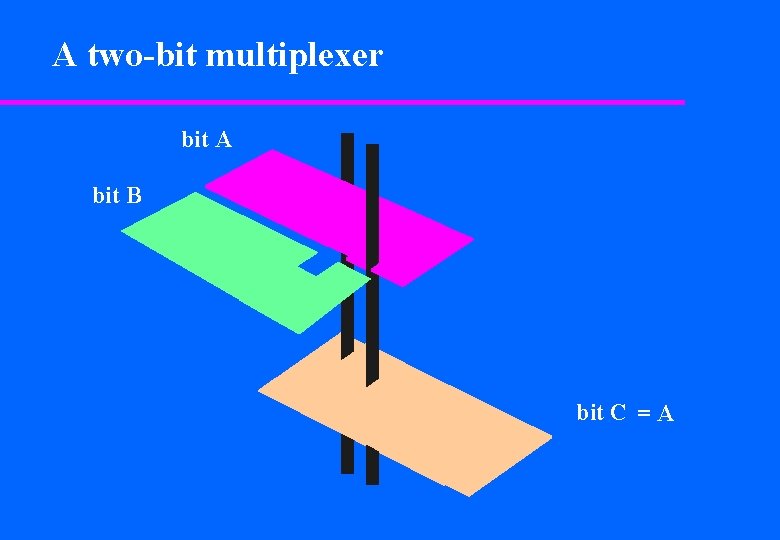

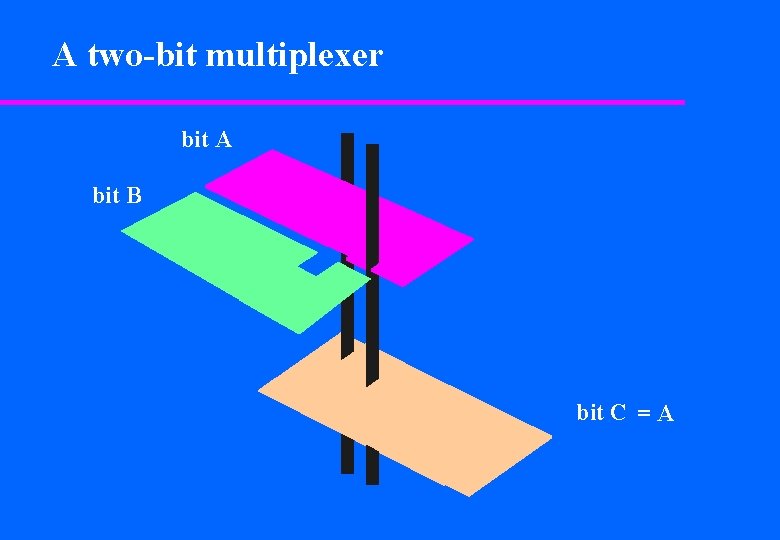

A two-bit multiplexer bit A bit B bit C = A

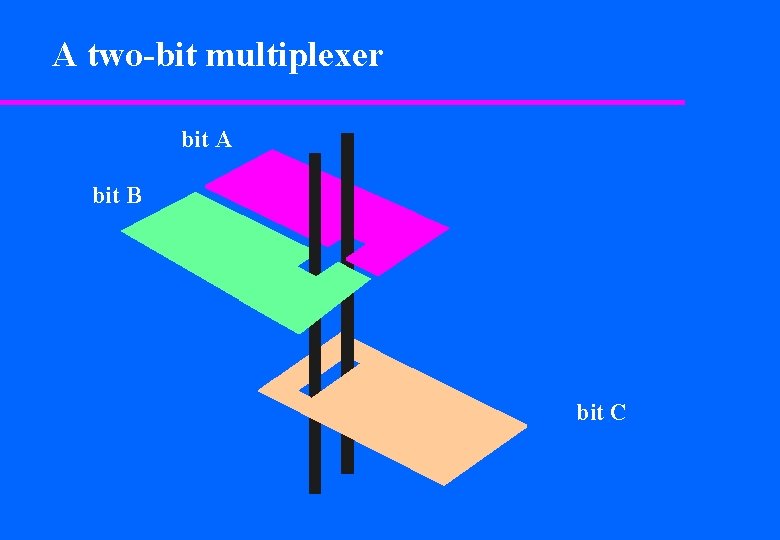

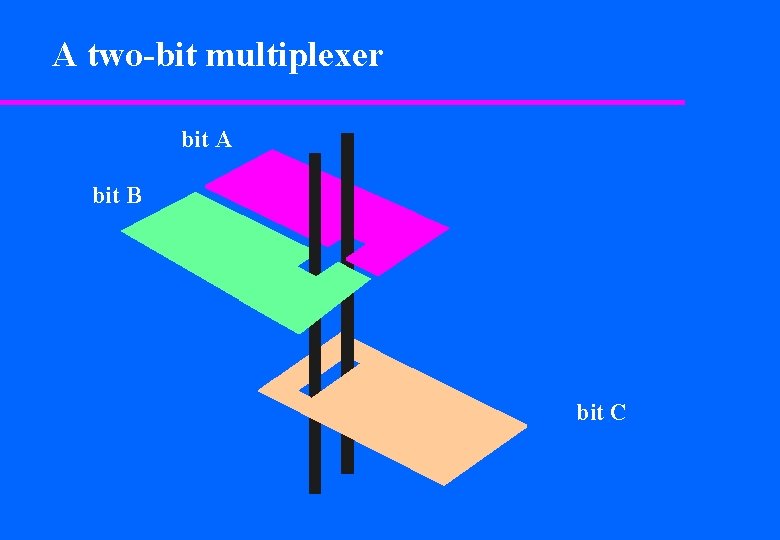

A two-bit multiplexer bit A bit B bit C

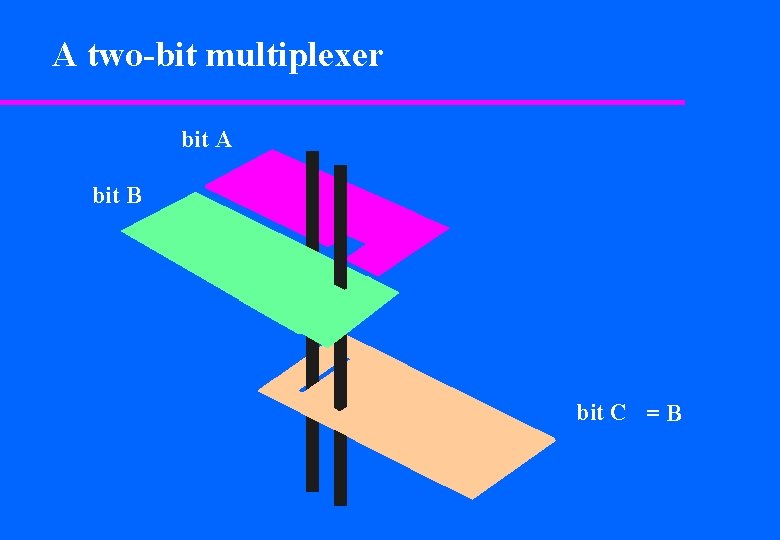

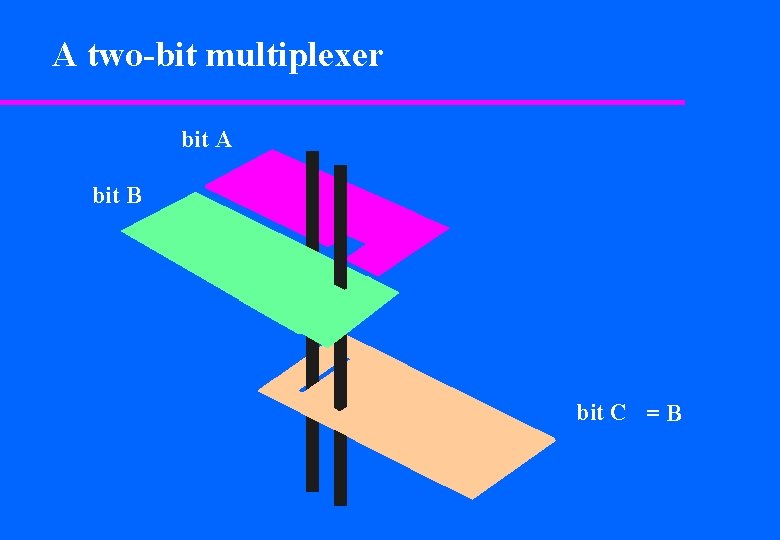

A two-bit multiplexer bit A bit B bit C = B

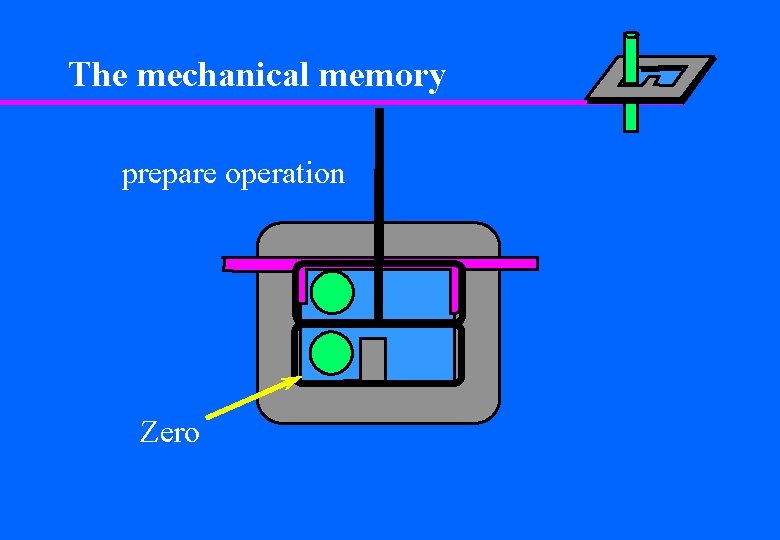

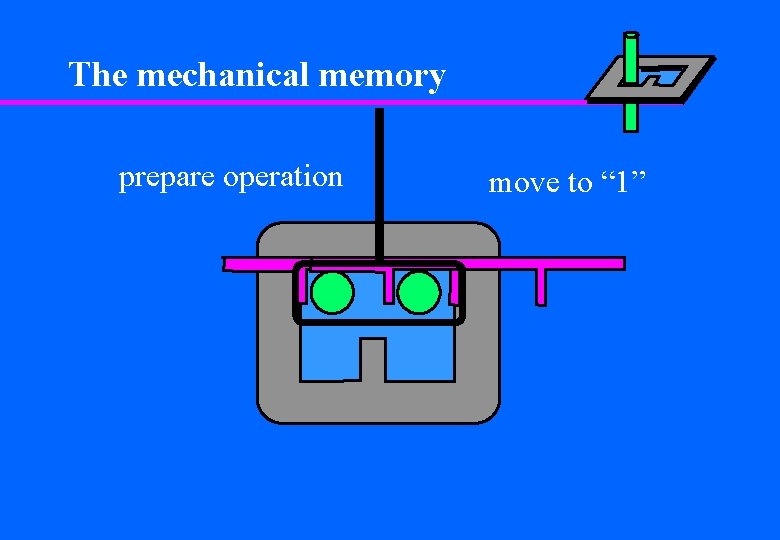

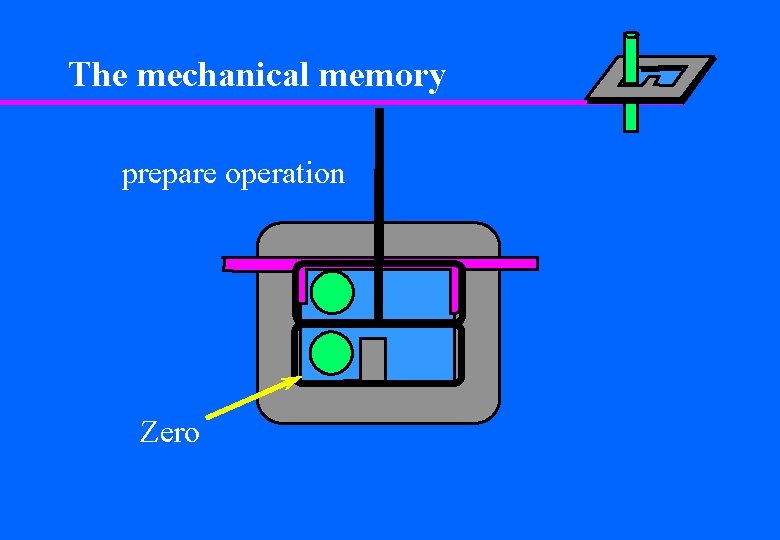

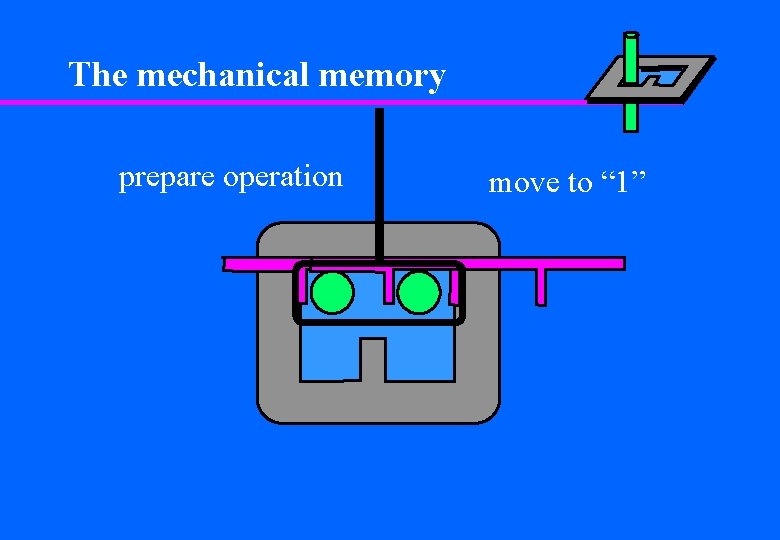

The mechanical memory prepare operation Zero

The mechanical memory prepare operation move to “ 1”

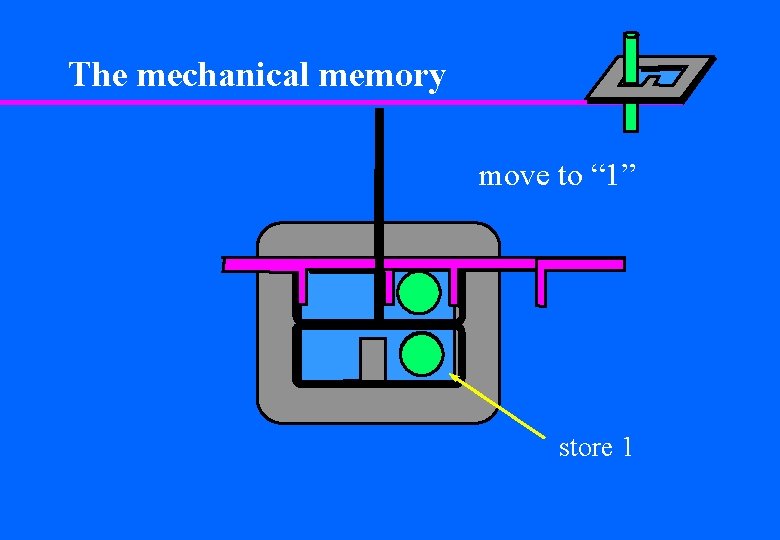

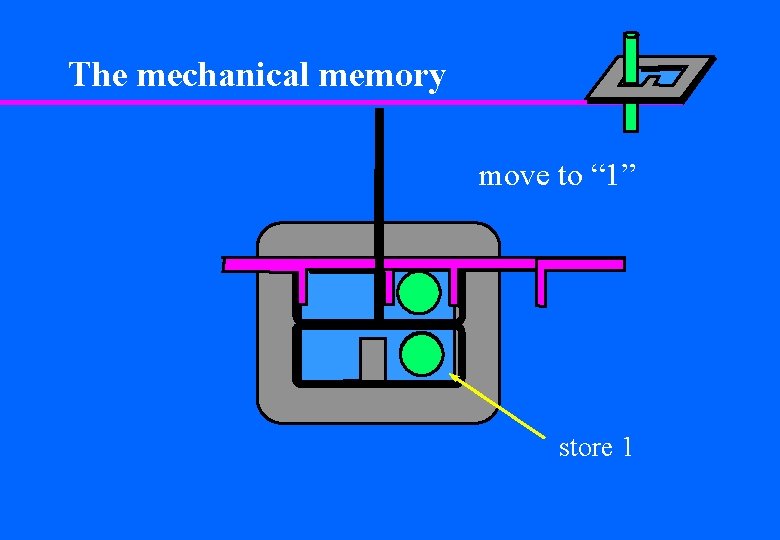

The mechanical memory move to “ 1” store 1

The Z 4 in Zurich

Question: Were the Z 1 and Z 3 universal? YES

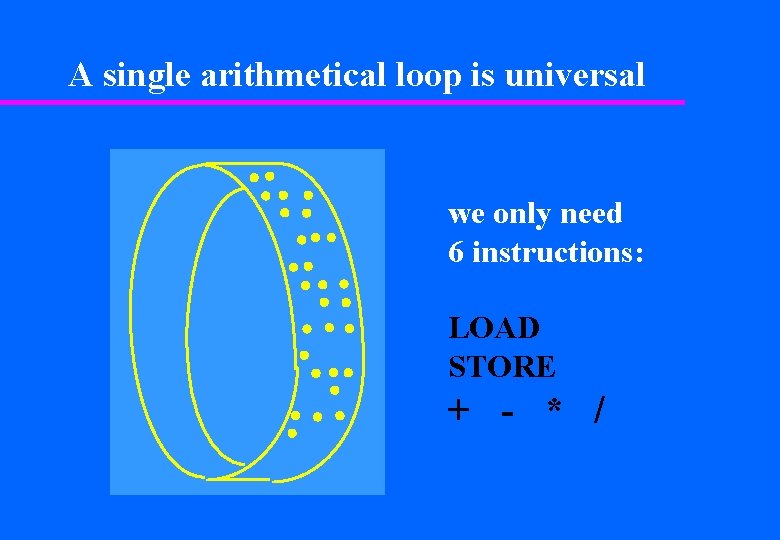

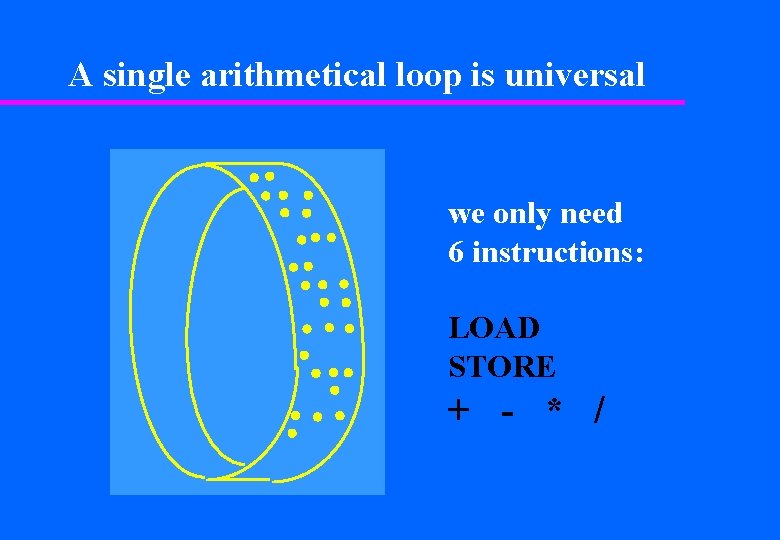

A single arithmetical loop is universal we only need 6 instructions: LOAD STORE + - * /

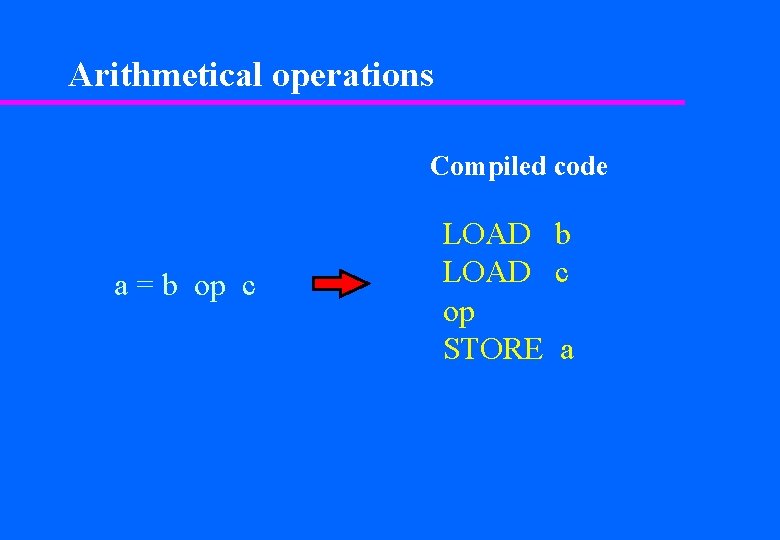

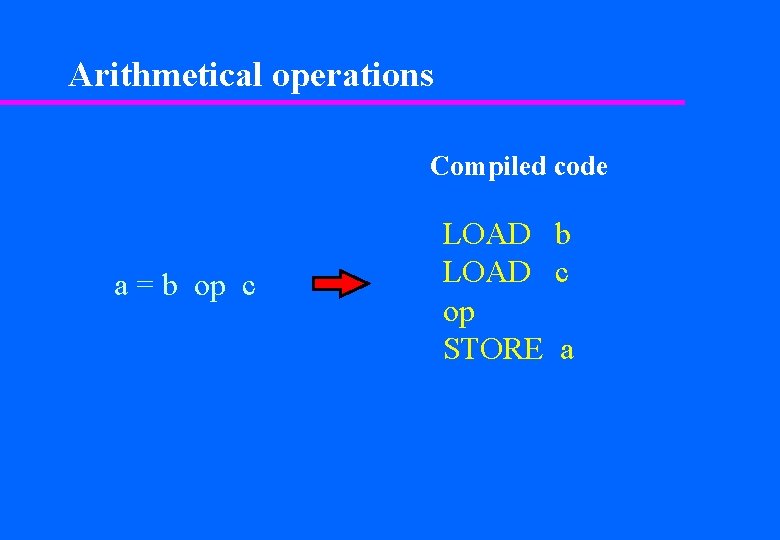

Arithmetical operations Compiled code a = b op c LOAD b LOAD c op STORE a

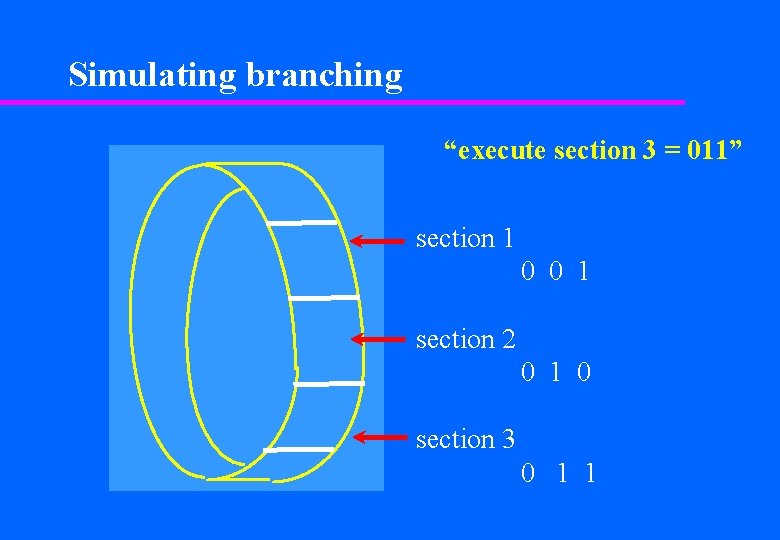

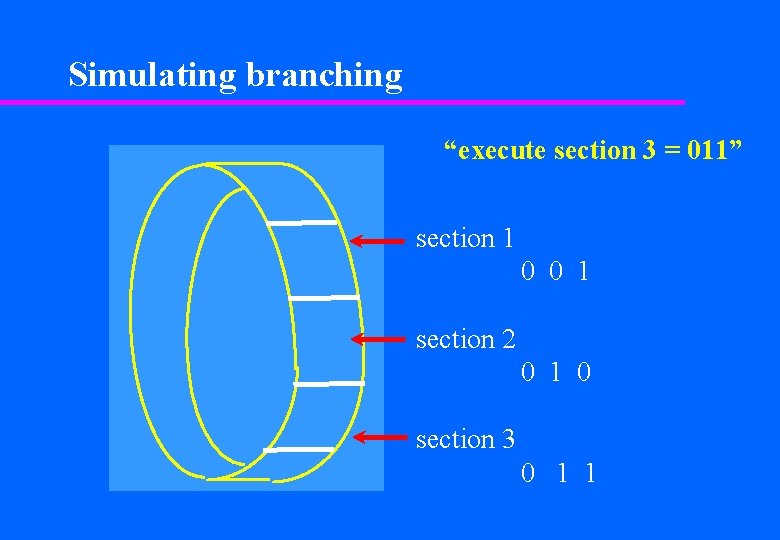

Simulating branching “execute section 3 = 011” section 1 0 0 1 section 2 0 1 0 section 3 0 1 1

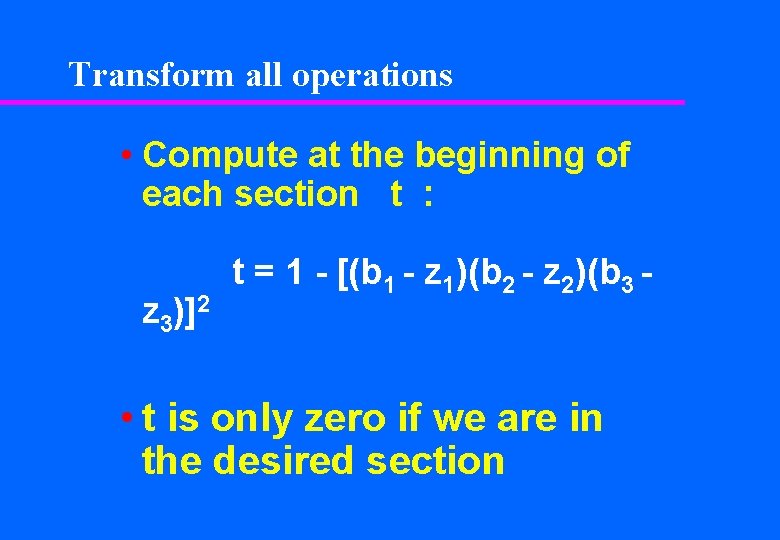

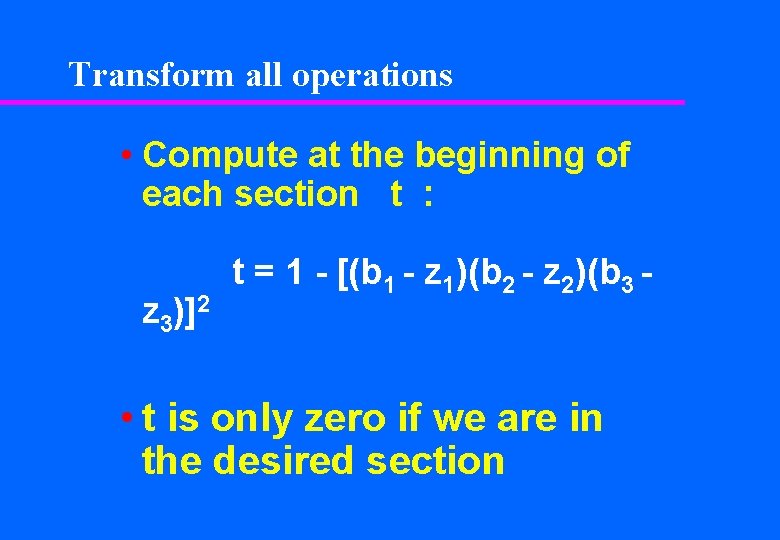

Transform all operations • Compute at the beginning of each section t : z 3)]2 t = 1 - [(b 1 - z 1)(b 2 - z 2)(b 3 - • t is only zero if we are in the desired section

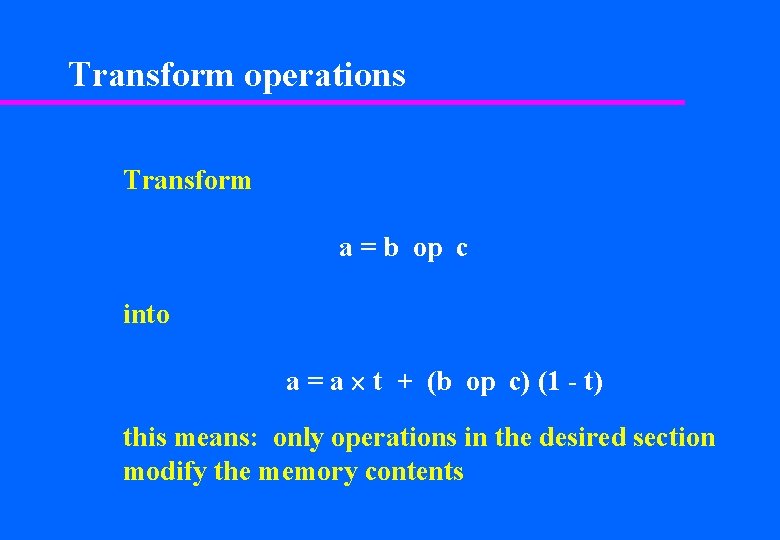

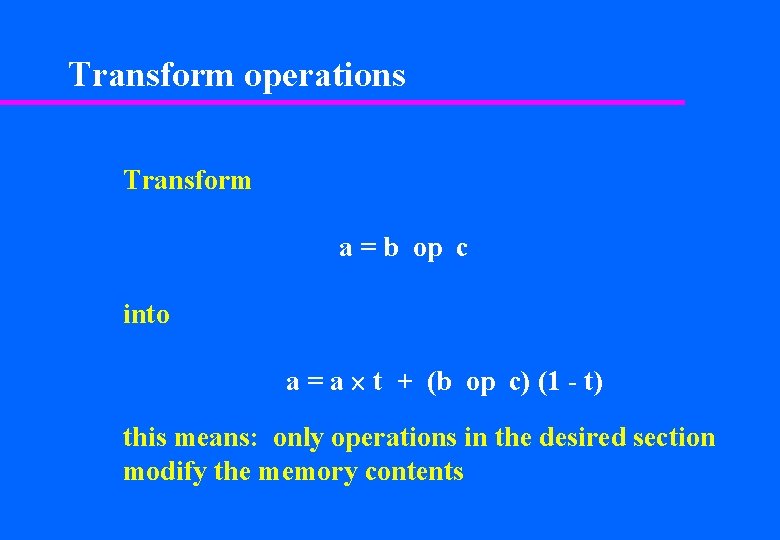

Transform operations Transform a = b op c into a = a ´ t + (b op c) (1 - t) this means: only operations in the desired section modify the memory contents

The halting problem • But how do we stop the loop? -compute 0/q in each iteration -the machine stops when q=0

Summary Theoretical machines The logarithmic machine The „logical“ machine Algebraic machines Z 1 36 -38 Z 2 39 Z 3 39 -41 Special machines S 1 42 S 2 44 Z 4 42 -45

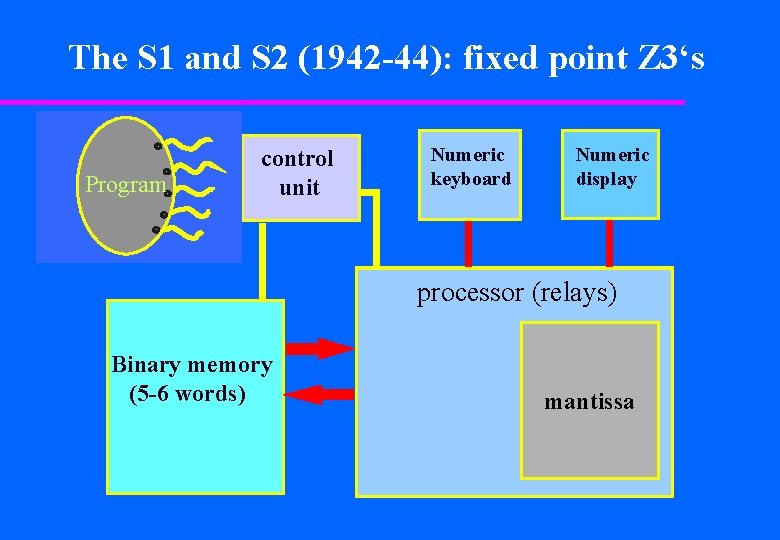

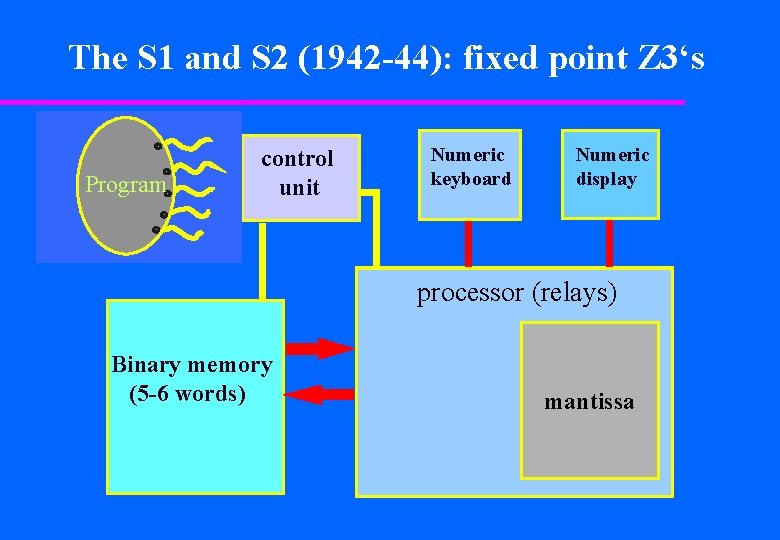

The S 1 and S 2 (1942 -44): fixed point Z 3‘s punched Program tape control unit Numeric keyboard Numeric display FP processor (relays) Binary memory (5 -6 words) exponent mantissa

Die Rekonstruktion der Z 3

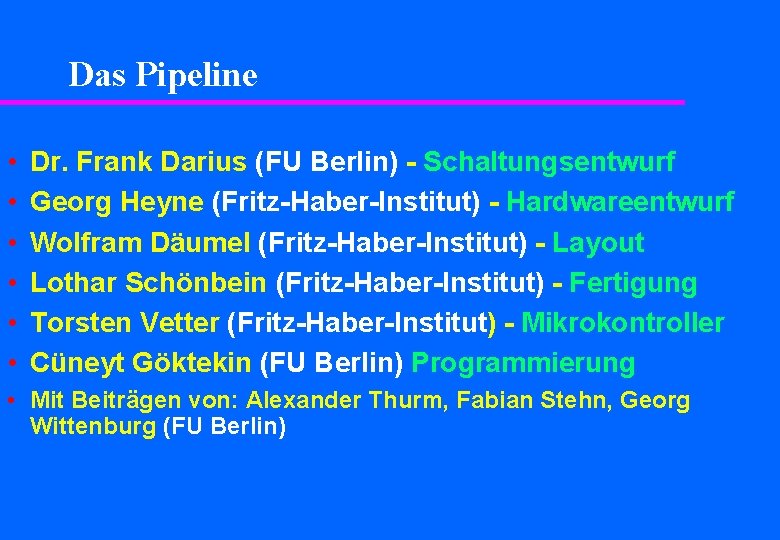

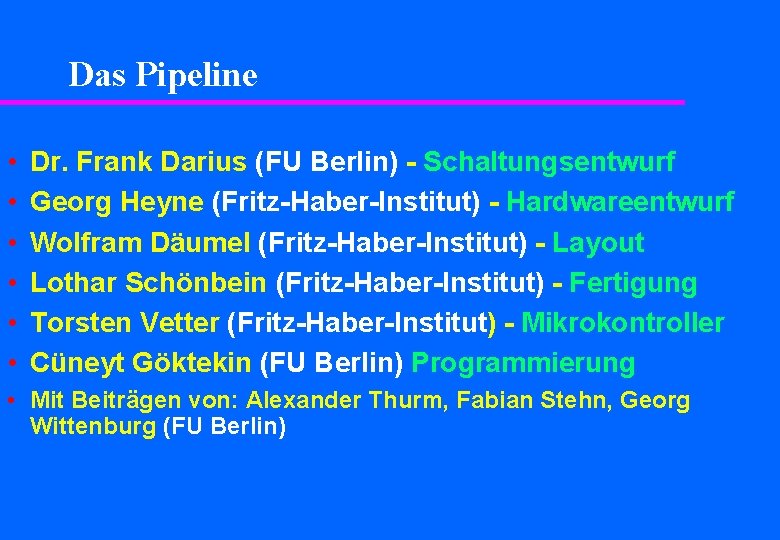

Das Pipeline • • • Dr. Frank Darius (FU Berlin) - Schaltungsentwurf Georg Heyne (Fritz-Haber-Institut) - Hardwareentwurf Wolfram Däumel (Fritz-Haber-Institut) - Layout Lothar Schönbein (Fritz-Haber-Institut) - Fertigung Torsten Vetter (Fritz-Haber-Institut) - Mikrokontroller Cüneyt Göktekin (FU Berlin) Programmierung • Mit Beiträgen von: Alexander Thurm, Fabian Stehn, Georg Wittenburg (FU Berlin)