The 8051 Assembly Language hsabaghianb kashanu ac ir

The 8051 Assembly Language hsabaghianb @ kashanu. ac. ir Microprocessors 1 -1

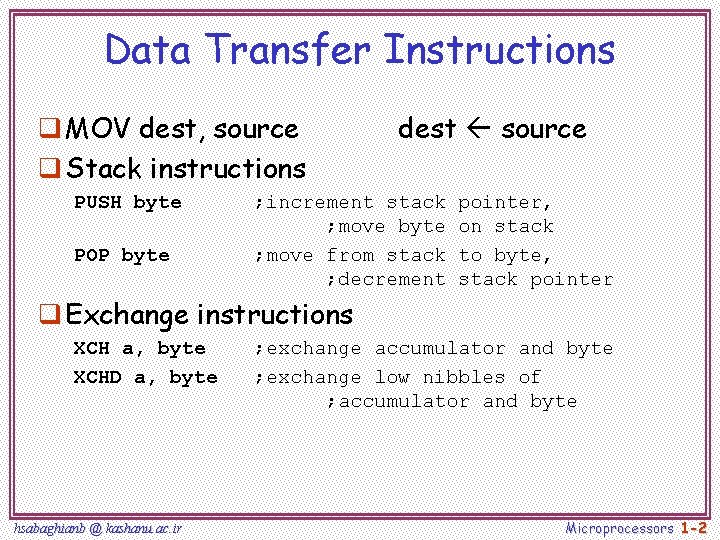

Data Transfer Instructions q MOV dest, source q Stack instructions PUSH byte POP byte dest source ; increment stack ; move byte ; move from stack ; decrement pointer, on stack to byte, stack pointer q Exchange instructions XCH a, byte XCHD a, byte hsabaghianb @ kashanu. ac. ir ; exchange accumulator and byte ; exchange low nibbles of ; accumulator and byte Microprocessors 1 -2

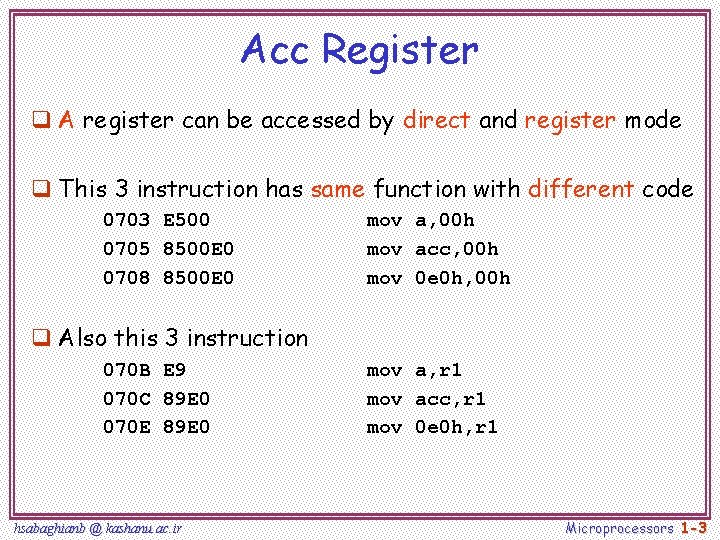

Acc Register q A register can be accessed by direct and register mode q This 3 instruction has same function with different code 0703 E 500 0705 8500 E 0 0708 8500 E 0 mov a, 00 h mov acc, 00 h mov 0 e 0 h, 00 h q Also this 3 instruction 070 B E 9 070 C 89 E 0 070 E 89 E 0 hsabaghianb @ kashanu. ac. ir mov a, r 1 mov acc, r 1 mov 0 e 0 h, r 1 Microprocessors 1 -3

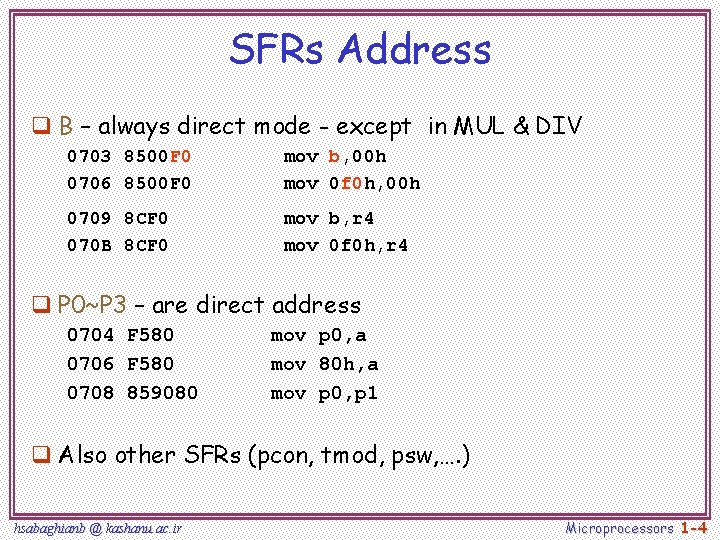

SFRs Address q B – always direct mode - except in MUL & DIV 0703 8500 F 0 0706 8500 F 0 mov b, 00 h mov 0 f 0 h, 00 h 0709 8 CF 0 070 B 8 CF 0 mov b, r 4 mov 0 f 0 h, r 4 q P 0~P 3 – are direct address 0704 F 580 0706 F 580 0708 859080 mov p 0, a mov 80 h, a mov p 0, p 1 q Also other SFRs (pcon, tmod, psw, …. ) hsabaghianb @ kashanu. ac. ir Microprocessors 1 -4

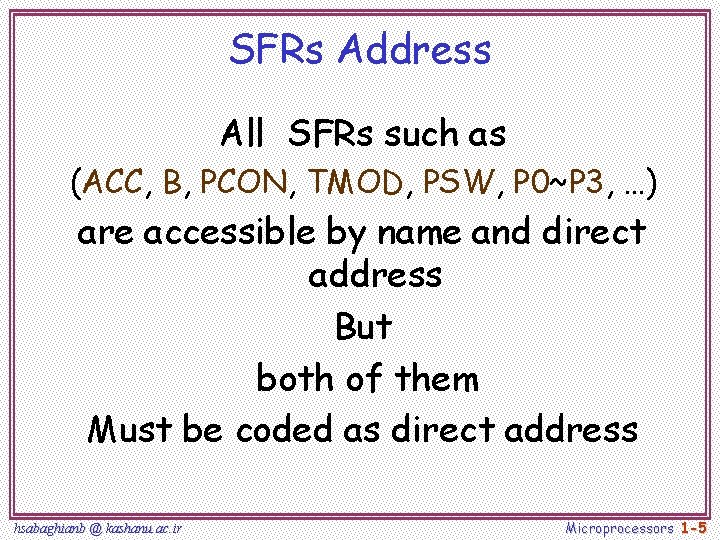

SFRs Address All SFRs such as (ACC, B, PCON, TMOD, PSW, P 0~P 3, …) are accessible by name and direct address But both of them Must be coded as direct address hsabaghianb @ kashanu. ac. ir Microprocessors 1 -5

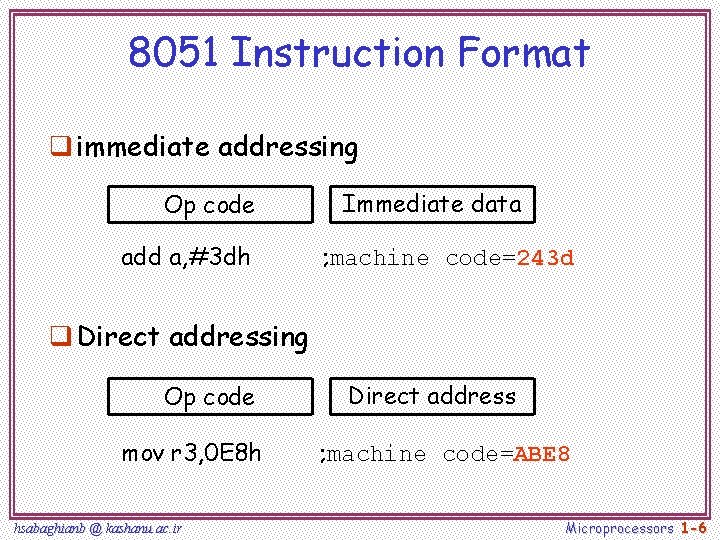

8051 Instruction Format q immediate addressing Op code add a, #3 dh Immediate data ; machine code=243 d q Direct addressing Op code mov r 3, 0 E 8 h hsabaghianb @ kashanu. ac. ir Direct address ; machine code=ABE 8 Microprocessors 1 -6

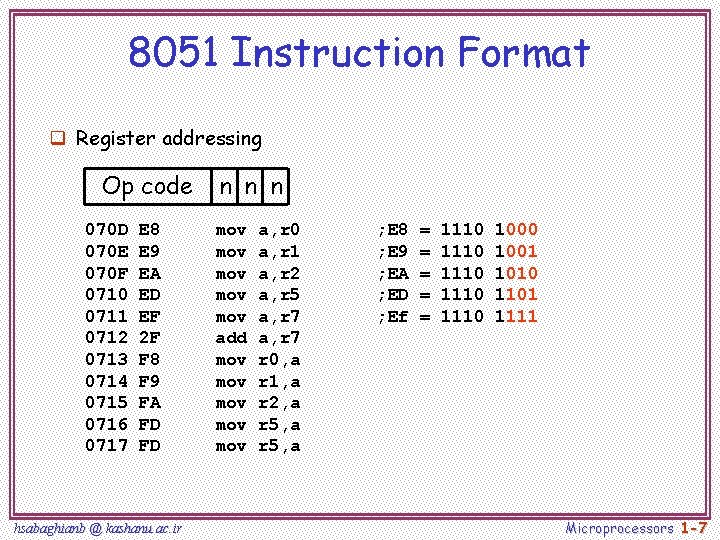

8051 Instruction Format q Register addressing Op code 070 D 070 E 070 F 0710 0711 0712 0713 0714 0715 0716 0717 E 8 E 9 EA ED EF 2 F F 8 F 9 FA FD FD hsabaghianb @ kashanu. ac. ir n n n mov mov mov add mov mov mov a, r 0 a, r 1 a, r 2 a, r 5 a, r 7 r 0, a r 1, a r 2, a r 5, a ; E 8 ; E 9 ; EA ; ED ; Ef = = = 1110 1110 1001 1010 1101 1111 Microprocessors 1 -7

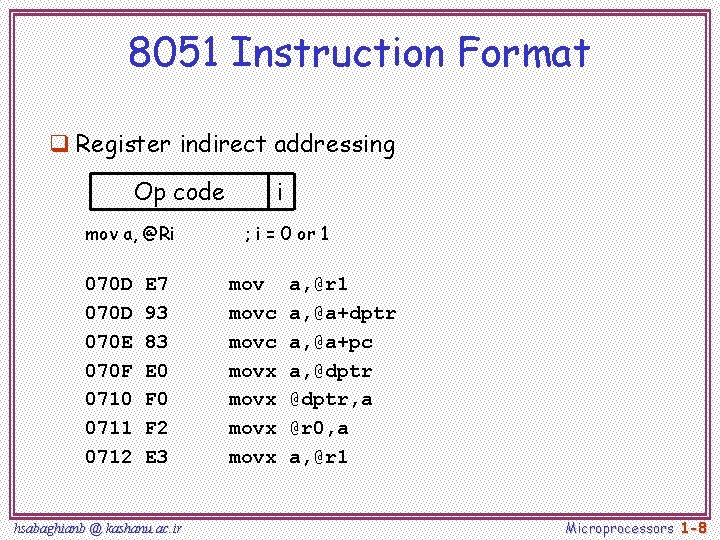

8051 Instruction Format q Register indirect addressing Op code mov a, @Ri 070 D 070 E 070 F 0710 0711 0712 E 7 93 83 E 0 F 2 E 3 hsabaghianb @ kashanu. ac. ir i ; i = 0 or 1 movc movx movx a, @r 1 a, @a+dptr a, @a+pc a, @dptr, a @r 0, a a, @r 1 Microprocessors 1 -8

8051 Instruction Format q relative addressing Op code Relative address here: sjmp here ; machine code=80 FE(FE=-2) Range = (-128 ~ 127) q Absolute addressing (limited in 2 k current mem block) A 10 -A 8 0700 0702 0703 0704 0705 Op code E 106 00 00 hsabaghianb @ kashanu. ac. ir A 7 -A 0 1 2 3 4 5 6 7 8 org 0700 h ajmp next nop nop 07 FEh ; next=706 h next: end Microprocessors 1 -9

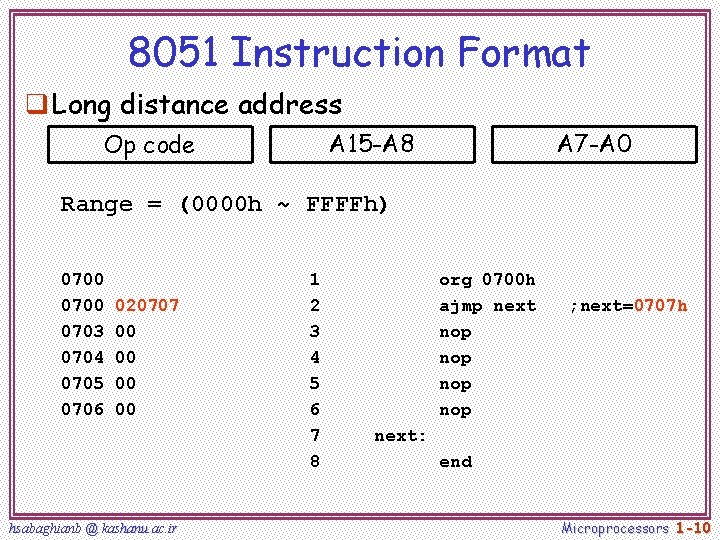

8051 Instruction Format q Long distance address A 15 -A 8 Op code A 7 -A 0 Range = (0000 h ~ FFFFh) 0700 0703 0704 0705 0706 020707 00 00 hsabaghianb @ kashanu. ac. ir 1 2 3 4 5 6 7 8 org 0700 h ajmp next nop nop ; next=0707 h next: end Microprocessors 1 -10

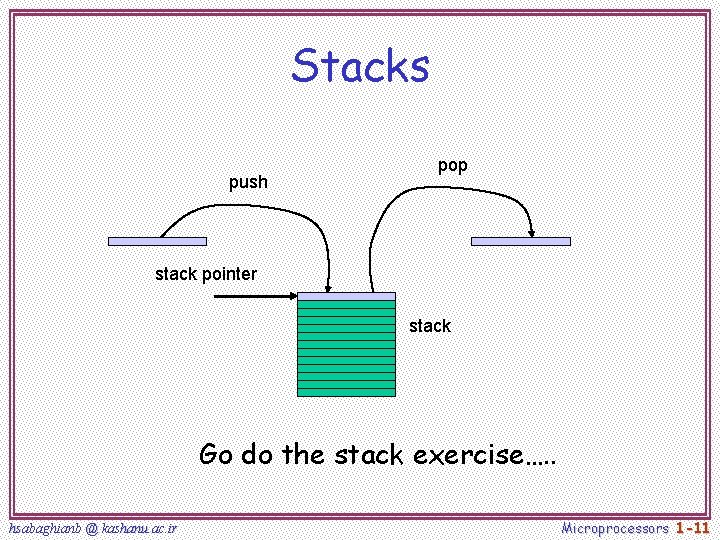

Stacks push pop stack pointer stack Go do the stack exercise…. . hsabaghianb @ kashanu. ac. ir Microprocessors 1 -11

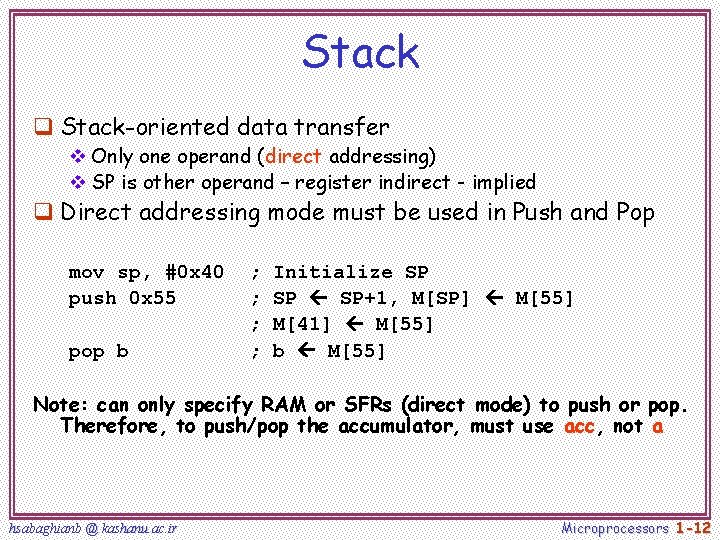

Stack q Stack-oriented data transfer v Only one operand (direct addressing) v SP is other operand – register indirect - implied q Direct addressing mode must be used in Push and Pop mov sp, #0 x 40 push 0 x 55 pop b ; ; Initialize SP SP SP+1, M[SP] M[55] M[41] M[55] b M[55] Note: can only specify RAM or SFRs (direct mode) to push or pop. Therefore, to push/pop the accumulator, must use acc, not a hsabaghianb @ kashanu. ac. ir Microprocessors 1 -12

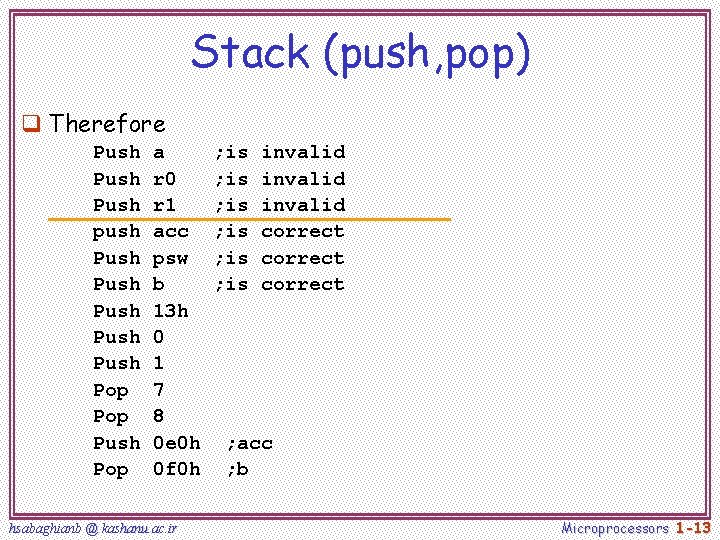

Stack (push, pop) q Therefore Push push Push Pop Push Pop a r 0 r 1 acc psw b 13 h 0 1 7 8 0 e 0 h 0 f 0 h hsabaghianb @ kashanu. ac. ir ; is ; is invalid correct ; acc ; b Microprocessors 1 -13

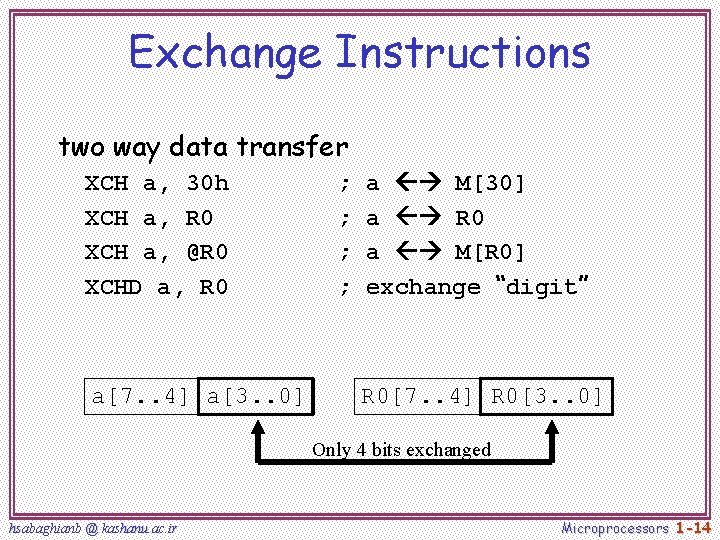

Exchange Instructions two way data transfer XCH a, 30 h XCH a, R 0 XCH a, @R 0 XCHD a, R 0 a[7. . 4] a[3. . 0] ; ; a M[30] a R 0 a M[R 0] exchange “digit” R 0[7. . 4] R 0[3. . 0] Only 4 bits exchanged hsabaghianb @ kashanu. ac. ir Microprocessors 1 -14

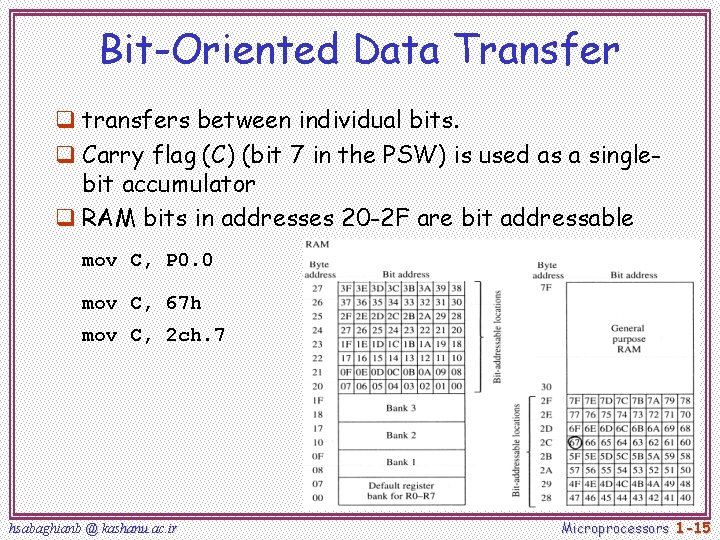

Bit-Oriented Data Transfer q transfers between individual bits. q Carry flag (C) (bit 7 in the PSW) is used as a singlebit accumulator q RAM bits in addresses 20 -2 F are bit addressable mov C, P 0. 0 mov C, 67 h mov C, 2 ch. 7 hsabaghianb @ kashanu. ac. ir Microprocessors 1 -15

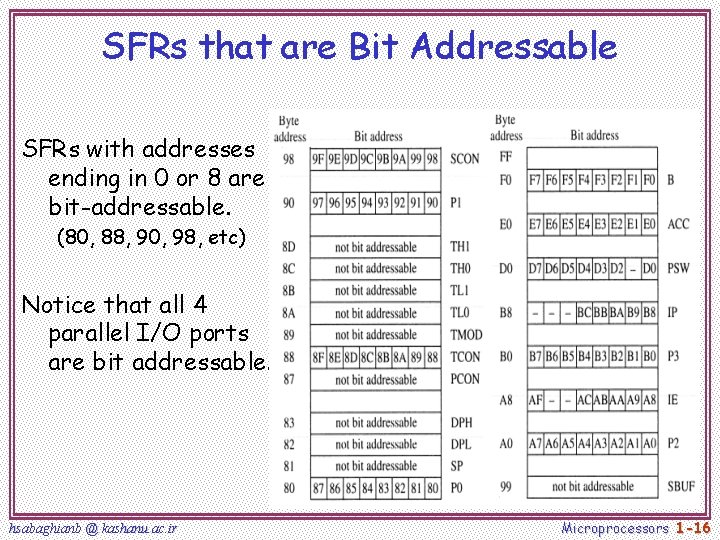

SFRs that are Bit Addressable SFRs with addresses ending in 0 or 8 are bit-addressable. (80, 88, 90, 98, etc) Notice that all 4 parallel I/O ports are bit addressable. hsabaghianb @ kashanu. ac. ir Microprocessors 1 -16

Data Processing Instructions Arithmetic Instructions Logic Instructions hsabaghianb @ kashanu. ac. ir Microprocessors 1 -17

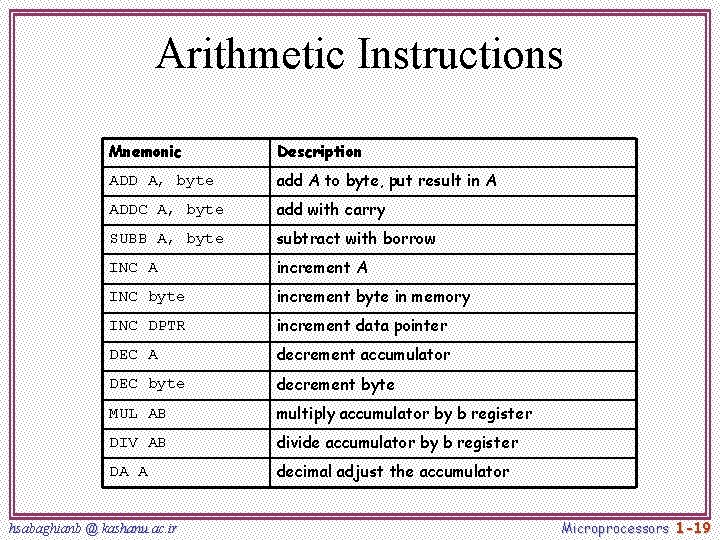

Arithmetic Instructions q Add q Subtract q Increment q Decrement q Multiply q Divide q Decimal adjust hsabaghianb @ kashanu. ac. ir Microprocessors 1 -18

Arithmetic Instructions Mnemonic Description ADD A, byte add A to byte, put result in A ADDC A, byte add with carry SUBB A, byte subtract with borrow INC A increment A INC byte increment byte in memory INC DPTR increment data pointer DEC A decrement accumulator DEC byte decrement byte MUL AB multiply accumulator by b register DIV AB divide accumulator by b register DA A decimal adjust the accumulator hsabaghianb @ kashanu. ac. ir Microprocessors 1 -19

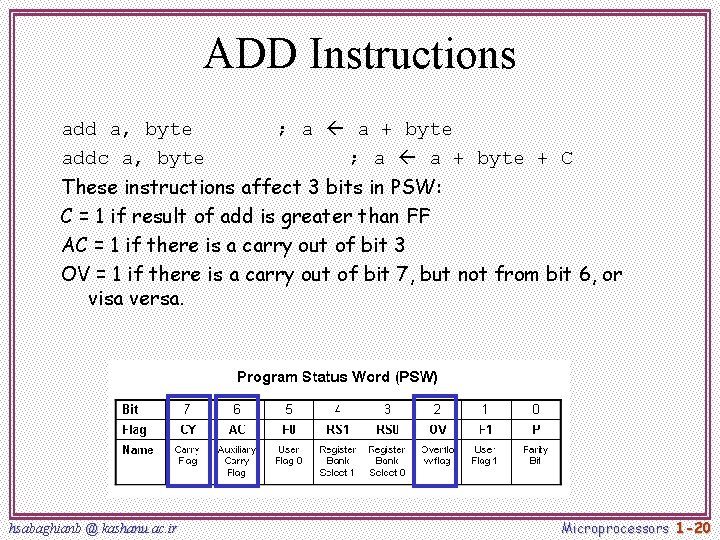

ADD Instructions add a, byte addc a, byte ; a a + byte + C These instructions affect 3 bits in PSW: C = 1 if result of add is greater than FF AC = 1 if there is a carry out of bit 3 OV = 1 if there is a carry out of bit 7, but not from bit 6, or visa versa. hsabaghianb @ kashanu. ac. ir Microprocessors 1 -20

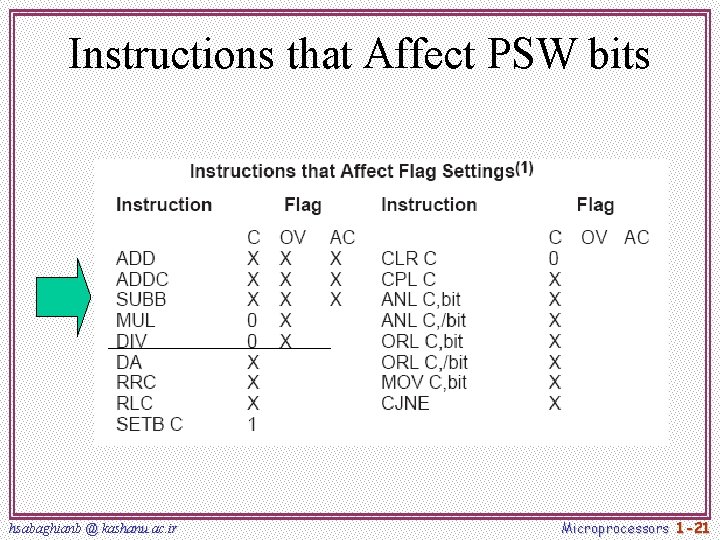

Instructions that Affect PSW bits hsabaghianb @ kashanu. ac. ir Microprocessors 1 -21

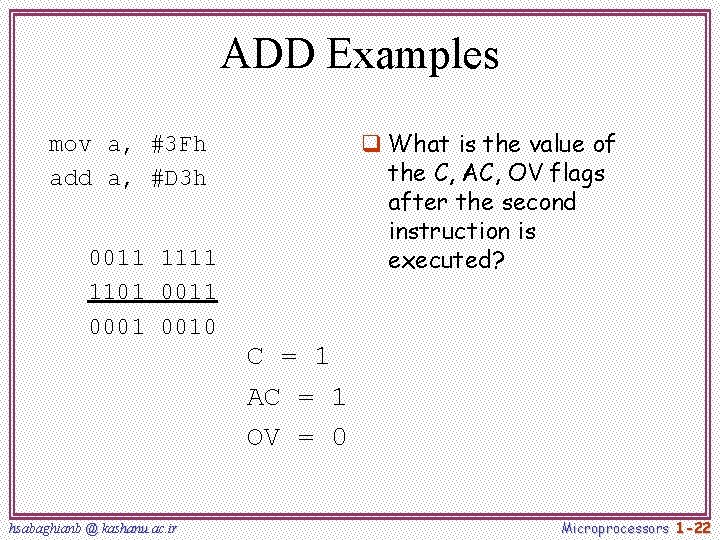

ADD Examples q What is the value of the C, AC, OV flags after the second instruction is executed? mov a, #3 Fh add a, #D 3 h 0011 1101 0011 0001 0010 hsabaghianb @ kashanu. ac. ir C = 1 AC = 1 OV = 0 Microprocessors 1 -22

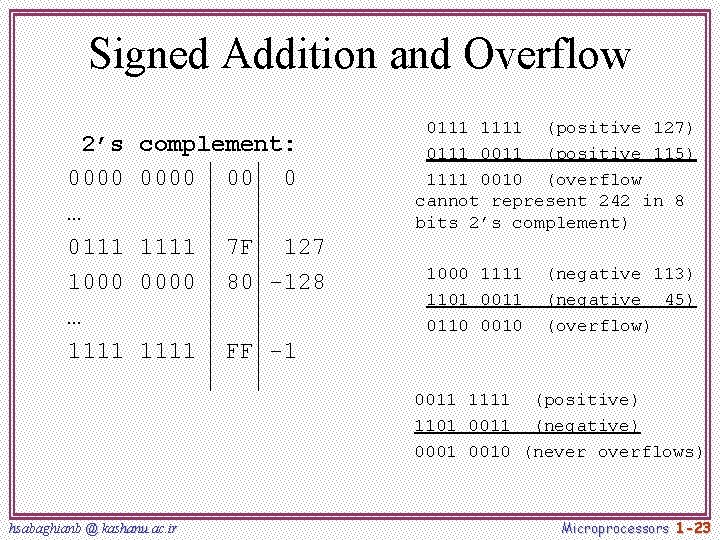

Signed Addition and Overflow 2’s 0000 … 0111 1000 … 1111 complement: 0000 00 0 1111 0000 7 F 127 80 -128 1111 FF -1 0111 1111 (positive 127) 0111 0011 (positive 115) 1111 0010 (overflow cannot represent 242 in 8 bits 2’s complement) 1000 1111 1101 0011 0110 0010 (negative 113) (negative 45) (overflow) 0011 1111 (positive) 1101 0011 (negative) 0001 0010 (never overflows) hsabaghianb @ kashanu. ac. ir Microprocessors 1 -23

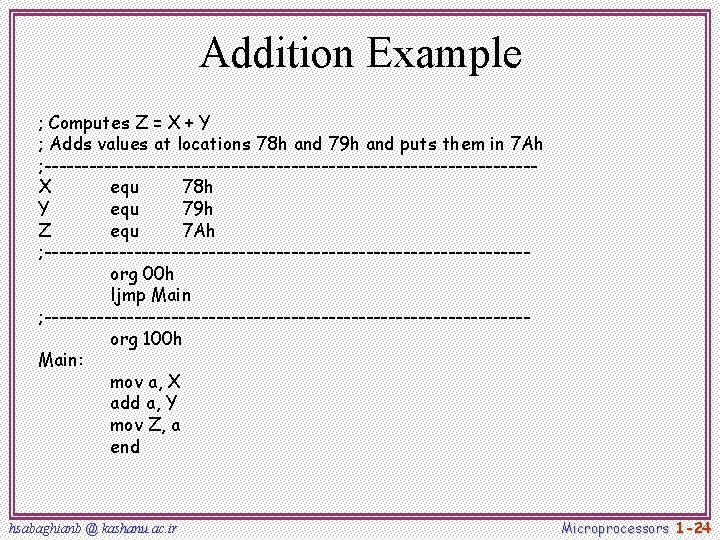

Addition Example ; Computes Z = X + Y ; Adds values at locations 78 h and 79 h and puts them in 7 Ah ; ---------------------------------X equ 78 h Y equ 79 h Z equ 7 Ah ; --------------------------------org 00 h ljmp Main ; --------------------------------org 100 h Main: mov a, X add a, Y mov Z, a end hsabaghianb @ kashanu. ac. ir Microprocessors 1 -24

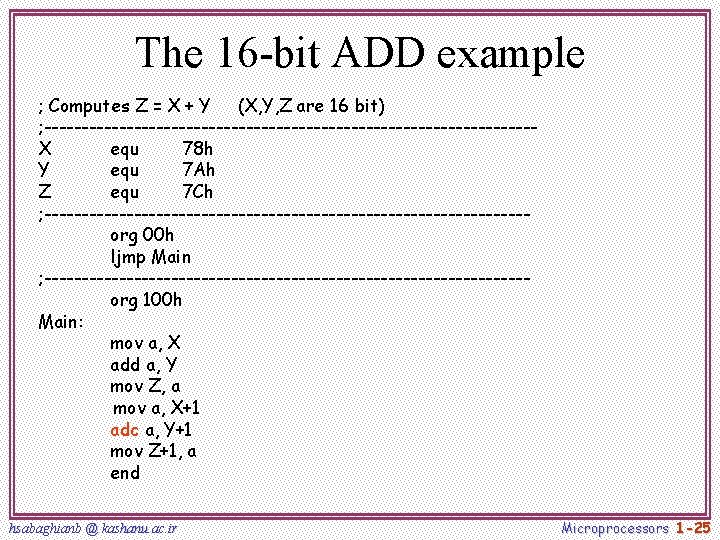

The 16 -bit ADD example ; Computes Z = X + Y (X, Y, Z are 16 bit) ; ---------------------------------X equ 78 h Y equ 7 Ah Z equ 7 Ch ; --------------------------------org 00 h ljmp Main ; --------------------------------org 100 h Main: mov a, X add a, Y mov Z, a mov a, X+1 adc a, Y+1 mov Z+1, a end hsabaghianb @ kashanu. ac. ir Microprocessors 1 -25

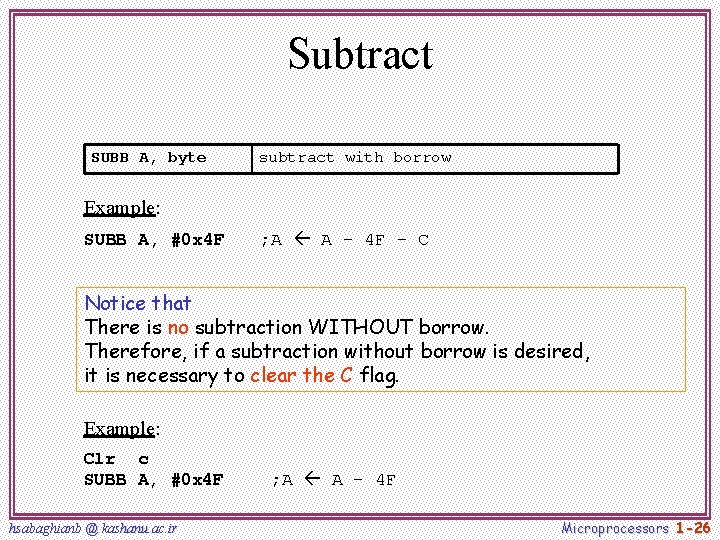

Subtract SUBB A, byte subtract with borrow Example: SUBB A, #0 x 4 F ; A A – 4 F – C Notice that There is no subtraction WITHOUT borrow. Therefore, if a subtraction without borrow is desired, it is necessary to clear the C flag. Example: Clr c SUBB A, #0 x 4 F hsabaghianb @ kashanu. ac. ir ; A A – 4 F Microprocessors 1 -26

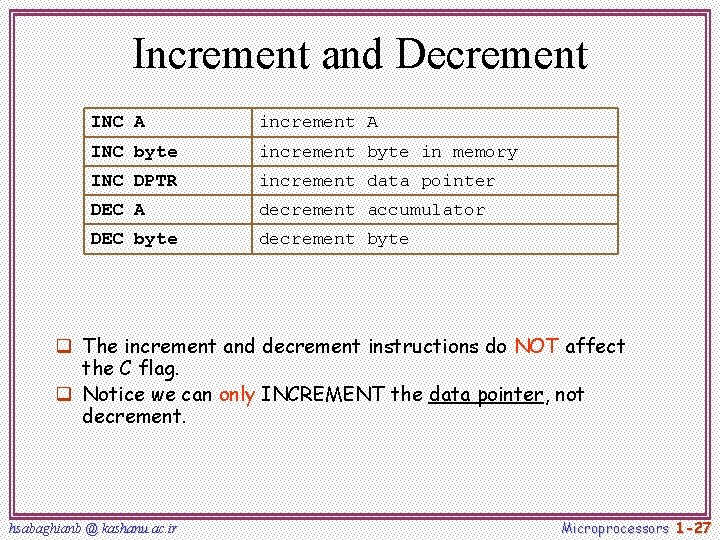

Increment and Decrement INC A increment A INC byte increment byte in memory INC DPTR increment data pointer DEC A decrement accumulator DEC byte decrement byte q The increment and decrement instructions do NOT affect the C flag. q Notice we can only INCREMENT the data pointer, not decrement. hsabaghianb @ kashanu. ac. ir Microprocessors 1 -27

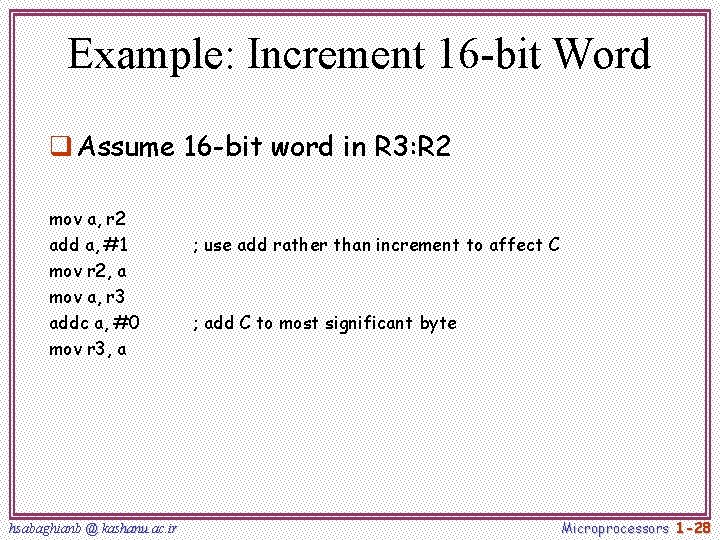

Example: Increment 16 -bit Word q Assume 16 -bit word in R 3: R 2 mov a, r 2 add a, #1 mov r 2, a mov a, r 3 addc a, #0 mov r 3, a hsabaghianb @ kashanu. ac. ir ; use add rather than increment to affect C ; add C to most significant byte Microprocessors 1 -28

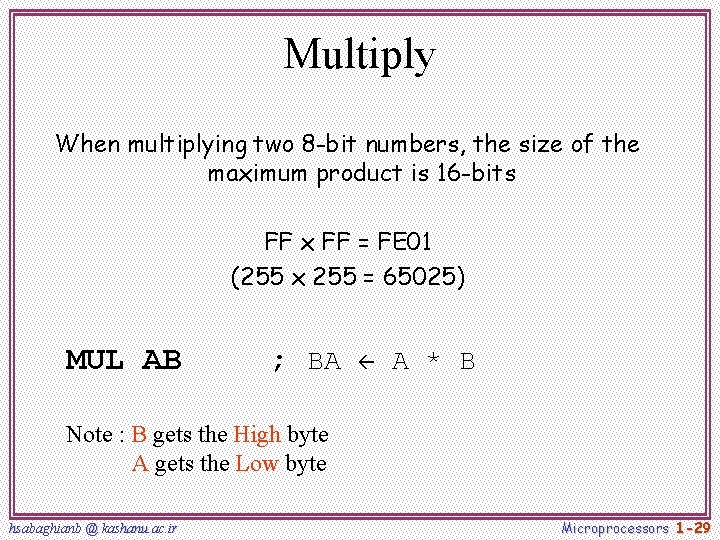

Multiply When multiplying two 8 -bit numbers, the size of the maximum product is 16 -bits FF x FF = FE 01 (255 x 255 = 65025) MUL AB ; BA A * B Note : B gets the High byte A gets the Low byte hsabaghianb @ kashanu. ac. ir Microprocessors 1 -29

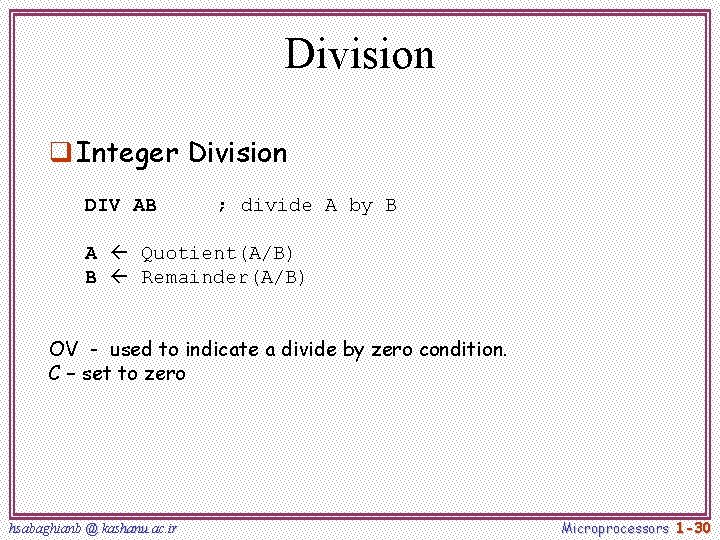

Division q Integer Division DIV AB ; divide A by B A Quotient(A/B) B Remainder(A/B) OV - used to indicate a divide by zero condition. C – set to zero hsabaghianb @ kashanu. ac. ir Microprocessors 1 -30

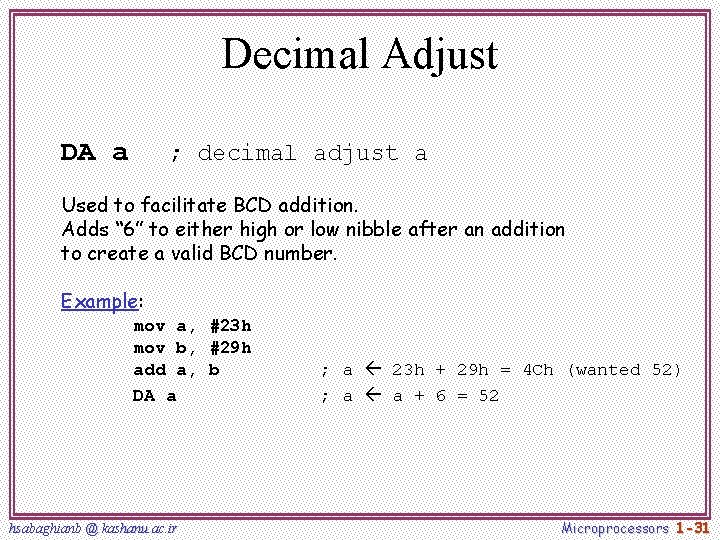

Decimal Adjust DA a ; decimal adjust a Used to facilitate BCD addition. Adds “ 6” to either high or low nibble after an addition to create a valid BCD number. Example: mov a, #23 h mov b, #29 h add a, b DA a hsabaghianb @ kashanu. ac. ir ; a 23 h + 29 h = 4 Ch (wanted 52) ; a a + 6 = 52 Microprocessors 1 -31

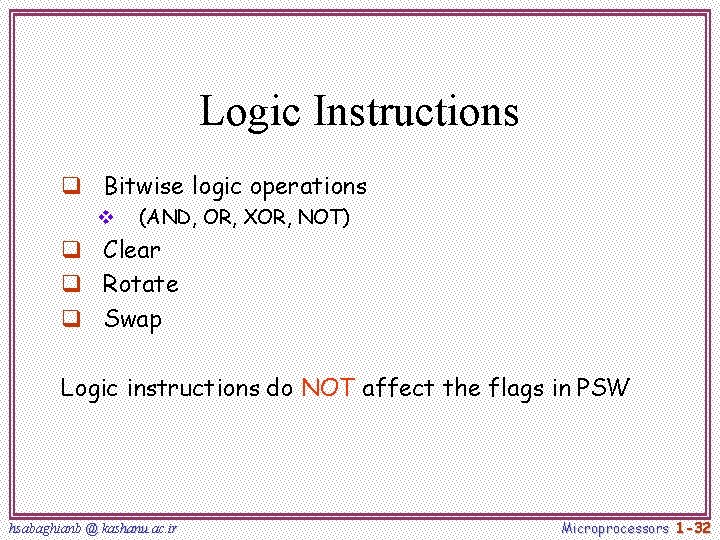

Logic Instructions q Bitwise logic operations v (AND, OR, XOR, NOT) q Clear q Rotate q Swap Logic instructions do NOT affect the flags in PSW hsabaghianb @ kashanu. ac. ir Microprocessors 1 -32

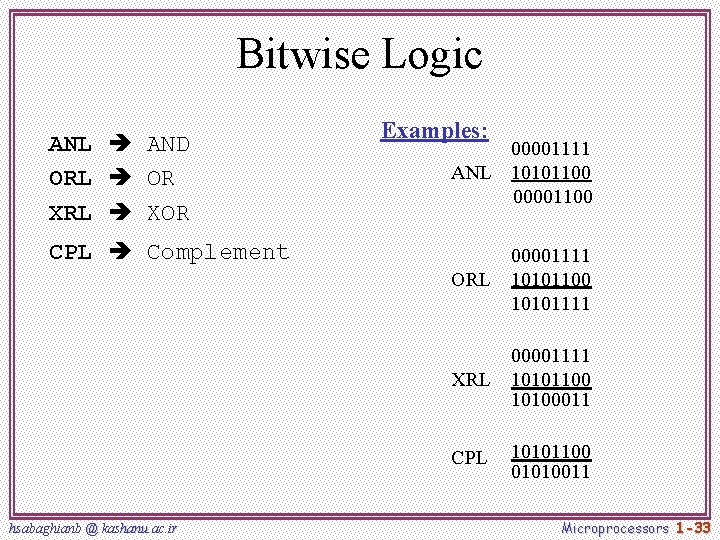

Bitwise Logic ANL AND ORL OR XRL XOR Examples: 00001111 ANL 10101100 00001100 CPL Complement hsabaghianb @ kashanu. ac. ir ORL 00001111 10101100 10101111 XRL 00001111 10101100 10100011 CPL 10101100 01010011 Microprocessors 1 -33

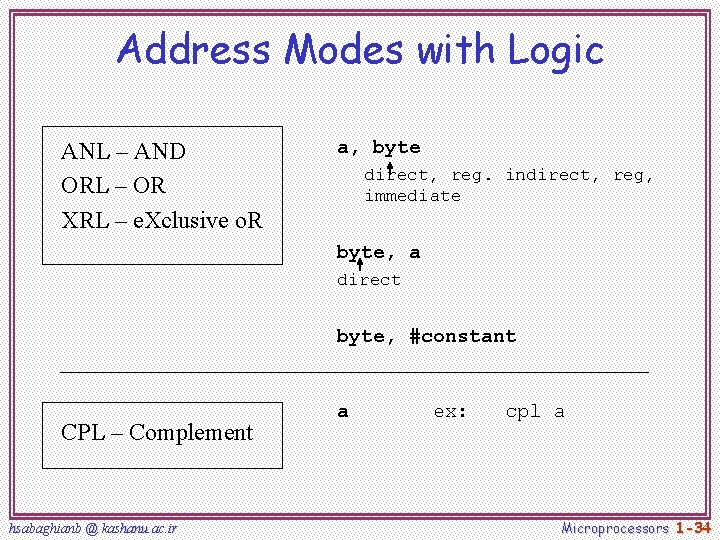

Address Modes with Logic ANL – AND ORL – OR XRL – e. Xclusive o. R a, byte direct, reg. indirect, reg, immediate byte, a direct byte, #constant CPL – Complement hsabaghianb @ kashanu. ac. ir a ex: cpl a Microprocessors 1 -34

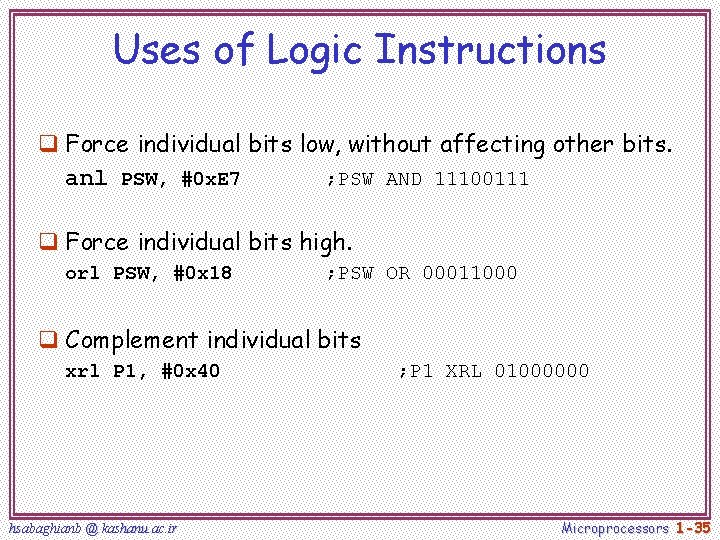

Uses of Logic Instructions q Force individual bits low, without affecting other bits. anl PSW, #0 x. E 7 ; PSW AND 11100111 q Force individual bits high. orl PSW, #0 x 18 ; PSW OR 00011000 q Complement individual bits xrl P 1, #0 x 40 hsabaghianb @ kashanu. ac. ir ; P 1 XRL 01000000 Microprocessors 1 -35

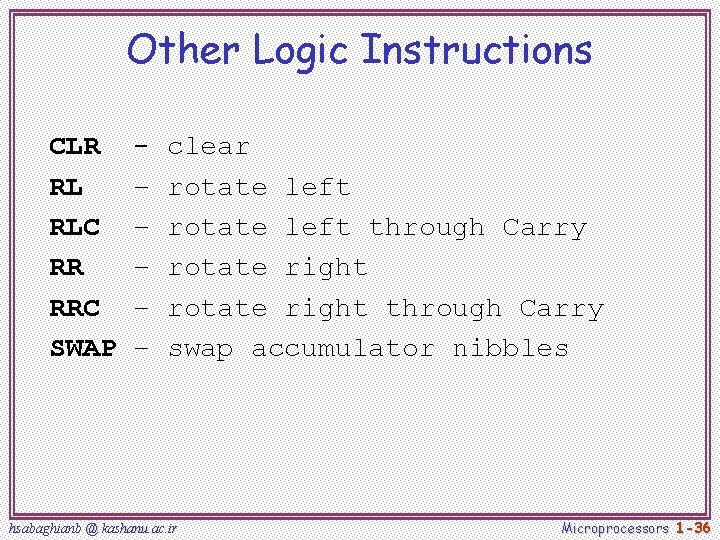

Other Logic Instructions CLR RL RLC RR RRC SWAP – – – clear rotate left through Carry rotate right through Carry swap accumulator nibbles hsabaghianb @ kashanu. ac. ir Microprocessors 1 -36

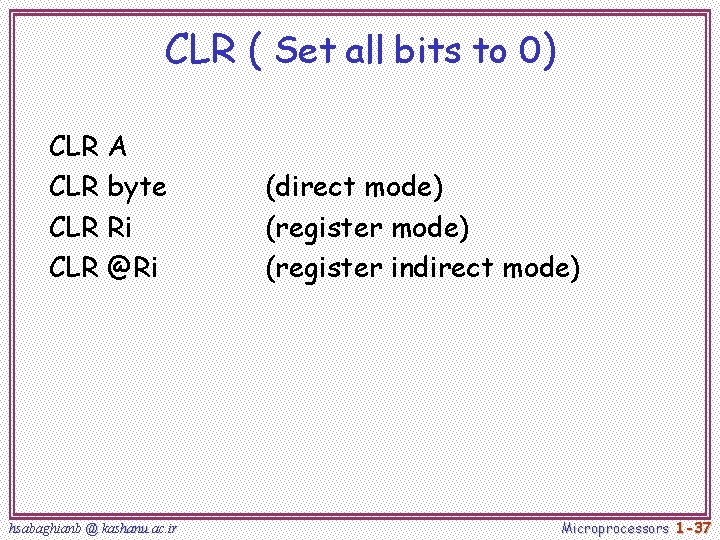

CLR ( Set all bits to 0) CLR A CLR byte CLR Ri CLR @Ri hsabaghianb @ kashanu. ac. ir (direct mode) (register indirect mode) Microprocessors 1 -37

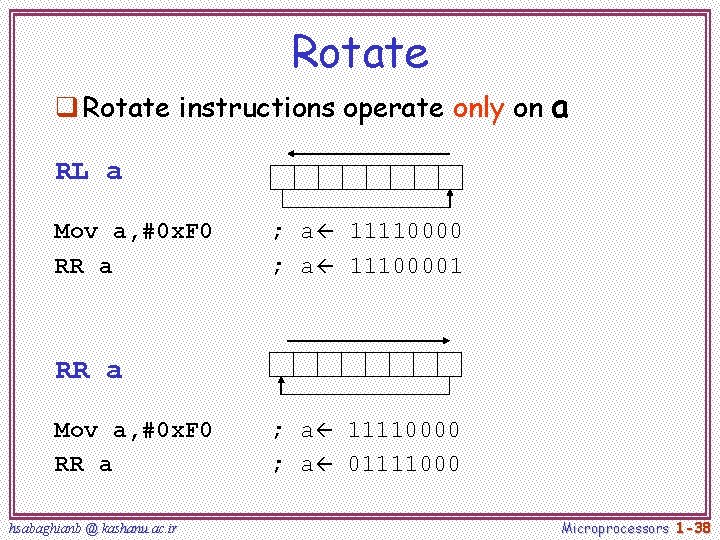

Rotate q Rotate instructions operate only on a RL a Mov a, #0 x. F 0 RR a ; a 11110000 ; a 11100001 RR a Mov a, #0 x. F 0 RR a hsabaghianb @ kashanu. ac. ir ; a 11110000 ; a 01111000 Microprocessors 1 -38

Rotate through Carry RRC a C mov a, #0 A 9 h add a, #14 h ; a A 9 ; a BD (10111101), C 0 rrc a ; a 01011110, C 1 RLC a C mov a, #3 ch setb c ; a 3 ch(00111100) ; c 1 rlc a ; a 01111001, C 1 hsabaghianb @ kashanu. ac. ir Microprocessors 1 -39

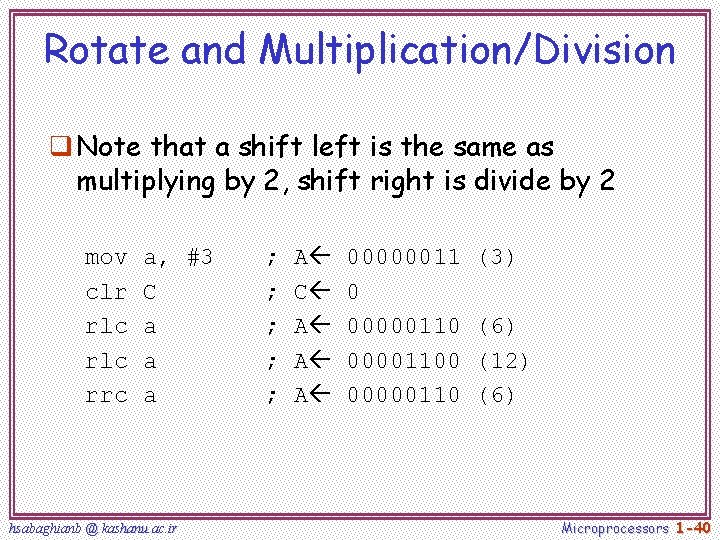

Rotate and Multiplication/Division q Note that a shift left is the same as multiplying by 2, shift right is divide by 2 mov clr rlc rrc a, #3 C a a a hsabaghianb @ kashanu. ac. ir ; ; ; A C A A A 00000011 0 000001100 00000110 (3) (6) (12) (6) Microprocessors 1 -40

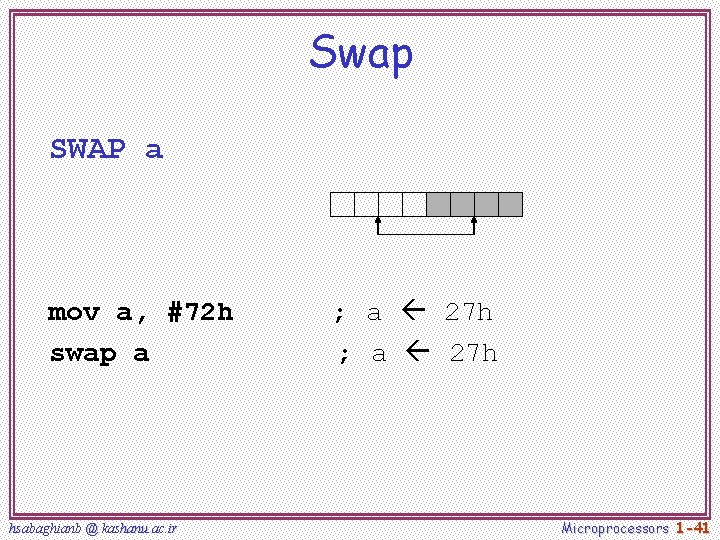

Swap SWAP a mov a, #72 h swap a hsabaghianb @ kashanu. ac. ir ; a 27 h Microprocessors 1 -41

Bit Logic Operations q Some logic operations can be used with single bit operands ANL C, bit ORL C, bit CLR C CLR bit CPL C CPL bit SETB C SETB bit q “bit” can be any of the bit-addressable RAM locations or SFRs. hsabaghianb @ kashanu. ac. ir Microprocessors 1 -42

- Slides: 42