TGC for Muon Trigger of ATLAS DETECTOR s

- Slides: 18

TGC for Muon Trigger of ATLAS DETECTOR s. LHC PROPOSAL for FRONT END ELECTRONICS Upgrading for Phase 1 9/16/2021 Nachman Lupu 1

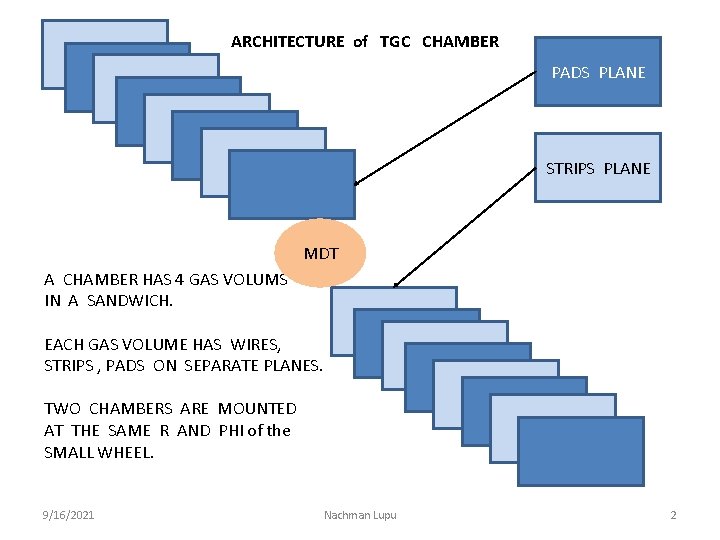

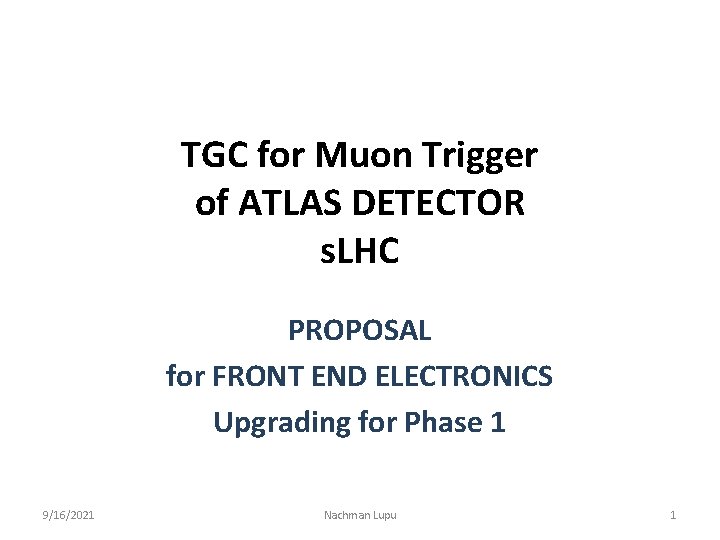

ARCHITECTURE of TGC CHAMBER PADS PLANE STRIPS PLANE MDT A CHAMBER HAS 4 GAS VOLUMS IN A SANDWICH. EACH GAS VOLUME HAS WIRES, STRIPS , PADS ON SEPARATE PLANES. TWO CHAMBERS ARE MOUNTED AT THE SAME R AND PHI of the SMALL WHEEL. 9/16/2021 Nachman Lupu 2

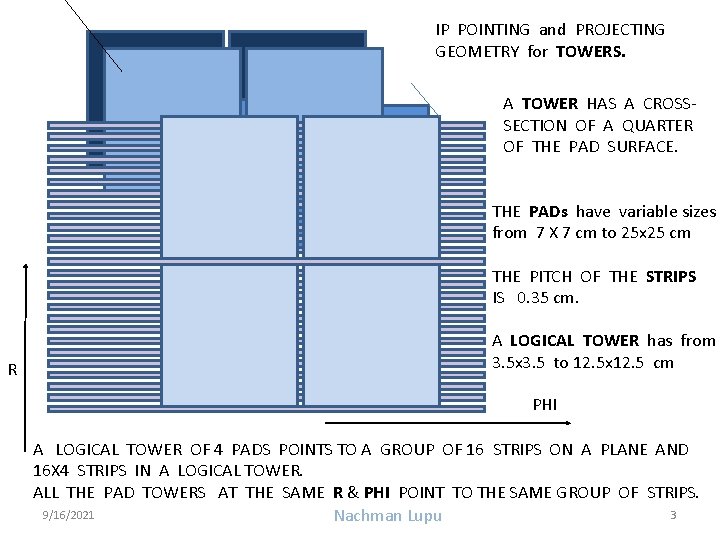

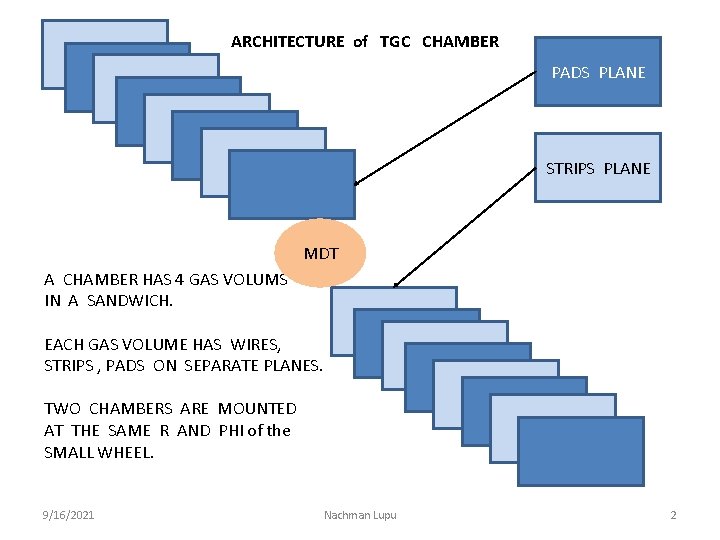

IP POINTING and PROJECTING GEOMETRY for TOWERS. A TOWER HAS A CROSSSECTION OF A QUARTER OF THE PAD SURFACE. THE PADs have variable sizes from 7 X 7 cm to 25 x 25 cm THE PITCH OF THE STRIPS IS 0. 35 cm. R A LOGICAL TOWER has from 3. 5 x 3. 5 to 12. 5 x 12. 5 cm PHI A LOGICAL TOWER OF 4 PADS POINTS TO A GROUP OF 16 STRIPS ON A PLANE AND 16 X 4 STRIPS IN A LOGICAL TOWER. ALL THE PAD TOWERS AT THE SAME R & PHI POINT TO THE SAME GROUP OF STRIPS. 9/16/2021 3 Nachman Lupu

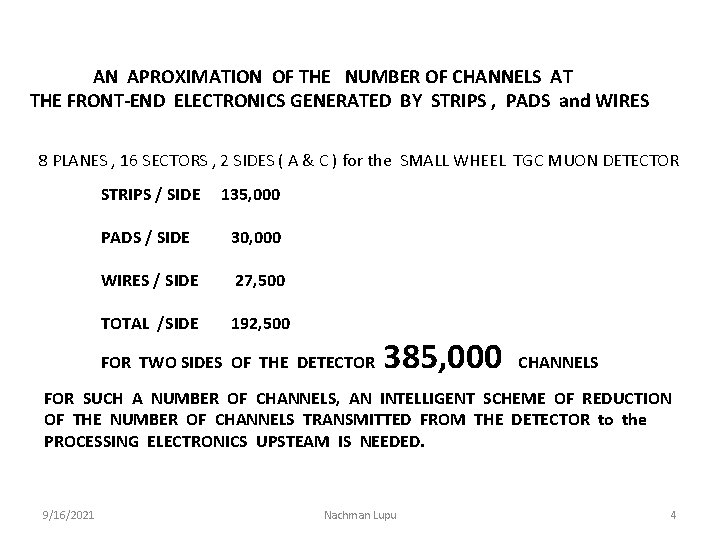

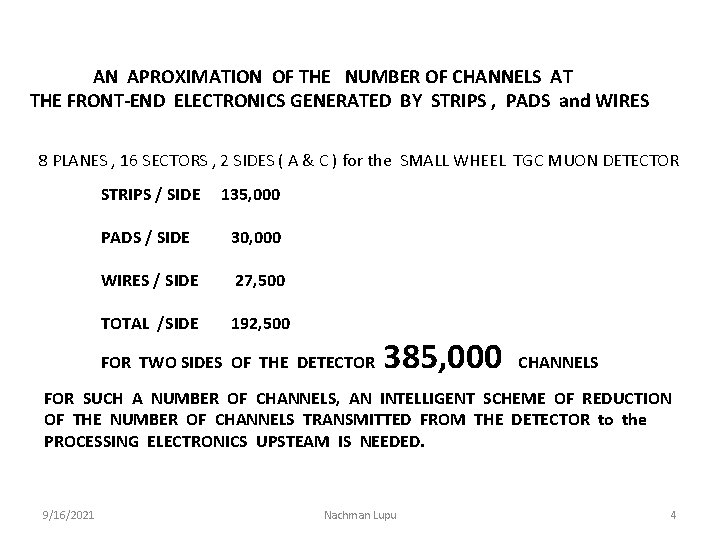

AN APROXIMATION OF THE NUMBER OF CHANNELS AT THE FRONT-END ELECTRONICS GENERATED BY STRIPS , PADS and WIRES 8 PLANES , 16 SECTORS , 2 SIDES ( A & C ) for the SMALL WHEEL TGC MUON DETECTOR STRIPS / SIDE 135, 000 PADS / SIDE 30, 000 WIRES / SIDE 27, 500 TOTAL /SIDE 192, 500 FOR TWO SIDES OF THE DETECTOR 385, 000 CHANNELS FOR SUCH A NUMBER OF CHANNELS, AN INTELLIGENT SCHEME OF REDUCTION OF THE NUMBER OF CHANNELS TRANSMITTED FROM THE DETECTOR to the PROCESSING ELECTRONICS UPSTEAM IS NEEDED. 9/16/2021 Nachman Lupu 4

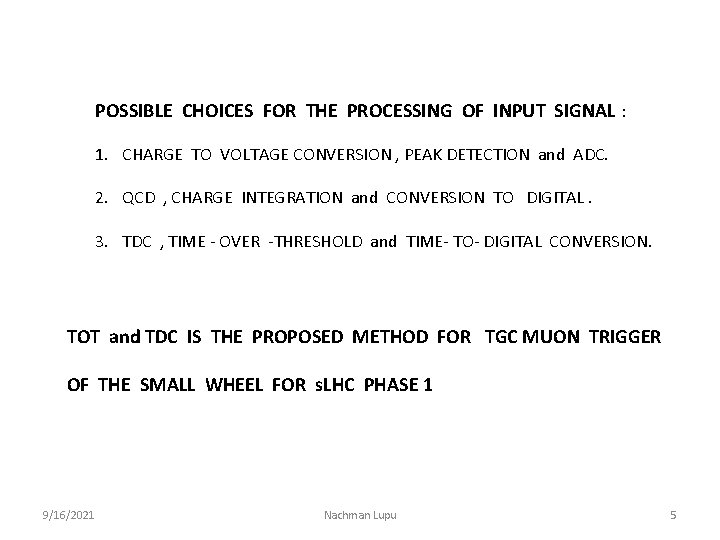

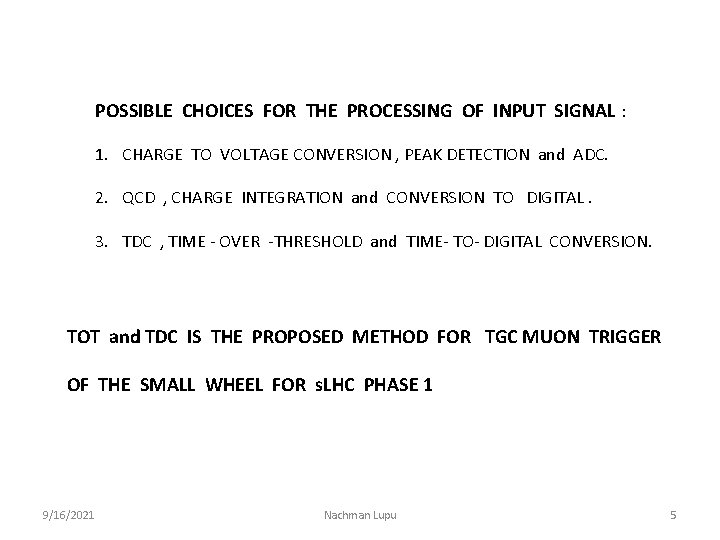

POSSIBLE CHOICES FOR THE PROCESSING OF INPUT SIGNAL : 1. CHARGE TO VOLTAGE CONVERSION , PEAK DETECTION and ADC. 2. QCD , CHARGE INTEGRATION and CONVERSION TO DIGITAL. 3. TDC , TIME - OVER -THRESHOLD and TIME- TO- DIGITAL CONVERSION. TOT and TDC IS THE PROPOSED METHOD FOR TGC MUON TRIGGER OF THE SMALL WHEEL FOR s. LHC PHASE 1 9/16/2021 Nachman Lupu 5

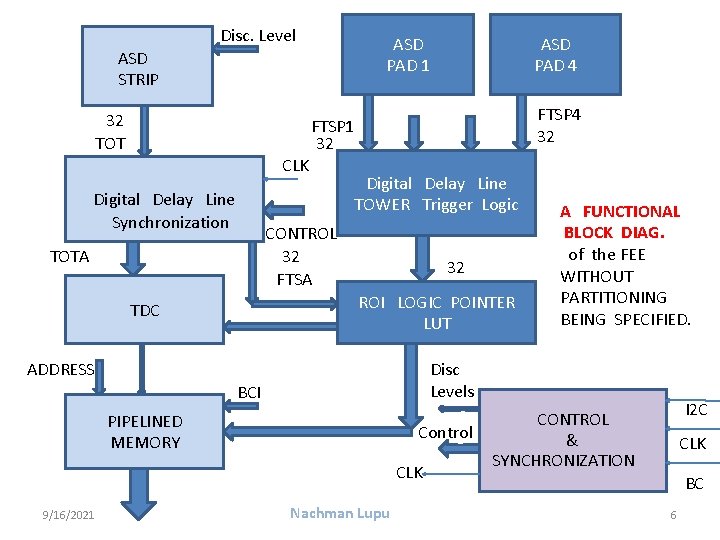

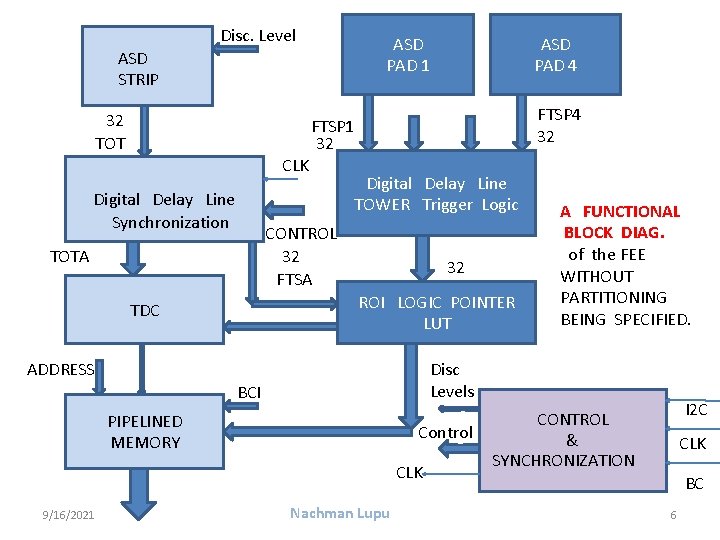

Disc. Level ASD PAD 1 ASD STRIP 32 TOT FTSP 4 32 FTSP 1 32 CLK Digital Delay Line Synchronization Digital Delay Line TOWER Trigger Logic CONTROL 32 FTSA TOTA 32 ROI LOGIC POINTER LUT TDC ADDRESS A FUNCTIONAL BLOCK DIAG. of the FEE WITHOUT PARTITIONING BEING SPECIFIED. Disc Levels C CONTROL Control O & NT SYNCHRONIZATION CLK R BCI PIPELINED MEMORY 9/16/2021 ASD PAD 4 Nachman Lupu I 2 C CLK BC 6

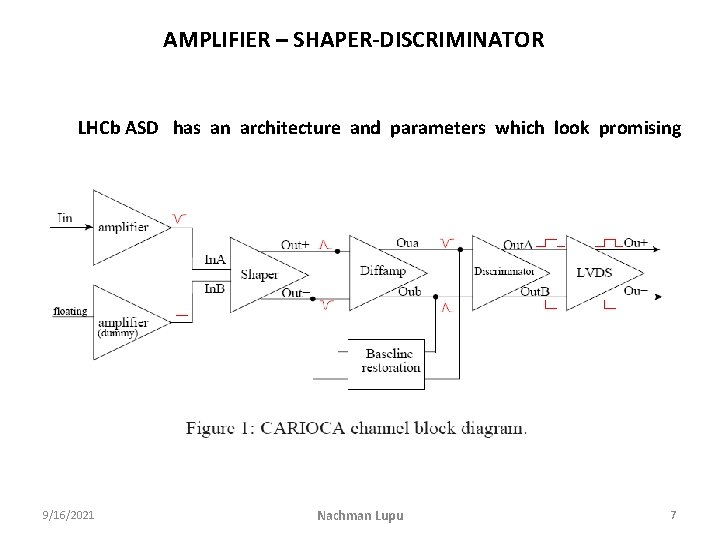

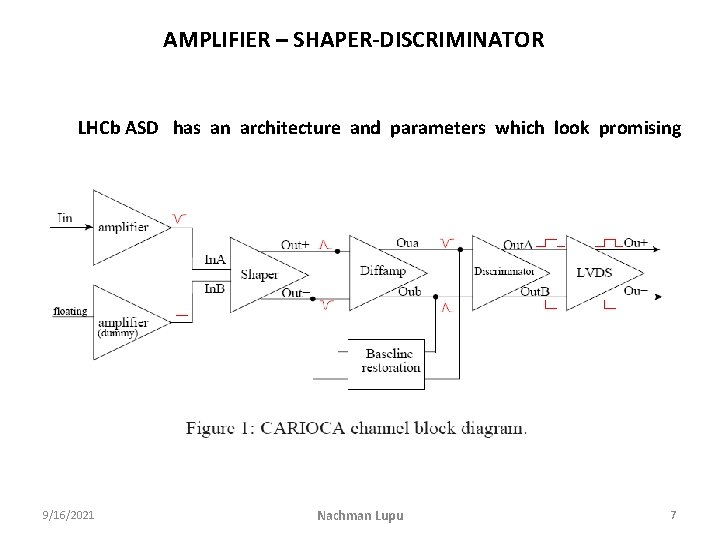

AMPLIFIER – SHAPER-DISCRIMINATOR LHCb ASD has an architecture and parameters which look promising 9/16/2021 Nachman Lupu 7

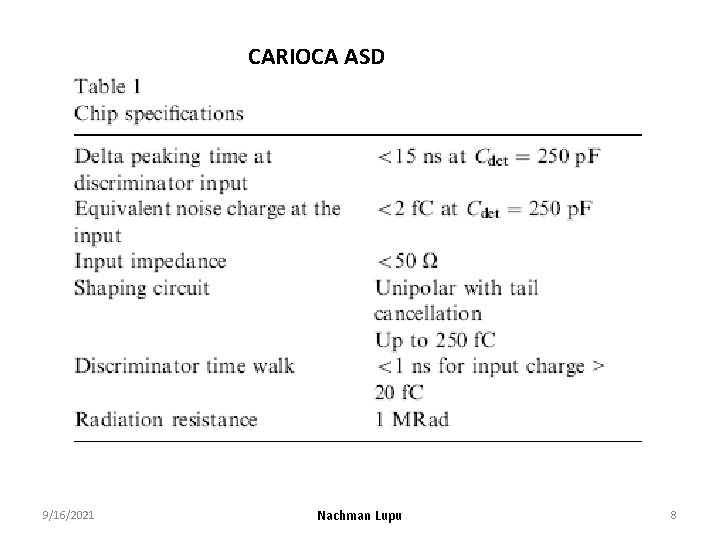

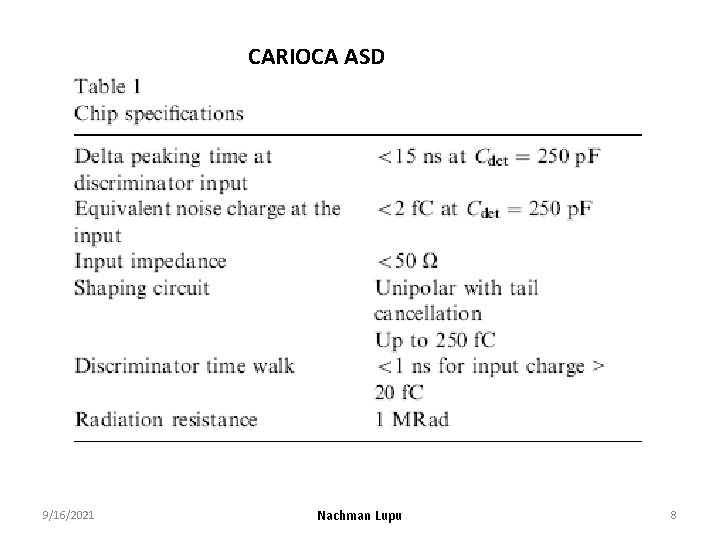

CARIOCA ASD 9/16/2021 Nachman Lupu 8

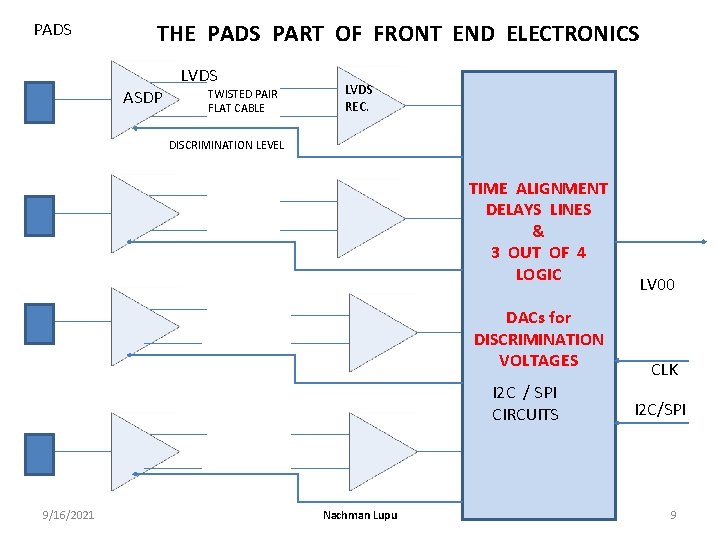

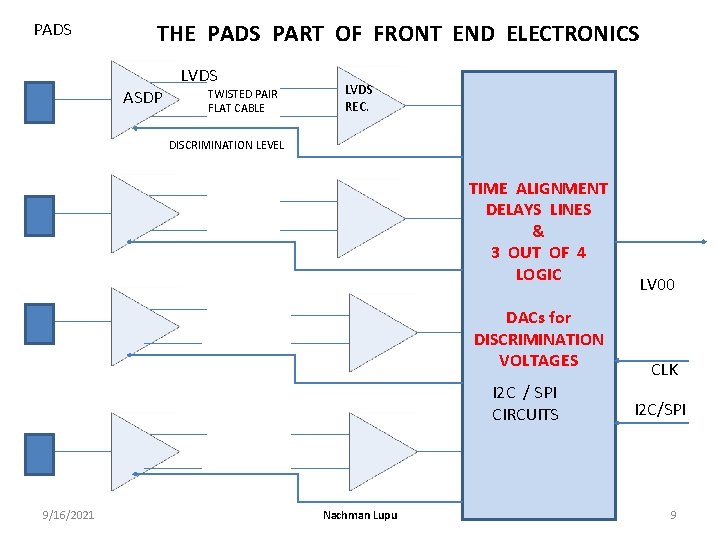

PADS THE PADS PART OF FRONT END ELECTRONICS LVDS ASDP TWISTED PAIR FLAT CABLE LVDS REC. DISCRIMINATION LEVEL TIME ALIGNMENT DELAYS LINES & 3 OUT OF 4 LOGIC DACs for DISCRIMINATION VOLTAGES I 2 C / SPI CIRCUITS 9/16/2021 Nachman Lupu LV 00 CLK I 2 C/SPI 9

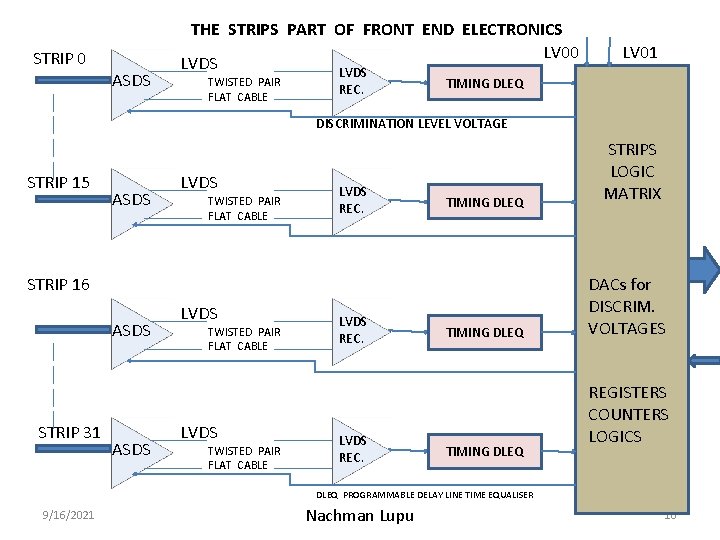

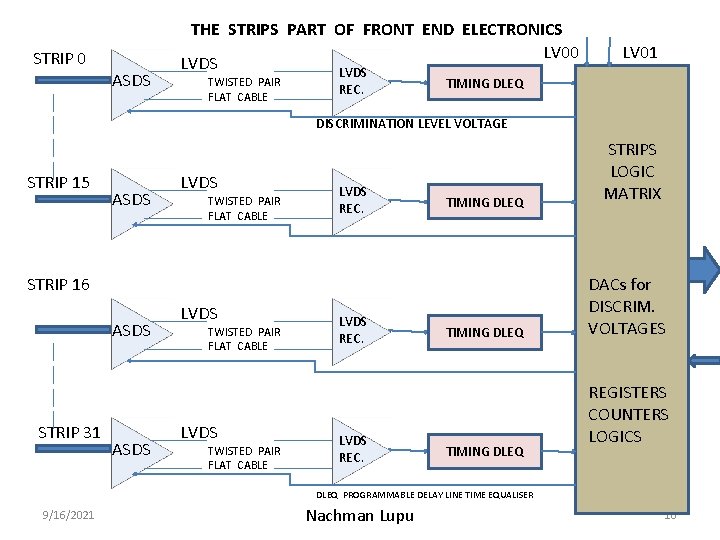

STRIP 0 ASDS THE STRIPS PART OF FRONT END ELECTRONICS LV 00 LVDS TWISTED PAIR FLAT CABLE REC. LV 01 TIMING DLEQ DISCRIMINATION LEVEL VOLTAGE STRIP 15 ASDS LVDS TWISTED PAIR FLAT CABLE LVDS REC. TIMING DLEQ STRIP 16 ASDS STRIP 31 ASDS LVDS TWISTED PAIR FLAT CABLE LVDS REC. TIMING DLEQ STRIPS LOGIC MATRIX DACs for DISCRIM. VOLTAGES REGISTERS COUNTERS LOGICS DLEQ PROGRAMMABLE DELAY LINE TIME EQUALISER 9/16/2021 Nachman Lupu 10

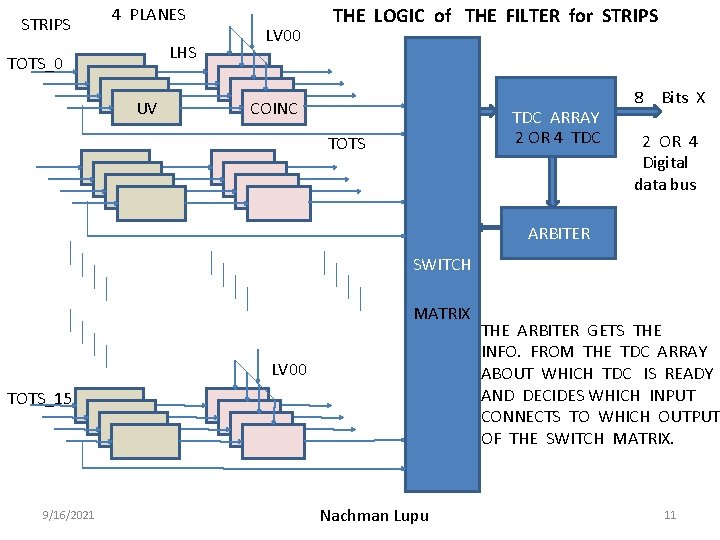

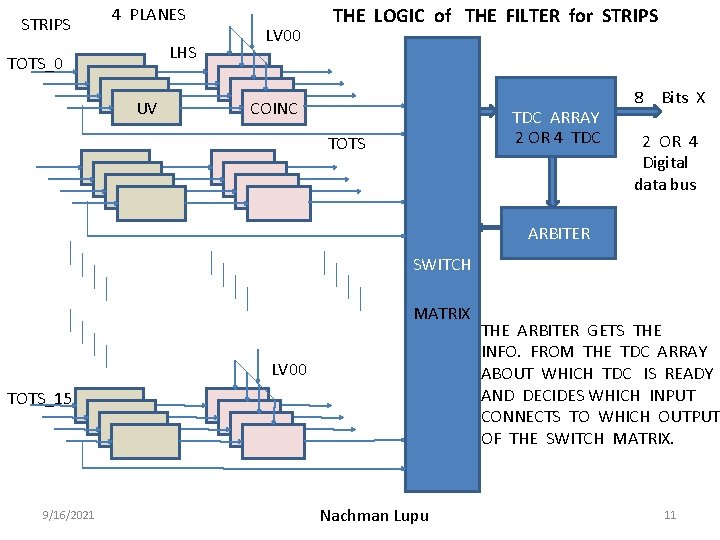

STRIPS 4 PLANES LHS TOTS_0 UV LV 00 THE LOGIC of THE FILTER for STRIPS COINC TDC ARRAY 2 OR 4 TDC TOTS 8 Bits X 2 OR 4 Digital data bus ARBITER SWITCH MATRIX LV 00 TOTS_15 9/16/2021 Nachman Lupu THE ARBITER GETS THE INFO. FROM THE TDC ARRAY ABOUT WHICH TDC IS READY AND DECIDES WHICH INPUT CONNECTS TO WHICH OUTPUT OF THE SWITCH MATRIX. 11

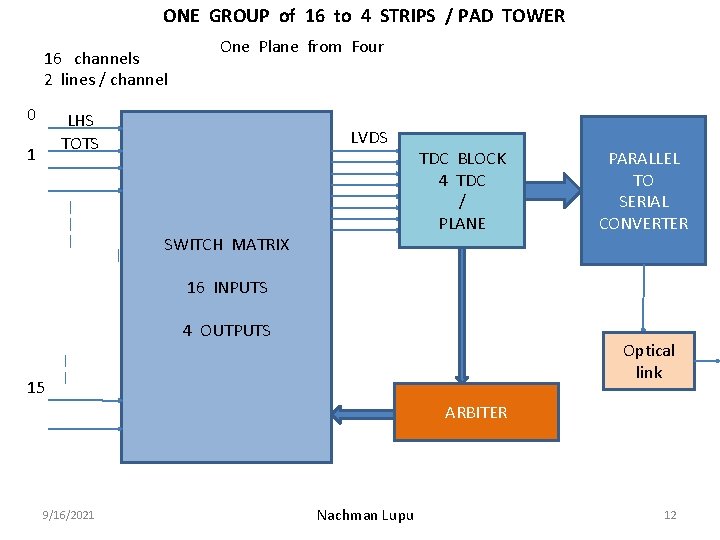

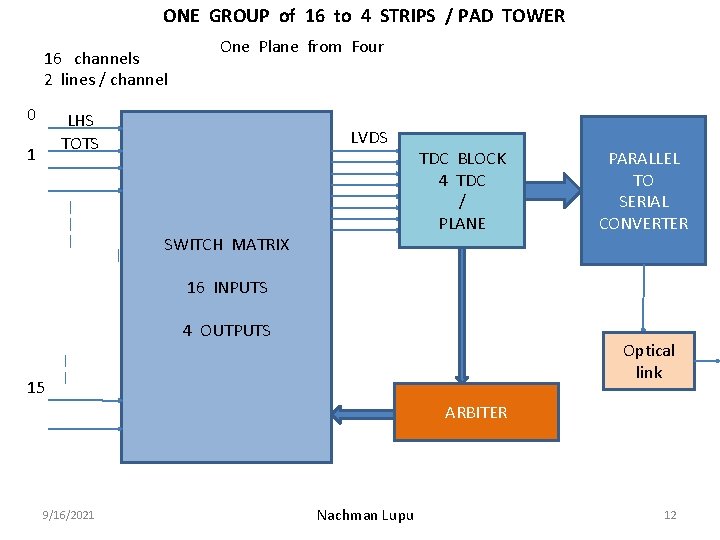

ONE GROUP of 16 to 4 STRIPS / PAD TOWER 16 channels 2 lines / channel 0 One Plane from Four LHS TOTS 1 LVDS SWITCH MATRIX TDC BLOCK 4 TDC / PLANE PARALLEL TO SERIAL CONVERTER 16 INPUTS 4 OUTPUTS Optical link 15 ARBITER 9/16/2021 Nachman Lupu 12

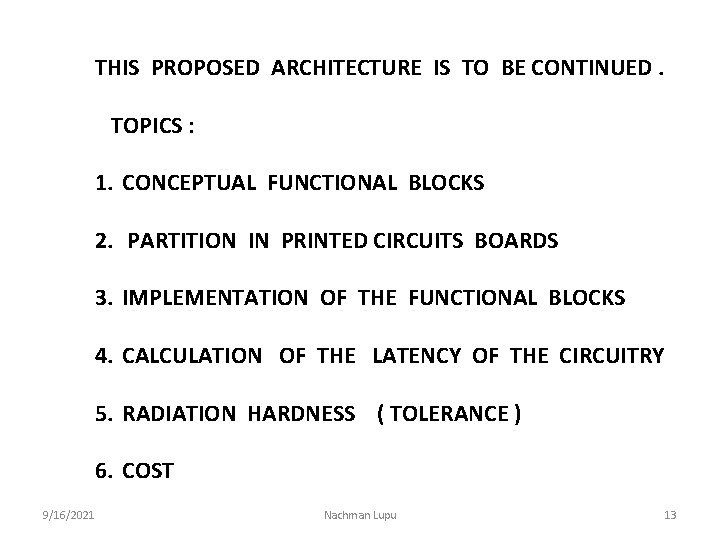

THIS PROPOSED ARCHITECTURE IS TO BE CONTINUED. TOPICS : 1. CONCEPTUAL FUNCTIONAL BLOCKS 2. PARTITION IN PRINTED CIRCUITS BOARDS 3. IMPLEMENTATION OF THE FUNCTIONAL BLOCKS 4. CALCULATION OF THE LATENCY OF THE CIRCUITRY 5. RADIATION HARDNESS ( TOLERANCE ) 6. COST 9/16/2021 Nachman Lupu 13

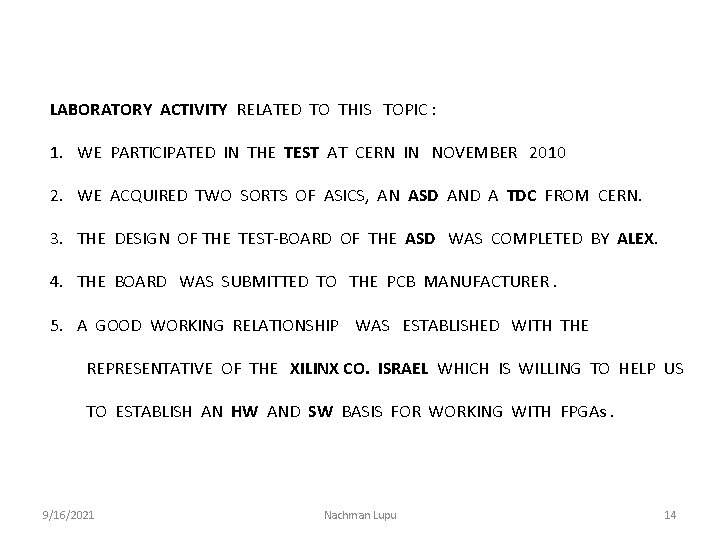

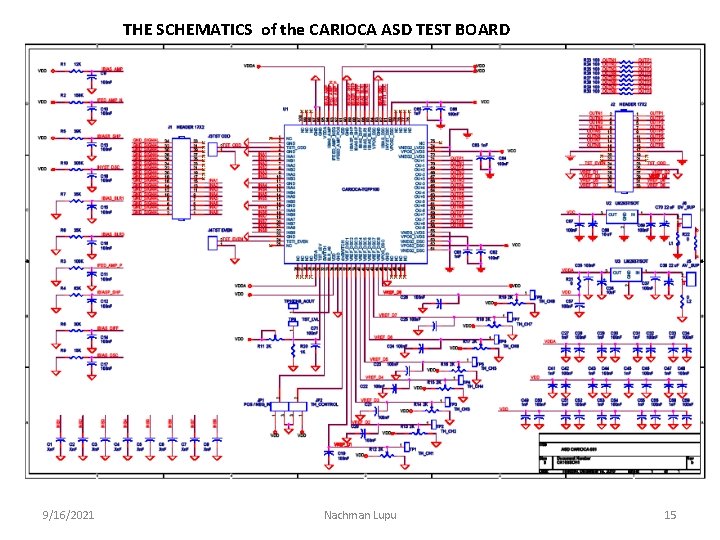

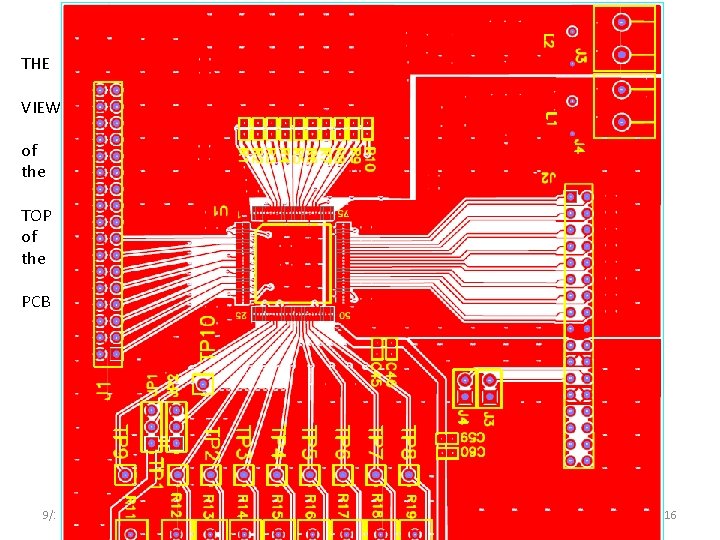

LABORATORY ACTIVITY RELATED TO THIS TOPIC : 1. WE PARTICIPATED IN THE TEST AT CERN IN NOVEMBER 2010 2. WE ACQUIRED TWO SORTS OF ASICS, AN ASD AND A TDC FROM CERN. 3. THE DESIGN OF THE TEST-BOARD OF THE ASD WAS COMPLETED BY ALEX. 4. THE BOARD WAS SUBMITTED TO THE PCB MANUFACTURER. 5. A GOOD WORKING RELATIONSHIP WAS ESTABLISHED WITH THE REPRESENTATIVE OF THE XILINX CO. ISRAEL WHICH IS WILLING TO HELP US TO ESTABLISH AN HW AND SW BASIS FOR WORKING WITH FPGAs. 9/16/2021 Nachman Lupu 14

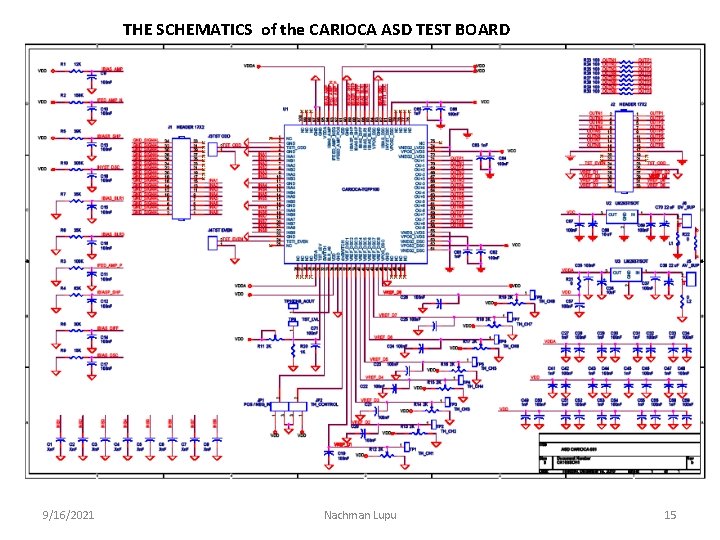

THE SCHEMATICS of the CARIOCA ASD TEST BOARD 9/16/2021 Nachman Lupu 15

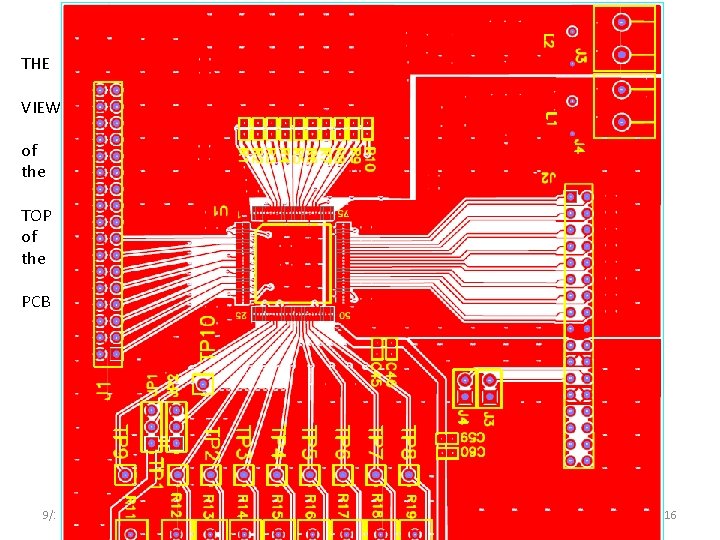

THE VIEW of the TOP of the PCB 9/16/2021 Nachman Lupu 16

WORKING PLAN for 2011 • The Front –End- Electronics for TGC is in continuous development. • The target is to have a CONCEPT SYSTEM design by March 2011. • By the end of January to have a working and tested concept for ASD • By the beginning of February to start working on the implementation of the functional modules on a ready -made Test- Board with the FPGA VIRTEX 6 from XILINX CO. IL. • CERN HAS A WG FOR THE USE OF FPGAs IN RADIATION ENVIRONMENT and we will follow its work and results. 9/16/2021 Nachman Lupu 17

THANK YOU FOR YOUR ATTENTION !!! 9/16/2021 Nachman Lupu 18