Testing of integrated circuits and design for testability

Testing of integrated circuits and design for testability J. Christiansen CERN - EP/MIC Jorgen. Christiansen@cern. ch J. Christiansen/CERN

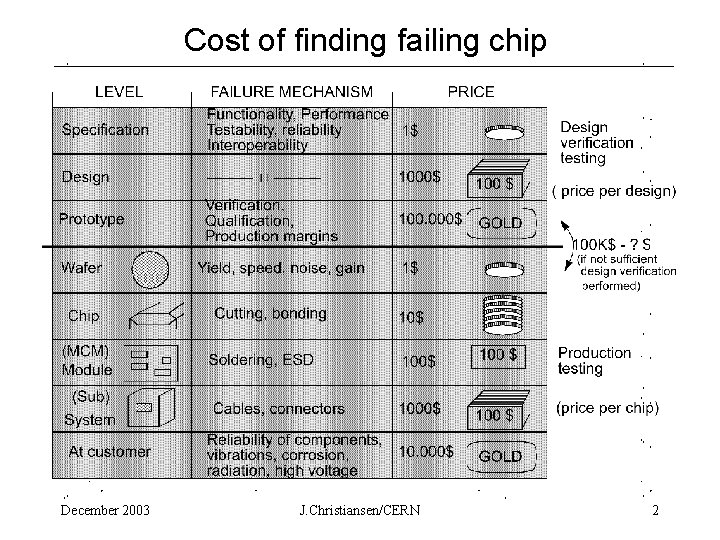

Cost of finding failing chip December 2003 J. Christiansen/CERN 2

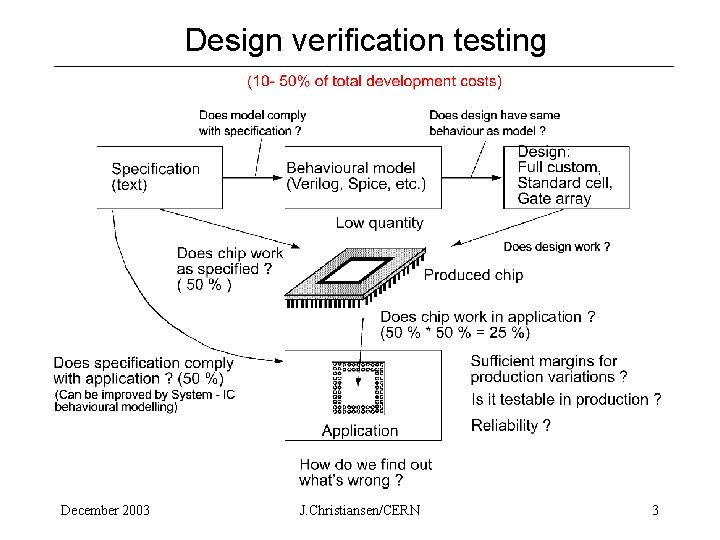

Design verification testing December 2003 J. Christiansen/CERN 3

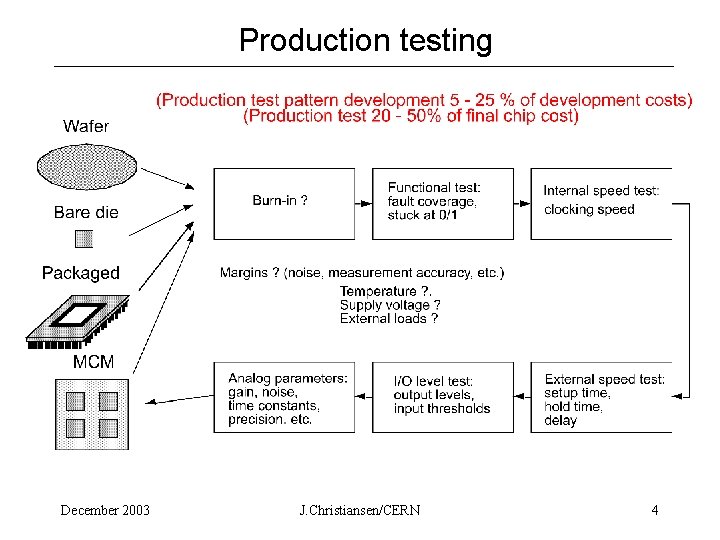

Production testing December 2003 J. Christiansen/CERN 4

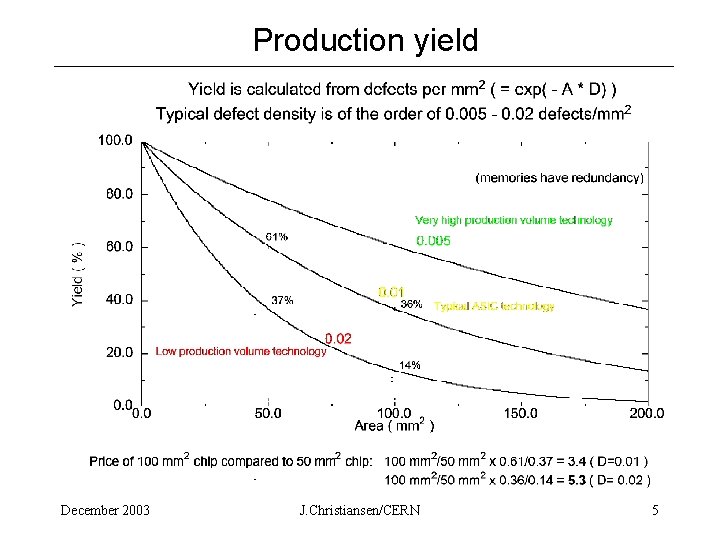

Production yield December 2003 J. Christiansen/CERN 5

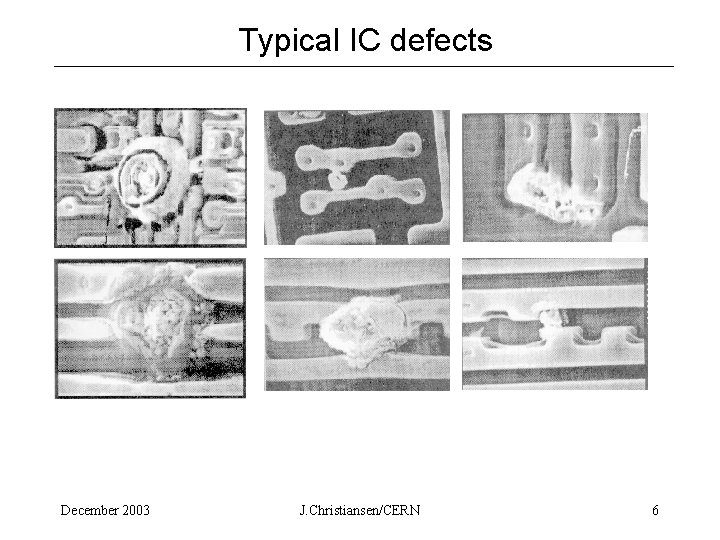

Typical IC defects December 2003 J. Christiansen/CERN 6

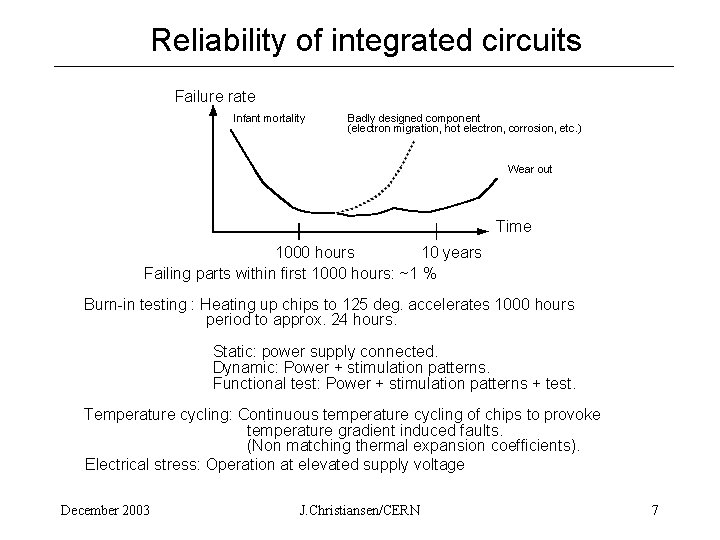

Reliability of integrated circuits Failure rate Infant mortality Badly designed component (electron migration, hot electron, corrosion, etc. ) Wear out Time 1000 hours 10 years Failing parts within first 1000 hours: ~1 % Burn-in testing : Heating up chips to 125 deg. accelerates 1000 hours period to approx. 24 hours. Static: power supply connected. Dynamic: Power + stimulation patterns. Functional test: Power + stimulation patterns + test. Temperature cycling: Continuous temperature cycling of chips to provoke temperature gradient induced faults. (Non matching thermal expansion coefficients). Electrical stress: Operation at elevated supply voltage December 2003 J. Christiansen/CERN 7

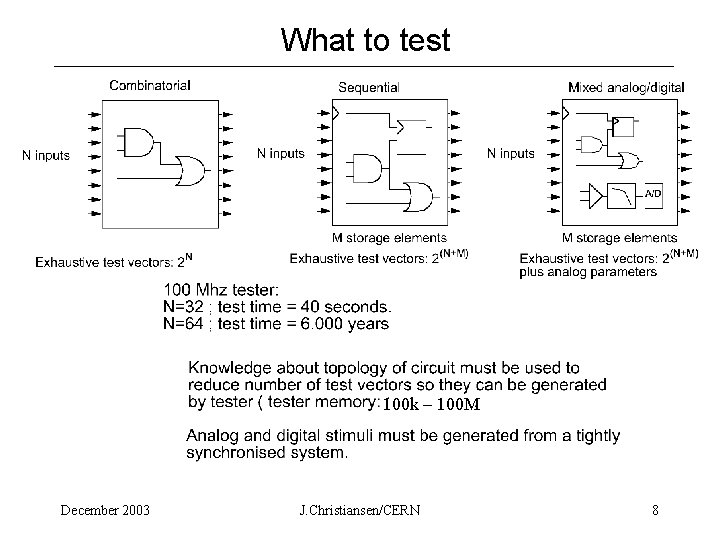

What to test 100 k – 100 M December 2003 J. Christiansen/CERN 8

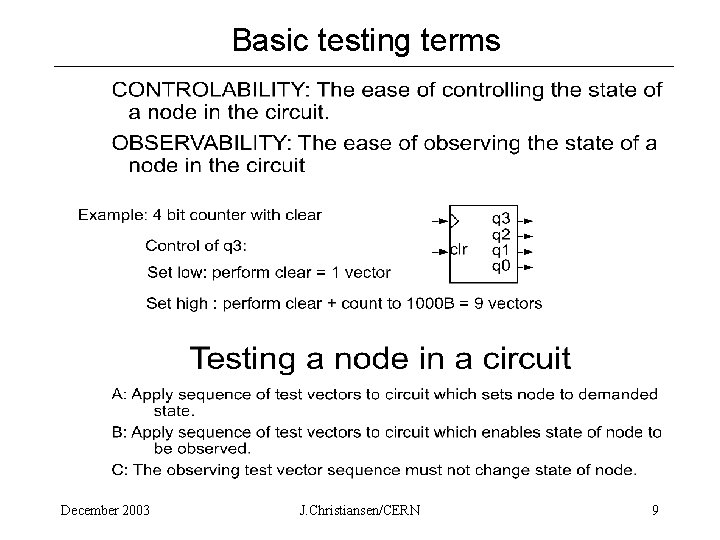

Basic testing terms December 2003 J. Christiansen/CERN 9

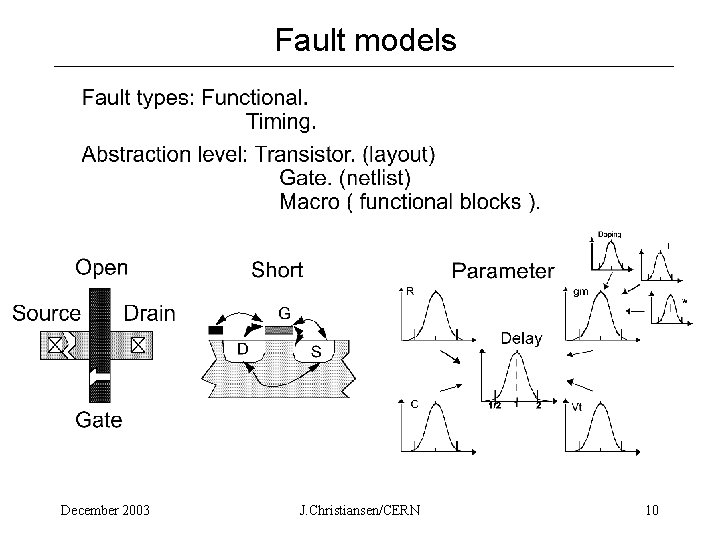

Fault models December 2003 J. Christiansen/CERN 10

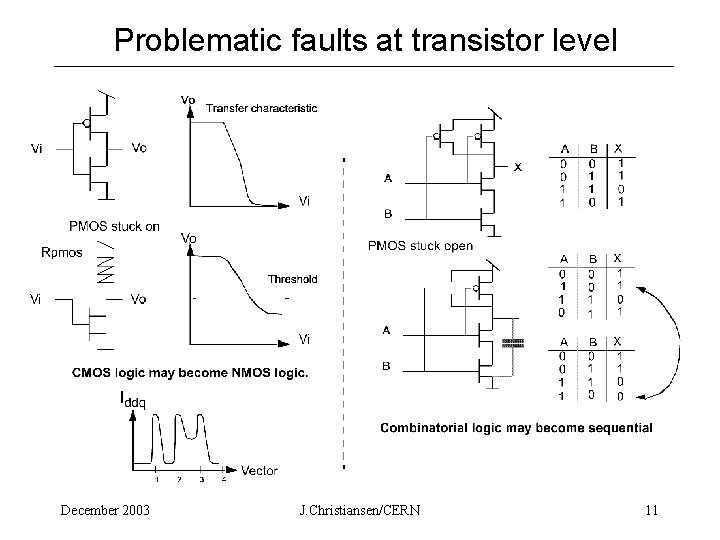

Problematic faults at transistor level December 2003 J. Christiansen/CERN 11

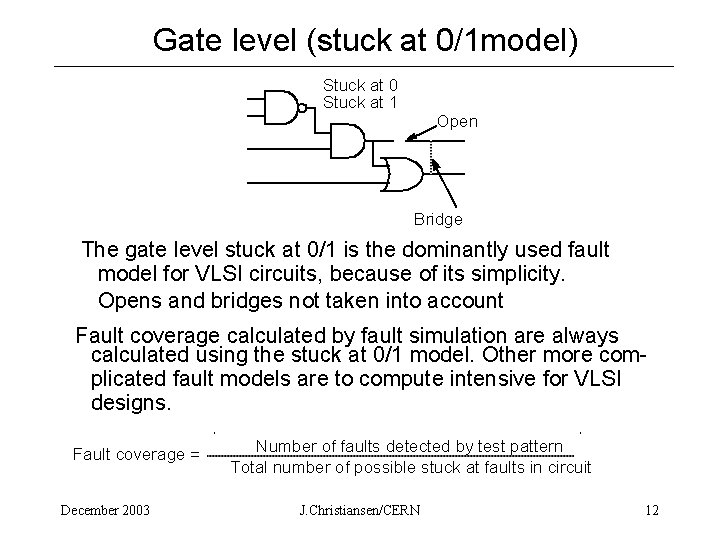

Gate level (stuck at 0/1 model) Stuck at 0 Stuck at 1 Open Bridge The gate level stuck at 0/1 is the dominantly used fault model for VLSI circuits, because of its simplicity. Opens and bridges not taken into account Fault coverage calculated by fault simulation are always calculated using the stuck at 0/1 model. Other more complicated fault models are to compute intensive for VLSI designs. Fault coverage = December 2003 Number of faults detected by test pattern Total number of possible stuck at faults in circuit J. Christiansen/CERN 12

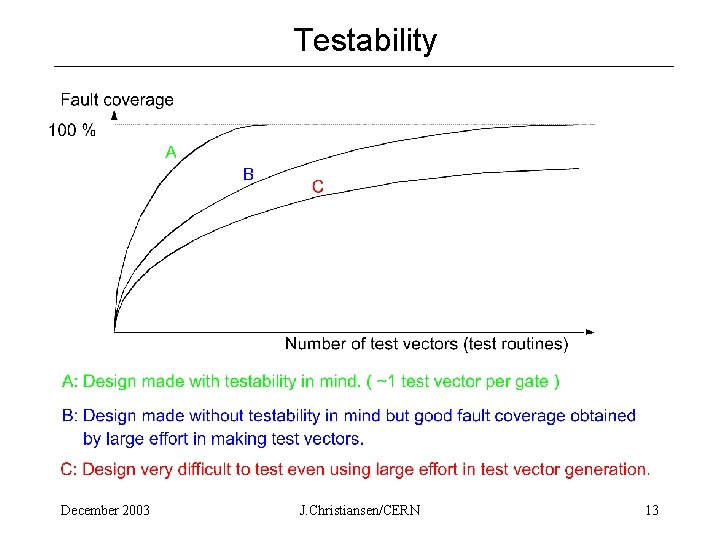

Testability December 2003 J. Christiansen/CERN 13

Generation of test patterns • Test vectors made by test engineer based on functional description and schematics. Proprietary test vector languages used to drive tester. (over the wall) • Test vectors made by design engineer on CAE system. Subset of test patterns may be taken from design verification simulations. • Generated by Automatic Test Pattern Generators ( ATPG). Requires internal scan path • Pseudo random generated test patterns. • Fault simulation calculates fault coverage. December 2003 J. Christiansen/CERN 14

Fault simulation December 2003 J. Christiansen/CERN 15

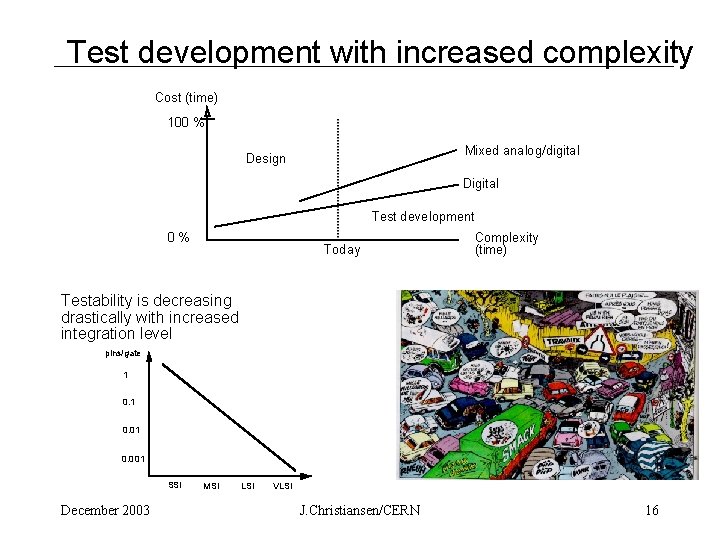

Test development with increased complexity Cost (time) 100 % Mixed analog/digital Design Digital Test development 0% Today Complexity (time) Testability is decreasing drastically with increased integration level pins/gate 1 0. 01 0. 001 SSI December 2003 MSI LSI VLSI J. Christiansen/CERN 16

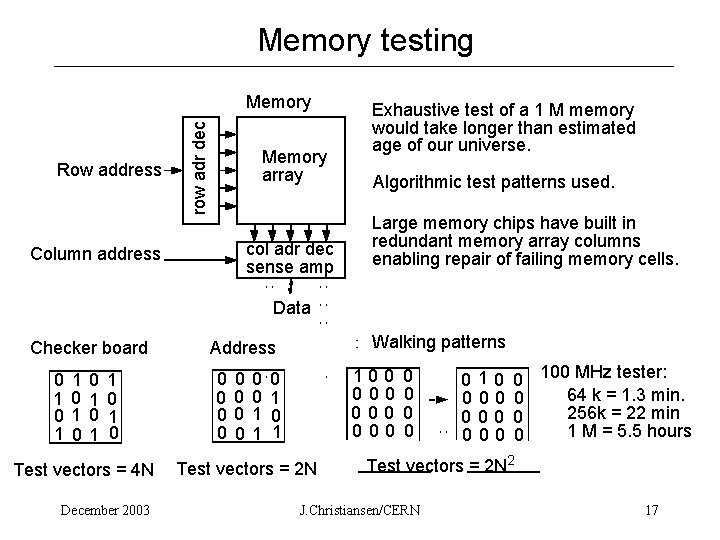

Memory testing Row address row adr dec Memory array col adr dec sense amp Column address Exhaustive test of a 1 M memory would take longer than estimated age of our universe. Algorithmic test patterns used. Large memory chips have built in redundant memory array columns enabling repair of failing memory cells. Data Checker board 0 1 0 1 0 Test vectors = 4 N December 2003 Walking patterns Address 0 0 0 0 0 1 1 100 000 0 1 0 1 Test vectors = 2 N 0 0 0 0 10 00 0 100 MHz tester: 64 k = 1. 3 min. 0 256 k = 22 min 0 1 M = 5. 5 hours 0 Test vectors = 2 N 2 J. Christiansen/CERN 17

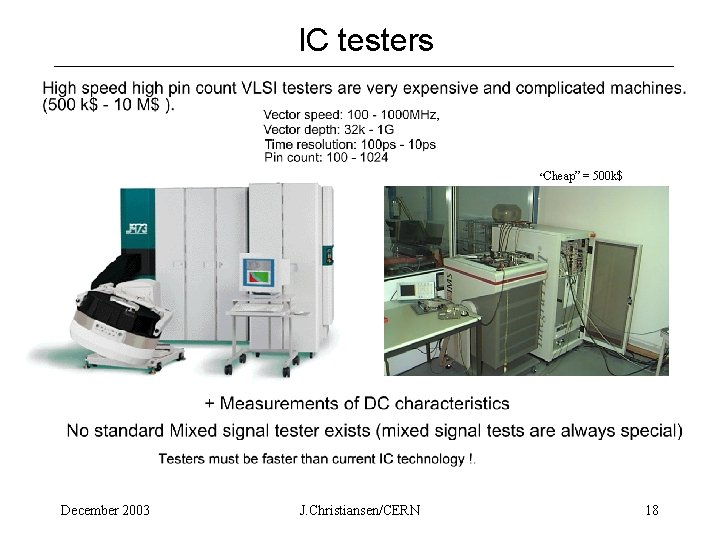

IC testers “Cheap” = December 2003 J. Christiansen/CERN 500 k$ 18

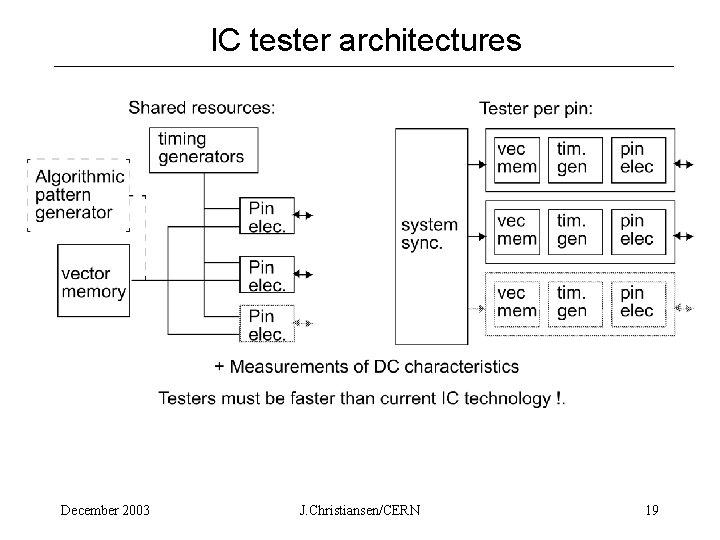

IC tester architectures December 2003 J. Christiansen/CERN 19

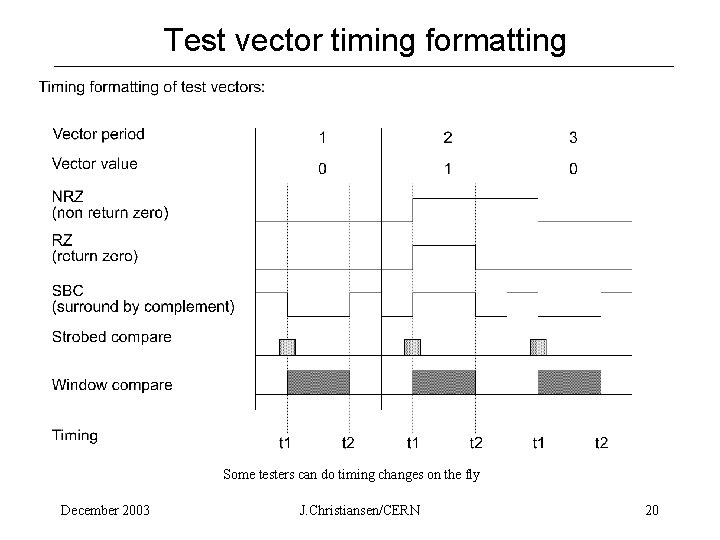

Test vector timing formatting Some testers can do timing changes on the fly December 2003 J. Christiansen/CERN 20

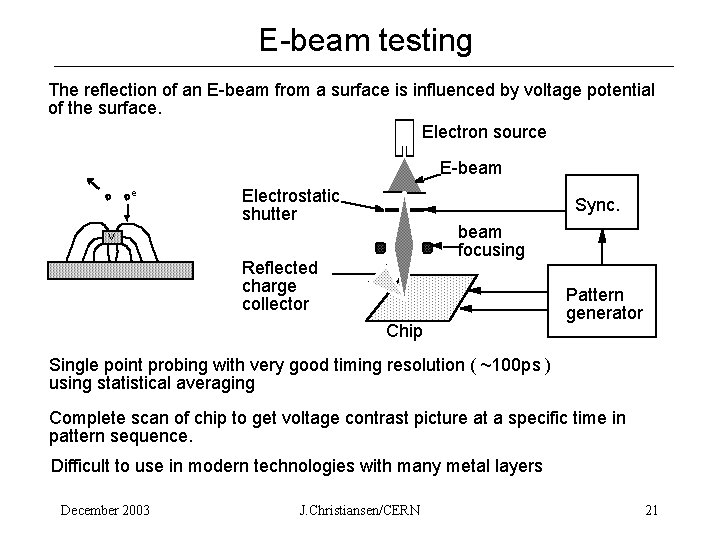

E-beam testing The reflection of an E-beam from a surface is influenced by voltage potential of the surface. Electron source E-beam e Electrostatic shutter Sync. beam focusing V Reflected charge collector Chip Pattern generator Single point probing with very good timing resolution ( ~100 ps ) using statistical averaging Complete scan of chip to get voltage contrast picture at a specific time in pattern sequence. Difficult to use in modern technologies with many metal layers December 2003 J. Christiansen/CERN 21

Scan Path testing December 2003 J. Christiansen/CERN 22

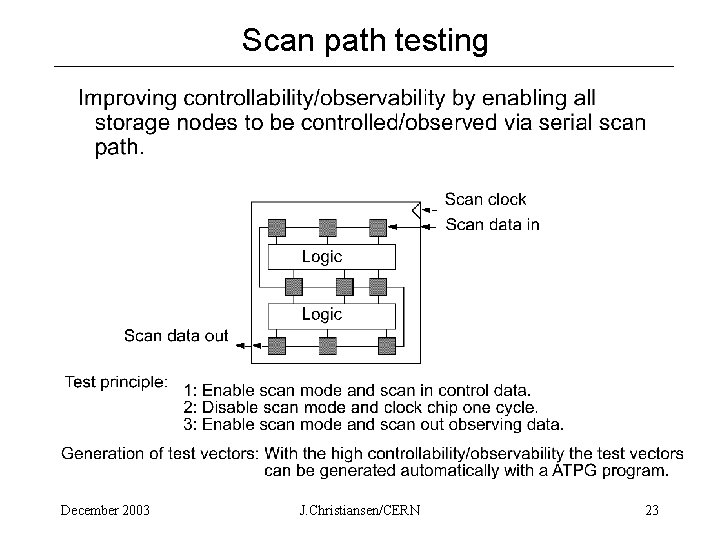

Scan path testing December 2003 J. Christiansen/CERN 23

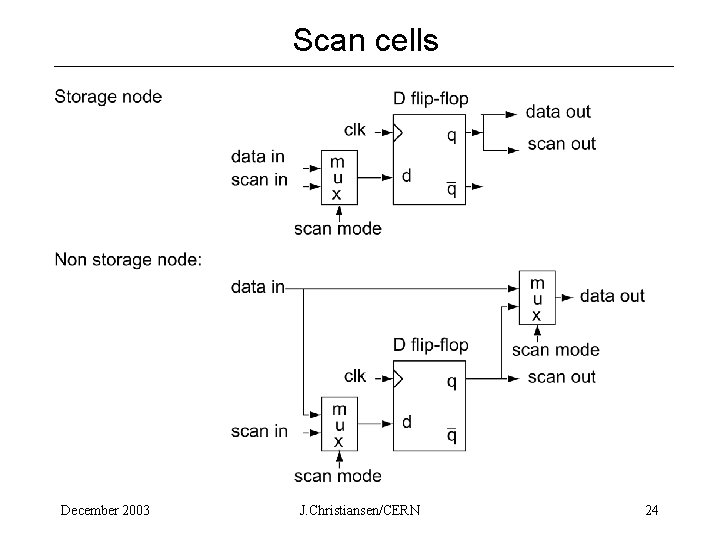

Scan cells December 2003 J. Christiansen/CERN 24

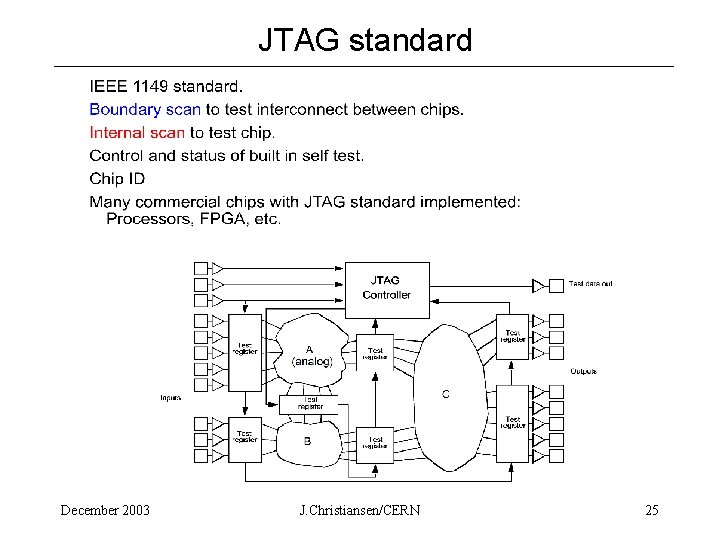

JTAG standard December 2003 J. Christiansen/CERN 25

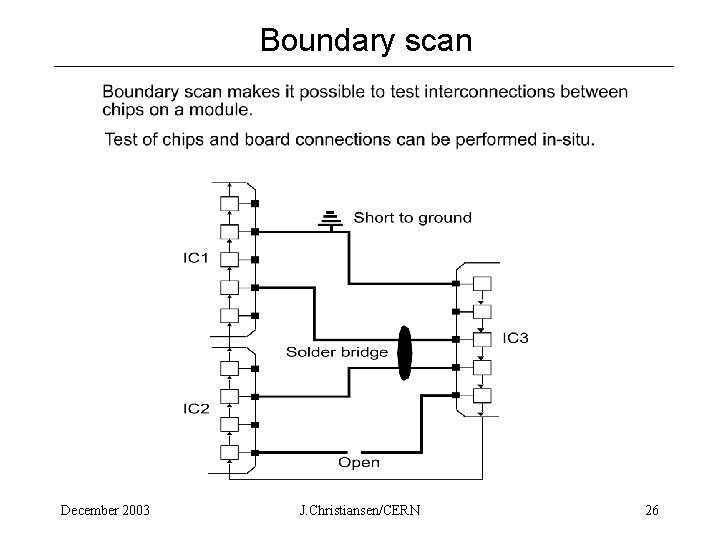

Boundary scan December 2003 J. Christiansen/CERN 26

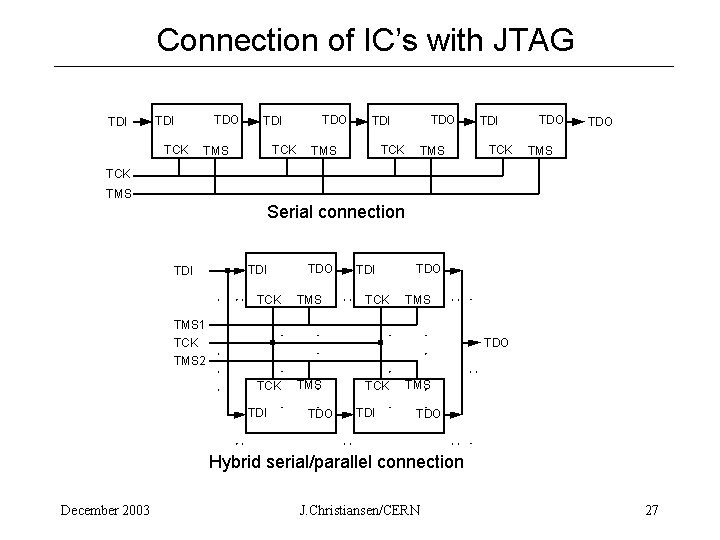

Connection of IC’s with JTAG TDI TDO TDI TCK TMS TDI TCK TDO TMS TCK TMS Serial connection TDI TCK TDO TMS 1 TCK TMS 2 TDO TCK TDI TMS TDO Hybrid serial/parallel connection December 2003 J. Christiansen/CERN 27

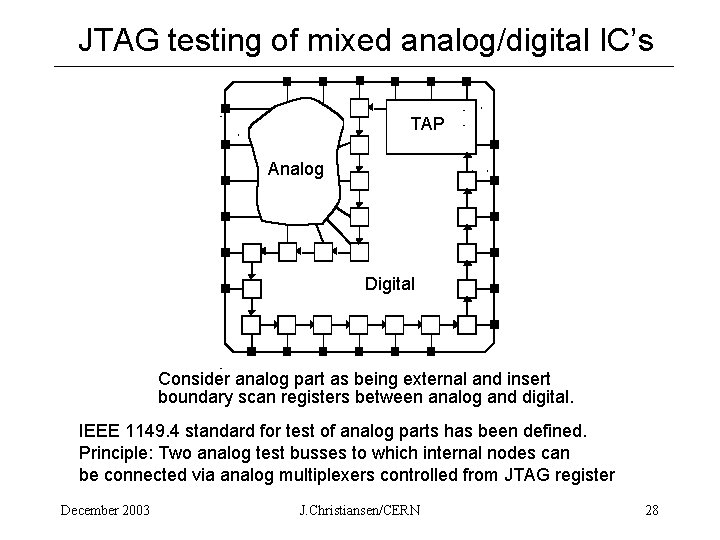

JTAG testing of mixed analog/digital IC’s TAP Analog Digital Consider analog part as being external and insert boundary scan registers between analog and digital. IEEE 1149. 4 standard for test of analog parts has been defined. Principle: Two analog test busses to which internal nodes can be connected via analog multiplexers controlled from JTAG register December 2003 J. Christiansen/CERN 28

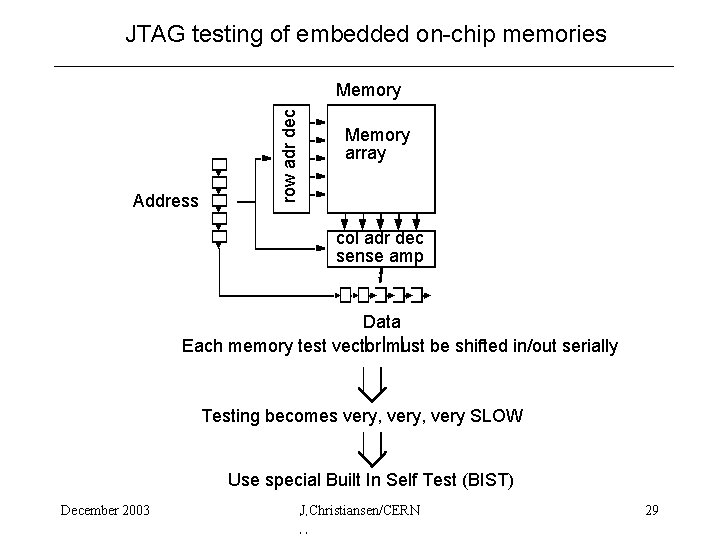

JTAG testing of embedded on-chip memories Address row adr dec Memory array col adr dec sense amp Data Each memory test vector must be shifted in/out serially Testing becomes very, very SLOW Use special Built In Self Test (BIST) December 2003 J. Christiansen/CERN 29

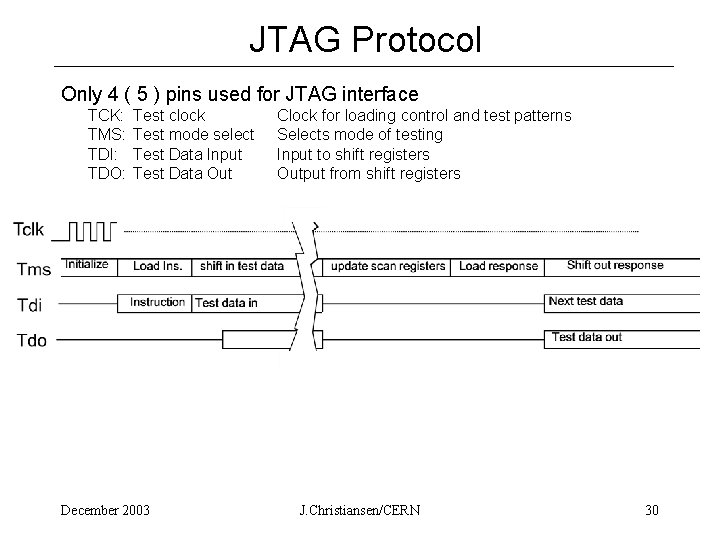

JTAG Protocol Only 4 ( 5 ) pins used for JTAG interface TCK: TMS: TDI: TDO: Test clock Test mode select Test Data Input Test Data Out December 2003 Clock for loading control and test patterns Selects mode of testing Input to shift registers Output from shift registers J. Christiansen/CERN 30

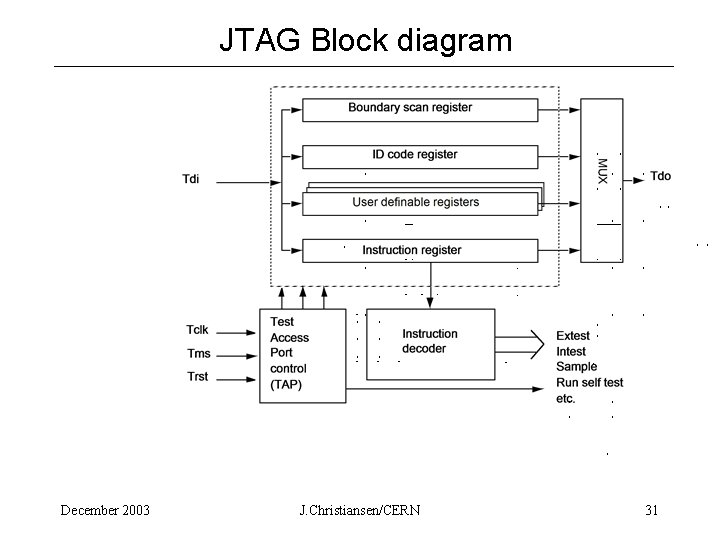

JTAG Block diagram December 2003 J. Christiansen/CERN 31

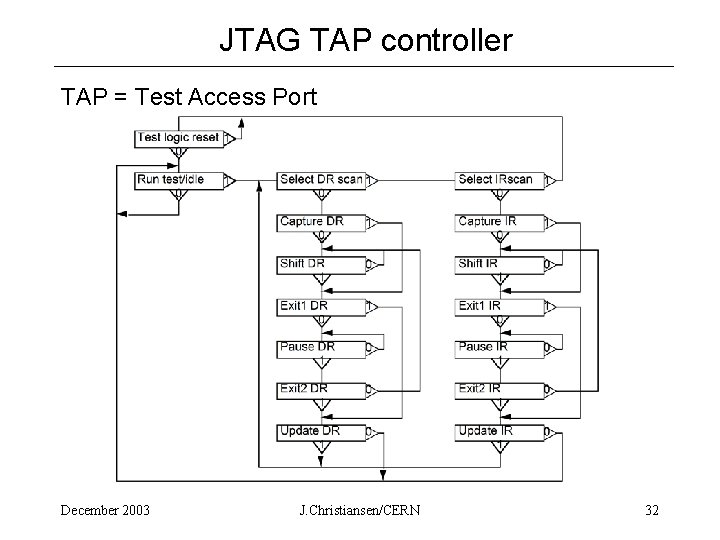

JTAG TAP controller TAP = Test Access Port December 2003 J. Christiansen/CERN 32

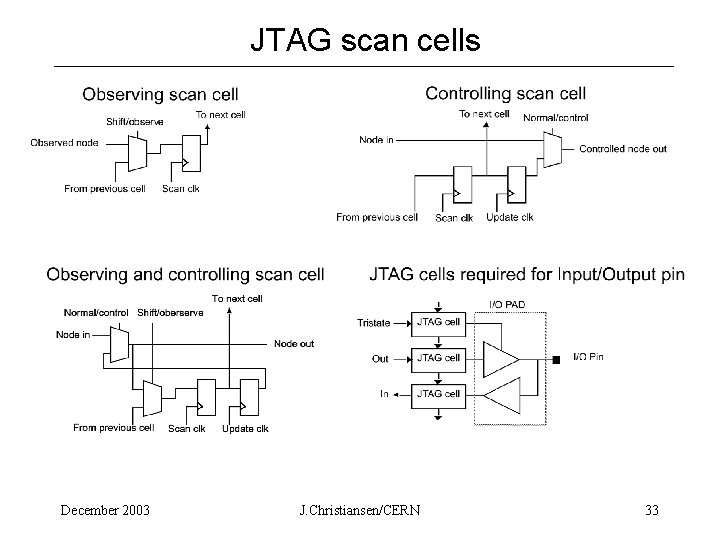

JTAG scan cells December 2003 J. Christiansen/CERN 33

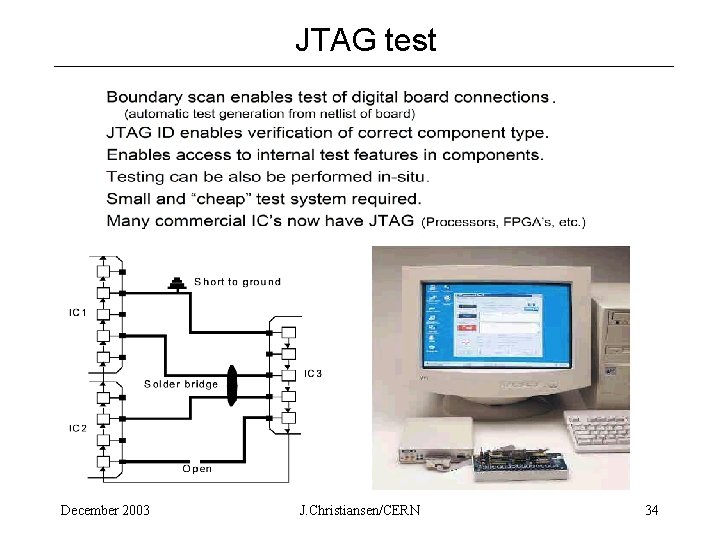

JTAG test December 2003 J. Christiansen/CERN 34

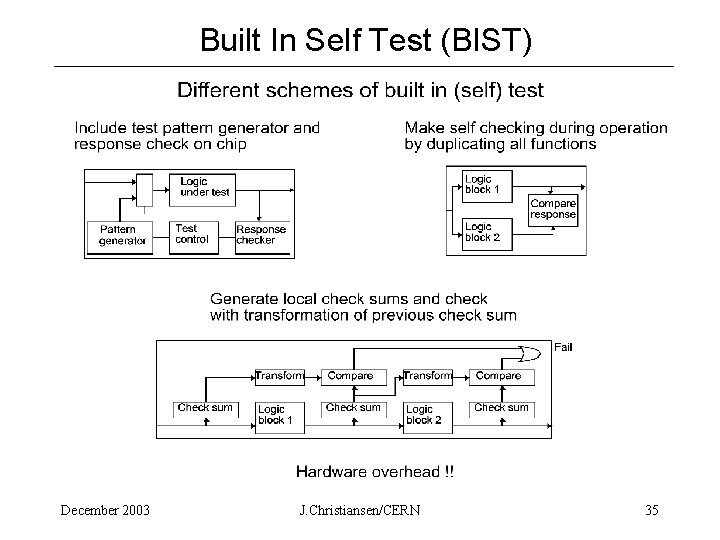

Built In Self Test (BIST) December 2003 J. Christiansen/CERN 35

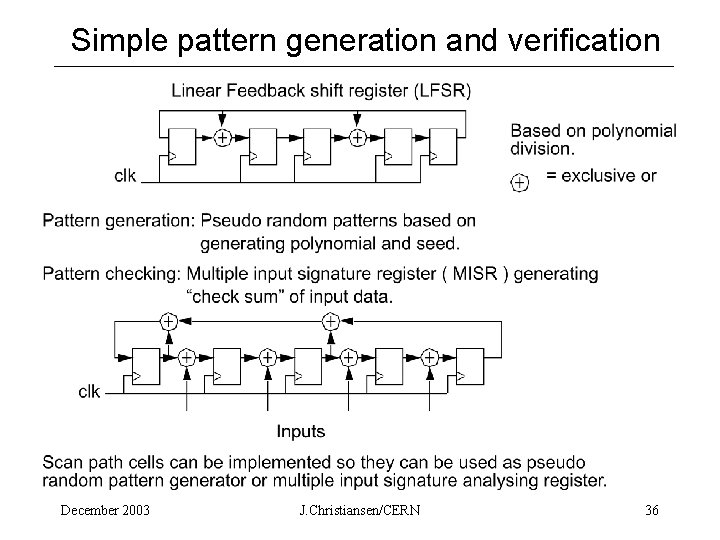

Simple pattern generation and verification December 2003 J. Christiansen/CERN 36

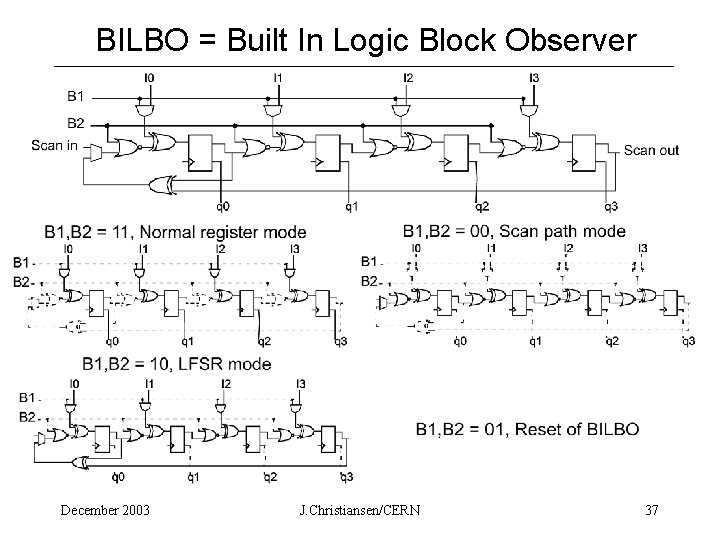

BILBO = Built In Logic Block Observer December 2003 J. Christiansen/CERN 37

Design for testability guidelines • Use static logic. • Make design completely synchronous. – use D flip-flops and not latches. – no clock gating. • No internal clock generation. • Prevent large counter like structures. • Use scan path (JTAG). • Use built in test of memories. December 2003 J. Christiansen/CERN 38

And if you forget about testing December 2003 J. Christiansen/CERN 39

- Slides: 39