TESTING OF COMBINATIONAL LOGIC CIRCUITS DIGITAL LOGIC CIRCUIT

TESTING OF COMBINATIONAL LOGIC CIRCUITS DIGITAL LOGIC CIRCUIT TESTING n DEFINITIONS n TYPICAL DIGITAL CIRCUIT TEST SETUP n FAULT MODELS n COMBINATIONAL LOGIC CIRCUITS n TEST GENERATION n EXCLUSIVE-OR METHOD n PATH-SENSITIZING METHOD n PATH-SESITIZING IN POPULAR GATES n PATH-SESITIZING IN A NETWORK n A NETWORK WITH FAN-OUT n COUNTER-EXAMPLE TO SINGLE-PATH SENSITIZING n UNTESTABLE FAULTS n MULTIPLE OUTPUT NETWORKS n FAULT DETECTION TEST SETS (FDTS) n FAULT TABLE REDUCTION – CHECK POINTS n MINIMUM FDTS __________________________________ n ECSE-323/Department of Electrical and Computer Engineering/Mc. Gill University/ Prof. Marin. Adapted from Digital Logic Circuit Analysis & Design, by Nelson, Nagle, Carroll, Irwin, Prentice-Hall, 1995, Chapter 12, pages 739 to 757 1

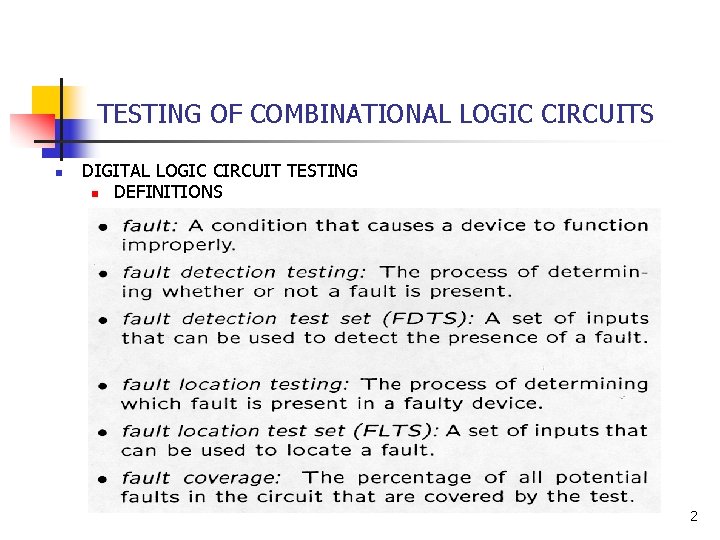

TESTING OF COMBINATIONAL LOGIC CIRCUITS n DIGITAL LOGIC CIRCUIT TESTING n DEFINITIONS 2

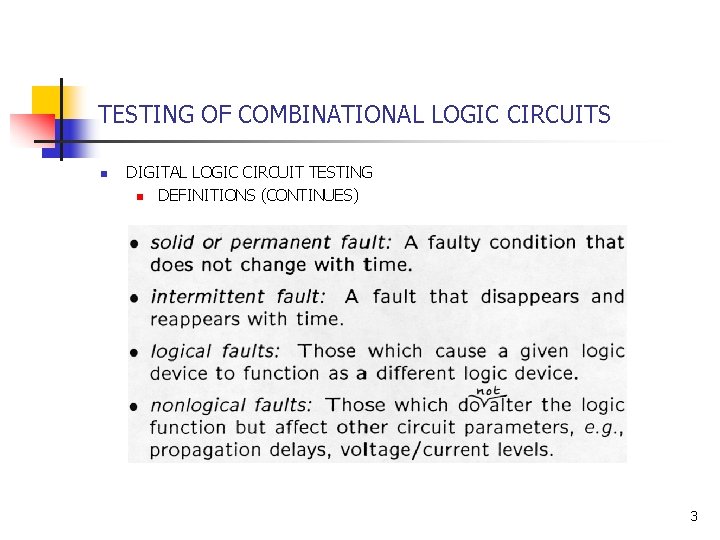

TESTING OF COMBINATIONAL LOGIC CIRCUITS n DIGITAL LOGIC CIRCUIT TESTING n DEFINITIONS (CONTINUES) 3

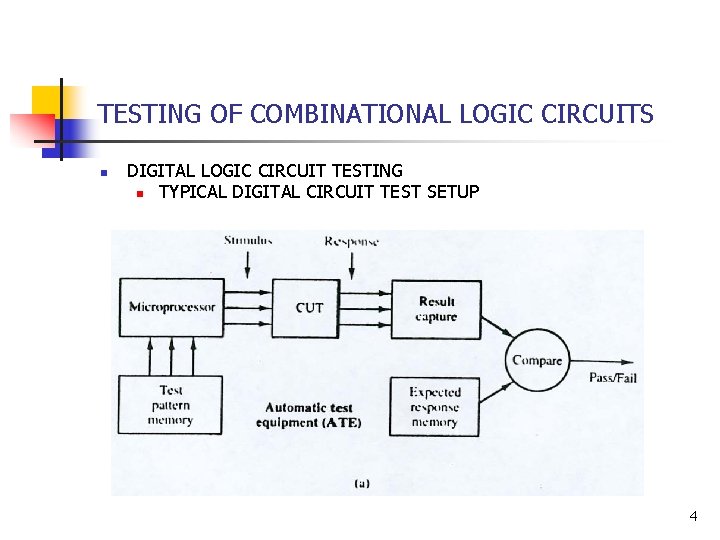

TESTING OF COMBINATIONAL LOGIC CIRCUITS n DIGITAL LOGIC CIRCUIT TESTING n TYPICAL DIGITAL CIRCUIT TEST SETUP 4

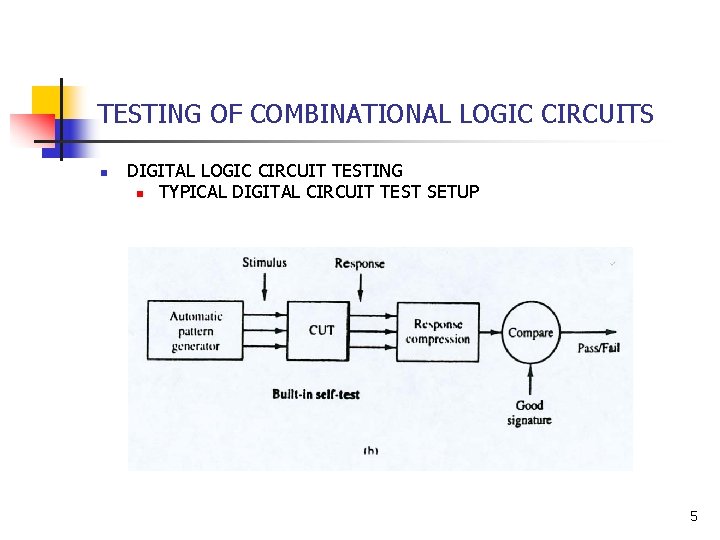

TESTING OF COMBINATIONAL LOGIC CIRCUITS n DIGITAL LOGIC CIRCUIT TESTING n TYPICAL DIGITAL CIRCUIT TEST SETUP 5

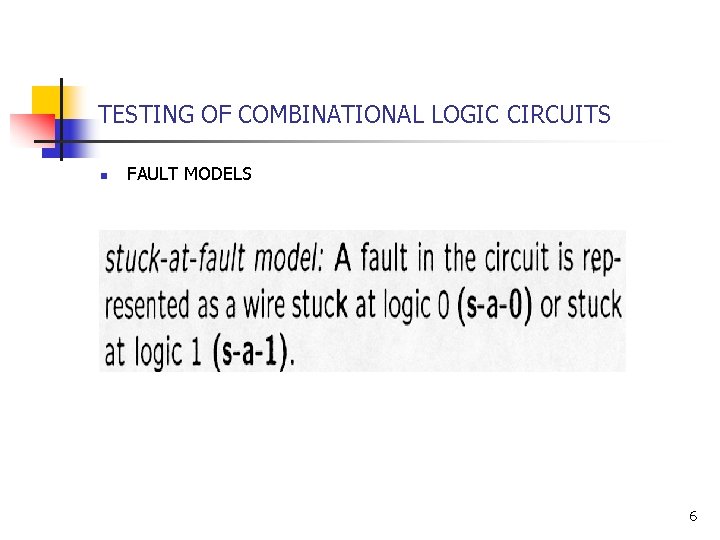

TESTING OF COMBINATIONAL LOGIC CIRCUITS n FAULT MODELS 6

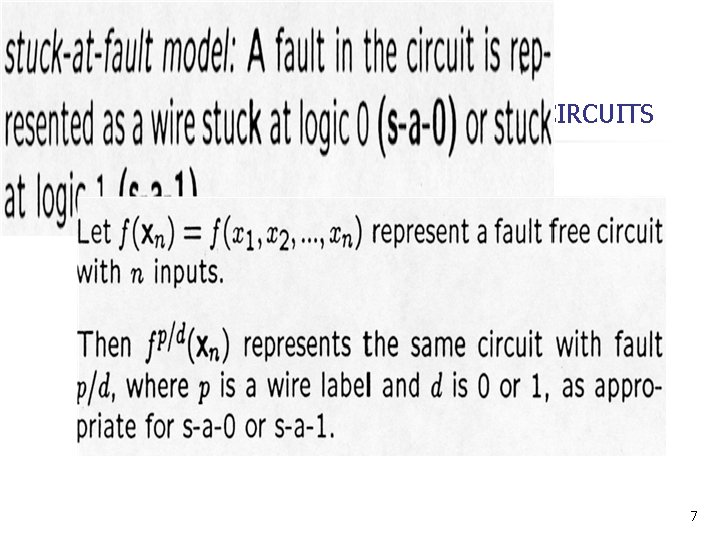

TESTING OF COMBINATIONAL LOGIC CIRCUITS n FAULT MODELS 7

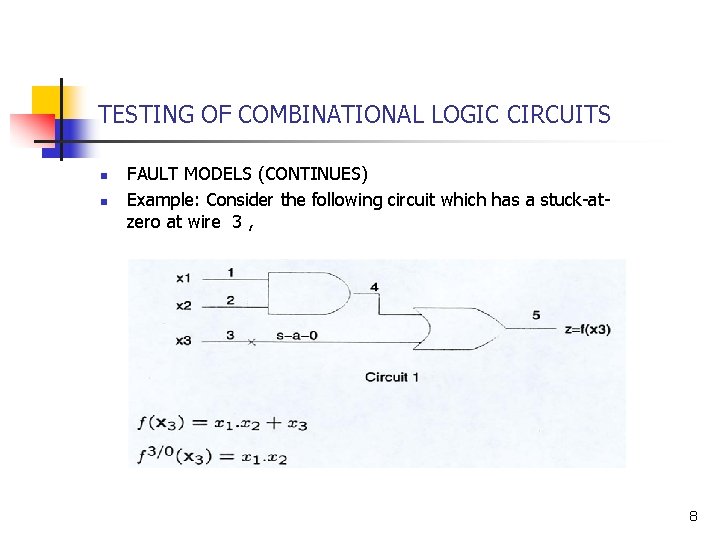

TESTING OF COMBINATIONAL LOGIC CIRCUITS n n FAULT MODELS (CONTINUES) Example: Consider the following circuit which has a stuck-atzero at wire 3 , 8

TESTING OF COMBINATIONAL LOGIC CIRCUITS n FAULT MODELS (CONTINUES) 9

TESTING OF COMBINATIONAL LOGIC CIRCUITS n COMBINATIONAL LOGIC CIRCUITS: n TEST GENERATION: DEFINITIONS 10

TESTING OF COMBINATIONAL LOGIC CIRCUITS n COMBINATIONAL LOGIC CIRCUITS: n TEST GENERATION: DEFINITIONS 11

TESTING OF COMBINATIONAL LOGIC CIRCUITS n TEST GENERATION: EXCLUSIVE-OR METHOD 12

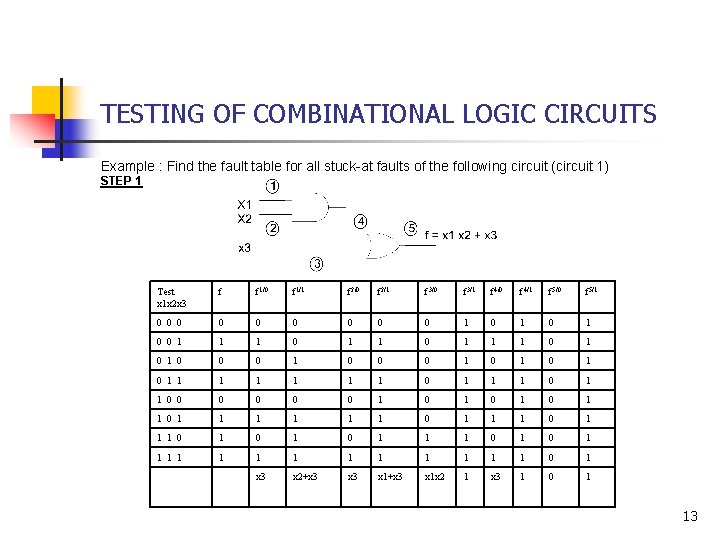

TESTING OF COMBINATIONAL LOGIC CIRCUITS Example : Find the fault table for all stuck-at faults of the following circuit (circuit 1) STEP 1 Test x 1 x 2 x 3 f f 1/0 f 1/1 f 2/0 f 2/1 f 3/0 f 3/1 f 4/0 f 4/1 f 5/0 f 5/1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 1 0 0 0 1 0 1 0 1 1 1 1 0 1 1 1 0 1 0 1 1 1 1 1 1 1 0 1 x 3 x 2+x 3 x 1+x 3 x 1 x 2 1 x 3 1 0 1 13

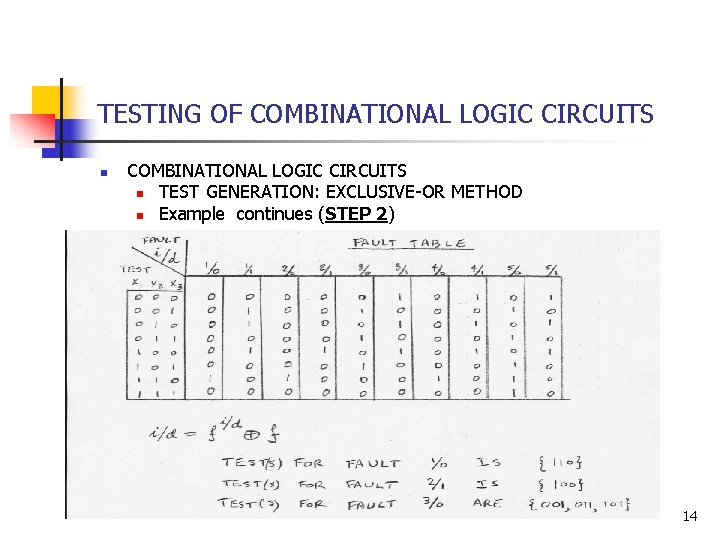

TESTING OF COMBINATIONAL LOGIC CIRCUITS n TEST GENERATION: EXCLUSIVE-OR METHOD n Example continues (STEP 2) 14

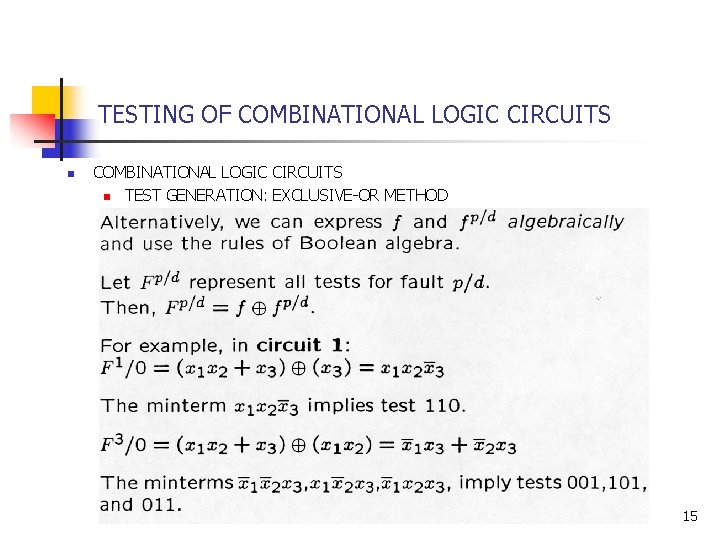

TESTING OF COMBINATIONAL LOGIC CIRCUITS n TEST GENERATION: EXCLUSIVE-OR METHOD 15

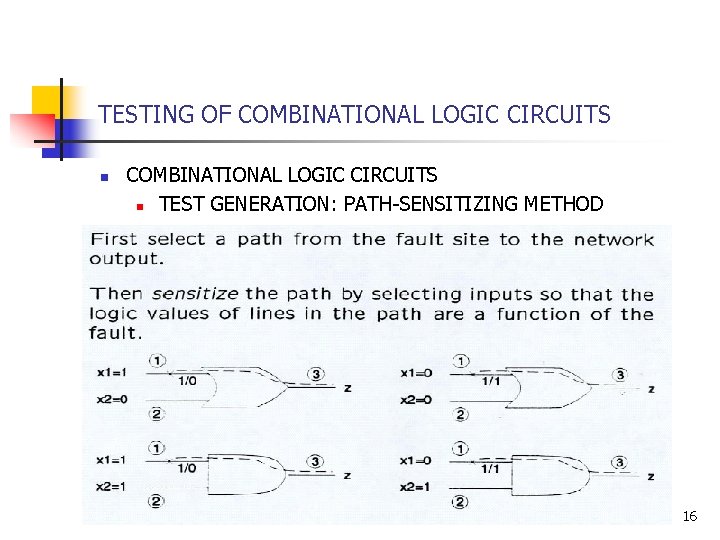

TESTING OF COMBINATIONAL LOGIC CIRCUITS n TEST GENERATION: PATH-SENSITIZING METHOD 16

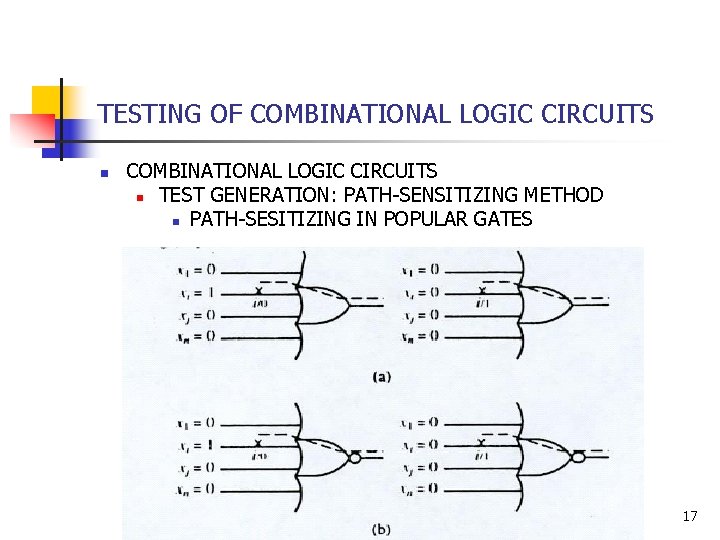

TESTING OF COMBINATIONAL LOGIC CIRCUITS n TEST GENERATION: PATH-SENSITIZING METHOD n PATH-SESITIZING IN POPULAR GATES 17

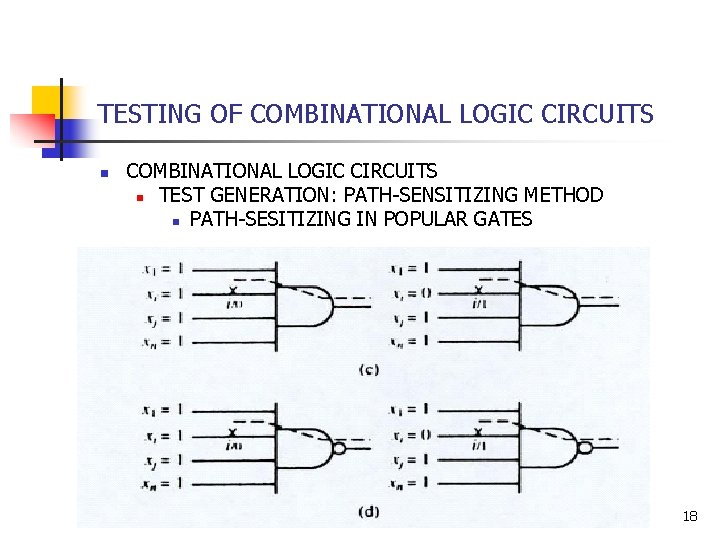

TESTING OF COMBINATIONAL LOGIC CIRCUITS n TEST GENERATION: PATH-SENSITIZING METHOD n PATH-SESITIZING IN POPULAR GATES 18

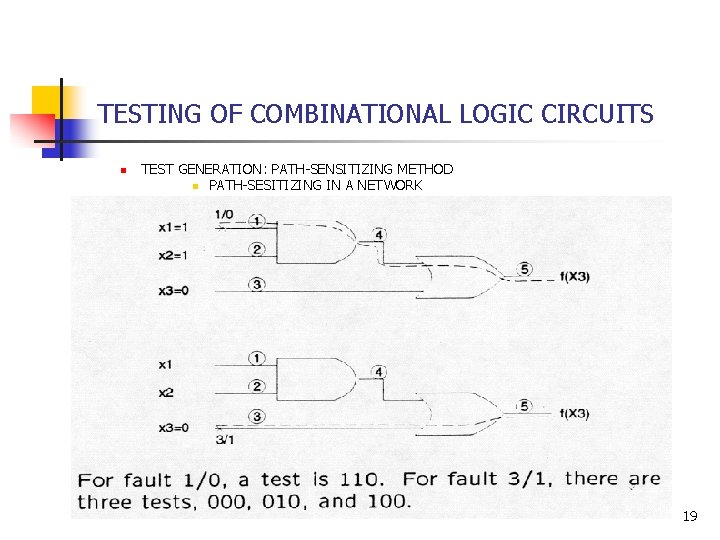

TESTING OF COMBINATIONAL LOGIC CIRCUITS n TEST GENERATION: PATH-SENSITIZING METHOD n PATH-SESITIZING IN A NETWORK 19

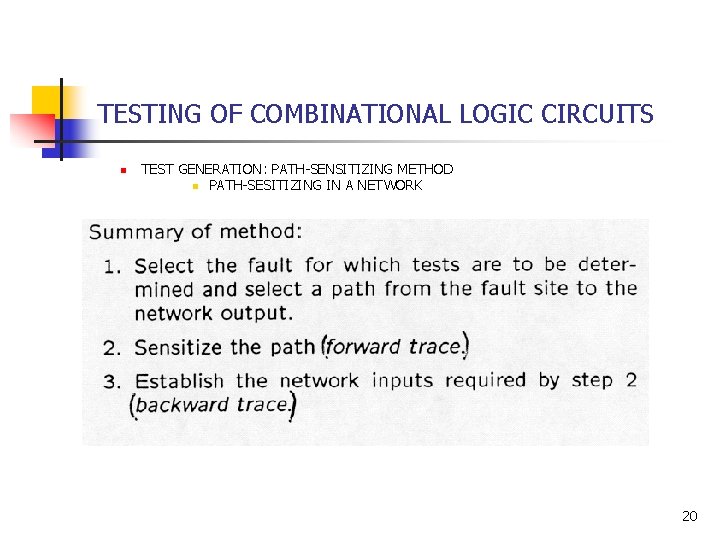

TESTING OF COMBINATIONAL LOGIC CIRCUITS n TEST GENERATION: PATH-SENSITIZING METHOD n PATH-SESITIZING IN A NETWORK 20

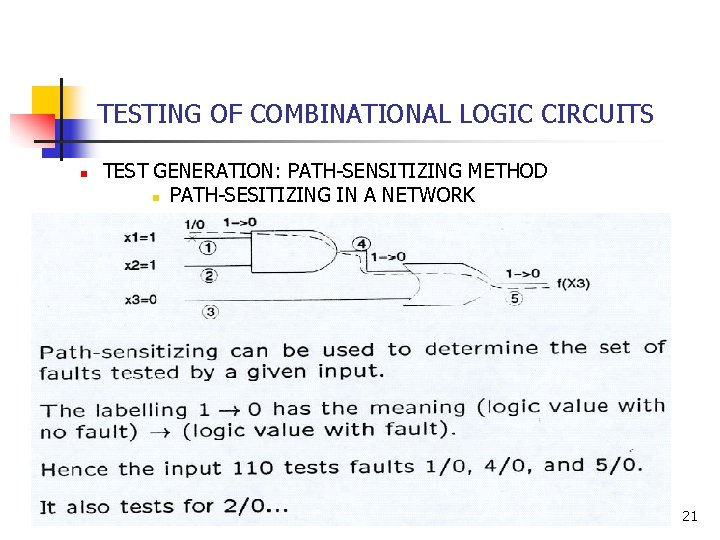

TESTING OF COMBINATIONAL LOGIC CIRCUITS n TEST GENERATION: PATH-SENSITIZING METHOD n PATH-SESITIZING IN A NETWORK 21

TESTING OF COMBINATIONAL LOGIC CIRCUITS n TEST GENERATION: PATH-SENSITIZING METHOD n PATH-SESITIZING IN A NETWORK 22

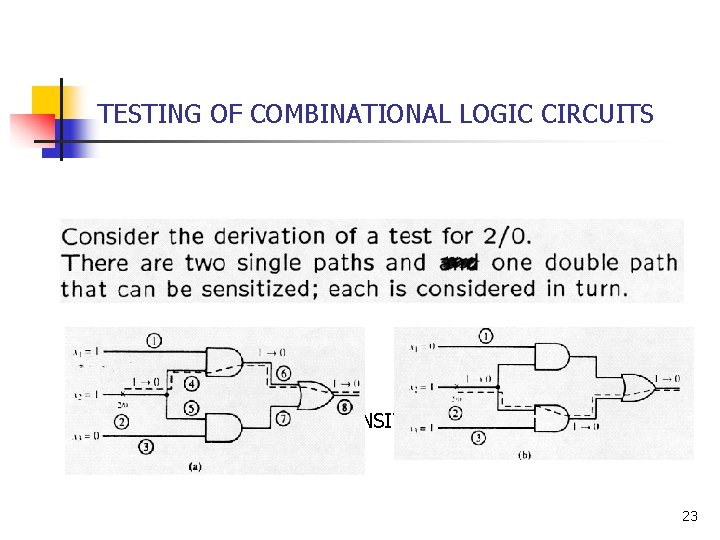

TESTING OF COMBINATIONAL LOGIC CIRCUITS n n TEST GENERATION - PATH-SENSITIZING METHOD: A NETWORK WITH FAN-OUT 23

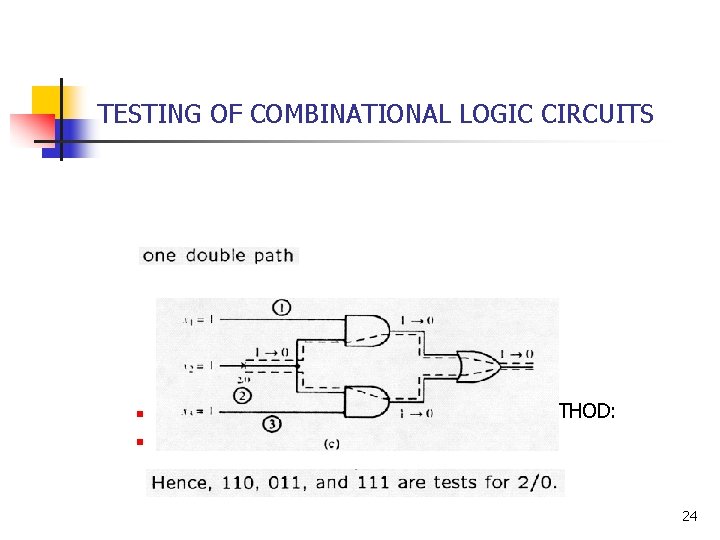

TESTING OF COMBINATIONAL LOGIC CIRCUITS n n TEST GENERATION - PATH-SENSITIZING METHOD: A NETWORK WITH FAN-OUT 24

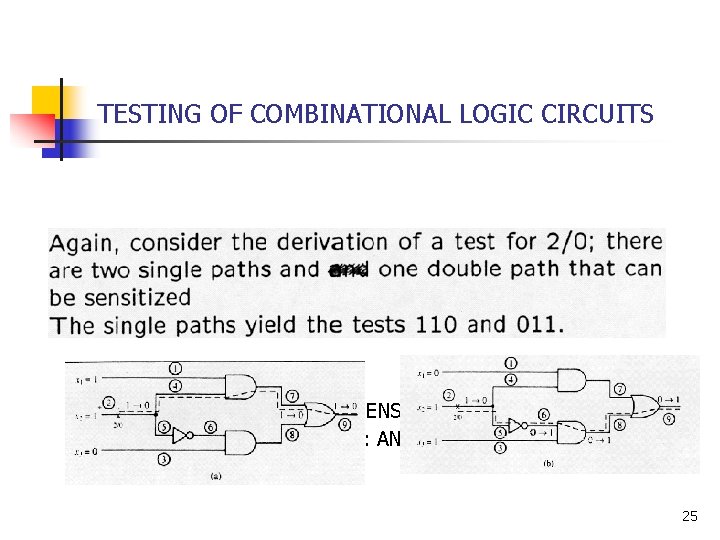

TESTING OF COMBINATIONAL LOGIC CIRCUITS n n TEST GENERATION - PATH-SENSITIZING METHOD: A NETWORK WITH FAN-OUT: ANOTHER EXAMPLE 25

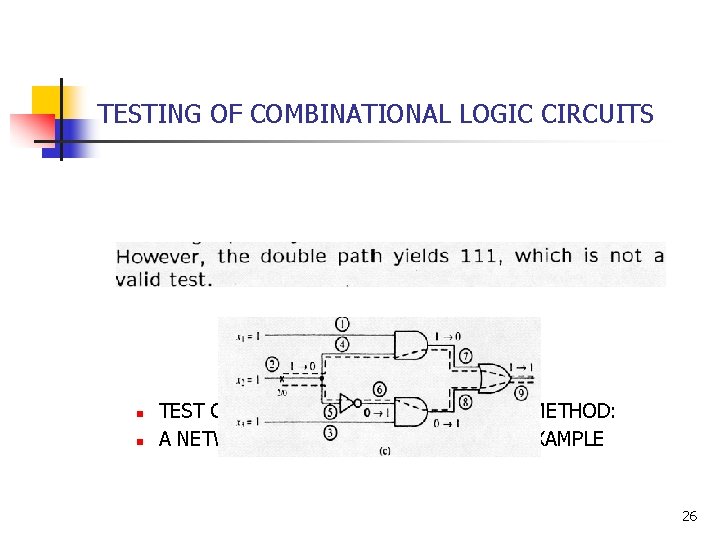

TESTING OF COMBINATIONAL LOGIC CIRCUITS n n TEST GENERATION - PATH-SENSITIZING METHOD: A NETWORK WITH FAN-OUT: ANOTHER EXAMPLE 26

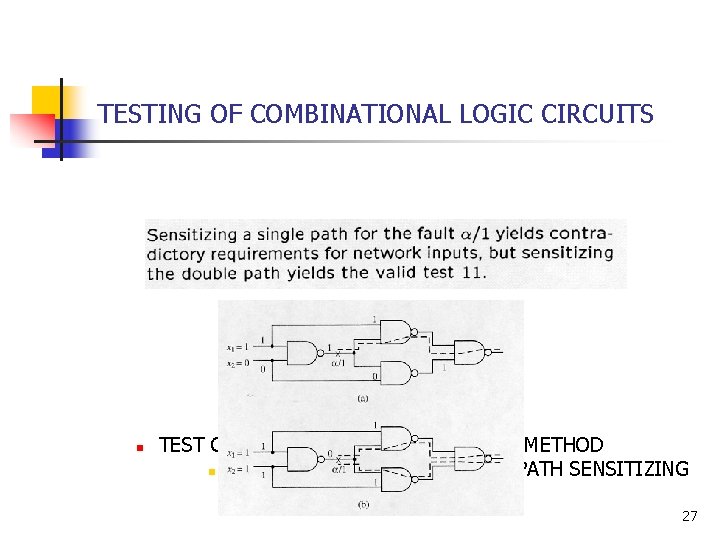

TESTING OF COMBINATIONAL LOGIC CIRCUITS n TEST GENERATION: PATH-SENSITIZING METHOD n COUNTER-EXAMPLE TO SINGLE-PATH SENSITIZING 27

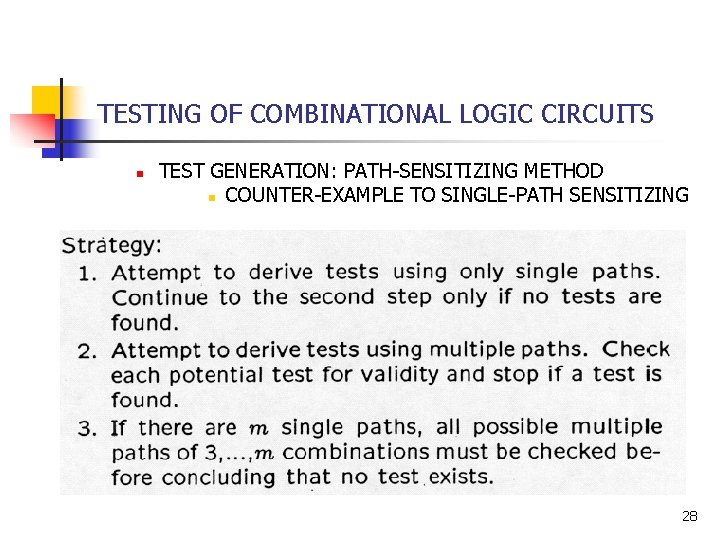

TESTING OF COMBINATIONAL LOGIC CIRCUITS n TEST GENERATION: PATH-SENSITIZING METHOD n COUNTER-EXAMPLE TO SINGLE-PATH SENSITIZING 28

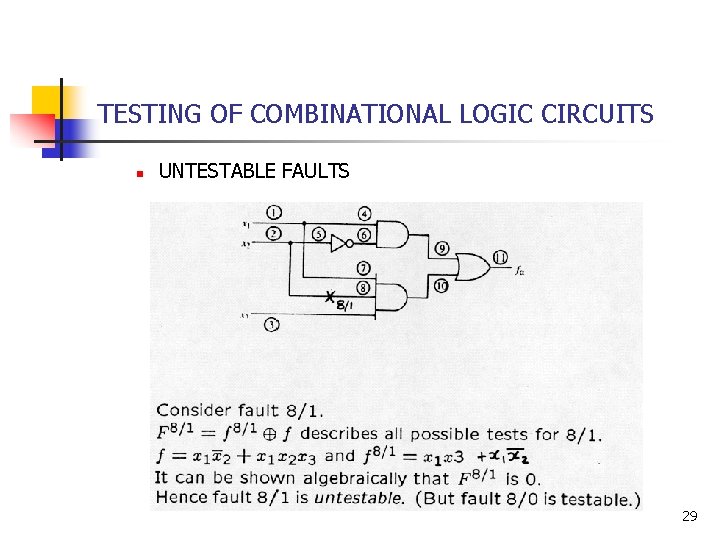

TESTING OF COMBINATIONAL LOGIC CIRCUITS n UNTESTABLE FAULTS 29

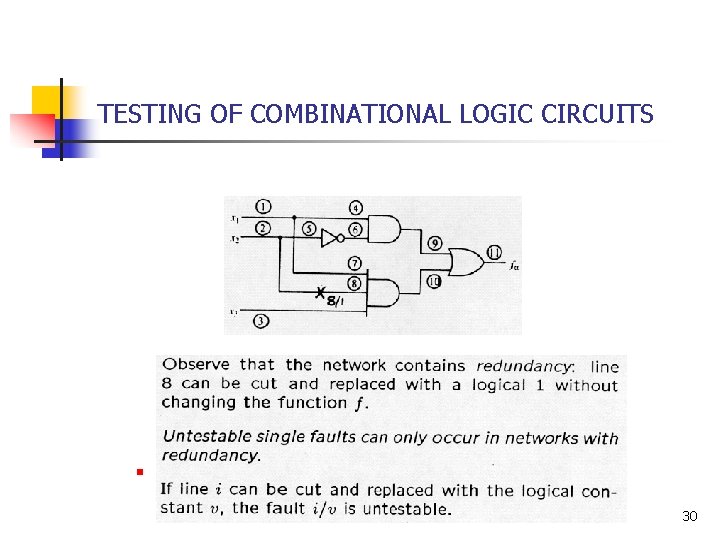

TESTING OF COMBINATIONAL LOGIC CIRCUITS n UNTESTABLE FAULTS (CONTINUES) 30

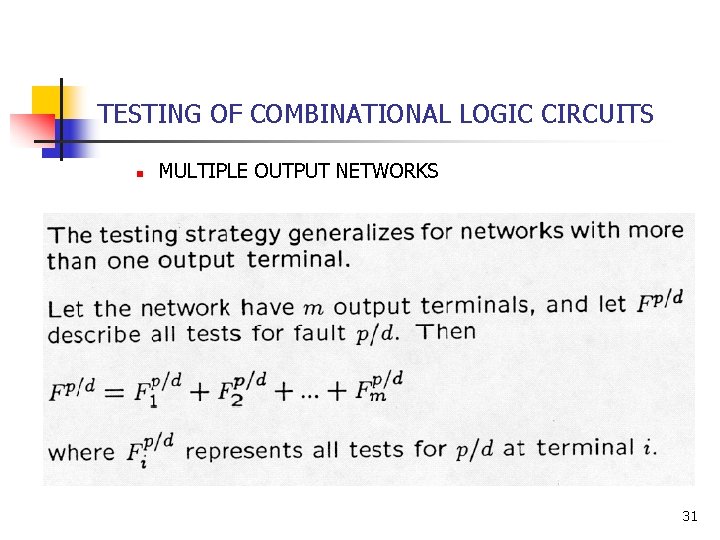

TESTING OF COMBINATIONAL LOGIC CIRCUITS n MULTIPLE OUTPUT NETWORKS 31

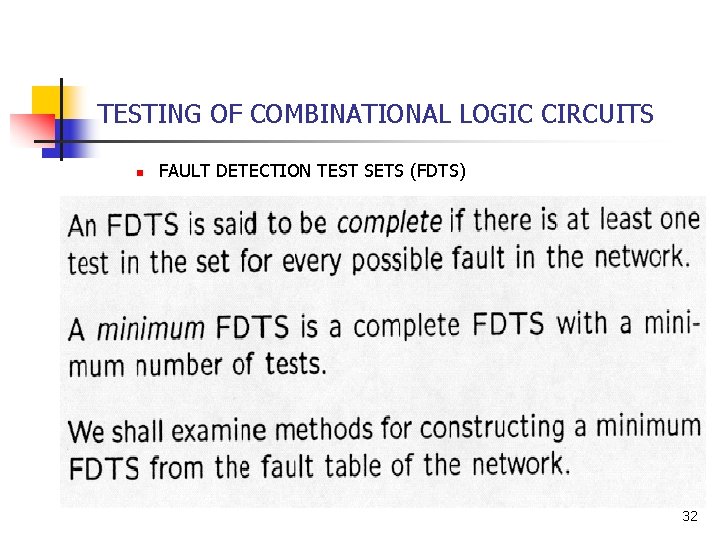

TESTING OF COMBINATIONAL LOGIC CIRCUITS n FAULT DETECTION TEST SETS (FDTS) 32

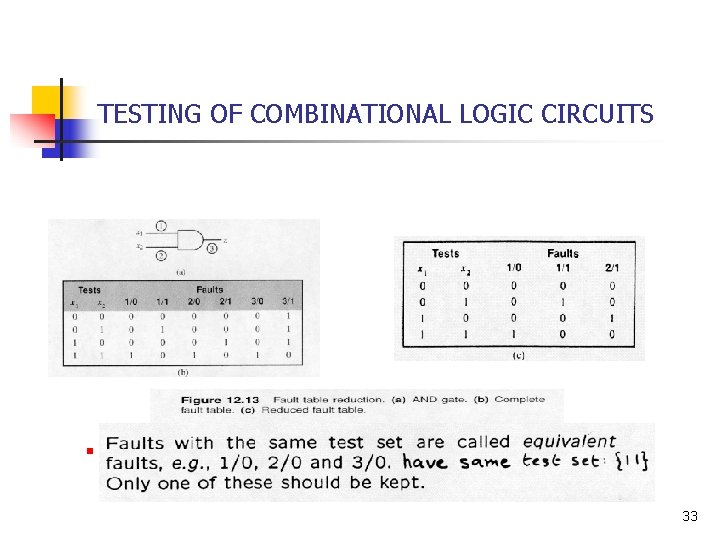

TESTING OF COMBINATIONAL LOGIC CIRCUITS n FAULT DETECTION TEST SETS (FDTS) n FAULT TABLE REDUCTION – CHECK POINTS 33

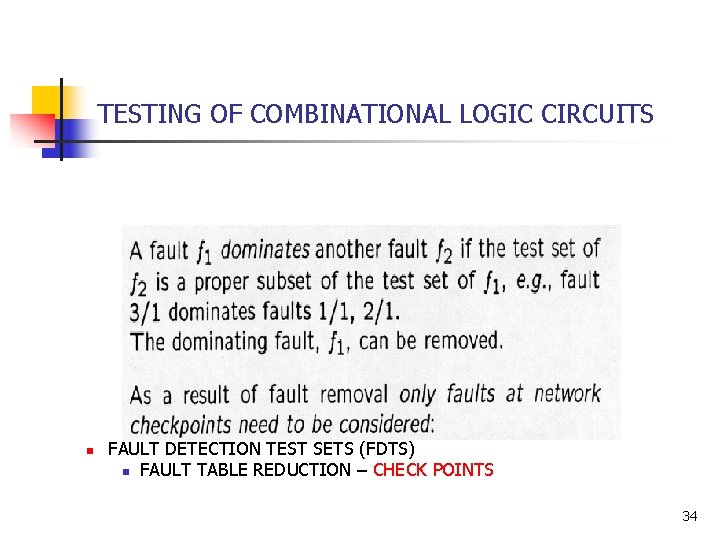

TESTING OF COMBINATIONAL LOGIC CIRCUITS n FAULT DETECTION TEST SETS (FDTS) n FAULT TABLE REDUCTION – CHECK POINTS 34

TESTING OF COMBINATIONAL LOGIC CIRCUITS n FAULT DETECTION TEST SETS (FDTS) n FAULT TABLE REDUCTION – CHECK POINTS n CHECK POINTS ARE: n ALL INPUT WIRES THAT ARE NOT FAN-OUT STEMS n ALL WIRES THAT ARE FAN-OUT BRANCHES n OUTPUTS TO XOR GATES n FAN-OUT STEM REFERS TO THE WIRE PRECEDING THE n FAN-OUT BRANCHES REFERS TO THE WIRES BEYOND FAN-OUT POINT. THE FAN-OUT POINT. EXAMPLE FOLLOWS 35

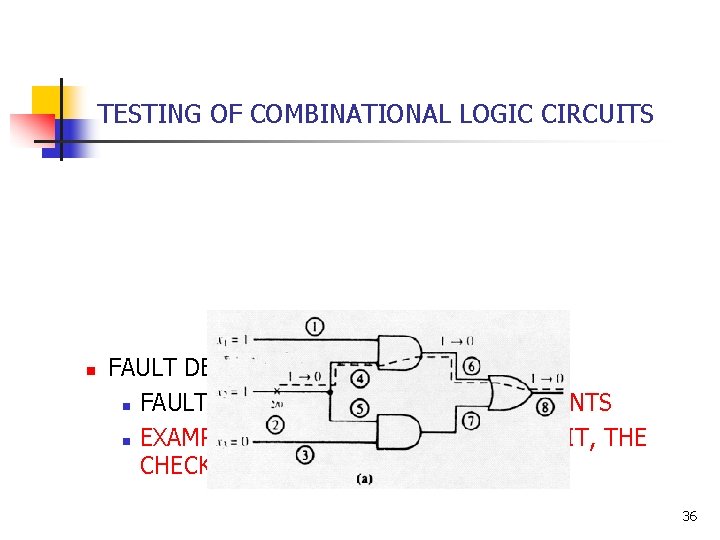

TESTING OF COMBINATIONAL LOGIC CIRCUITS n FAULT DETECTION TEST SETS (FDTS) n FAULT TABLE REDUCTION – CHECK POINTS n EXAMPLE: FOR THE FOLLOWING CIRCUIT, THE CHECK POINTS ARE 1, 3, 4 AND 5 36

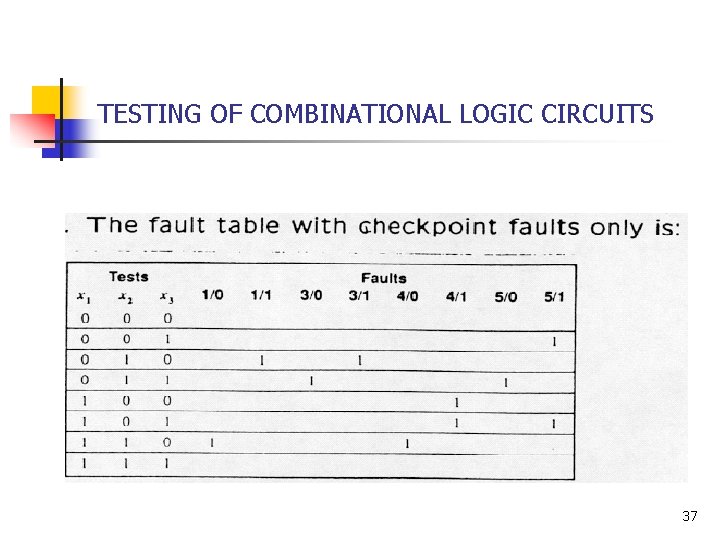

TESTING OF COMBINATIONAL LOGIC CIRCUITS EXAMPLE (CONTINUES): 37

TESTING OF COMBINATIONAL LOGIC CIRCUITS n FAULT DETECTION TEST SETS (FDTS) n MINIMUM FDTS 38

TESTING OF COMBINATIONAL LOGIC CIRCUITS n FAULT DETECTION TEST SETS (FDTS): MINIMUM FDTS: n APPLYING THE PROCEDURE TO THE TABLE ON SLIDE 37 YIEDLS {010, 011, 101, 110} AS A MINIMUM TEST SET. n THE PETRICK FUNCTION, P, CAN BE USED TO REDUCE THE TABLE: LABELLING THE TESTS ON THE TABLE P 0, P 1, P 2, P 3, P 4, P 5, P 6, P 7 P = (P 6)(P 2)(P 3)(P 2)(P 6)(P 4+P 5)(P 3)(P 1+P 5) P = P 6 P 2 P 3 (P 4+P 5)(P 1+P 5) = P 6 P 2 P 3 (P 4 P 1+P 5) P = P 6 P 2 P 3 P 4 P 1 + P 6 P 2 P 3 P 5. THE MINIMAL FDTS IS {P 6, P 2, P 3, P 5} = {110, 011, 101} FOR LARGE FAULT TABLES, THE USE OF PROCEDURES FOR SELECTING A NEAR MINIMAL IS MORE PRACTICAL. 39

- Slides: 39