Testing for readmaster Block diagram CPU 1 1

Testing for read_master

Block diagram CPU 1 1 Register File 2 Read_master 3 4 Dual Port Memory

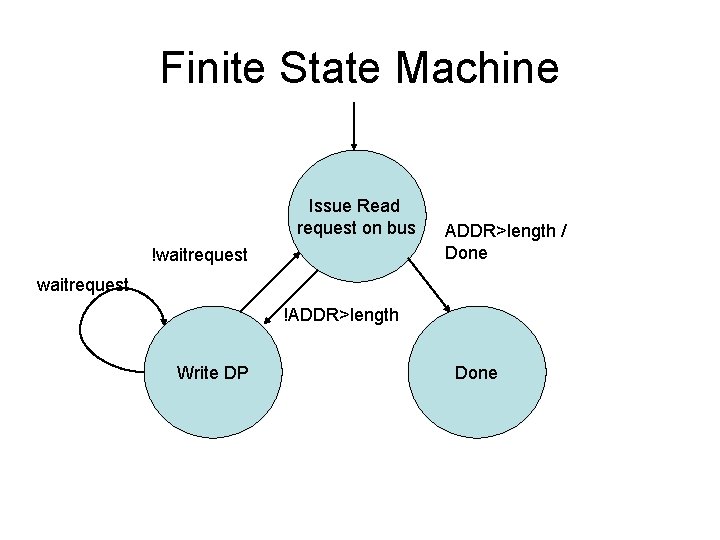

Finite State Machine Issue Read request on bus !waitrequest ADDR>length / Done waitrequest !ADDR>length Write DP Done

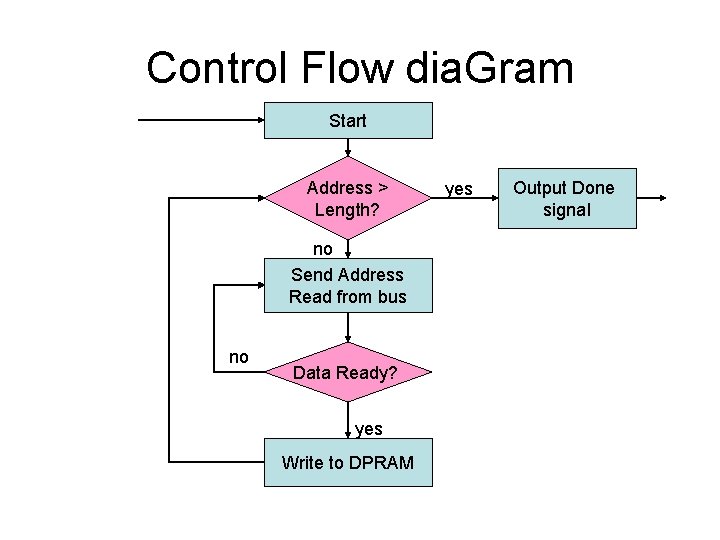

Control Flow dia. Gram Start Address > Length? no Send Address Read from bus no Data Ready? yes Write to DPRAM yes Output Done signal

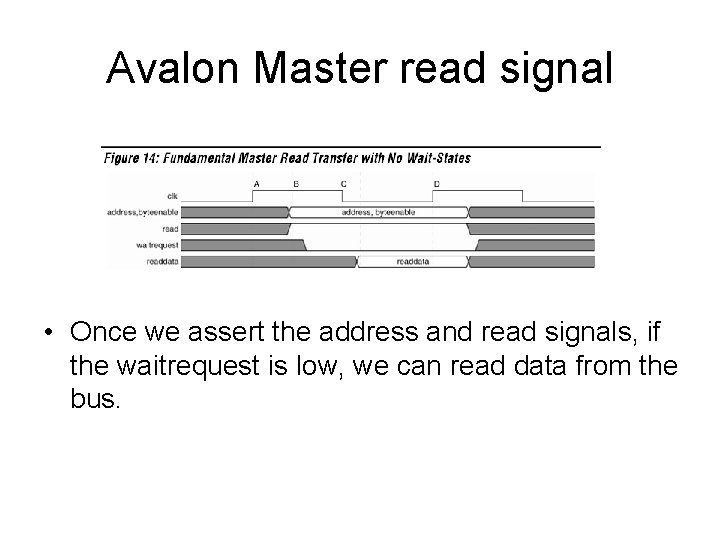

Avalon Master read signal • Once we assert the address and read signals, if the waitrequest is low, we can read data from the bus.

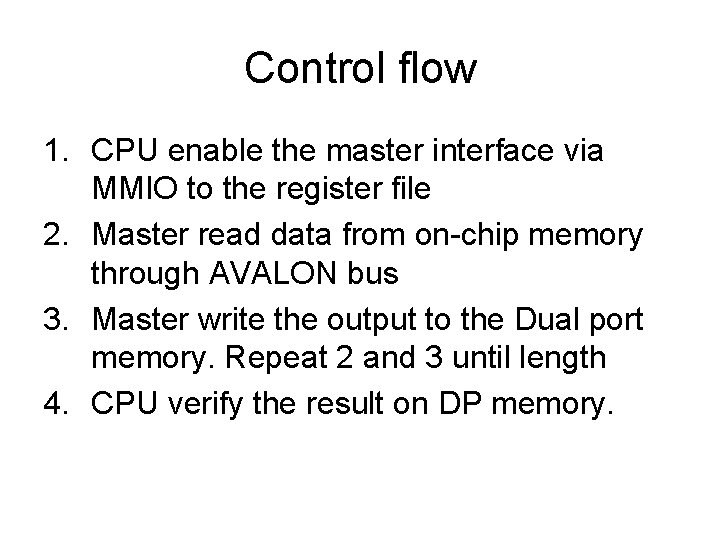

Control flow 1. CPU enable the master interface via MMIO to the register file 2. Master read data from on-chip memory through AVALON bus 3. Master write the output to the Dual port memory. Repeat 2 and 3 until length 4. CPU verify the result on DP memory.

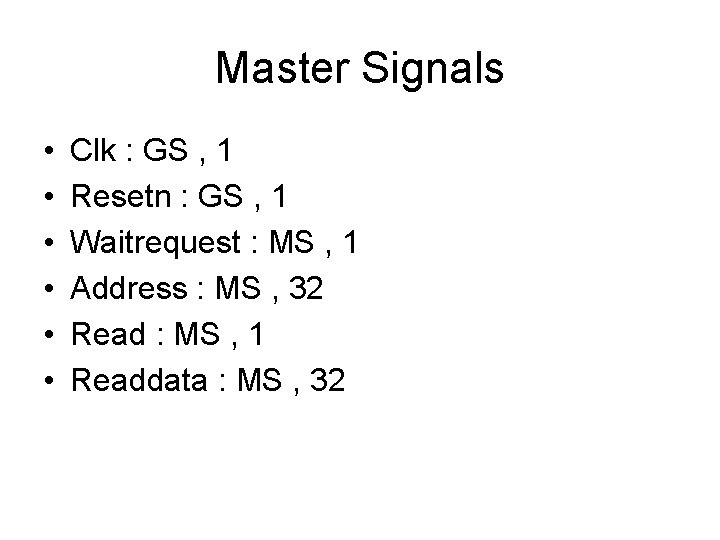

Master Signals • • • Clk : GS , 1 Resetn : GS , 1 Waitrequest : MS , 1 Address : MS , 32 Read : MS , 1 Readdata : MS , 32

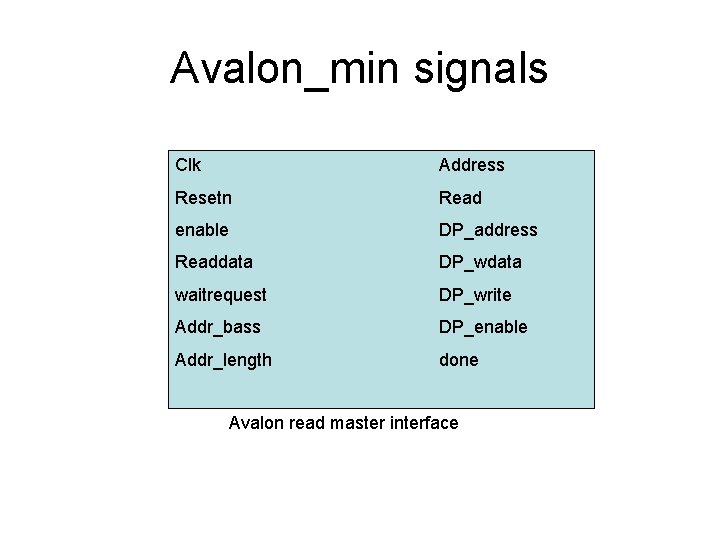

Avalon_min signals Clk Address Resetn Read enable DP_address Readdata DP_wdata waitrequest DP_write Addr_bass DP_enable Addr_length done Avalon read master interface

Avalon read master signals

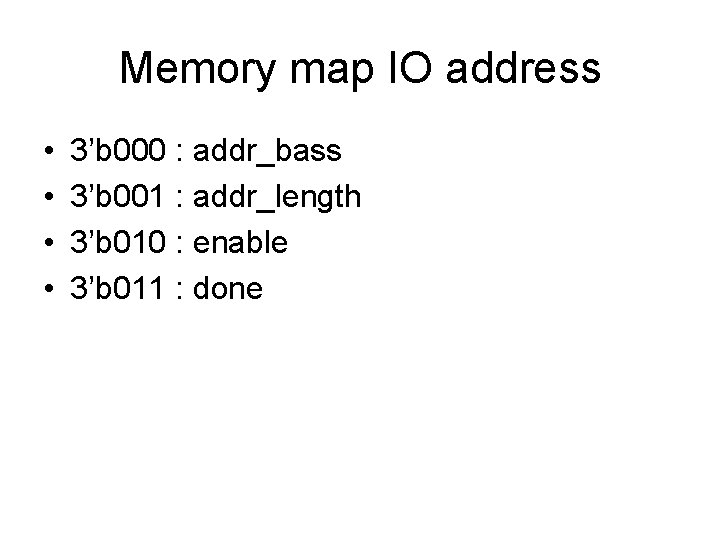

Memory map IO address • • 3’b 000 : addr_bass 3’b 001 : addr_length 3’b 010 : enable 3’b 011 : done

Implementation note • NIOS 2 system is Byte address. If we want to read a word(4 bytes) on the bus, we have to take about the address ourselves.

- Slides: 11