Testability in EOCHL and beyond Vladimir Zivkovic National

Testability in EOCHL (and beyond…) Vladimir Zivkovic National Institute for Subatomic Physics (Nikhef), Amsterdam, The Netherlands FEI 4_A review, 2 -3 rd November 2009 CERN, Geneve

Outline • • • Introduction Df. T Architecture Df. T Flow Back-end Test Development Future Work

Functional vs Structural Testing § Functional testing verifies that a circuit fulfils the desired spec. § Functional testing not feasible for exhaustive tests. § Example: 32 -bit adder requires 265 ≈ 3. 7*1019 test vectors § Structural test focuses rather on the circuit structure and can cover manufacturing defects that otherwise may not have been detected by functional testing. § Power or ground shorts § Open interconnect on the die (caused by dust particles) § Short circuited source or drain on the transistor, (caused by metal spike through)

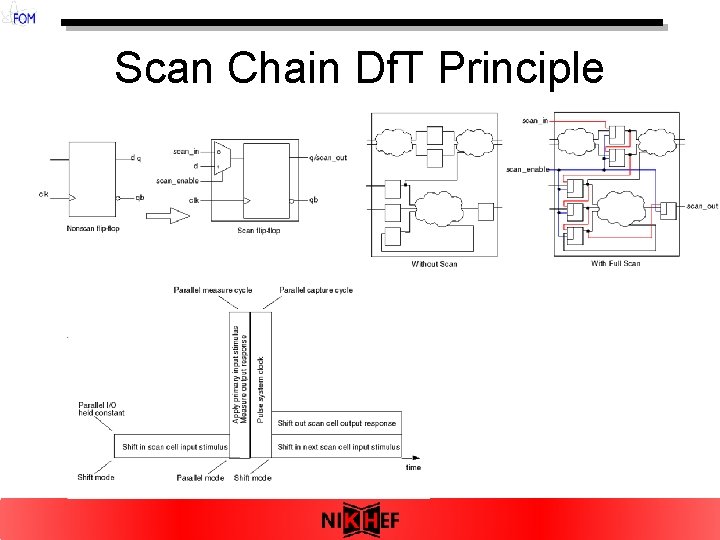

Scan Chain Df. T Principle

Outline • • • Introduction Df. T Architecture Df. T Flow Back-end Test Development Future Work

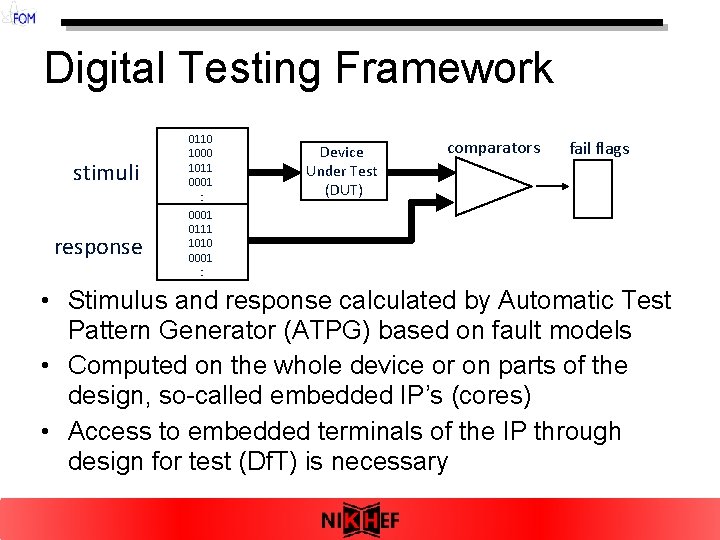

Digital Testing Framework stimuli response 0110 1000 1011 0001 : Device Under Test (DUT) comparators fail flags 0001 0111 1010 0001 : • Stimulus and response calculated by Automatic Test Pattern Generator (ATPG) based on fault models • Computed on the whole device or on parts of the design, so-called embedded IP’s (cores) • Access to embedded terminals of the IP through design for test (Df. T) is necessary

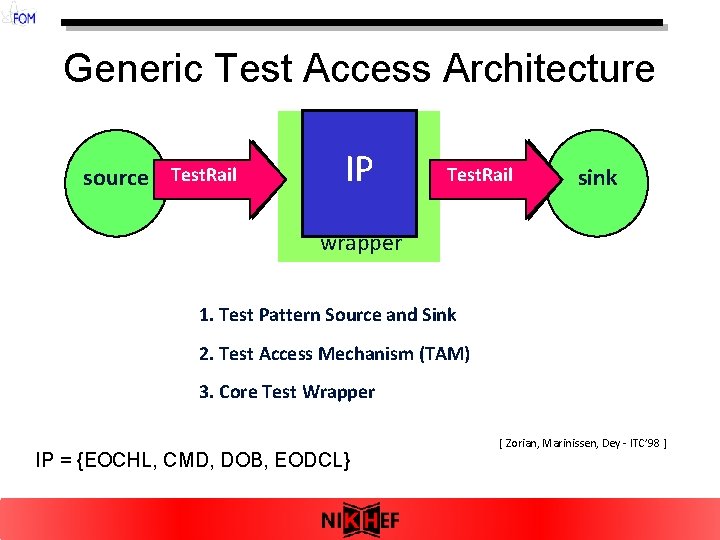

Generic Test Access Architecture TAM source Test. Rail IP Test. Rail TAM sink wrapper 1. Test Pattern Source and Sink 2. Test Access Mechanism (TAM) 3. Core Test Wrapper IP = {EOCHL, CMD, DOB, EODCL} [ Zorian, Marinissen, Dey - ITC’ 98 ]

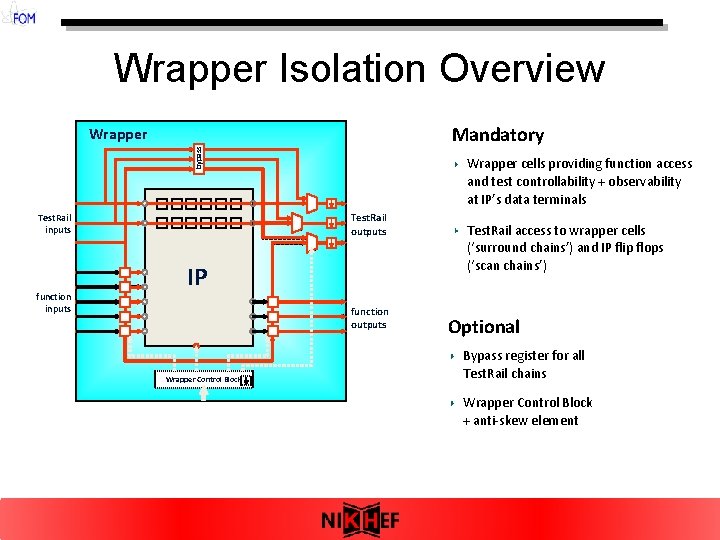

Wrapper Isolation Overview Mandatory bypass Wrapper Test. Rail outputs Test. Rail inputs function inputs Wrapper cells providing function access and test controllability + observability at IP’s data terminals IP function outputs Wrapper Control Block Test. Rail access to wrapper cells (‘surround chains’) and IP flip flops (‘scan chains’) Optional Bypass register for all Test. Rail chains Wrapper Control Block + anti-skew element

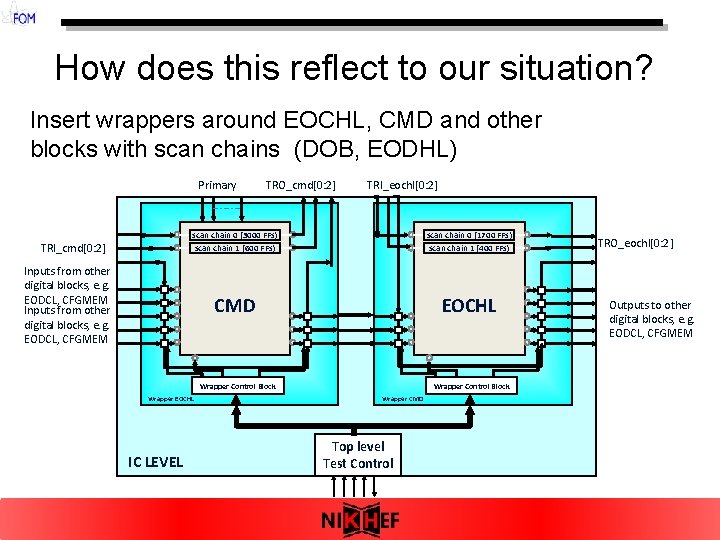

How does this reflect to our situation? Insert wrappers around EOCHL, CMD and other blocks with scan chains (DOB, EODHL) Primary TRI_cmd[0: 2] TRO_cmd[0: 2] TRI_eochl[0: 2] scan chain 0 (3000 FFs) scan chain 1 (600 FFs) scan chain 0 (1700 FFs) scan chain 1 (400 FFs) CMD EOCHL Inputs from other digital blocks, e. g. EODCL, CFGMEM Wrapper Control Block Wrapper EOCHL IC LEVEL Wrapper Control Block Wrapper CMD Top level Test Control TRO_eochl[0: 2] Outputs to other digital blocks, e. g. EODCL, CFGMEM

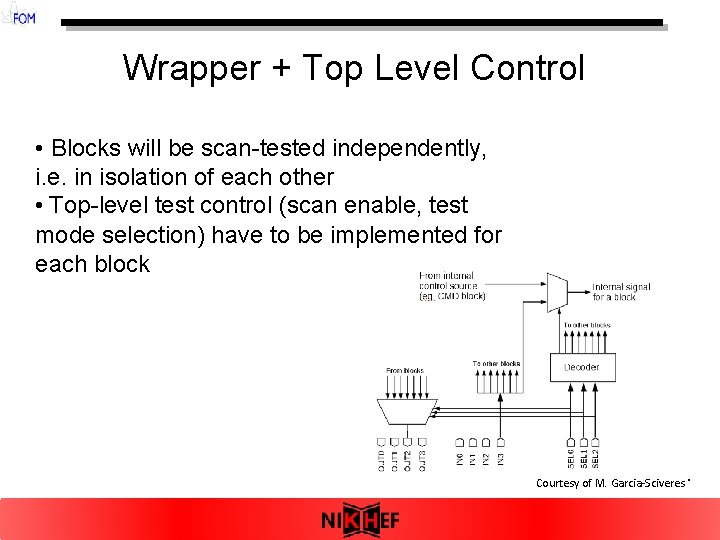

Wrapper + Top Level Control • Blocks will be scan-tested independently, i. e. in isolation of each other • Top-level test control (scan enable, test mode selection) have to be implemented for each block Courtesy of M. Garcia-Sciveres *

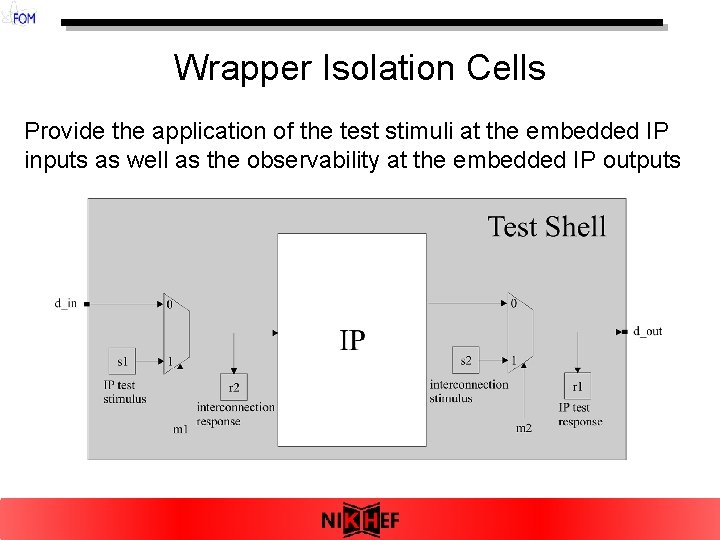

Wrapper Isolation Cells Provide the application of the test stimuli at the embedded IP inputs as well as the observability at the embedded IP outputs

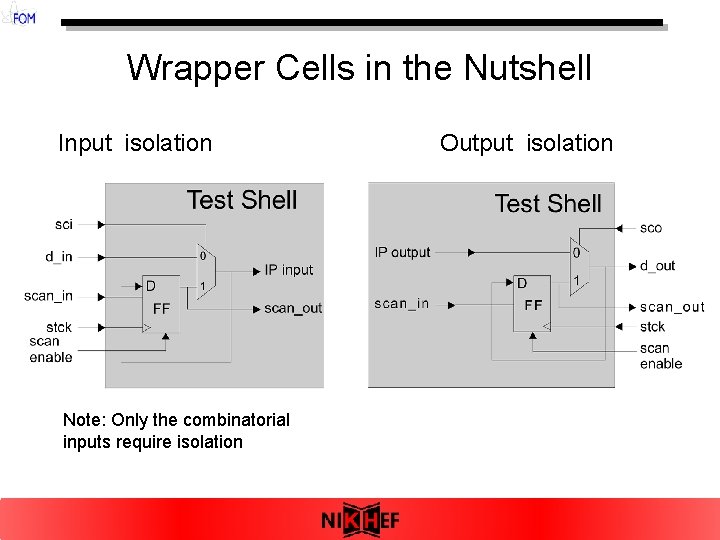

Wrapper Cells in the Nutshell Input isolation Note: Only the combinatorial inputs require isolation Output isolation

Outline • • • Introduction Df. T Architecture Df. T Flow Back-end Test Development Future Work

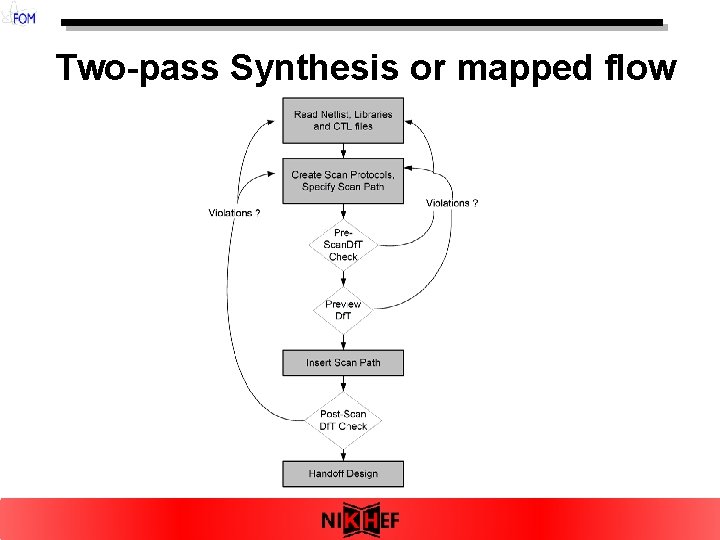

Two-pass Synthesis or mapped flow

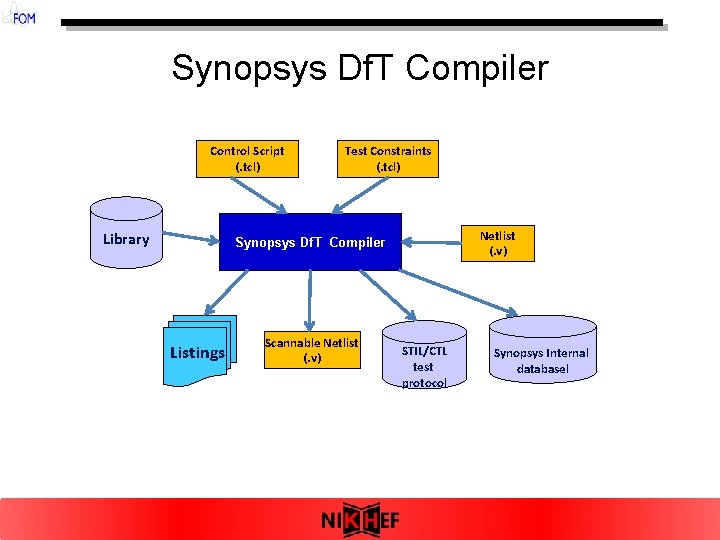

Synopsys Df. T Compiler Control Script (. tcl) Library Test Constraints (. tcl) Netlist (. v) Synopsys Df. T Compiler Listings Scannable Netlist (. v) STIL/CTL test protocol Synopsys Internal databasel

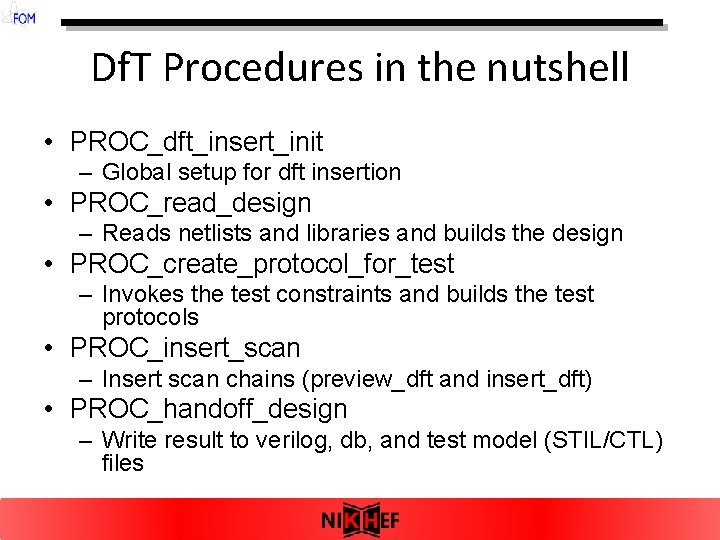

Df. T Procedures in the nutshell • PROC_dft_insert_init – Global setup for dft insertion • PROC_read_design – Reads netlists and libraries and builds the design • PROC_create_protocol_for_test – Invokes the test constraints and builds the test protocols • PROC_insert_scan – Insert scan chains (preview_dft and insert_dft) • PROC_handoff_design – Write result to verilog, db, and test model (STIL/CTL) files

Scan Chain reports for the EOCHL • 1 scan chain, length= 2927 • Standard Df. T signals: si, so, se • Clocked with an additional test clock (tck) –clock gating with functional clocks performed at the top level of the IP • Additional Df. T signal tm (to enable the test clock)

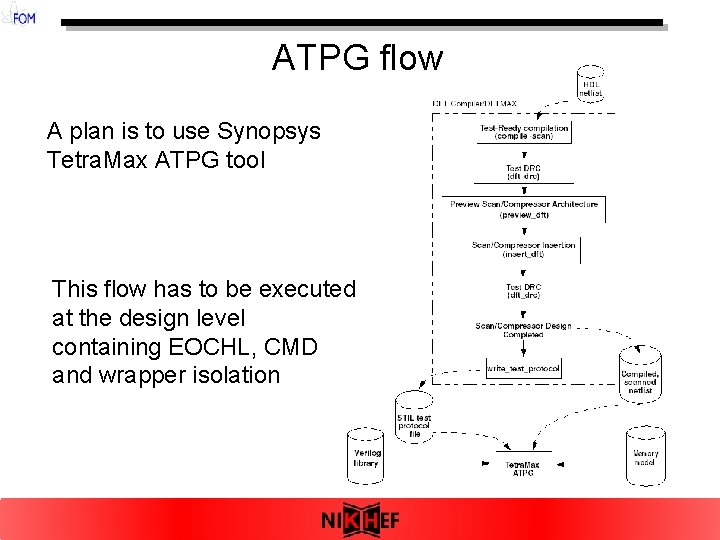

ATPG flow A plan is to use Synopsys Tetra. Max ATPG tool This flow has to be executed at the design level containing EOCHL, CMD and wrapper isolation

Test Patterns The Tetra. Max ATPG is expected to generate the following: • Continuity test patterns – To check the scan chain structures themsleves, typically 11101000 sequence is shifted through • Scan chain patterns for stuck-at faults Optionally: • IDDQ patterns • Transition/Path delay fault patterns • Bridge patterns

Outline • • • Introduction Df. T Architecture Df. T Flow Back-end Test Development Future Work

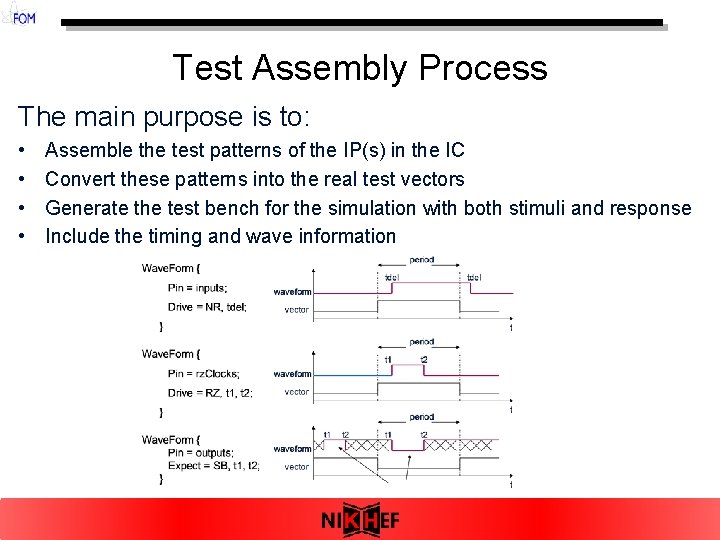

Test Assembly Process The main purpose is to: • • Assemble the test patterns of the IP(s) in the IC Convert these patterns into the real test vectors Generate the test bench for the simulation with both stimuli and response Include the timing and wave information

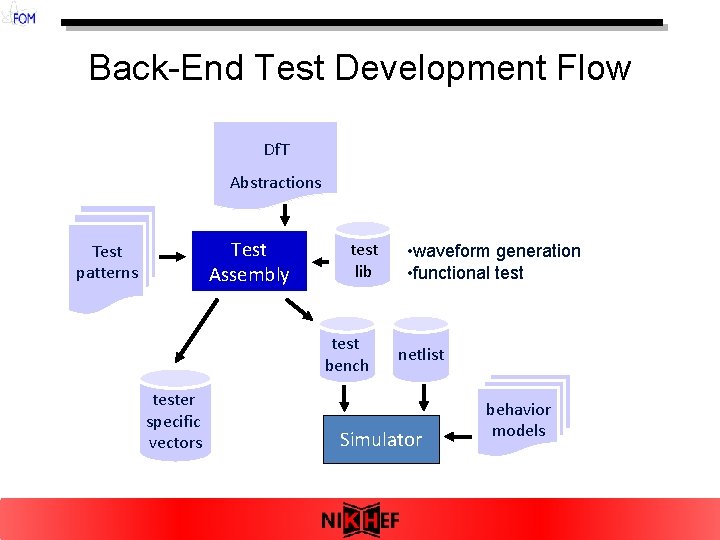

Back-End Test Development Flow Df. T Abstractions Test Assembly Test patterns test lib test bench tester specific vectors • waveform generation • functional test netlist Simulator behavior models

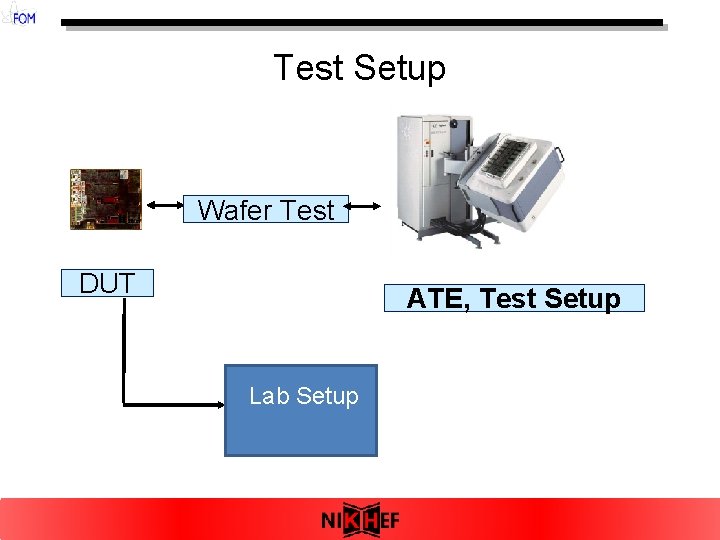

Test Setup Wafer Test DUT ATE, Test Setup Lab Setup

Future Work concerning the test development flow with scan chains • Create the Wrapper around CMD and EOCHL blocks • Run the ATPG at this level • Back-end test development – Link to lab setup – Link to tester vectors running at tester platform (Verigy? Teradyne? Or … ? ) • Mixed-Signal Test

- Slides: 24