Test de Circuitos Integrados Diseo ASIC TEST ndice

- Slides: 69

Test de Circuitos Integrados Diseño ASIC TEST

Índice § I: Introducción al Test de Circuitos Integrados § II: Métodos de Test § III: Design for testability Diseño ASIC TEST

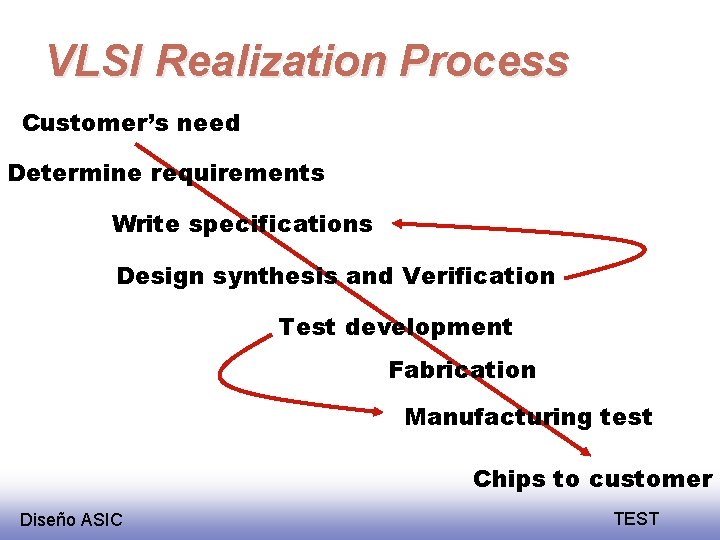

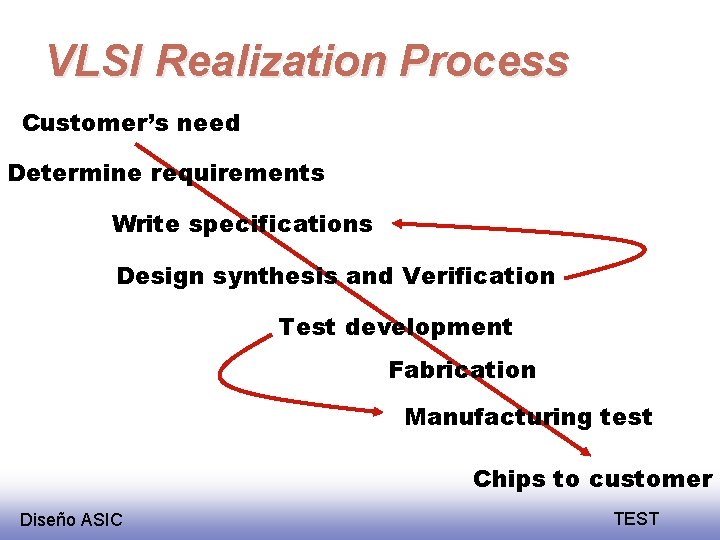

VLSI Realization Process Customer’s need Determine requirements Write specifications Design synthesis and Verification Test development Fabrication Manufacturing test Chips to customer Diseño ASIC TEST

Definitions Design synthesis: Given an I/O function, develop a procedure to manufacture a device using known materials and processes. q Verification: Predictive analysis to ensure that the synthesized design, when manufactured, will perform the given I/O function. q Test: A manufacturing step that ensures that the physical device, manufactured from the synthesized design, has no manufacturing defect. q Diseño ASIC TEST

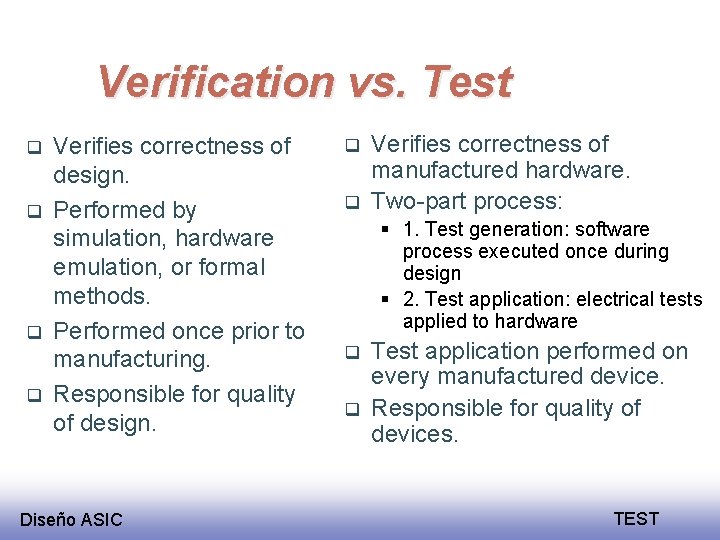

Verification vs. Test q q Verifies correctness of design. Performed by simulation, hardware emulation, or formal methods. Performed once prior to manufacturing. Responsible for quality of design. Diseño ASIC q q Verifies correctness of manufactured hardware. Two-part process: § 1. Test generation: software process executed once during design § 2. Test application: electrical tests applied to hardware q q Test application performed on every manufactured device. Responsible for quality of devices. TEST

Roles of Testing Detection: Determination whether or not the device under test (DUT) has some fault. q Diagnosis: Identification of a specific fault that is present on DUT. q Device characterization: Determination and correction of errors in design and/or test procedure. q Failure mode analysis (FMA): Determination of manufacturing process errors that may have caused defects on the DUT. q Diseño ASIC TEST

Problems of Ideal Tests Ideal tests detect all defects produced in the manufacturing process. q Ideal tests pass all functionally good devices. q Very large numbers and varieties of possible defects need to be tested. q Difficult to generate tests for some real defects. Defect-oriented testing is an open problem. q Diseño ASIC TEST

Real Tests Based on analyzable fault models, which may not map on real defects. q Incomplete coverage of modeled faults due to high complexity. q Some good chips are rejected. The fraction (or percentage) of such chips is called the yield loss. q Some bad chips pass tests. The fraction (or percentage) of bad chips among all passing chips is called the defect level. q Diseño ASIC TEST

Types of Testing q Verification testing, characterization testing, or design debug § Verifies correctness of design and of test procedure – usually requires correction to design q Manufacturing testing § Factory testing of all manufactured chips for parametric faults and for random defects q Acceptance testing (incoming inspection) § User (customer) tests purchased parts to ensure quality Diseño ASIC TEST

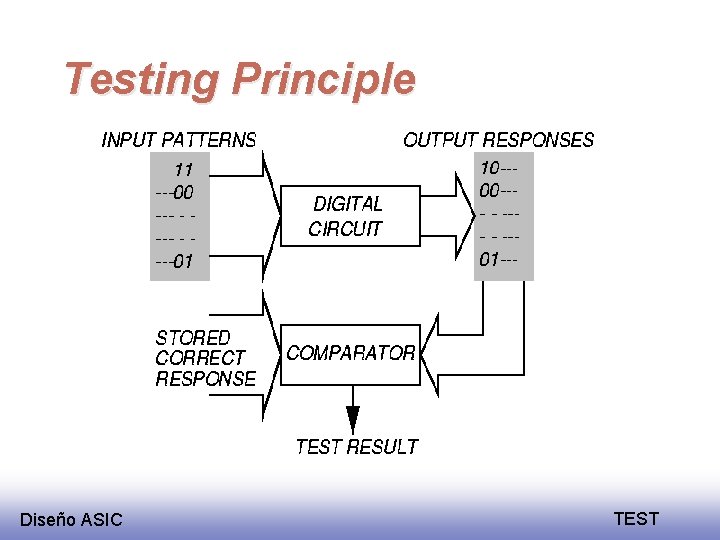

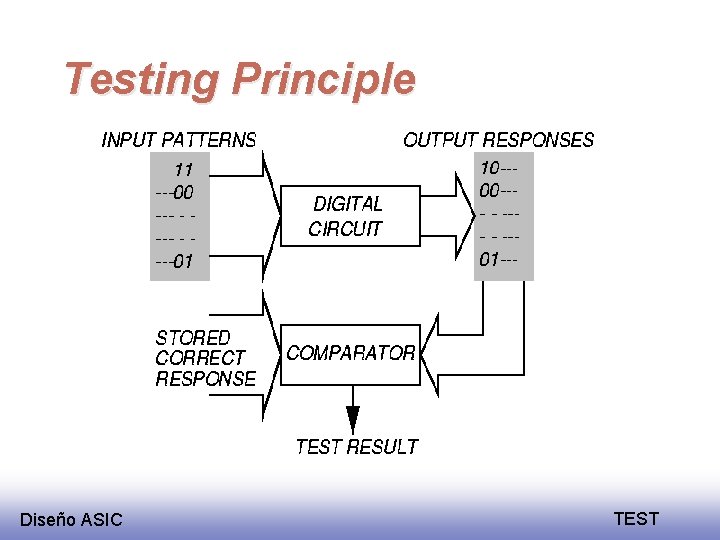

Testing Principle Diseño ASIC TEST

Manufacturing Test Determines whether manufactured chip meets specs q Must cover high % of modeled faults q Must minimize test time (to control cost) q No fault diagnosis q Tests every device on chip q Test at speed of application or speed guaranteed by supplier q Diseño ASIC TEST

Types of Manufacturing Tests q Wafer sort or probe test – done before wafer is scribed and cut into chips § Includes test site characterization – specific test devices are checked with specific patterns to measure: – Gate threshold – Polysilicon field threshold – Poly sheet resistance, etc. q Packaged device tests Diseño ASIC TEST

Sub-types of Tests Parametric – measures electrical properties of pin electronics – delay, voltages, currents, etc. – fast and cheap q Functional – used to cover very high % of modeled faults – test every transistor and wire in digital circuits – long and expensive q Diseño ASIC TEST

Two Different Meanings of Functional Test ATE and Manufacturing World – any vectors applied to cover high % of faults during manufacturing test q Automatic Test-Pattern Generation World – testing with verification vectors, which determine whether hardware matches its specification – typically have low fault coverage (< 70 %) q Diseño ASIC TEST

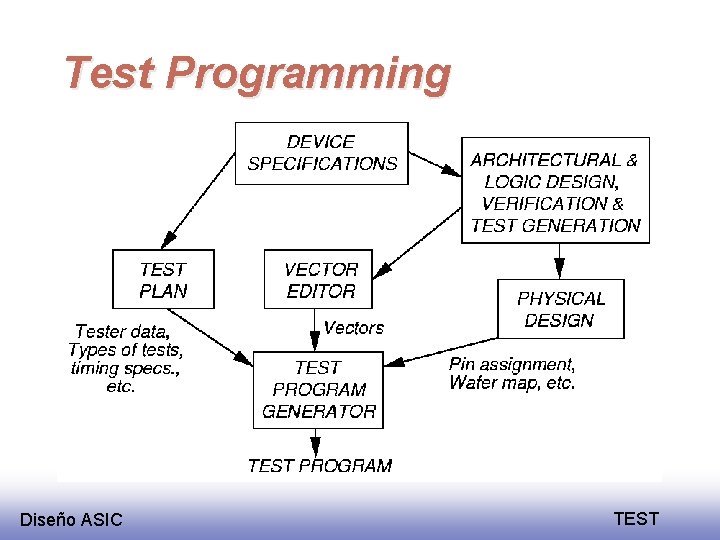

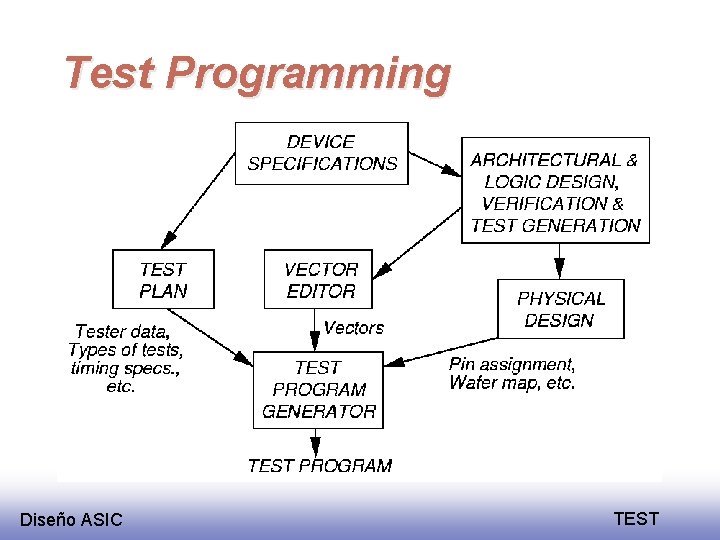

Test Programming Diseño ASIC TEST

Automatic Test Equipment (ATE) Diseño ASIC TEST

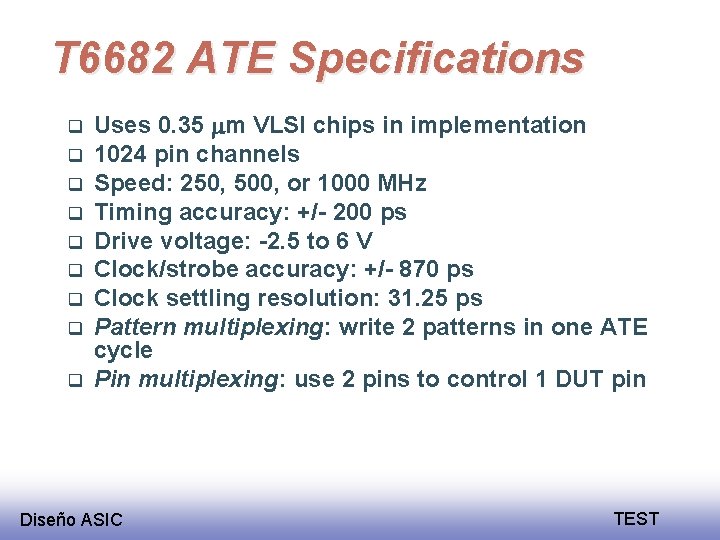

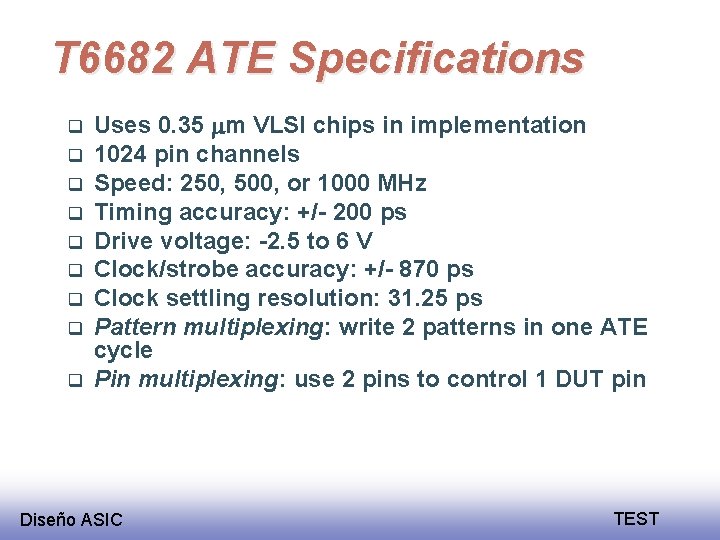

T 6682 ATE Specifications q q q q q Uses 0. 35 mm VLSI chips in implementation 1024 pin channels Speed: 250, 500, or 1000 MHz Timing accuracy: +/- 200 ps Drive voltage: -2. 5 to 6 V Clock/strobe accuracy: +/- 870 ps Clock settling resolution: 31. 25 ps Pattern multiplexing: write 2 patterns in one ATE cycle Pin multiplexing: use 2 pins to control 1 DUT pin Diseño ASIC TEST

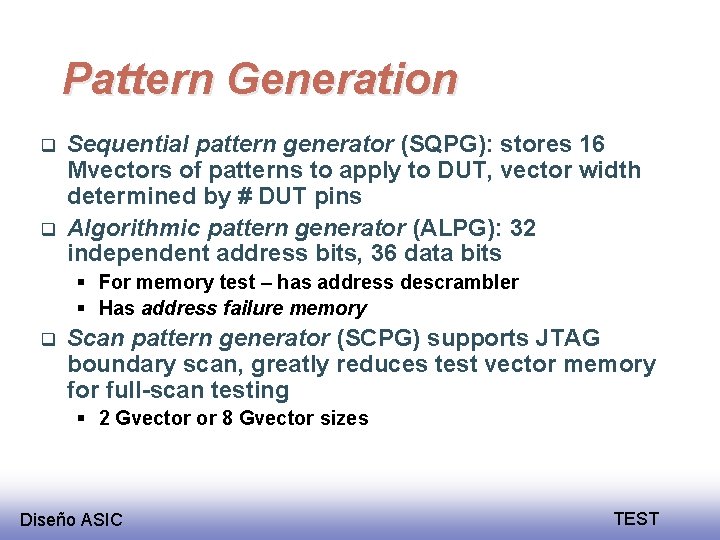

Pattern Generation q q Sequential pattern generator (SQPG): stores 16 Mvectors of patterns to apply to DUT, vector width determined by # DUT pins Algorithmic pattern generator (ALPG): 32 independent address bits, 36 data bits § For memory test – has address descrambler § Has address failure memory q Scan pattern generator (SCPG) supports JTAG boundary scan, greatly reduces test vector memory for full-scan testing § 2 Gvector or 8 Gvector sizes Diseño ASIC TEST

Fault Modeling Why model faults? q Some real defects in VLSI and PCB q Common fault models q Stuck-at faults q – – q Single stuck-at faults Fault equivalence Fault dominance and checkpoint theorem Classes of stuck-at faults and multiple faults Transistor faults Diseño ASIC TEST

Some Real Defects in Chips § Processing defects § § Missing contact windows Parasitic transistors Oxide breakdown. . . § Material defects § Bulk defects (cracks, crystal imperfections) § Surface impurities (ion migration) §. . . § Time-dependent failures § Dielectric breakdown § Electromigration §. . . § Packaging failures § Contact degradation § Seal leaks §. . . Diseño ASIC TEST

Common Fault Models Single stuck-at faults q Transistor open and short faults q Memory faults q PLA faults (stuck-at, cross-point, bridging) q Functional faults (processors) q Delay faults (transition, path) q Analog faults q Diseño ASIC TEST

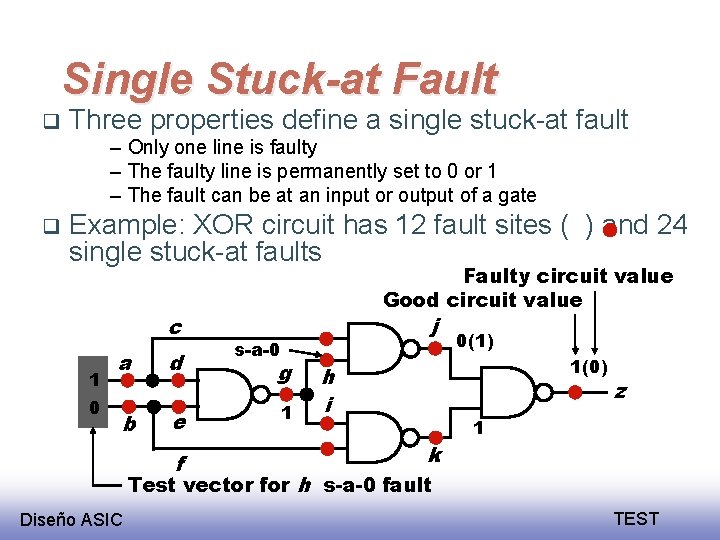

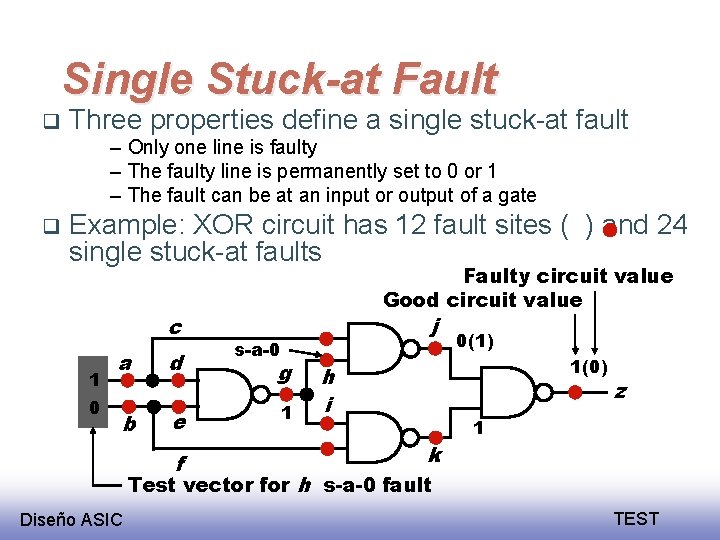

Single Stuck-at Fault q Three properties define a single stuck-at fault – Only one line is faulty – The faulty line is permanently set to 0 or 1 – The fault can be at an input or output of a gate q Example: XOR circuit has 12 fault sites ( ) and 24 single stuck-at faults c 1 0 a d b e f Faulty circuit value Good circuit value j s-a-0 g 1 0(1) 1(0) h i k z 1 Test vector for h s-a-0 fault Diseño ASIC TEST

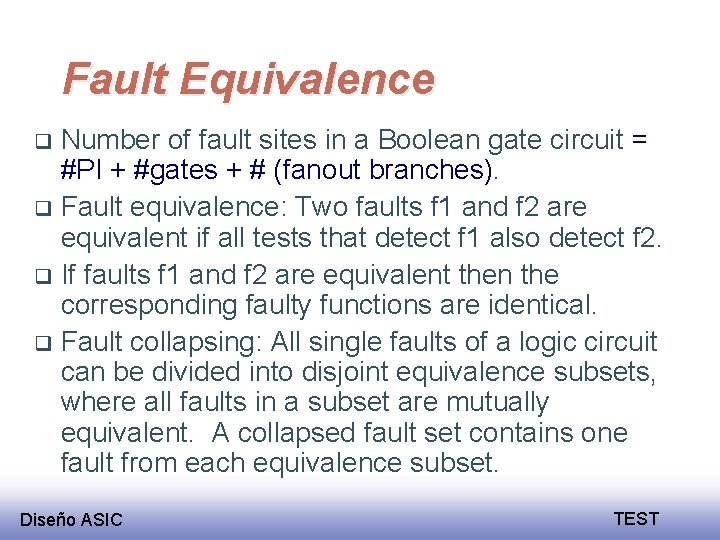

Fault Equivalence Number of fault sites in a Boolean gate circuit = #PI + #gates + # (fanout branches). q Fault equivalence: Two faults f 1 and f 2 are equivalent if all tests that detect f 1 also detect f 2. q If faults f 1 and f 2 are equivalent then the corresponding faulty functions are identical. q Fault collapsing: All single faults of a logic circuit can be divided into disjoint equivalence subsets, where all faults in a subset are mutually equivalent. A collapsed fault set contains one fault from each equivalence subset. q Diseño ASIC TEST

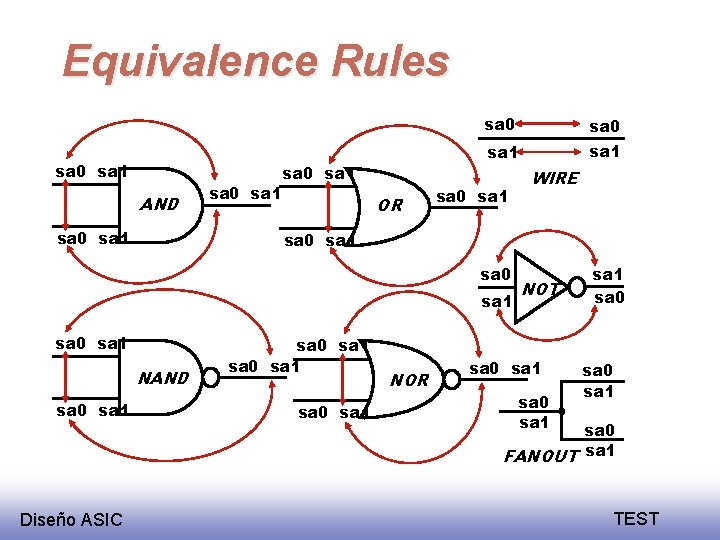

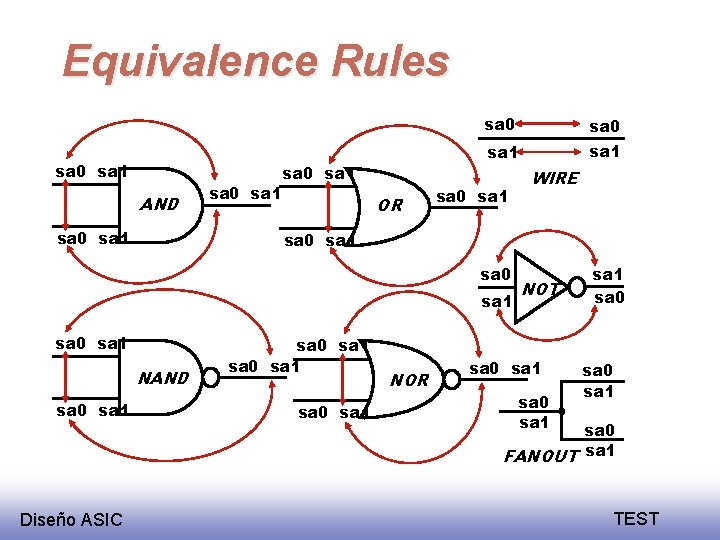

Equivalence Rules sa 0 sa 1 AND sa 0 sa 1 OR sa 0 sa 1 sa 0 sa 1 NAND sa 0 sa 1 Diseño ASIC WIRE sa 0 sa 1 NOR NOT sa 0 sa 1 sa 0 sa 1 sa 0 FANOUT sa 1 TEST

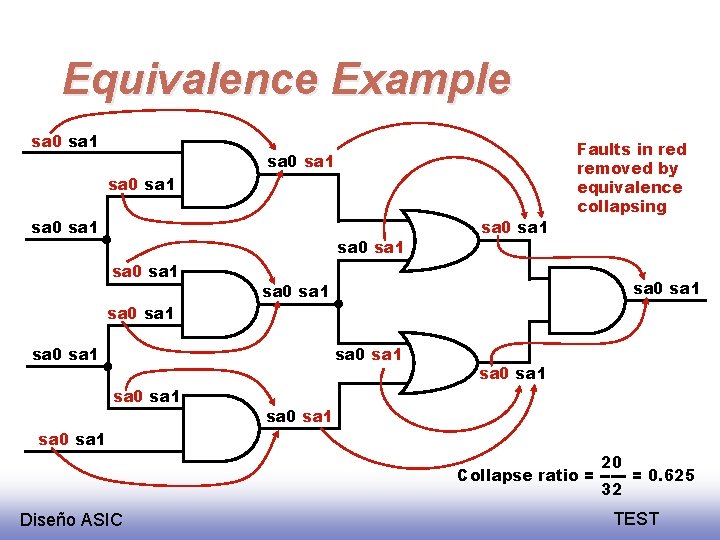

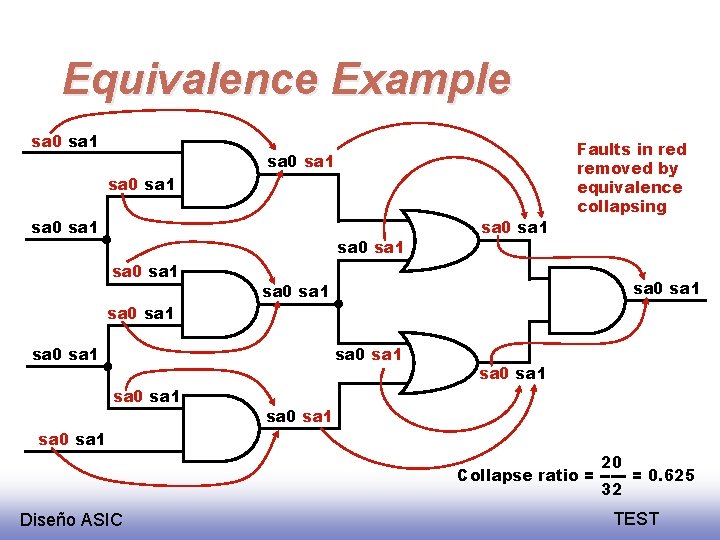

Equivalence Example sa 0 sa 1 sa 0 sa 1 sa 0 sa 1 sa 0 sa 1 Diseño ASIC sa 0 sa 1 Faults in red removed by equivalence collapsing sa 0 sa 1 20 Collapse ratio = ----- = 0. 625 32 TEST

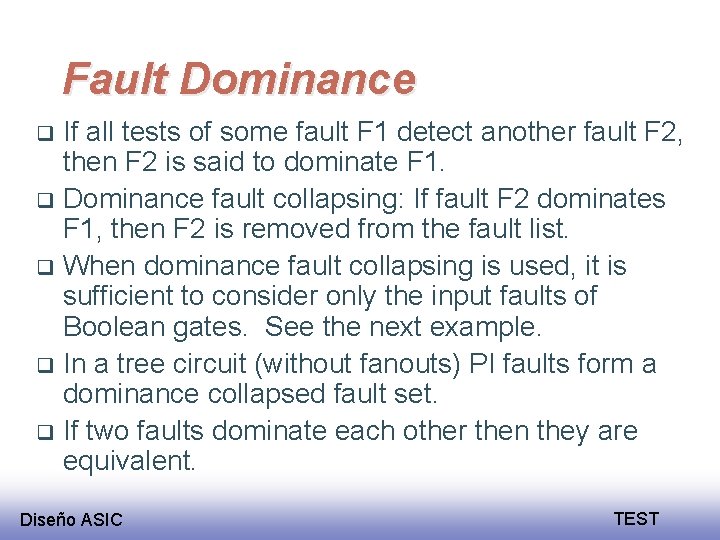

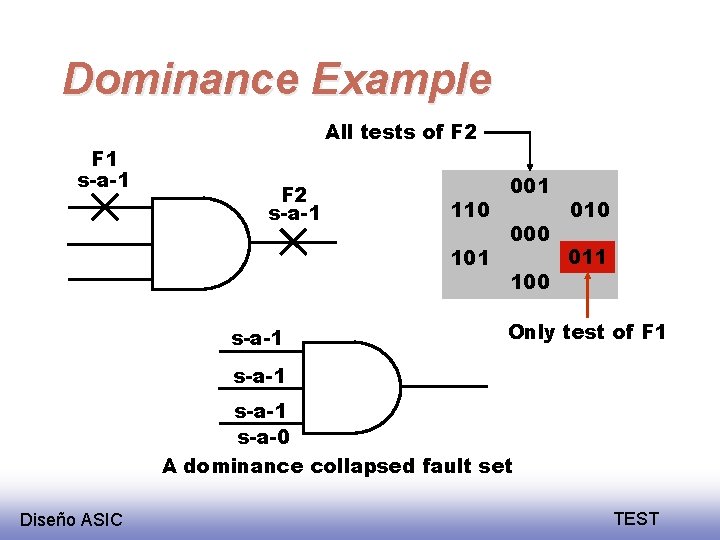

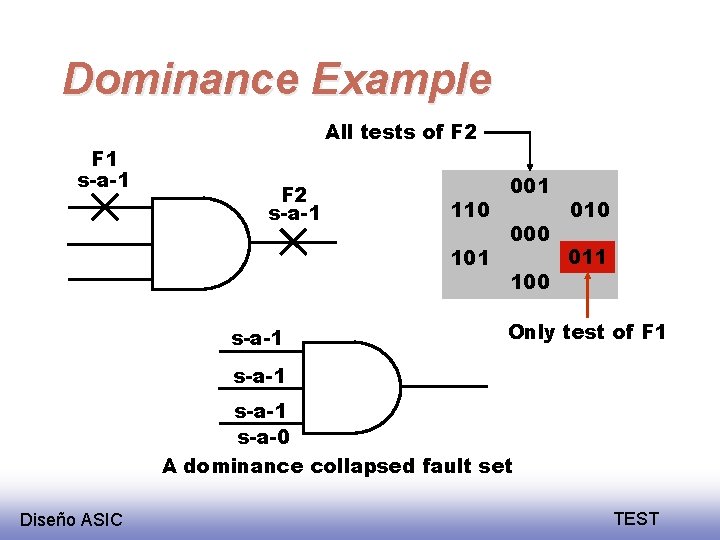

Fault Dominance If all tests of some fault F 1 detect another fault F 2, then F 2 is said to dominate F 1. q Dominance fault collapsing: If fault F 2 dominates F 1, then F 2 is removed from the fault list. q When dominance fault collapsing is used, it is sufficient to consider only the input faults of Boolean gates. See the next example. q In a tree circuit (without fanouts) PI faults form a dominance collapsed fault set. q If two faults dominate each other then they are equivalent. q Diseño ASIC TEST

Dominance Example F 1 s-a-1 All tests of F 2 s-a-1 110 101 s-a-1 000 100 011 Only test of F 1 s-a-1 s-a-0 A dominance collapsed fault set Diseño ASIC TEST

Checkpoints Primary inputs and fanout branches of a combinational circuit are called checkpoints. q Checkpoint theorem: A test set that detects all single (multiple) stuck-at faults on all checkpoints of a combinational circuit, also detects all single (multiple) stuck-at faults in that circuit. q Total fault sites = 16 Checkpoints ( ) = 10 Diseño ASIC TEST

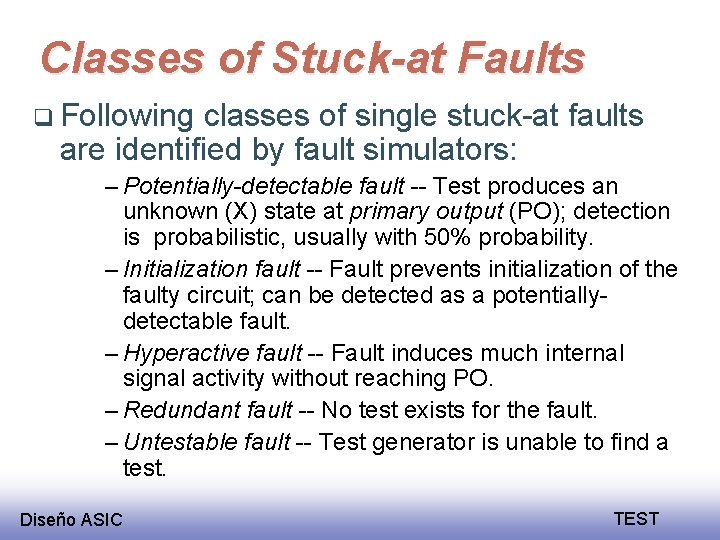

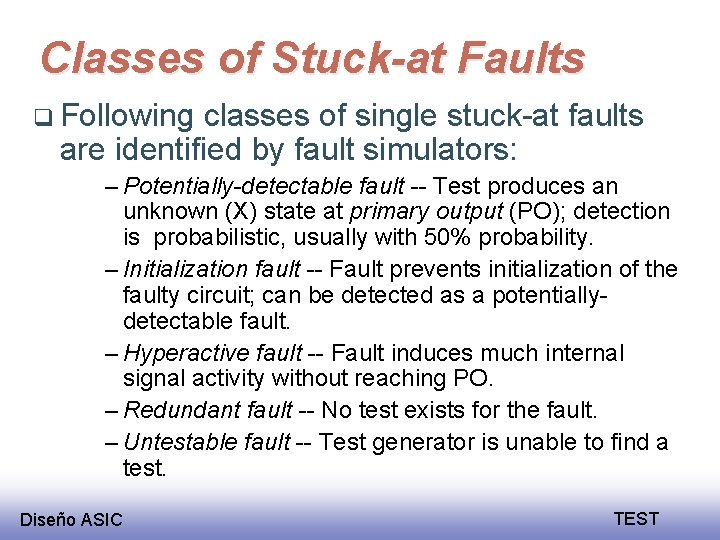

Classes of Stuck-at Faults q Following classes of single stuck-at faults are identified by fault simulators: – Potentially-detectable fault -- Test produces an unknown (X) state at primary output (PO); detection is probabilistic, usually with 50% probability. – Initialization fault -- Fault prevents initialization of the faulty circuit; can be detected as a potentiallydetectable fault. – Hyperactive fault -- Fault induces much internal signal activity without reaching PO. – Redundant fault -- No test exists for the fault. – Untestable fault -- Test generator is unable to find a test. Diseño ASIC TEST

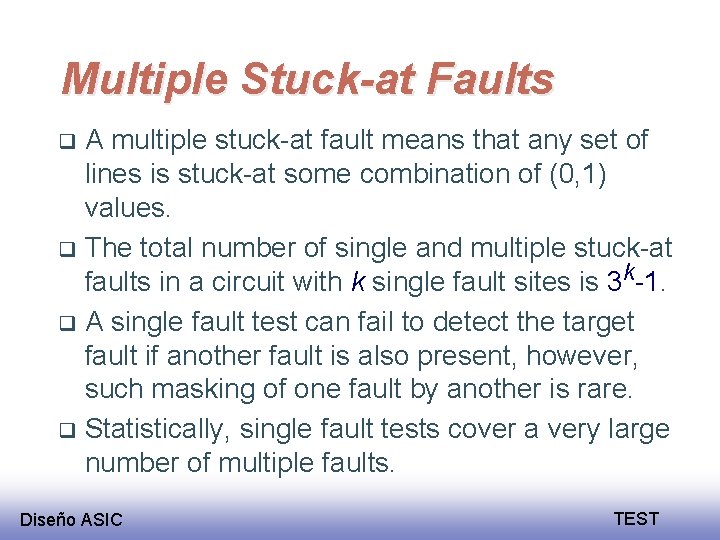

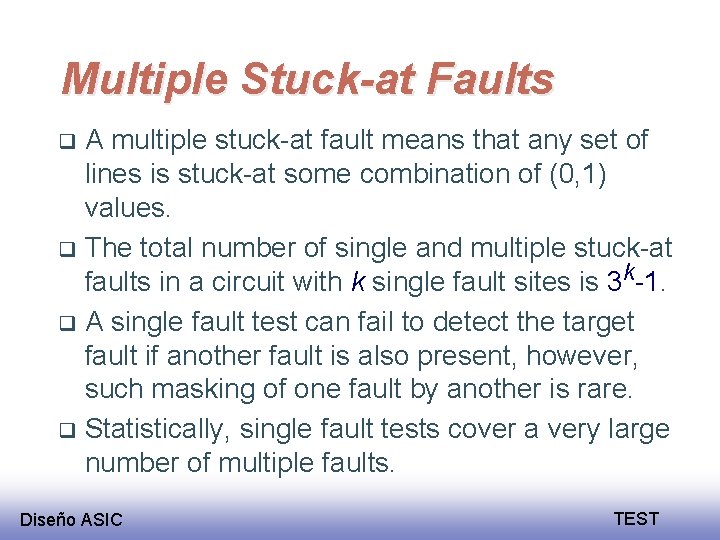

Multiple Stuck-at Faults A multiple stuck-at fault means that any set of lines is stuck-at some combination of (0, 1) values. q The total number of single and multiple stuck-at faults in a circuit with k single fault sites is 3 k-1. q A single fault test can fail to detect the target fault if another fault is also present, however, such masking of one fault by another is rare. q Statistically, single fault tests cover a very large number of multiple faults. q Diseño ASIC TEST

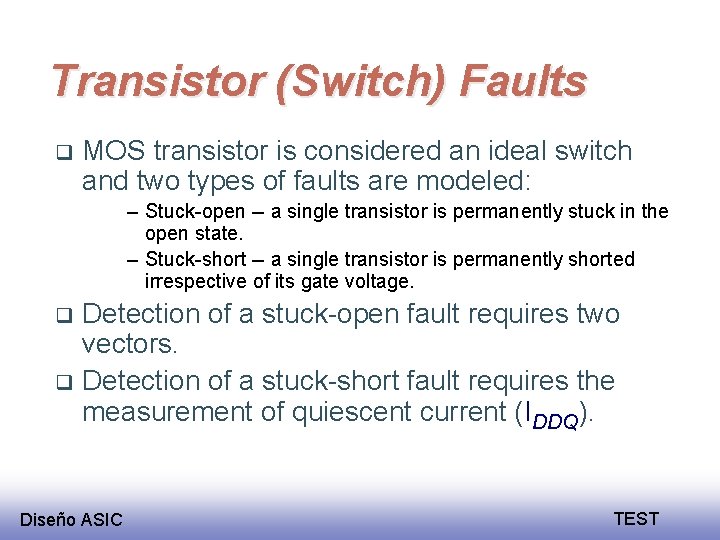

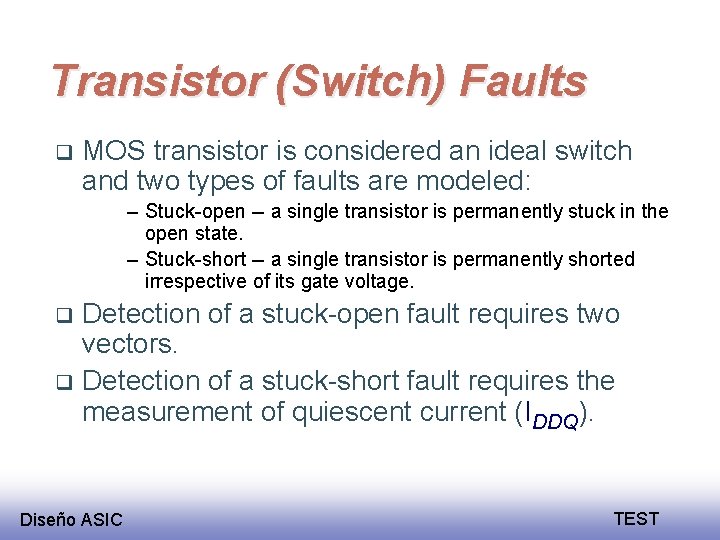

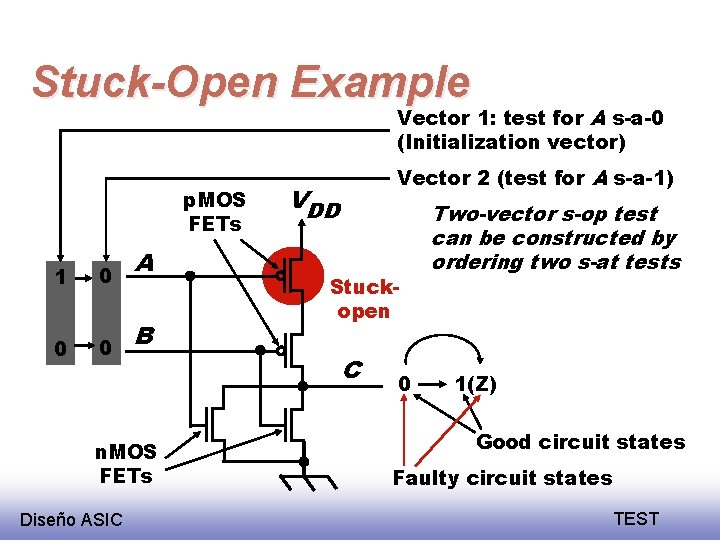

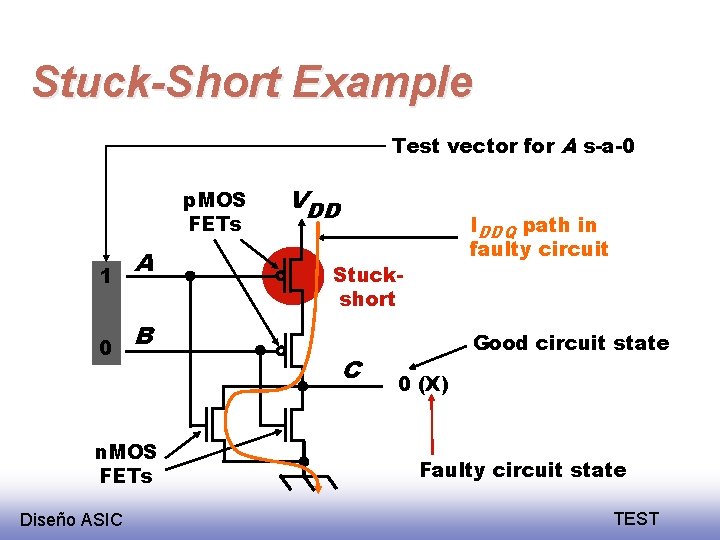

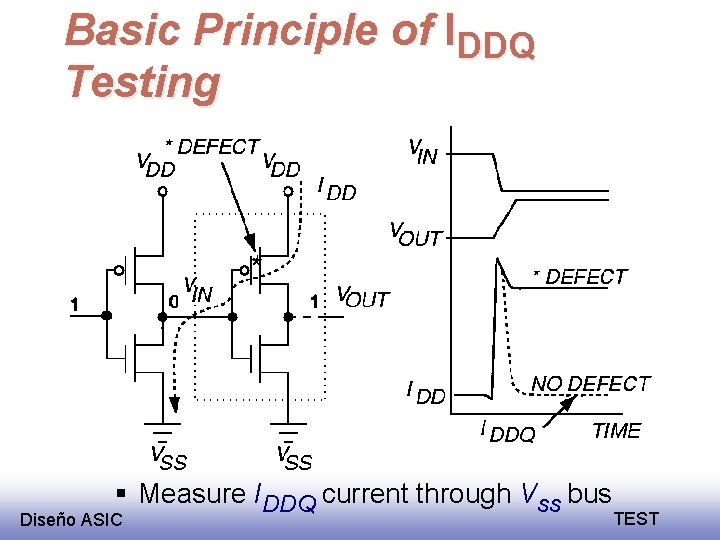

Transistor (Switch) Faults q MOS transistor is considered an ideal switch and two types of faults are modeled: – Stuck-open -- a single transistor is permanently stuck in the open state. – Stuck-short -- a single transistor is permanently shorted irrespective of its gate voltage. Detection of a stuck-open fault requires two vectors. q Detection of a stuck-short fault requires the measurement of quiescent current (IDDQ). q Diseño ASIC TEST

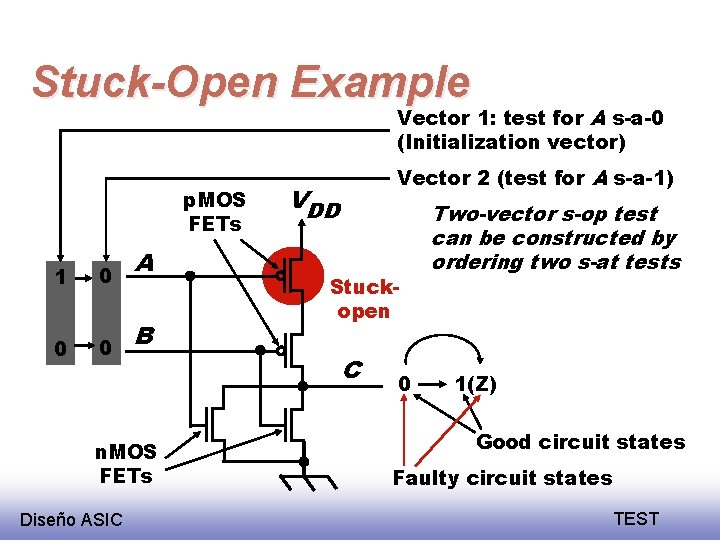

Stuck-Open Example Vector 1: test for A s-a-0 (Initialization vector) p. MOS FETs 1 0 0 0 A B n. MOS FETs Diseño ASIC Vector 2 (test for A s-a-1) VDD Stuckopen C 0 Two-vector s-op test can be constructed by ordering two s-at tests 1(Z) Good circuit states Faulty circuit states TEST

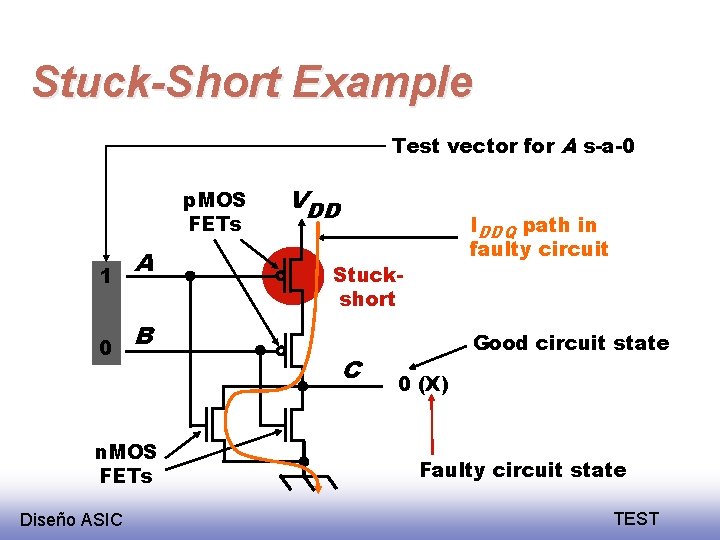

Stuck-Short Example Test vector for A s-a-0 p. MOS FETs 1 0 A B n. MOS FETs Diseño ASIC VDD IDDQ path in faulty circuit Stuckshort C Good circuit state 0 (X) Faulty circuit state TEST

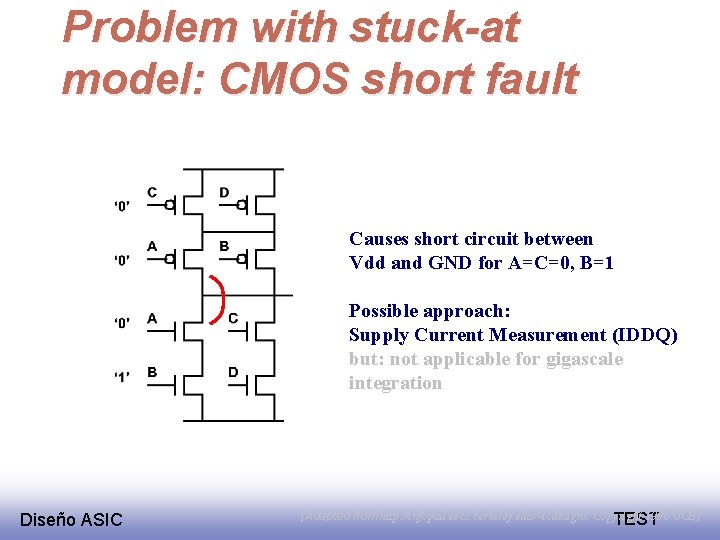

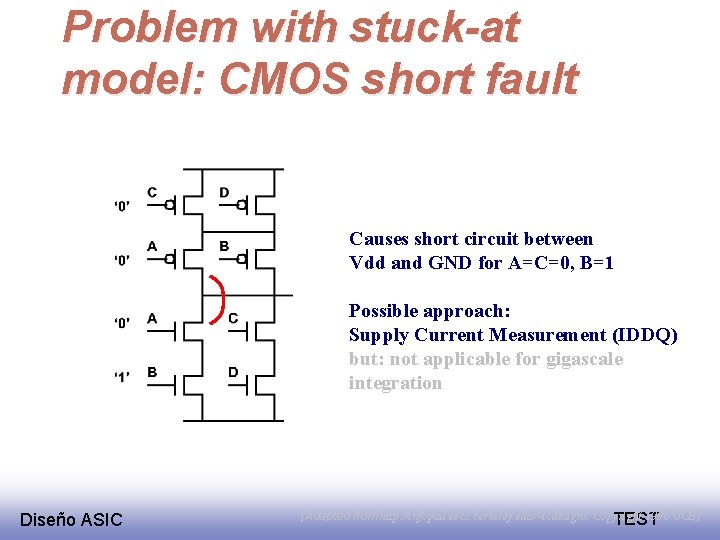

Problem with stuck-at model: CMOS short fault Causes short circuit between Vdd and GND for A=C=0, B=1 Possible approach: Supply Current Measurement (IDDQ) but: not applicable for gigascale integration Diseño ASIC [Adapted from http: //infopad. eecs. berkeley. edu/~icdesign/. Copyright 1996 UCB] TEST

Fault Simulation q Problem and motivation q Fault simulation algorithms – Serial – Parallel – Deductive – Concurrent q Random Diseño ASIC Fault Sampling TEST

Problem and Motivation q Fault simulation Problem: Given § A circuit § A sequence of test vectors § A fault model § Determine § Fault coverage - fraction (or percentage) of modeled faults detected by test vectors § Set of undetected faults q Motivation § Determine test quality and in turn product quality § Find undetected fault targets to improve tests Diseño ASIC TEST

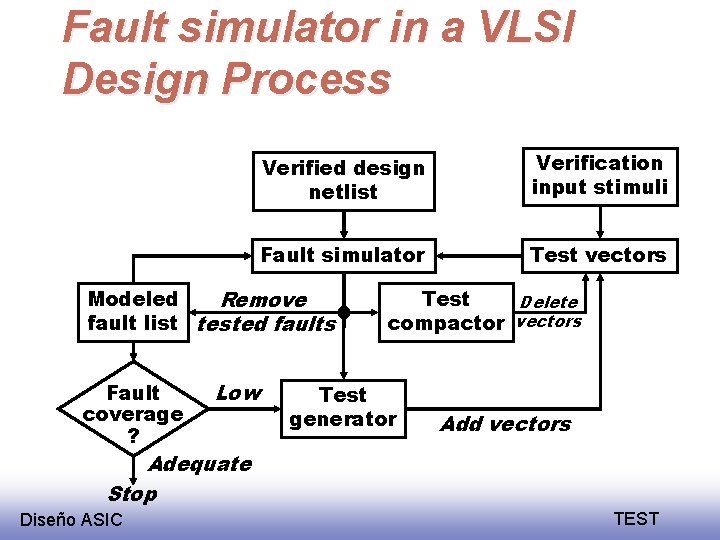

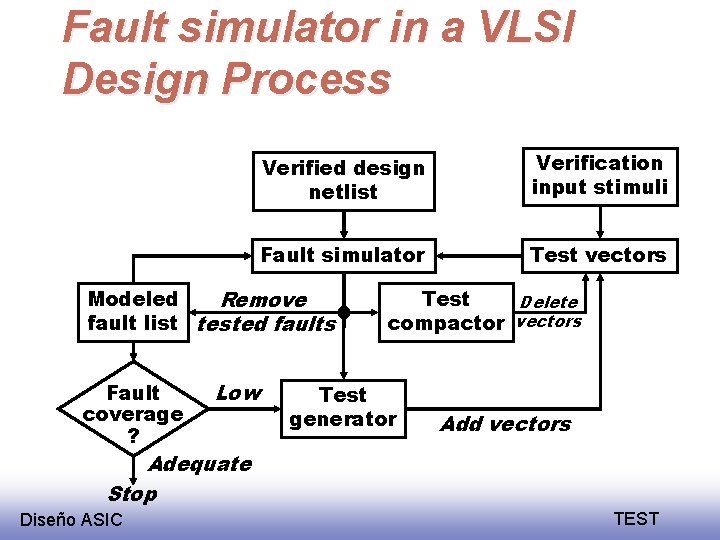

Fault simulator in a VLSI Design Process Verified design netlist Verification input stimuli Fault simulator Test vectors Modeled Remove fault list tested faults Fault coverage ? Low Test Delete compactor vectors Test generator Add vectors Adequate Stop Diseño ASIC TEST

Fault Simulation Scenario q Circuit model: mixed-level – Mostly logic with some switch-level for high-impedance (Z) and bidirectional signals – High-level models (memory, etc. ) with pin faults q Signal states: logic – Two (0, 1) or three (0, 1, X) states for purely Boolean logic circuits – Four states (0, 1, X, Z) for sequential MOS circuits q Timing: – Zero-delay for combinational and synchronous circuits – Mostly unit-delay for circuits with feedback Diseño ASIC TEST

Fault Simulation Scenario (continued) q Faults: – Mostly single stuck-at faults – Sometimes stuck-open, transition, and path-delay faults; analog circuit fault simulators are not yet in common use – Equivalence fault collapsing of single stuck-at faults – Fault-dropping -- a fault once detected is dropped from consideration as more vectors are simulated; fault-dropping may be suppressed for diagnosis – Fault sampling -- a random sample of faults is simulated when the circuit is large Diseño ASIC TEST

Fault Simulation Algorithms q Serial q Parallel q Deductive q Concurrent q Differential Diseño ASIC TEST

Serial Algorithm q Algorithm: Simulate fault-free circuit and save responses. Repeat following steps for each fault in the fault list: – Modify netlist by injecting one fault – Simulate modified netlist, vector by vector, comparing responses with saved responses – If response differs, report fault detection and suspend simulation of remaining vectors q Advantages: – Easy to implement; needs only a true-value simulator, less memory – Most faults, including analog faults, can be simulated Diseño ASIC TEST

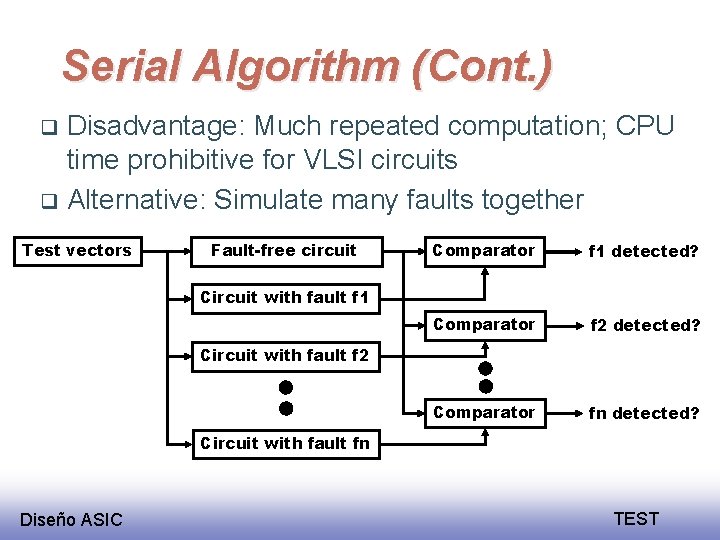

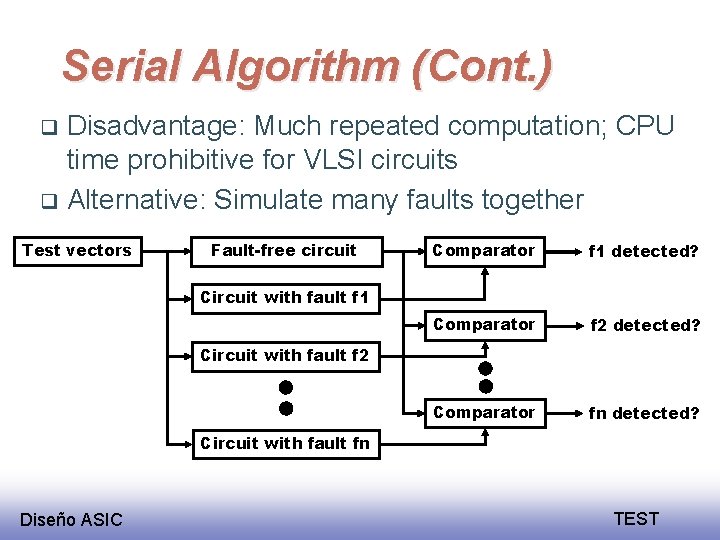

Serial Algorithm (Cont. ) Disadvantage: Much repeated computation; CPU time prohibitive for VLSI circuits q Alternative: Simulate many faults together q Test vectors Fault-free circuit Comparator f 1 detected? Comparator f 2 detected? Comparator fn detected? Circuit with fault f 1 Circuit with fault f 2 Circuit with fault fn Diseño ASIC TEST

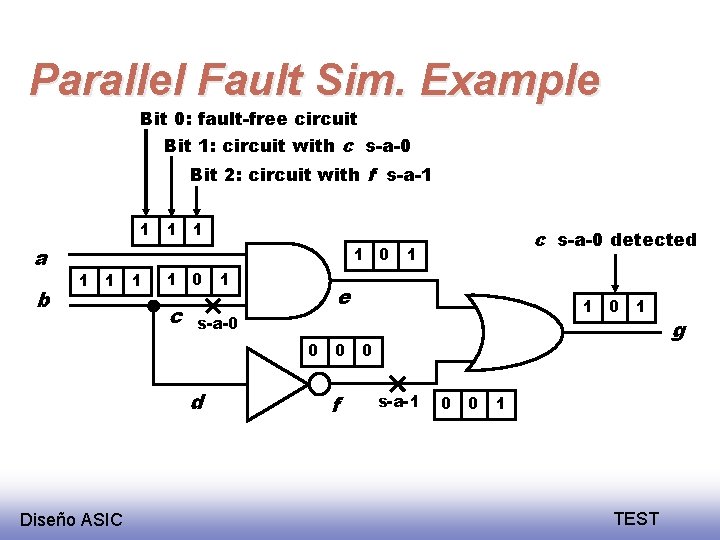

Parallel Fault Simulation Compiled-code method; best with two-states (0, 1) q Exploits inherent bit-parallelism of logic operations on computer words q Storage: one word per line for two-state simulation q Multi-pass simulation: Each pass simulates w 1 new faults, where w is the machine word length q Speed up over serial method ~ w-1 q Not suitable for circuits with timing-critical and non-Boolean logic q Diseño ASIC TEST

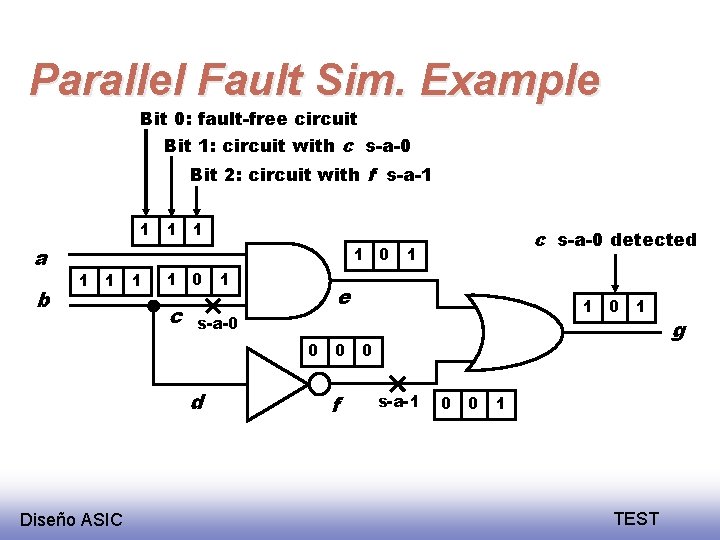

Parallel Fault Sim. Example Bit 0: fault-free circuit Bit 1: circuit with c s-a-0 Bit 2: circuit with f s-a-1 1 a b c s-a-0 detected 1 0 1 1 1 0 1 c e 1 0 1 s-a-0 0 d Diseño ASIC f s-a-1 0 0 1 TEST g

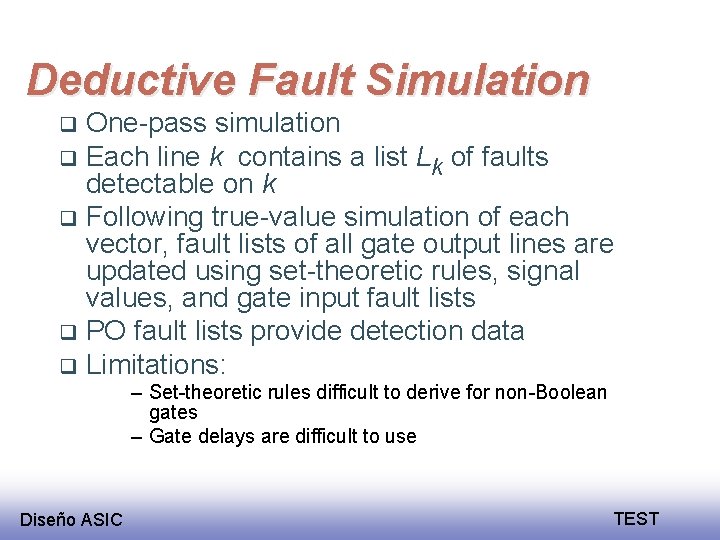

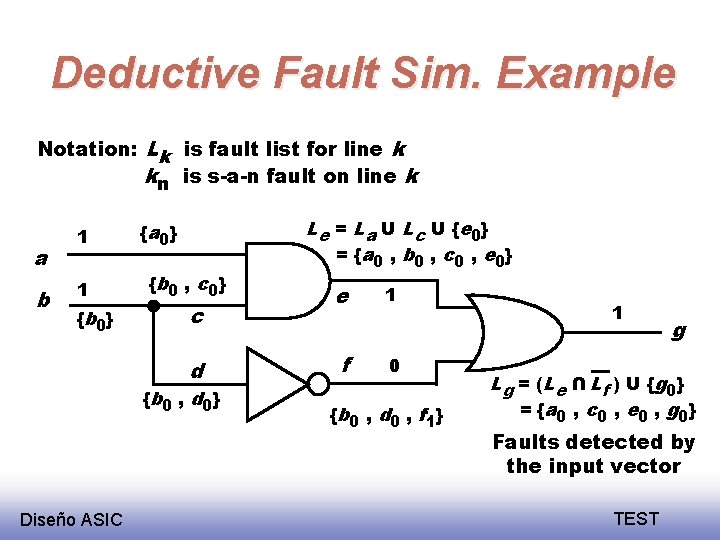

Deductive Fault Simulation One-pass simulation q Each line k contains a list Lk of faults detectable on k q Following true-value simulation of each vector, fault lists of all gate output lines are updated using set-theoretic rules, signal values, and gate input fault lists q PO fault lists provide detection data q Limitations: q – Set-theoretic rules difficult to derive for non-Boolean gates – Gate delays are difficult to use Diseño ASIC TEST

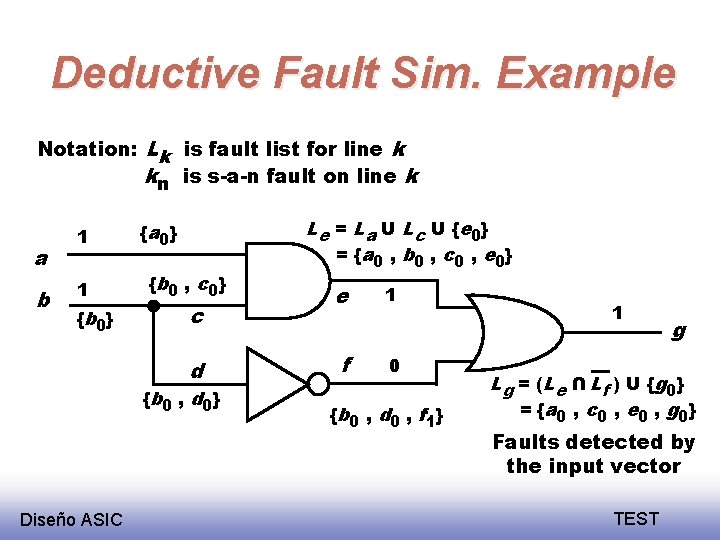

Deductive Fault Sim. Example Notation: Lk is fault list for line k kn is s-a-n fault on line k b 1 {b 0 } {a 0 } {b 0 , c 0 } c d {b 0 , d 0 } Diseño ASIC Le = La U Lc U { e 0} = { a 0 , b 0 , c 0 , e 0} e f 1 0 {b 0 , d 0 , f 1 } 1 g Lg = ( Le Lf ) U { g 0} = { a 0 , c 0 , e 0 , g 0} Faults detected by the input vector U a 1 TEST

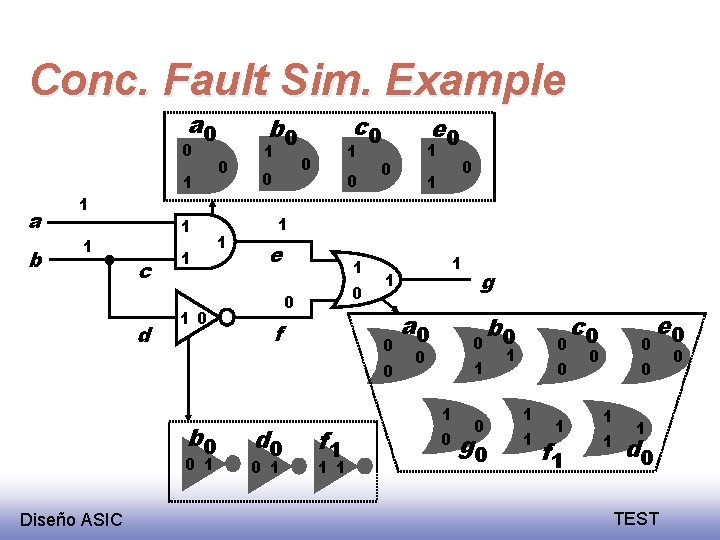

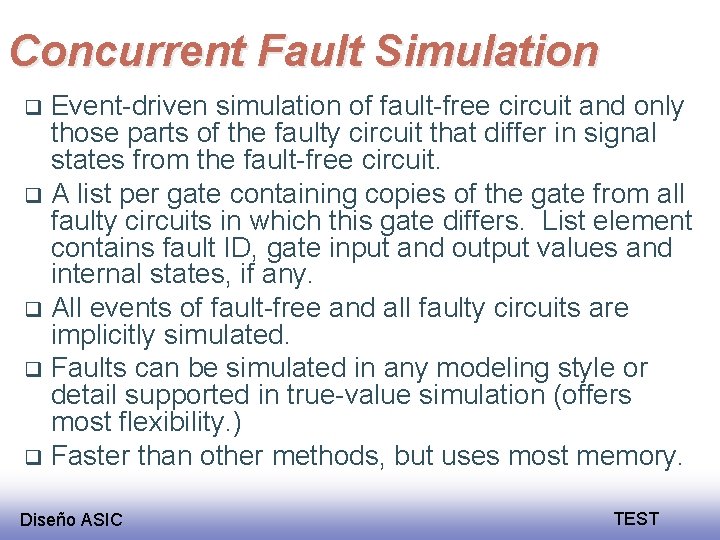

Concurrent Fault Simulation Event-driven simulation of fault-free circuit and only those parts of the faulty circuit that differ in signal states from the fault-free circuit. q A list per gate containing copies of the gate from all faulty circuits in which this gate differs. List element contains fault ID, gate input and output values and internal states, if any. q All events of fault-free and all faulty circuits are implicitly simulated. q Faults can be simulated in any modeling style or detail supported in true-value simulation (offers most flexibility. ) q Faster than other methods, but uses most memory. q Diseño ASIC TEST

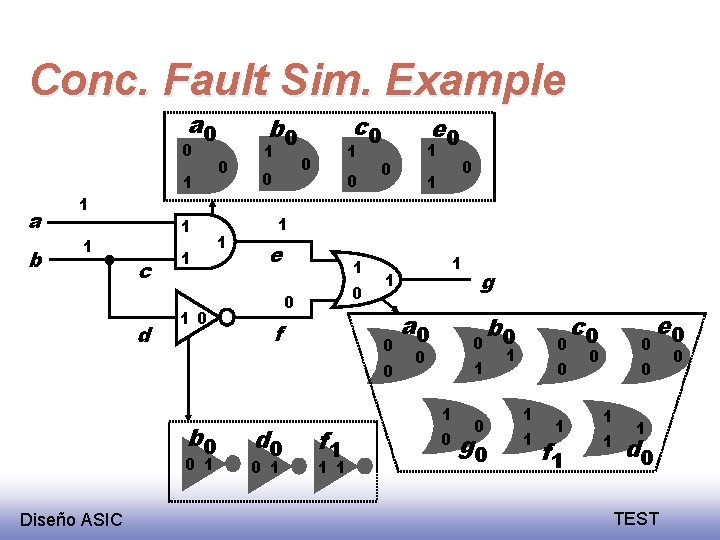

Conc. Fault Sim. Example a 0 0 a b 1 1 0 1 1 c d 1 1 1 0 c 0 b 0 1 1 0 0 0 e 0 0 0 1 Diseño ASIC 0 1 1 e 1 0 0 f d 0 0 0 1 f 1 1 1 0 b 0 1 a 0 0 1 0 g b 0 0 0 1 0 0 g 0 1 1 f 1 c 0 0 0 e 0 0 1 1 1 d 0 TEST 0

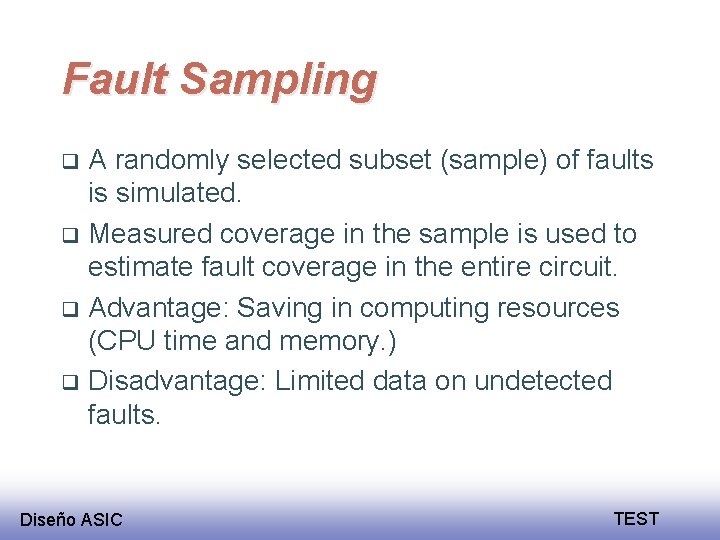

Fault Sampling A randomly selected subset (sample) of faults is simulated. q Measured coverage in the sample is used to estimate fault coverage in the entire circuit. q Advantage: Saving in computing resources (CPU time and memory. ) q Disadvantage: Limited data on undetected faults. q Diseño ASIC TEST

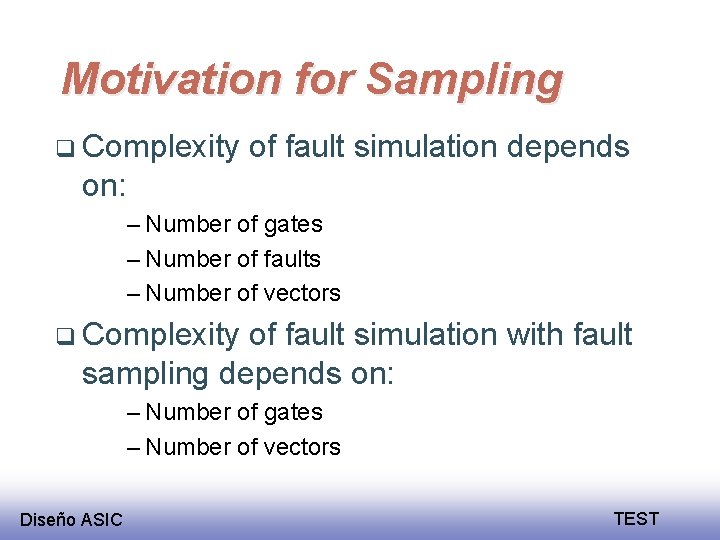

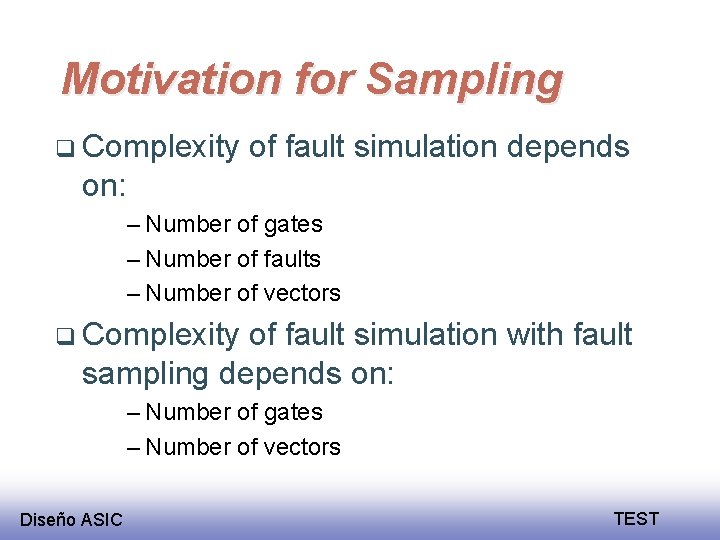

Motivation for Sampling q Complexity of fault simulation depends on: – Number of gates – Number of faults – Number of vectors q Complexity of fault simulation with fault sampling depends on: – Number of gates – Number of vectors Diseño ASIC TEST

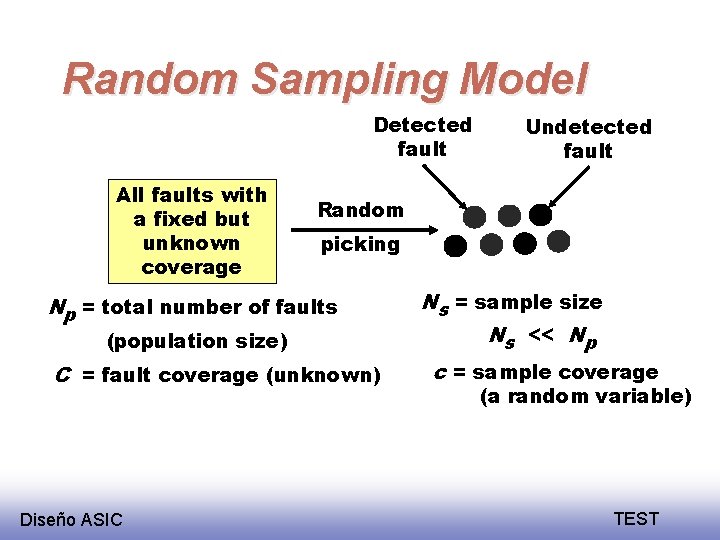

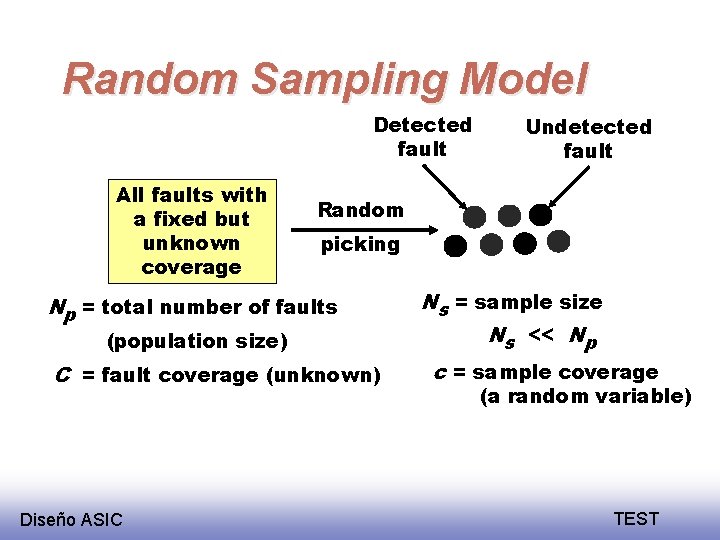

Random Sampling Model Detected fault All faults with a fixed but unknown coverage Random picking Np = total number of faults (population size) C = fault coverage (unknown) Diseño ASIC Undetected fault Ns = sample size Ns << Np c = sample coverage (a random variable) TEST

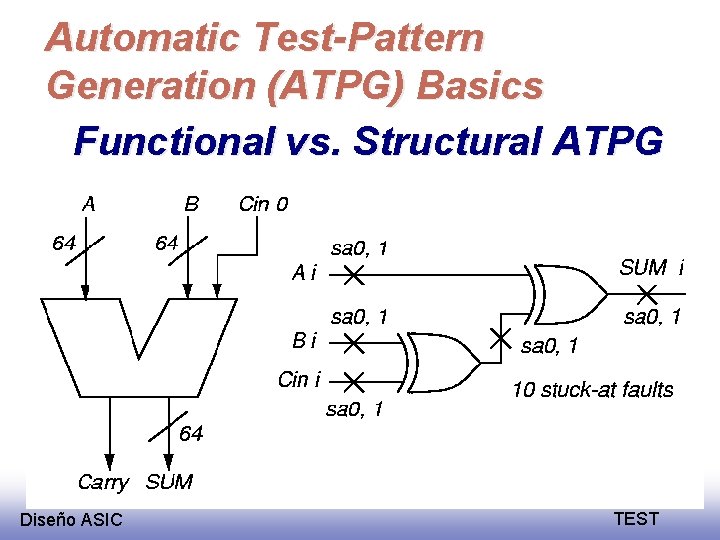

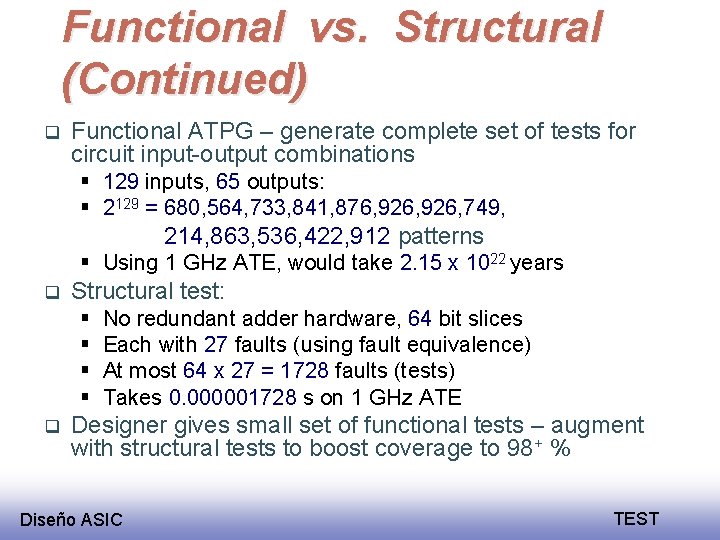

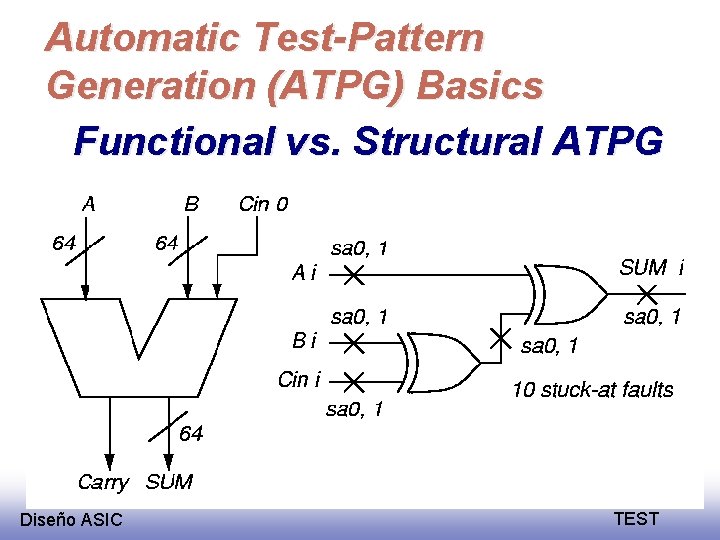

Automatic Test-Pattern Generation (ATPG) Basics Functional vs. Structural ATPG Diseño ASIC TEST

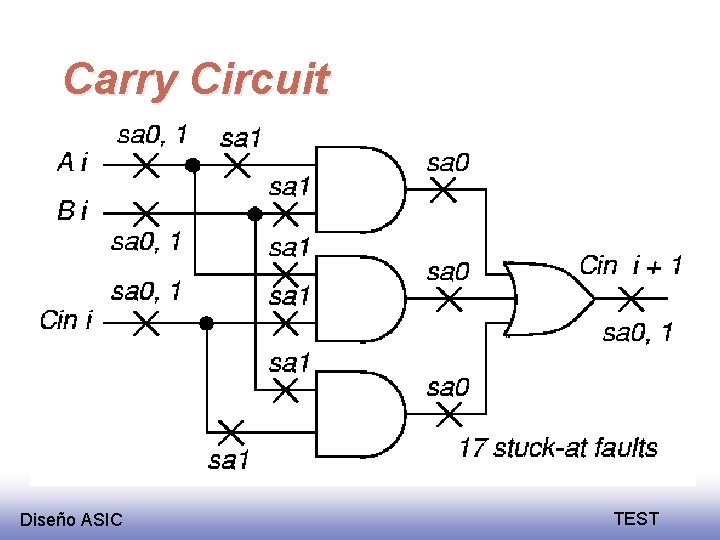

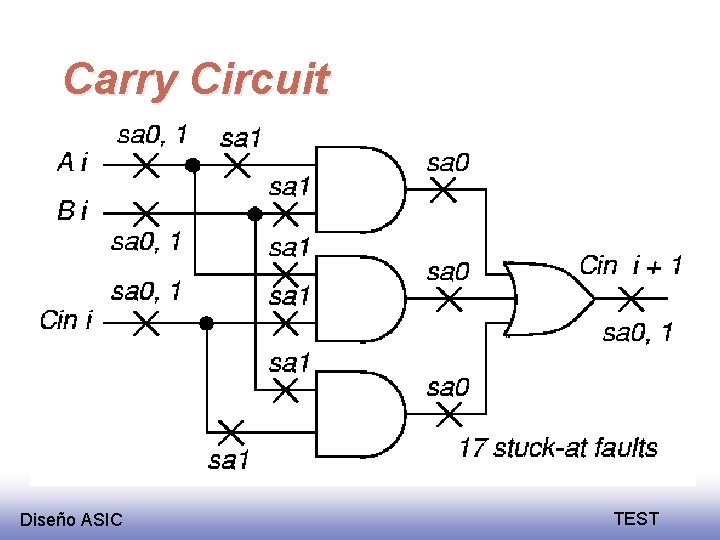

Carry Circuit Diseño ASIC TEST

Functional vs. Structural (Continued) q Functional ATPG – generate complete set of tests for circuit input-output combinations § 129 inputs, 65 outputs: § 2129 = 680, 564, 733, 841, 876, 926, 749, 214, 863, 536, 422, 912 patterns § Using 1 GHz ATE, would take 2. 15 x 1022 years q Structural test: § § q No redundant adder hardware, 64 bit slices Each with 27 faults (using fault equivalence) At most 64 x 27 = 1728 faults (tests) Takes 0. 000001728 s on 1 GHz ATE Designer gives small set of functional tests – augment with structural tests to boost coverage to 98+ % Diseño ASIC TEST

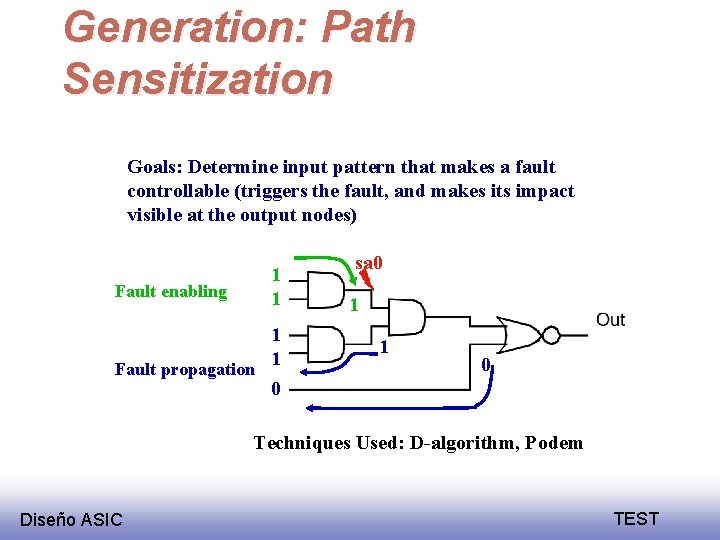

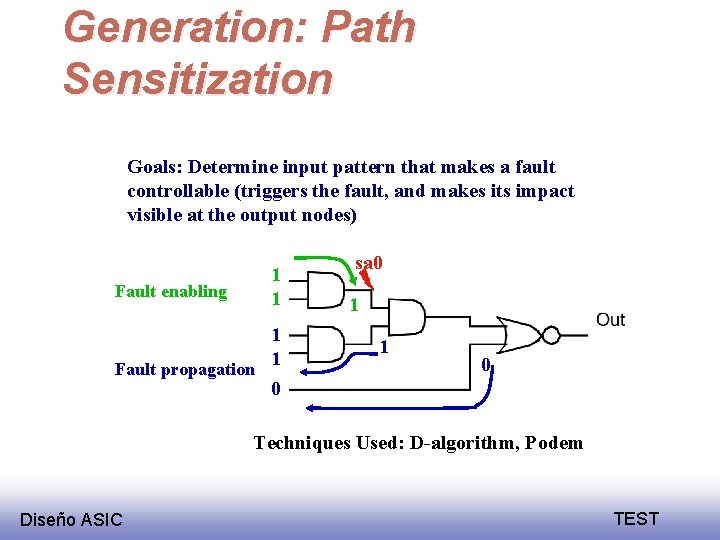

Generation: Path Sensitization Goals: Determine input pattern that makes a fault controllable (triggers the fault, and makes its impact visible at the output nodes) Fault enabling 1 1 Fault propagation 0 sa 0 1 1 0 Techniques Used: D-algorithm, Podem Diseño ASIC TEST

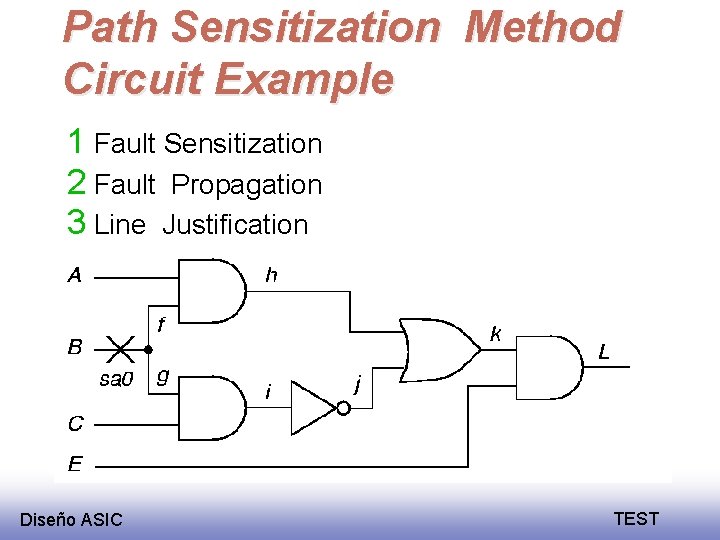

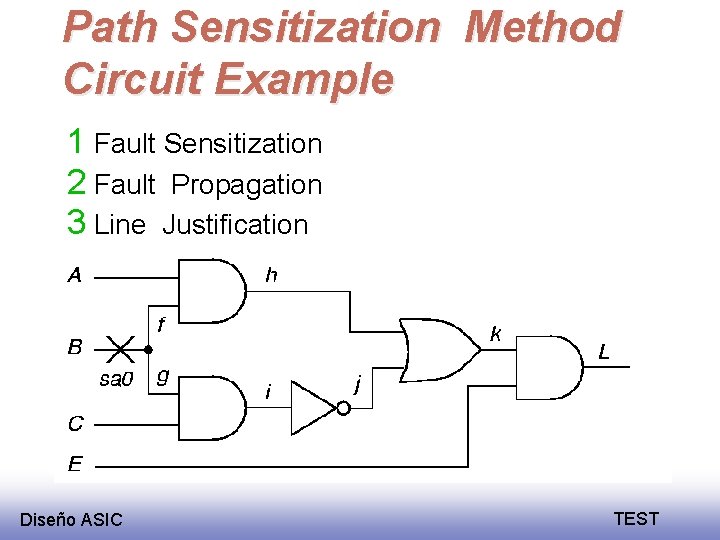

Path Sensitization Method Circuit Example 1 Fault Sensitization 2 Fault Propagation 3 Line Justification Diseño ASIC TEST

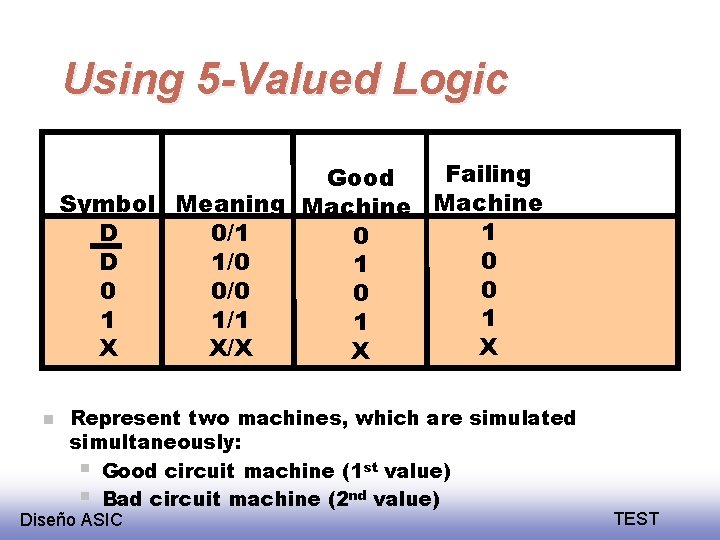

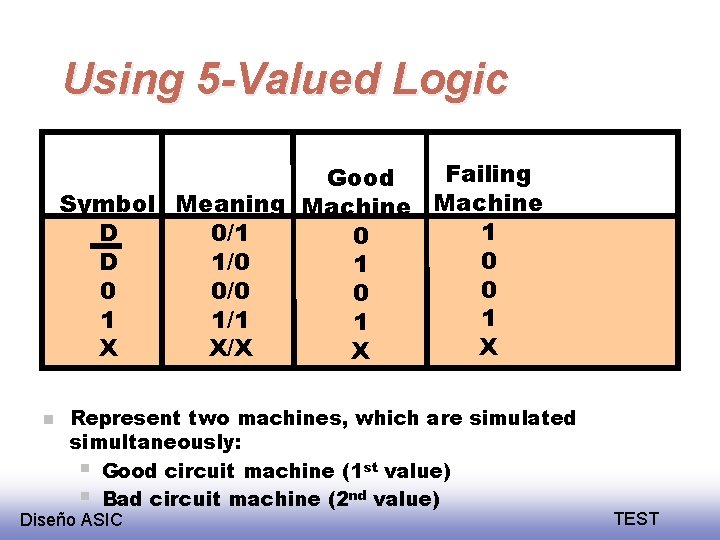

Using 5 -Valued Logic Failing Good Symbol Meaning Machine 1 D 0/1 0 0 D 1/0 1 0 0 0/0 0 1 1 1/1 1 X X X/X X n Represent two machines, which are simulated simultaneously: § Good circuit machine (1 st value) § Bad circuit machine (2 nd value) Diseño ASIC TEST

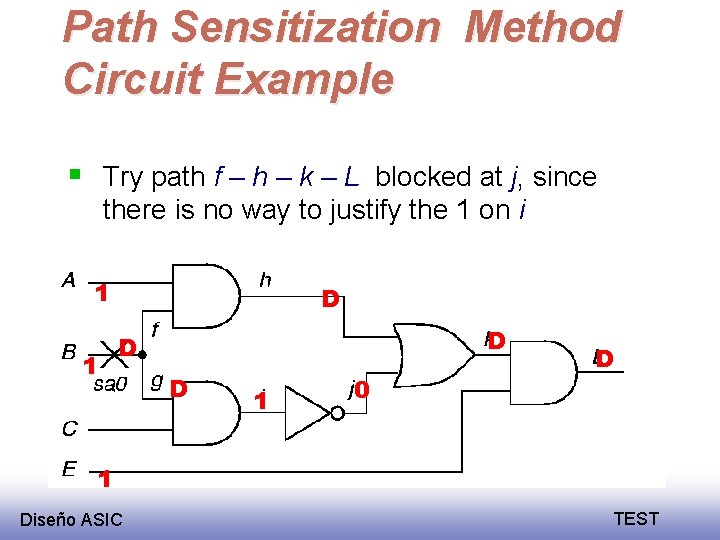

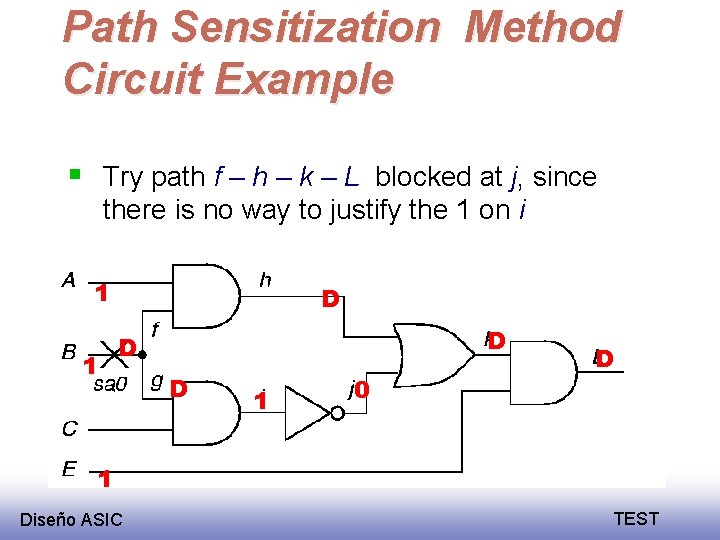

Path Sensitization Method Circuit Example § Try path f – h – k – L blocked at j, since there is no way to justify the 1 on i 1 1 D D 1 0 D 1 Diseño ASIC TEST

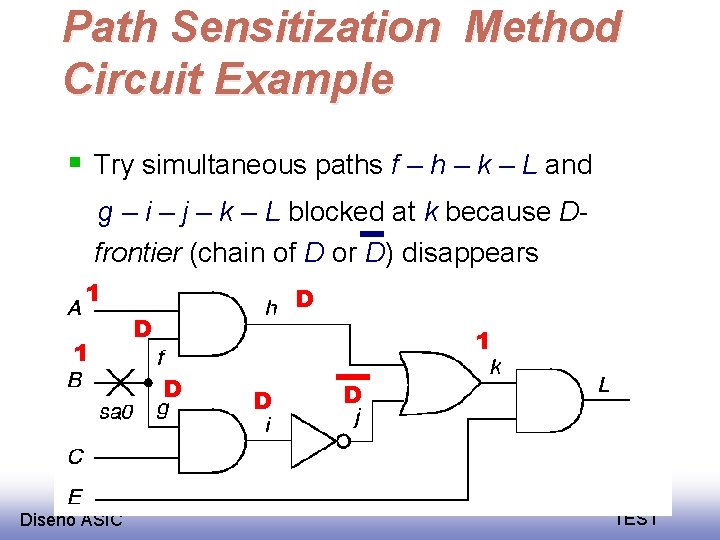

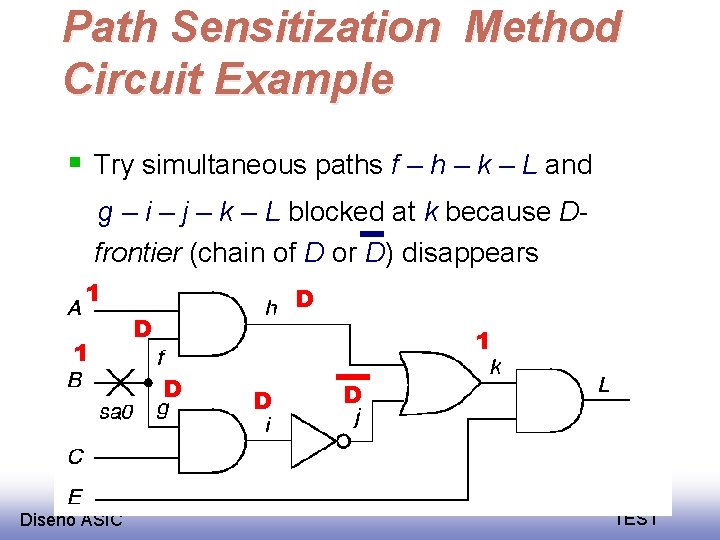

Path Sensitization Method Circuit Example § Try simultaneous paths f – h – k – L and g – i – j – k – L blocked at k because Dfrontier (chain of D or D) disappears 1 1 D Diseño ASIC D D TEST

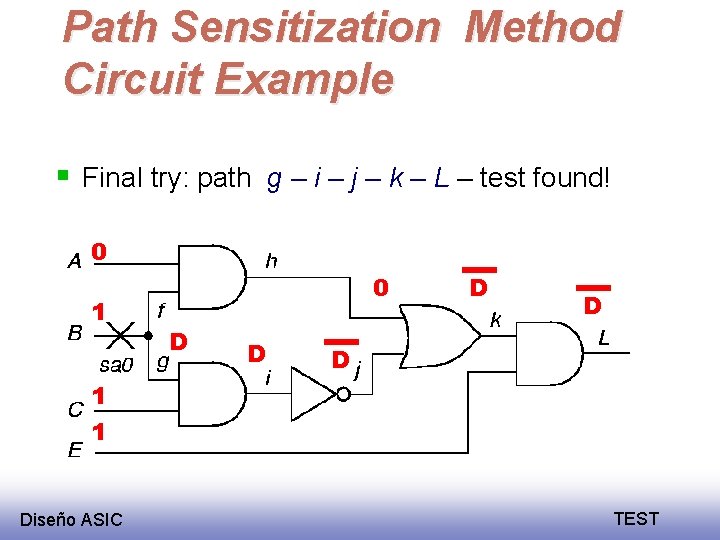

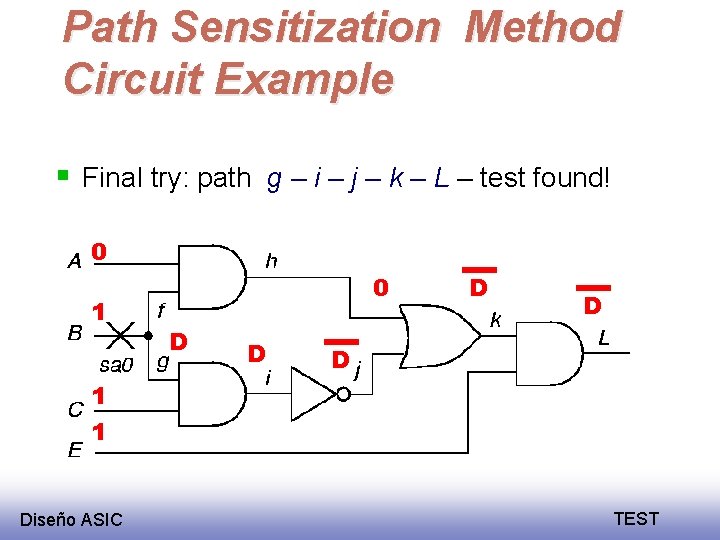

Path Sensitization Method Circuit Example § Final try: path g – i – j – k – L – test found! 0 1 0 D D D 1 1 Diseño ASIC TEST

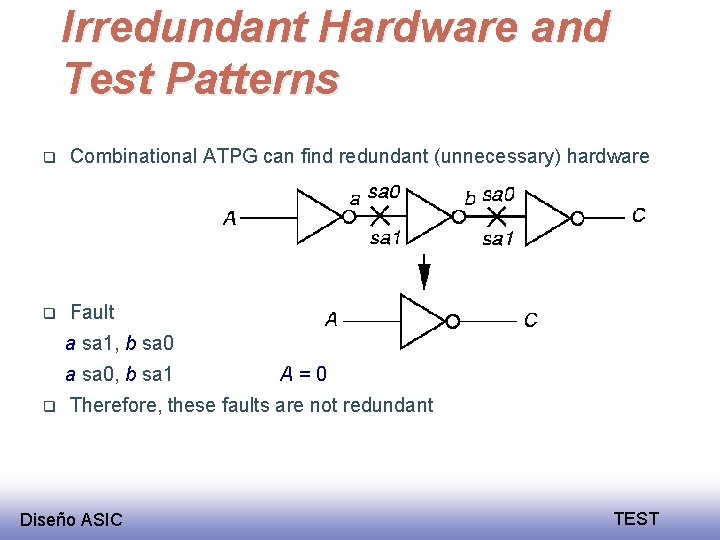

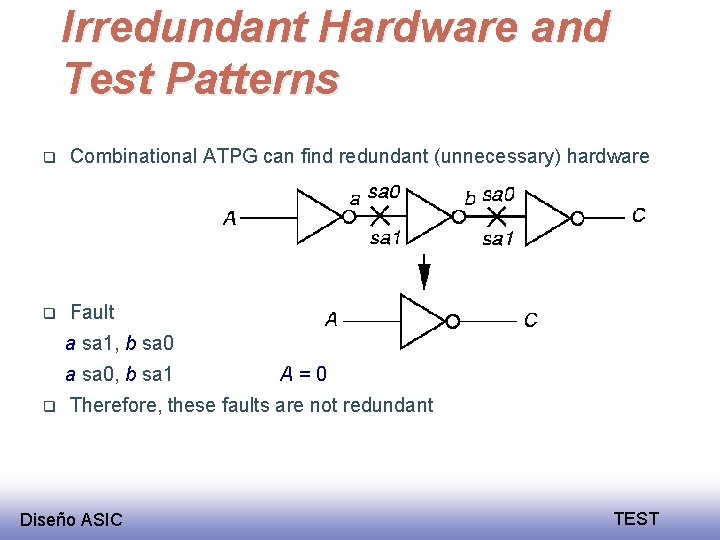

Irredundant Hardware and Test Patterns q Combinational ATPG can find redundant (unnecessary) hardware q Fault Test a sa 1, b sa 0 A=1 a sa 0, b sa 1 A=0 q Therefore, these faults are not redundant Diseño ASIC TEST

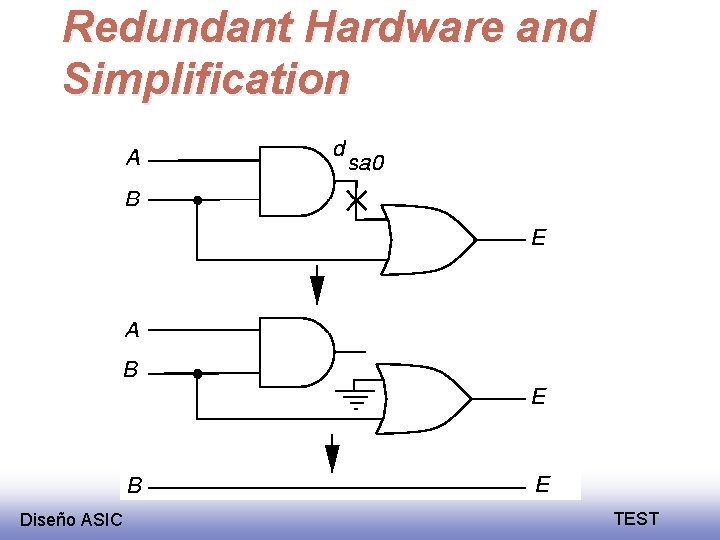

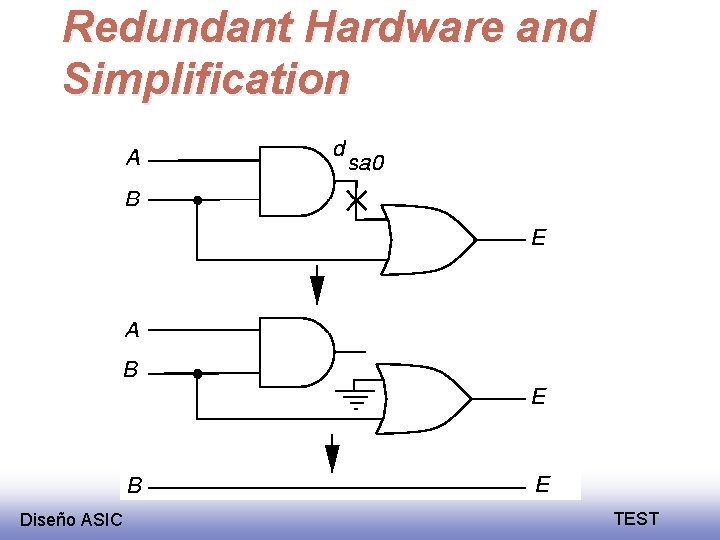

Redundant Hardware and Simplification Diseño ASIC TEST

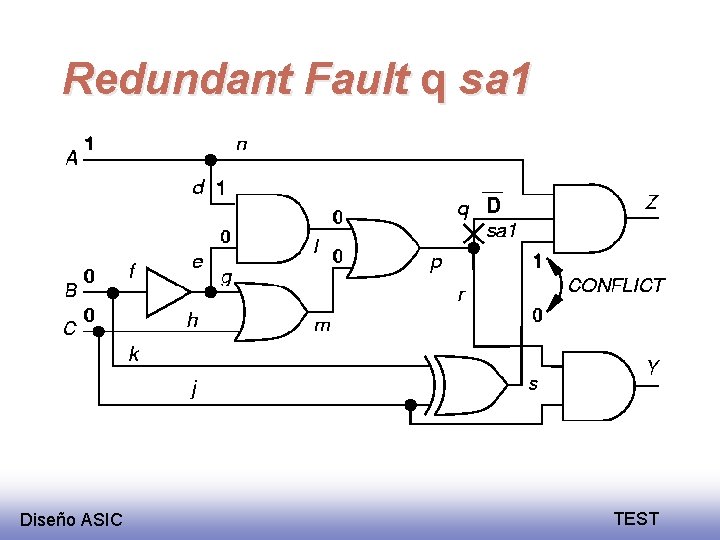

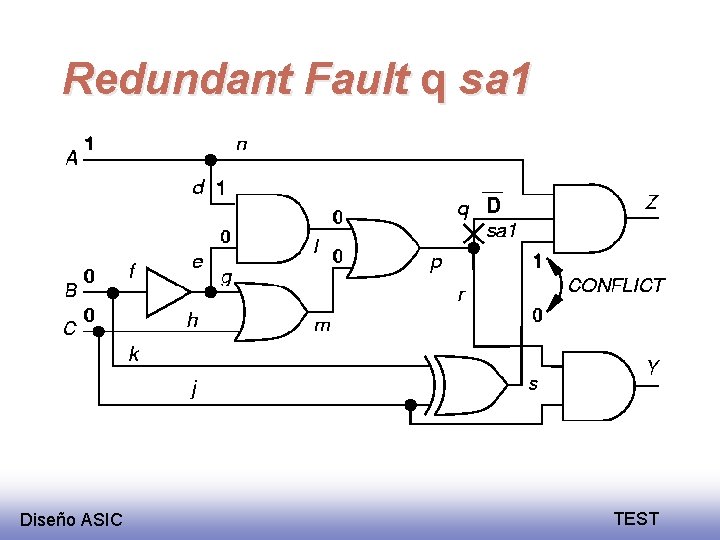

Redundant Fault q sa 1 Diseño ASIC TEST

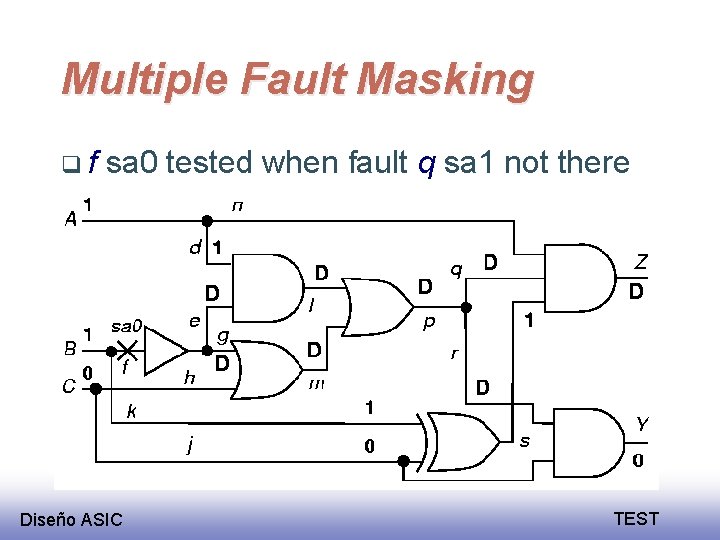

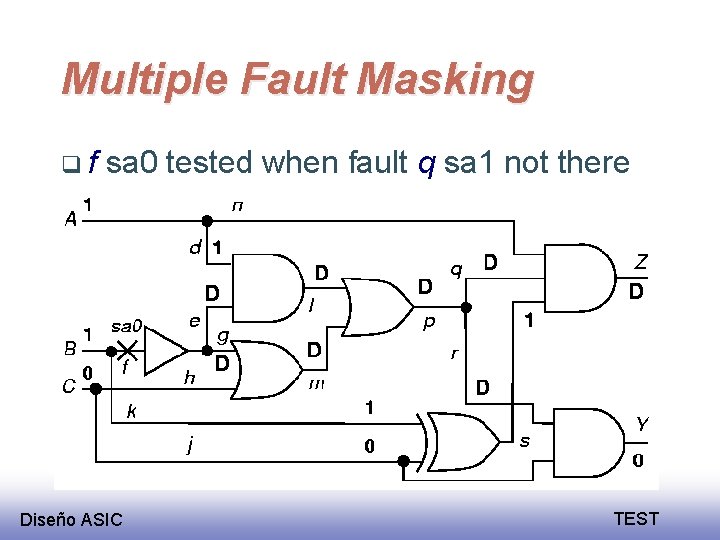

Multiple Fault Masking qf sa 0 tested when fault q sa 1 not there Diseño ASIC TEST

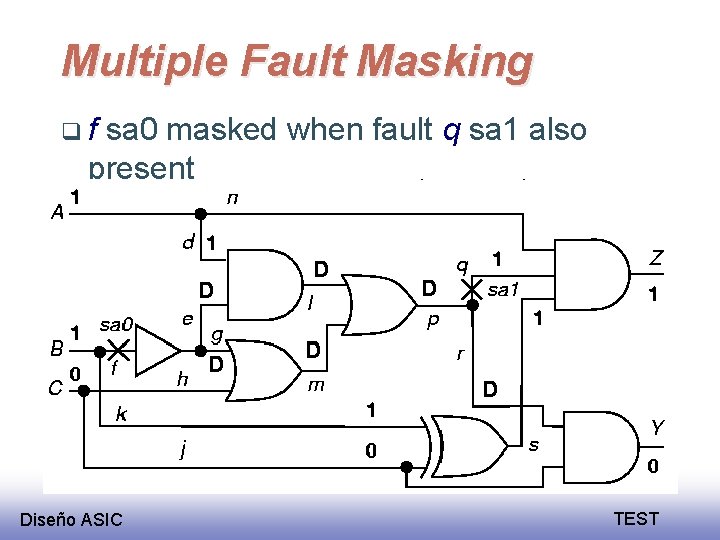

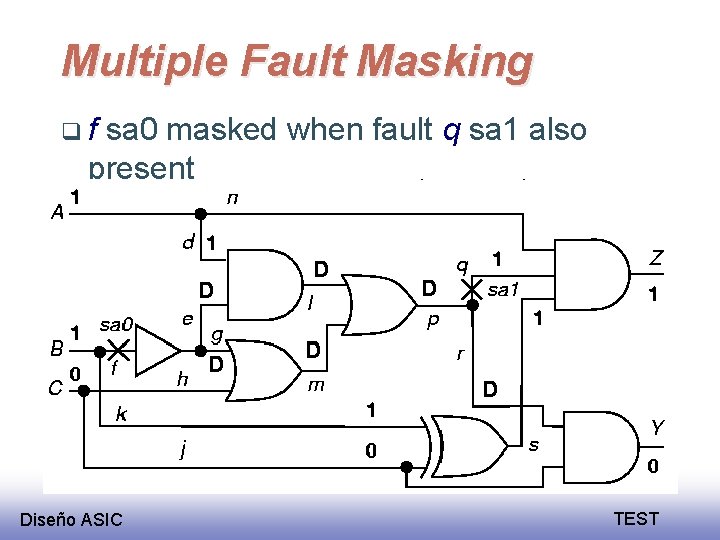

Multiple Fault Masking qf sa 0 masked when fault q sa 1 also present Diseño ASIC TEST

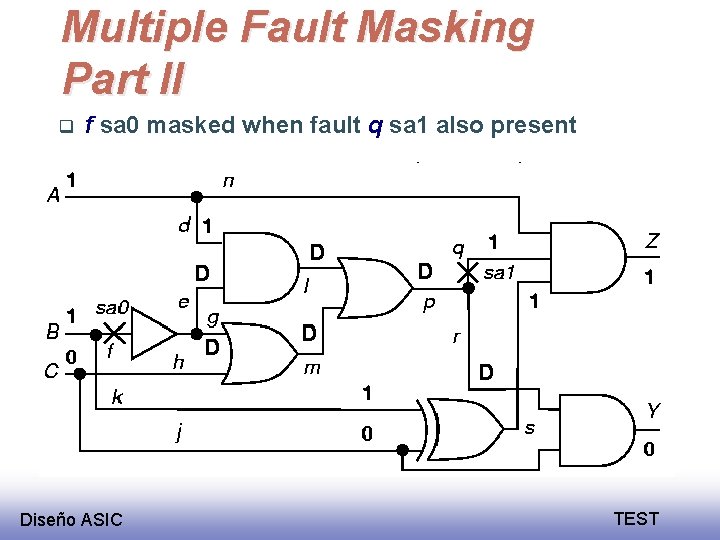

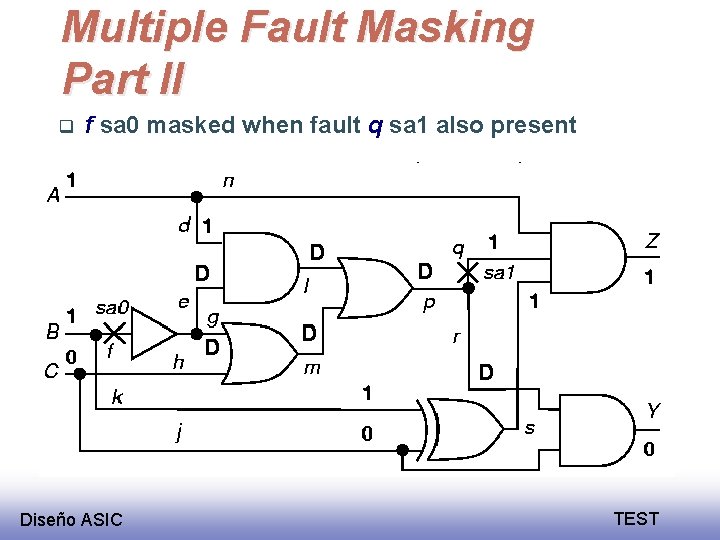

Multiple Fault Masking Part II q f sa 0 masked when fault q sa 1 also present Diseño ASIC TEST

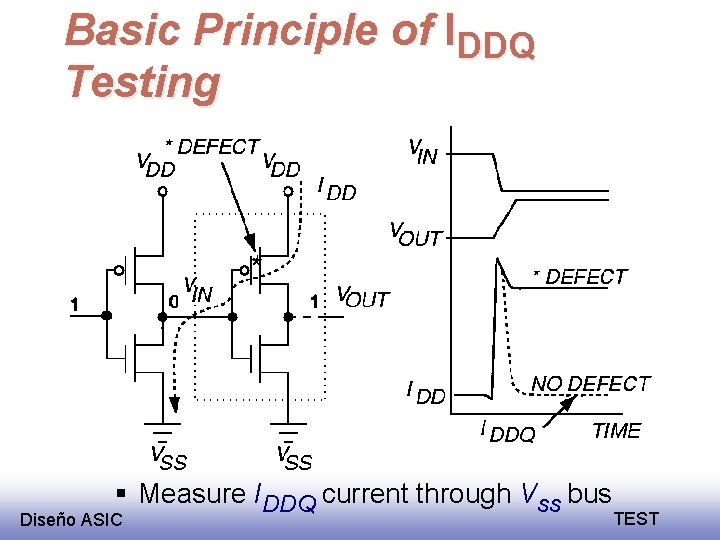

Basic Principle of IDDQ Testing § Measure IDDQ current through Vss bus TEST Diseño ASIC

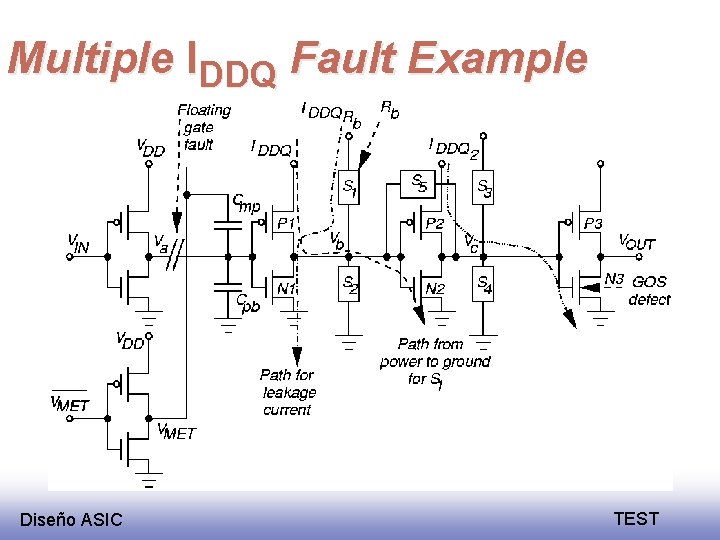

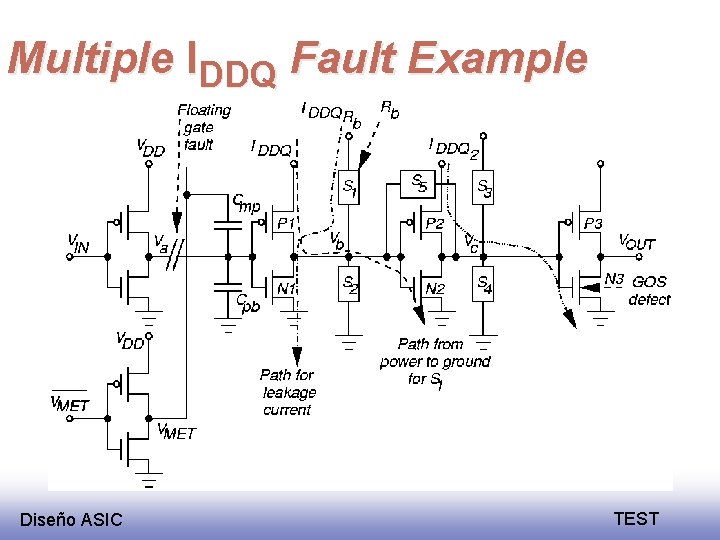

Multiple IDDQ Fault Example Diseño ASIC TEST

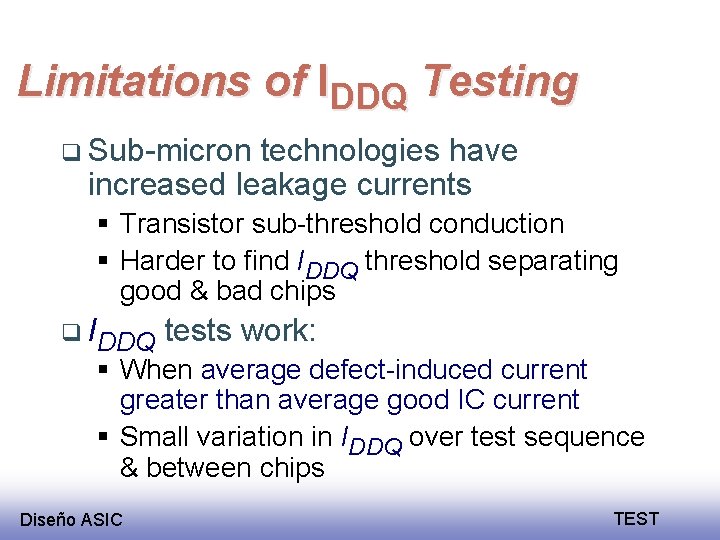

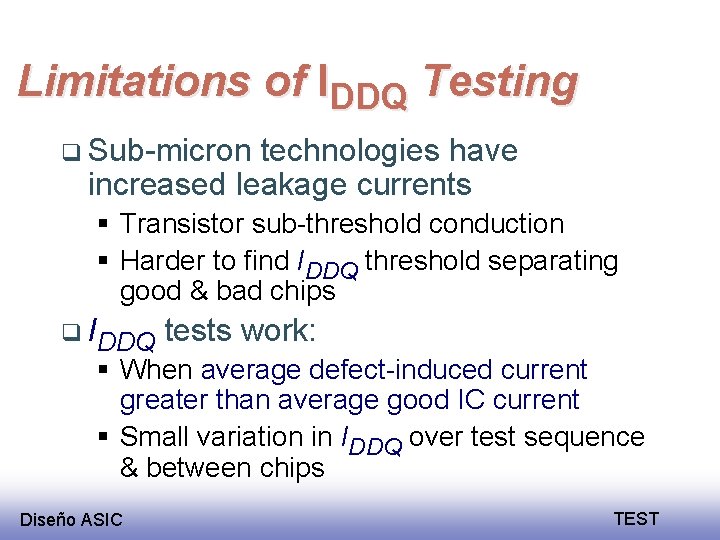

Limitations of IDDQ Testing q Sub-micron technologies have increased leakage currents § Transistor sub-threshold conduction § Harder to find IDDQ threshold separating good & bad chips q IDDQ tests work: § When average defect-induced current greater than average good IC current § Small variation in IDDQ over test sequence & between chips Diseño ASIC TEST