Test Bench for Serdes Radiation Qualification A Aloisio

Test Bench for Serdes Radiation Qualification A. Aloisio, R. Giordano aloisio@na. infn. it, rgiordano@na. infn. it University of Naples ‘Federico II’ and INFN XII Super. B Workshop - LAPP, Annecy - Mar. 18 th, 2010 1

Overview n n n On-detector Ser. Des in the ETD framework Test boards for Rad Tests The full test bench Status and work plan Budget issues Conclusions XII Super. B Workshop - LAPP, Annecy - Mar. 18 th, 2010 2

Ser. Des in rad enviroments Layout by D. Breton LNF, Dec. 09 n FCTS links: ¡ ¡ ¡ n DATA links: ¡ n ¡ ¡ FCTS link Tight latency requirements DS 92 lv 18 Data link No tight latency requirements DS 92 lv 18 or TLK 2711 A Read-out payload DS 92 lv 18: ¡ n Timing & Clock Commands & Controls config data Fixed latency 1. 2 Gbit/s FCTS and DATA TLK 2711 A ¡ ¡ ¡ XII Super. B Workshop - LAPP, Annecy - Mar. 18 th, 2010 Variable latency Up to 2. 7 Gbit/s DATA only 3

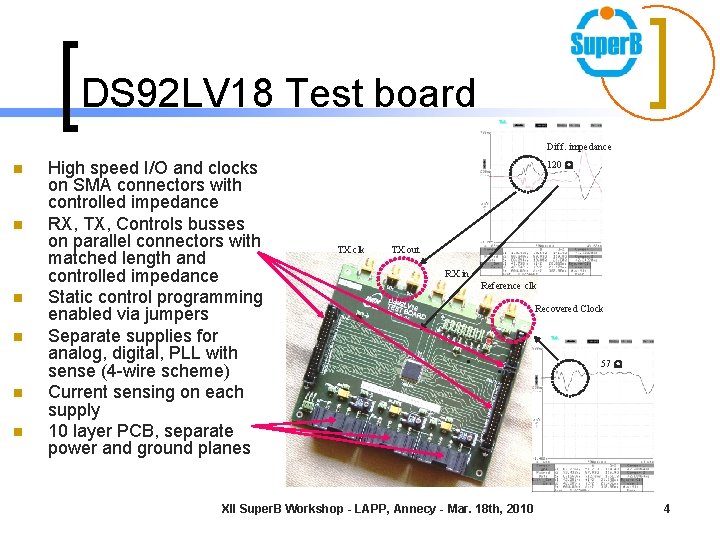

DS 92 LV 18 Test board Diff. impedance n n n High speed I/O and clocks on SMA connectors with controlled impedance RX, TX, Controls busses on parallel connectors with matched length and controlled impedance Static control programming enabled via jumpers Separate supplies for analog, digital, PLL with sense (4 -wire scheme) Current sensing on each supply 10 layer PCB, separate power and ground planes 120 W TX clk TX out RX in Reference clk XII Super. B Workshop - LAPP, Annecy - Mar. 18 th, 2010 Recovered Clock 57 W 4

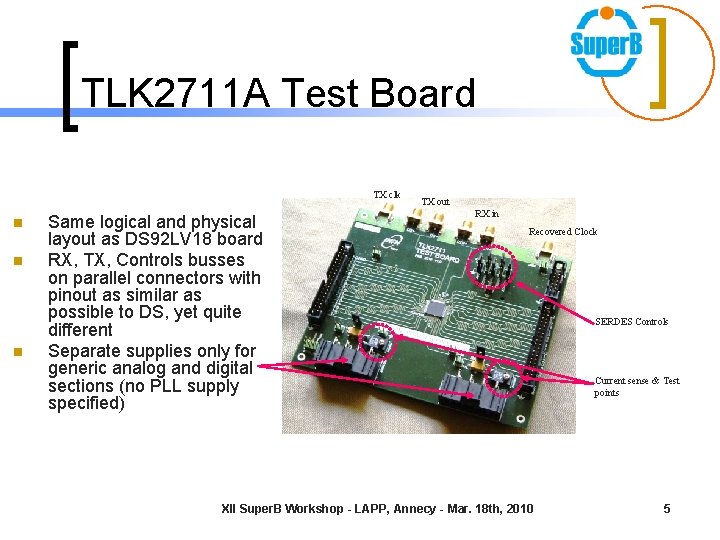

TLK 2711 A Test Board TX clk n n n Same logical and physical layout as DS 92 LV 18 board RX, TX, Controls busses on parallel connectors with pinout as similar as possible to DS, yet quite different Separate supplies only for generic analog and digital sections (no PLL supply specified) TX out RX in Recovered Clock XII Super. B Workshop - LAPP, Annecy - Mar. 18 th, 2010 SERDES Controls Current sense & Test points 5

Test Bench (DS 92 LV 18) XILINX ML 505 Tektronix DTG 5334 Tektronix MSO 70000 Clock Generator FPGA Clk 18 2 RX Reference Clk Recovered Clk TX Clk 8 18 TX Data in Controls Jitter Analyzer RX Data out Power Analyzer Controls RX Serdes TX Serdes AGILENT E 5052 B 3. 3 V Power AGILENT N 6705 A XII Super. B Workshop - LAPP, Annecy - Mar. 18 th, 2010 6

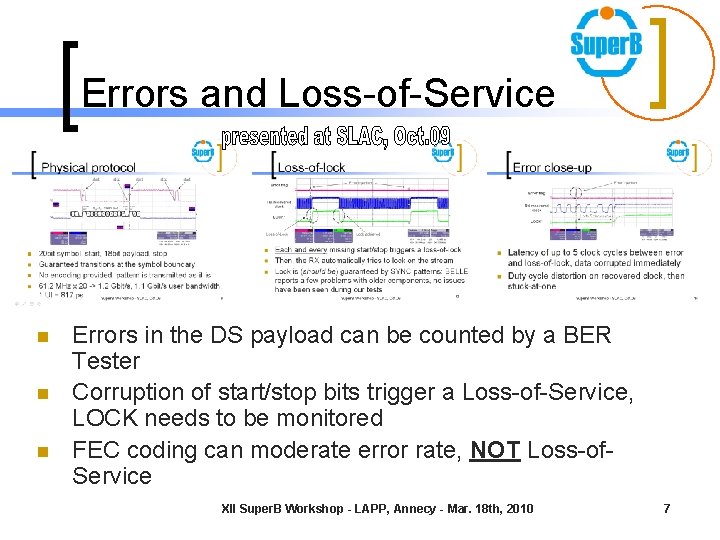

Errors and Loss-of-Service n n n Errors in the DS payload can be counted by a BER Tester Corruption of start/stop bits trigger a Loss-of-Service, LOCK needs to be monitored FEC coding can moderate error rate, NOT Loss-of. Service XII Super. B Workshop - LAPP, Annecy - Mar. 18 th, 2010 7

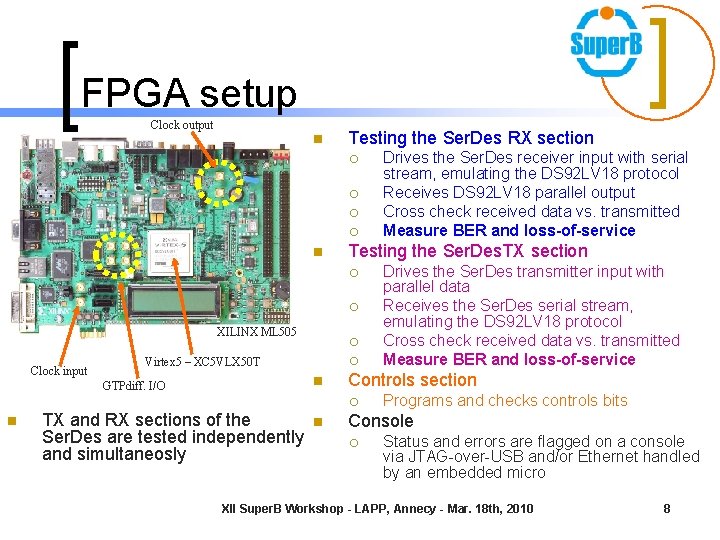

FPGA setup Clock output n Testing the Ser. Des RX section ¡ ¡ n Testing the Ser. Des. TX section ¡ ¡ XILINX ML 505 Clock input ¡ Virtex 5 – XC 5 VLX 50 T ¡ n GTPdiff. I/O TX and RX sections of the Ser. Des are tested independently and simultaneosly n Drives the Ser. Des transmitter input with parallel data Receives the Ser. Des serial stream, emulating the DS 92 LV 18 protocol Cross check received data vs. transmitted Measure BER and loss-of-service Controls section ¡ n Drives the Ser. Des receiver input with serial stream, emulating the DS 92 LV 18 protocol Receives DS 92 LV 18 parallel output Cross check received data vs. transmitted Measure BER and loss-of-service Programs and checks controls bits Console ¡ Status and errors are flagged on a console via JTAG-over-USB and/or Ethernet handled by an embedded micro XII Super. B Workshop - LAPP, Annecy - Mar. 18 th, 2010 8

TLK vs. DS n n n TLK 2711 A and DS 92 LV 18 test boards are very similar … …however, chip-sets have different clock frequency, coding scheme, lock procedure and control handling FPGA firmware will be quite different XII Super. B Workshop - LAPP, Annecy - Mar. 18 th, 2010 9

Status and road-map n n n PCBs have been designed in Nov. /Dec. 09, received last week, assembled (1 board per type) and successfully tested 10 boards per Ser. Des will be used for rad tests (TID and SEU/SEL) FPGA firmware for DS testing is presently being developed, firmware for TLK will follow later Test bench ready in the lab, will be validated as soon as firmware will be available (2 months) LNS (Catania, Italy) call for proton beam allocation still on hold, expected around summer XII Super. B Workshop - LAPP, Annecy - Mar. 18 th, 2010 10

Budget Issues n Funding from INFN CSN I: ¡ n Bills till now: ¡ ¡ n 1 k€ 10+10 PCBs: 2040 € + VAT Components for 20 boards: 4800 € + VAT (including SMA cables, connectors, …) We have got a loan from other groups, but we have to pay it down soon XII Super. B Workshop - LAPP, Annecy - Mar. 18 th, 2010 11

Conclusions n n n Boards for TLK and DS evaluation have been developed and tested Test bench for Rad tests is presently under developments: power consumption, BER, Loss-of-Service waiting for beam time at LNS (at no cost) Q 3/Q 4 2010 XII Super. B Workshop - LAPP, Annecy - Mar. 18 th, 2010 12

- Slides: 12