Test Bench A test bench can be used

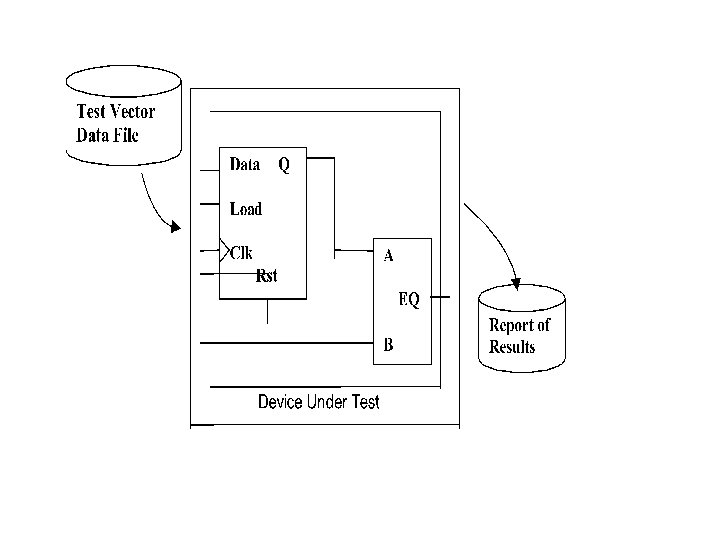

Test Bench • A test bench can be used to verify a design’s functionality. • It allows input test vectors to be applied to a design ( the unit under test ) and the output test vectors to be either observed by waveform, recorded in an output vector file, or compared within the test bench against the expected values.

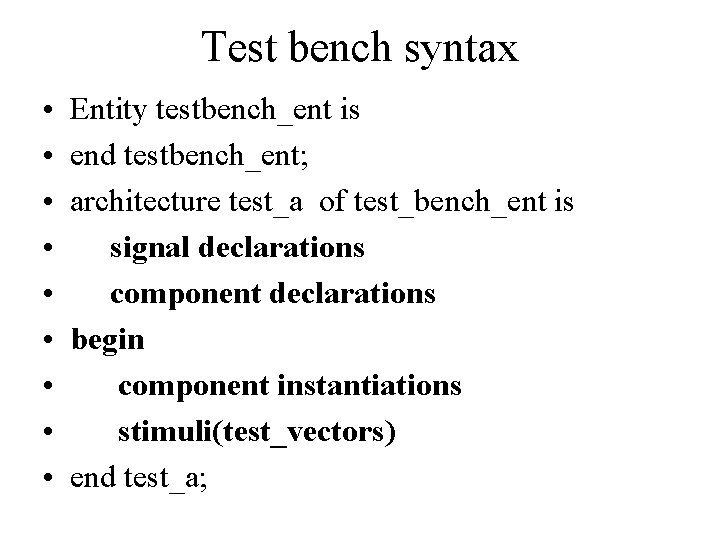

Test bench syntax • • • Entity testbench_ent is end testbench_ent; architecture test_a of test_bench_ent is signal declarations component declarations begin component instantiations stimuli(test_vectors) end test_a;

Test bench • Test bench may be written using one or more sequential processes, or a series of signal assignments and wait statements to describe the actual stimulus. • You can use VHDL’s looping features to simplify the description of repetitive stimulus (such as the system clock).

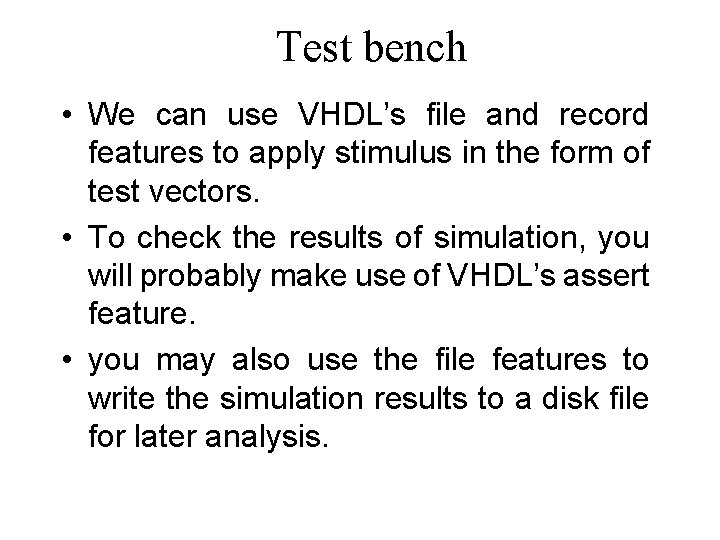

Test bench • We can use VHDL’s file and record features to apply stimulus in the form of test vectors. • To check the results of simulation, you will probably make use of VHDL’s assert feature. • you may also use the file features to write the simulation results to a disk file for later analysis.

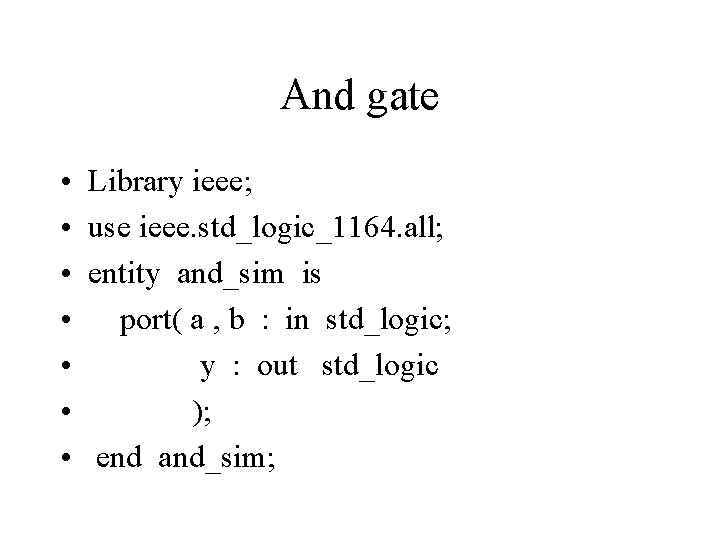

And gate • • Library ieee; use ieee. std_logic_1164. all; entity and_sim is port( a , b : in std_logic; y : out std_logic ); end and_sim;

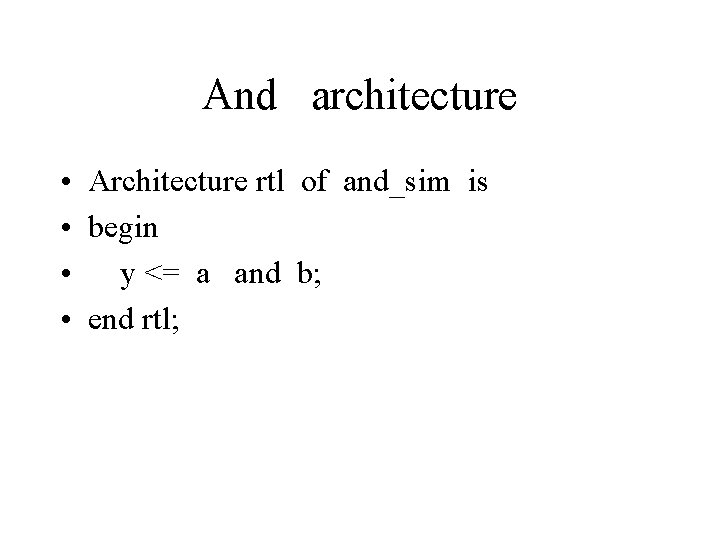

And architecture • Architecture rtl of and_sim is • begin • y <= a and b; • end rtl;

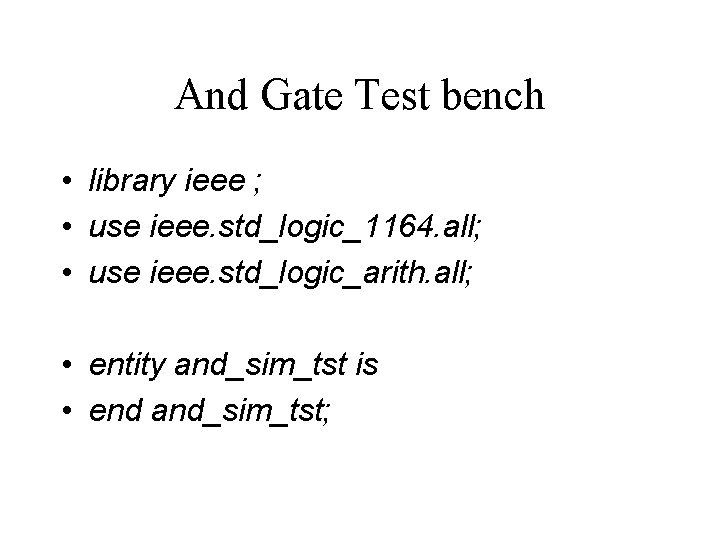

And Gate Test bench • library ieee ; • use ieee. std_logic_1164. all; • use ieee. std_logic_arith. all; • entity and_sim_tst is • end and_sim_tst;

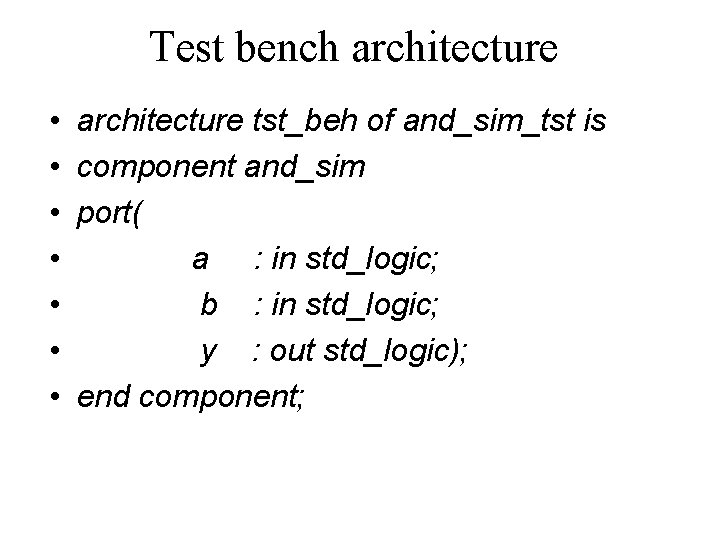

Test bench architecture • • architecture tst_beh of and_sim_tst is component and_sim port( a : in std_logic; b : in std_logic; y : out std_logic); end component;

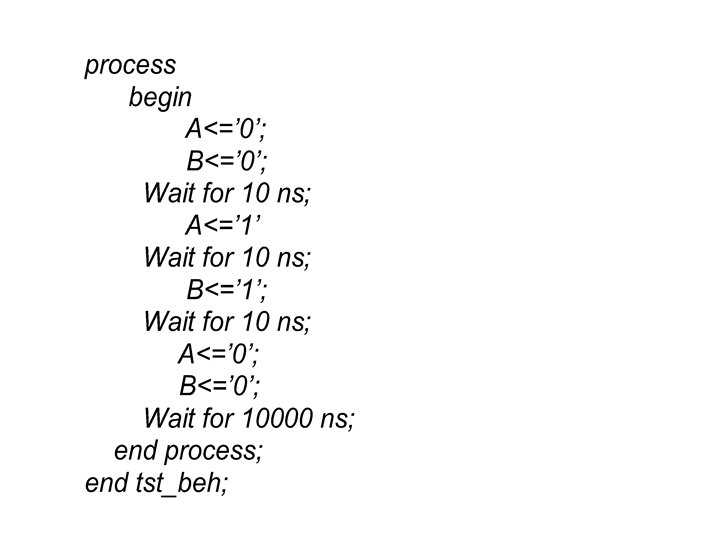

• signal a, b, y : std_logic; • begin • UUT: and_sim portmap(a=>a, y=>y); b=>b,

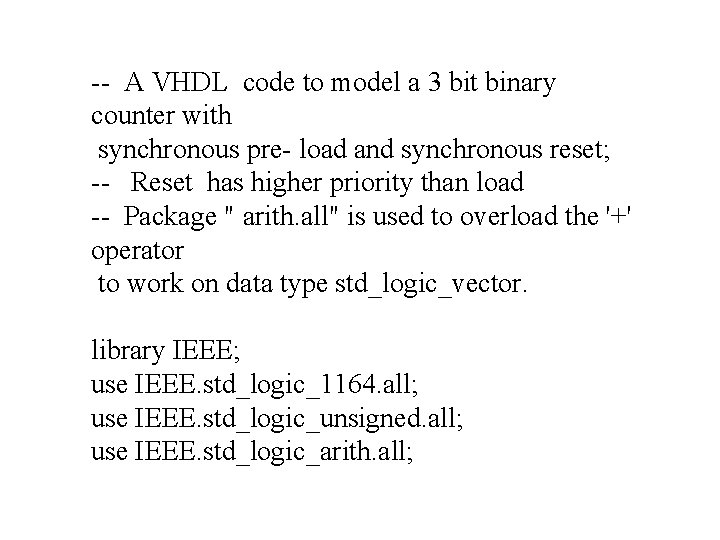

-- A VHDL code to model a 3 bit binary counter with synchronous pre- load and synchronous reset; -- Reset has higher priority than load -- Package " arith. all" is used to overload the '+' operator to work on data type std_logic_vector. library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_unsigned. all; use IEEE. std_logic_arith. all;

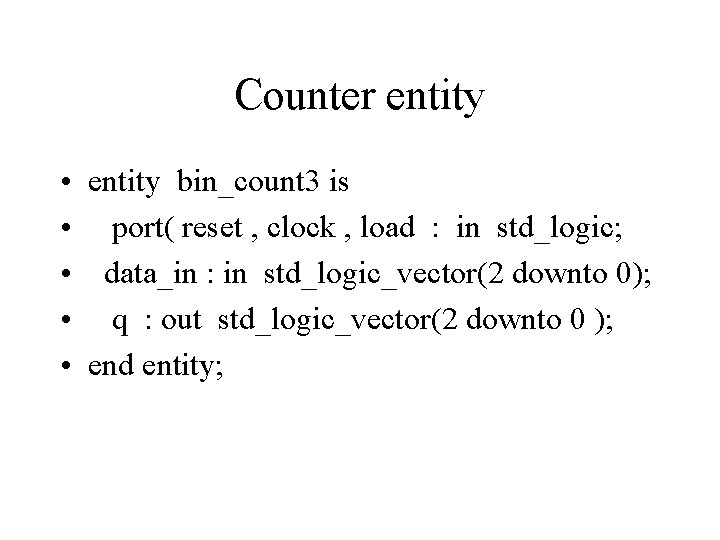

Counter entity • entity bin_count 3 is • port( reset , clock , load : in std_logic; • data_in : in std_logic_vector(2 downto 0); • q : out std_logic_vector(2 downto 0 ); • end entity;

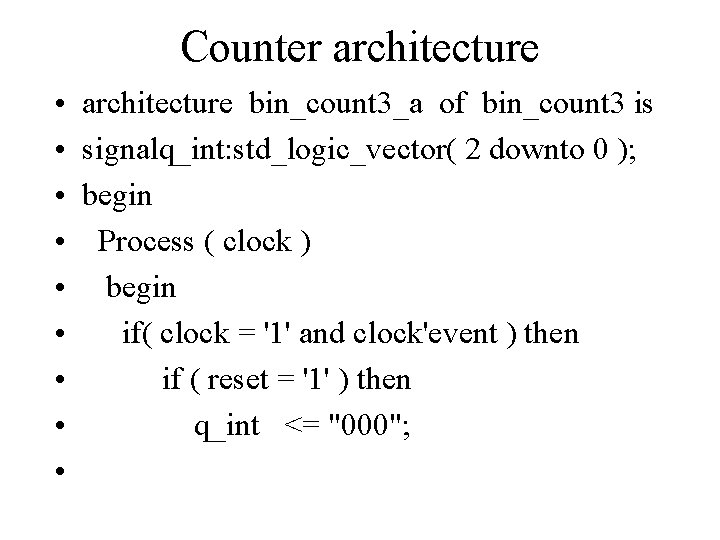

Counter architecture • • • architecture bin_count 3_a of bin_count 3 is signalq_int: std_logic_vector( 2 downto 0 ); begin Process ( clock ) begin if( clock = '1' and clock'event ) then if ( reset = '1' ) then q_int <= "000";

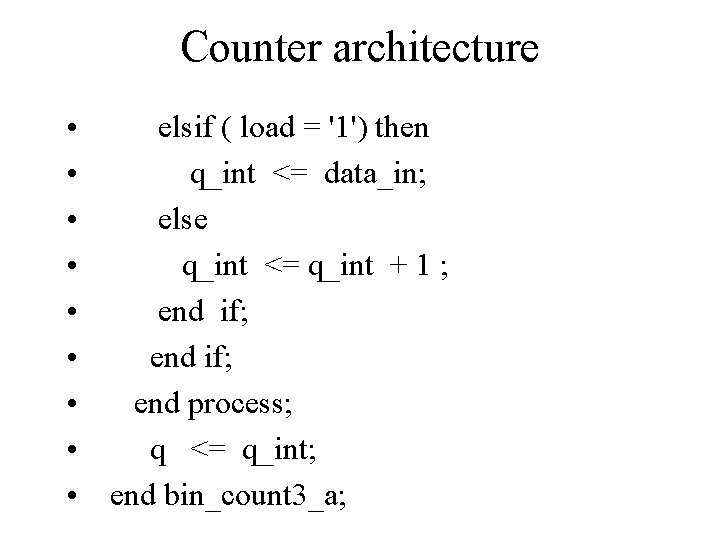

Counter architecture • elsif ( load = '1') then • q_int <= data_in; • else • q_int <= q_int + 1 ; • end if; • end process; • q <= q_int; • end bin_count 3_a;

Counter test bench • • • Library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_arith. all; entity bin_count 3_tst is; end bin_count 3_tst;

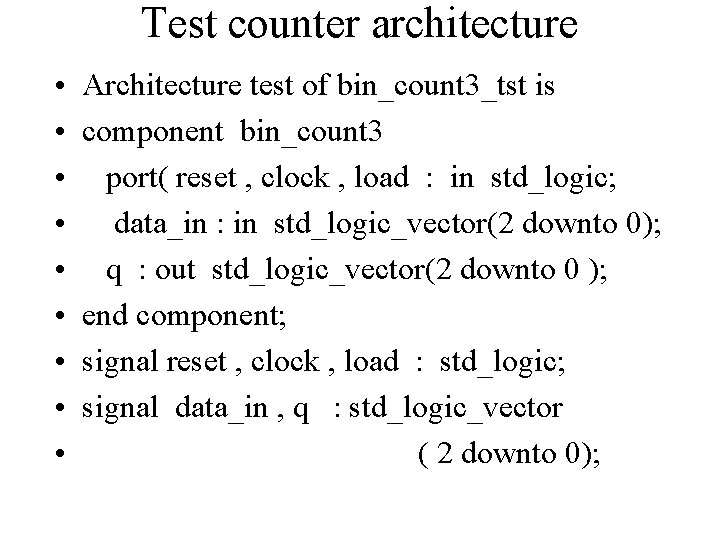

Test counter architecture • • • Architecture test of bin_count 3_tst is component bin_count 3 port( reset , clock , load : in std_logic; data_in : in std_logic_vector(2 downto 0); q : out std_logic_vector(2 downto 0 ); end component; signal reset , clock , load : std_logic; signal data_in , q : std_logic_vector ( 2 downto 0);

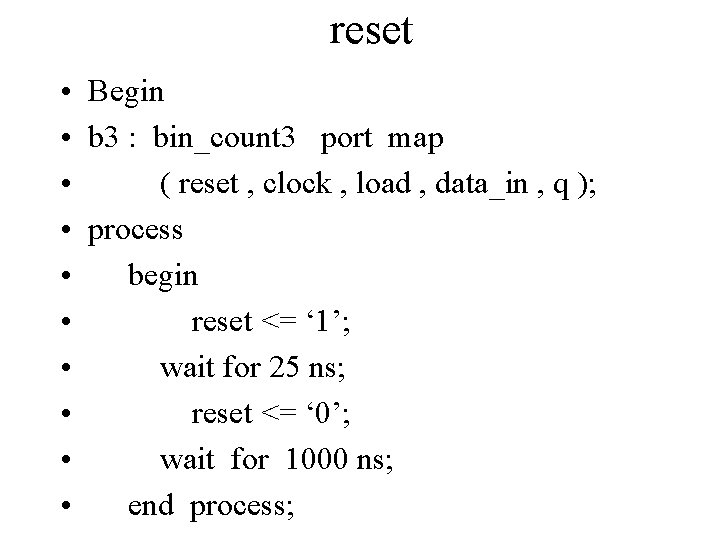

reset • Begin • b 3 : bin_count 3 port map • ( reset , clock , load , data_in , q ); • process • begin • reset <= ‘ 1’; • wait for 25 ns; • reset <= ‘ 0’; • wait for 1000 ns; • end process;

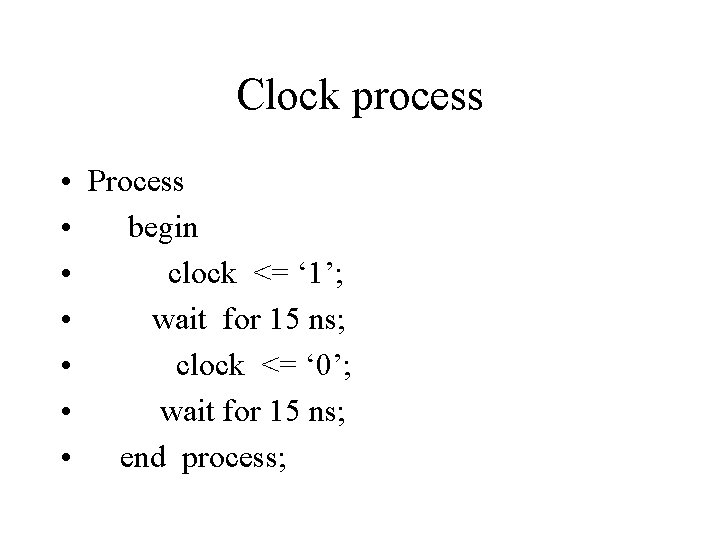

Clock process • Process • begin • clock <= ‘ 1’; • wait for 15 ns; • clock <= ‘ 0’; • wait for 15 ns; • end process;

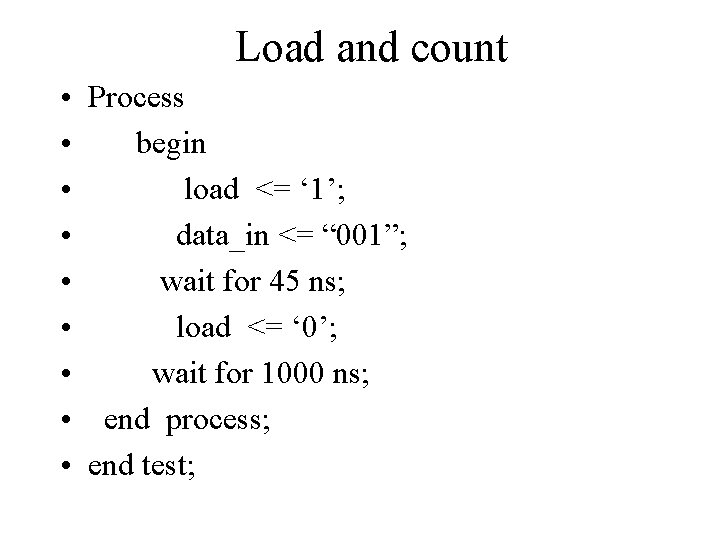

Load and count • Process • begin • load <= ‘ 1’; • data_in <= “ 001”; • wait for 45 ns; • load <= ‘ 0’; • wait for 1000 ns; • end process; • end test;

- Slides: 21