TCAD Simulation for SOI Pixel Detectors October 31

TCAD Simulation for SOI Pixel Detectors October 31, 2006 Hirokazu Hayashi, Hirotaka Komatsubara (Oki Elec. Ind. Co. ), Masashi Hazumi (KEK) for the SOIPIX group 2006/10/31 M. Hazumi (KEK)

![SOIPIX collaborators KEK Detector Technology Project : [SOIPIX Group] Y. Arai*, Y. Ikegami, H. SOIPIX collaborators KEK Detector Technology Project : [SOIPIX Group] Y. Arai*, Y. Ikegami, H.](http://slidetodoc.com/presentation_image_h/f7f3e10da1d6ed203f57ef3bde60816b/image-2.jpg)

SOIPIX collaborators KEK Detector Technology Project : [SOIPIX Group] Y. Arai*, Y. Ikegami, H. Ushiroda, Y. Unno, O. Tajima, T. Tsuboyama, S. Terada, M. Hazumi, H. Ikeda. A, K. Hara. B, H. Ishino. C, T. Kawasaki. D, H. Miyake. E, G. Varner. F, E. Martin. F, H. Tajima. G, M. Ohno. H, K. Fukuda. H, H. Hayashi. H, H. Komatsubara. H, J. Ida. H KEK、JAXAA, U. Tsukuba. B, TITC, Niigata U. D, Osaka U. E, U. Hawaii. F, SLACG, OKI Elec. Ind. Co. H Financial Support by KEK (*)—contact person 2006/10/31 Detector Technology Project 2 M. Hazumi (KEK)

Outline • TCAD Overview • Breakdown voltage • Effect of bias voltage on readout electronics • P-substrate option • Summary 2006/10/31 M. Hazumi (KEK) 3

TCAD Overview 2006/10/31 M. Hazumi (KEK) 4

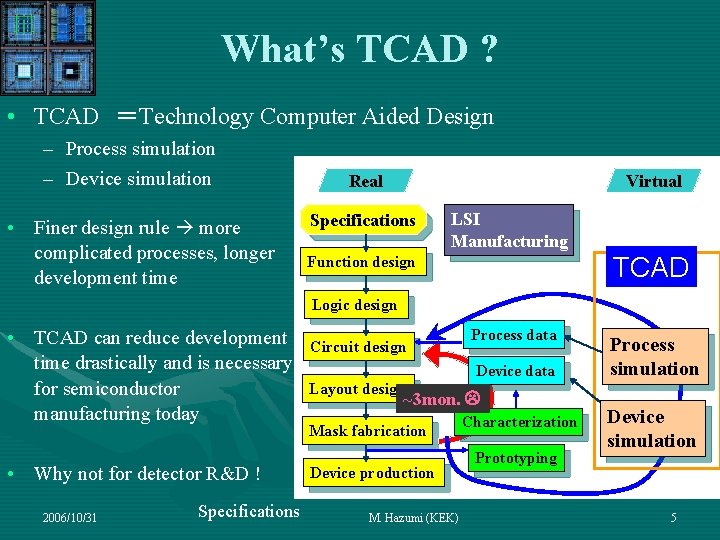

What’s TCAD ? • TCAD =Technology Computer Aided Design – Process simulation – Device simulation • Finer design rule more complicated processes, longer development time Real Virtual Specifications LSI Manufacturing TCAD Function design Logic design • TCAD can reduce development time drastically and is necessary for semiconductor manufacturing today • Why not for detector R&D ! 2006/10/31 Specifications Circuit design Process data Device data Process simulation Layout design ~3 mon. Mask fabrication Device production M. Hazumi (KEK) Characterization Prototyping Device simulation 5

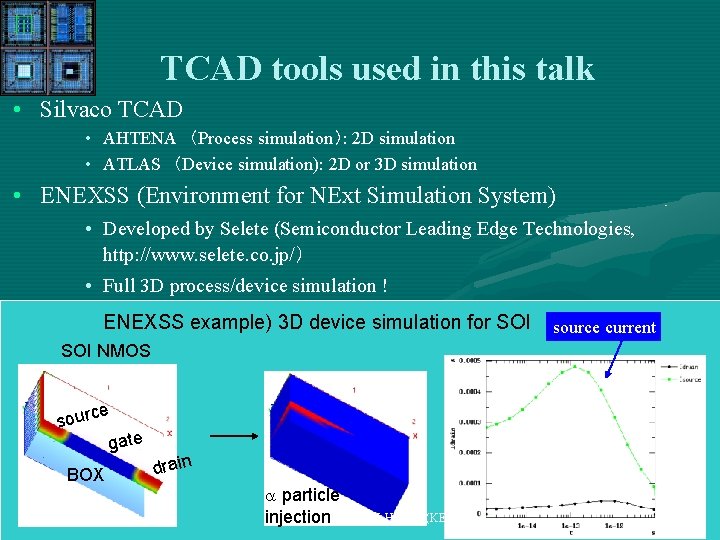

TCAD tools used in this talk • Silvaco TCAD • AHTENA (Process simulation): 2 D simulation • ATLAS (Device simulation): 2 D or 3 D simulation • ENEXSS (Environment for NExt Simulation System) • Developed by Selete (Semiconductor Leading Edge Technologies, http: //www. selete. co. jp/) • Full 3 D process/device simulation ! ENEXSS example) 3 D device simulation for SOI source current SOI NMOS e sourc gate BOX 2006/10/31 drain a particle injection M. Hazumi (KEK) 6

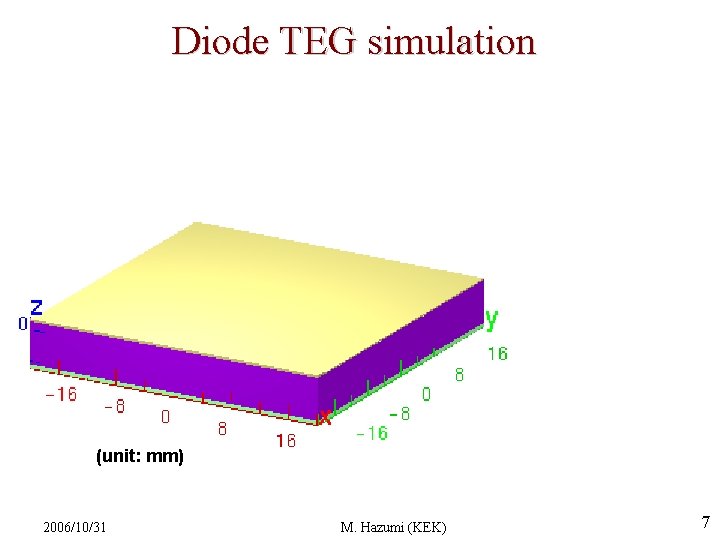

Diode TEG simulation (unit: mm) 2006/10/31 M. Hazumi (KEK) 7

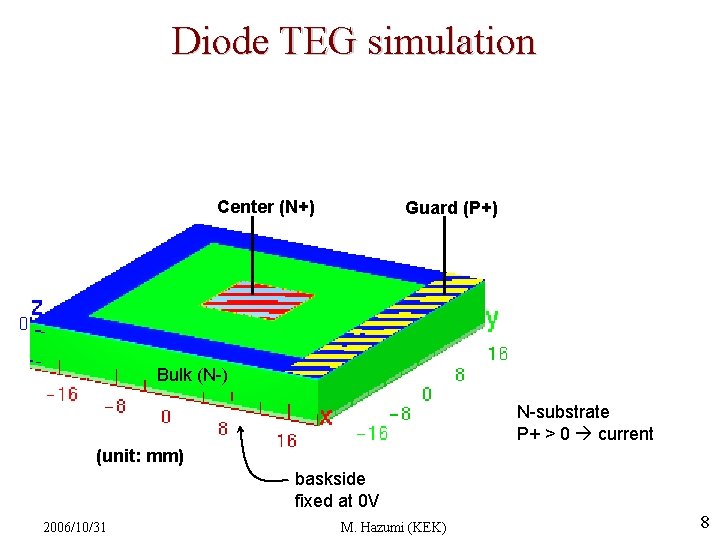

Diode TEG simulation Center (N+) Guard (P+) Bulk (N-) N-substrate P+ > 0 current (unit: mm) baskside fixed at 0 V 2006/10/31 M. Hazumi (KEK) 8

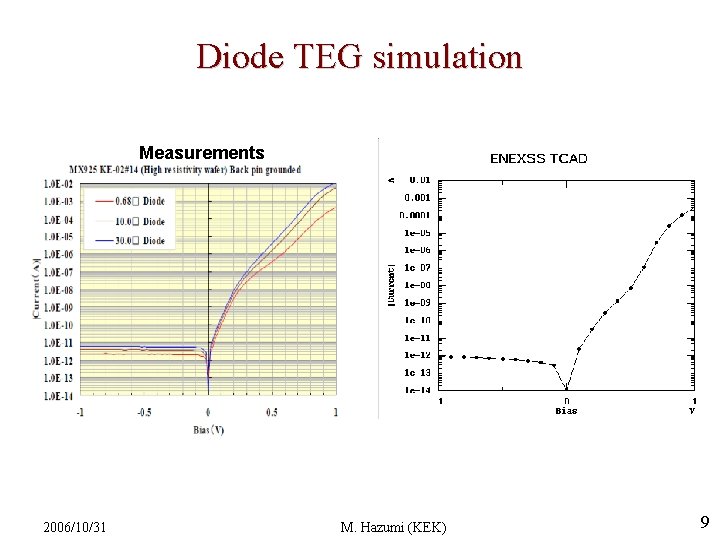

Diode TEG simulation Measurements 2006/10/31 M. Hazumi (KEK) 9

TCAD for SOIPIX R&D Useful to obtain Ø field maps Ø device characteristics Ø signals induced by particles • Handle wafer (i. e. sensor) simulation – Pixel and guard ring design optimization • Breakdown voltage • Charge collection – Problem finding/solving before fabrication • Effect of bias voltage on readout electronics – I/O pads – p-stops for P-substrate option 2006/10/31 M. Hazumi (KEK) 10

Breakdown voltage Results of measurements are reported by H. Miyake: Breakdown voltage ~ 100 V at bias-ring edges. 2006/10/31 M. Hazumi (KEK) 11

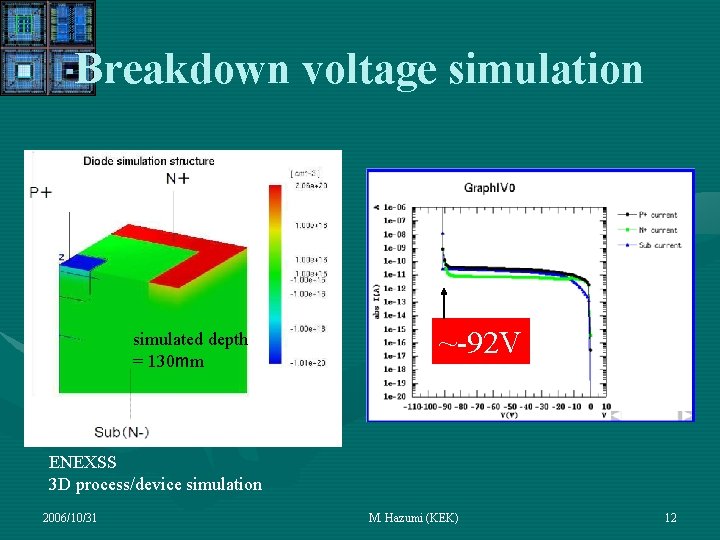

Breakdown voltage simulation simulated depth = 130 mm ~-92 V ENEXSS 3 D process/device simulation 2006/10/31 M. Hazumi (KEK) 12

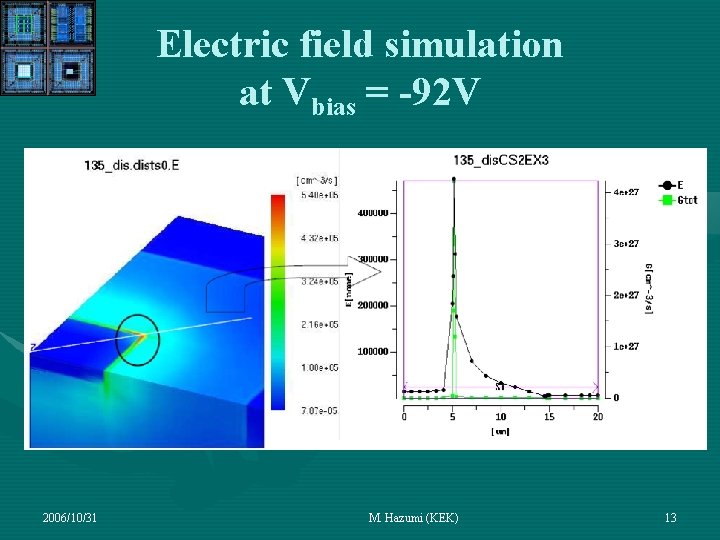

Electric field simulation at Vbias = -92 V 2006/10/31 M. Hazumi (KEK) 13

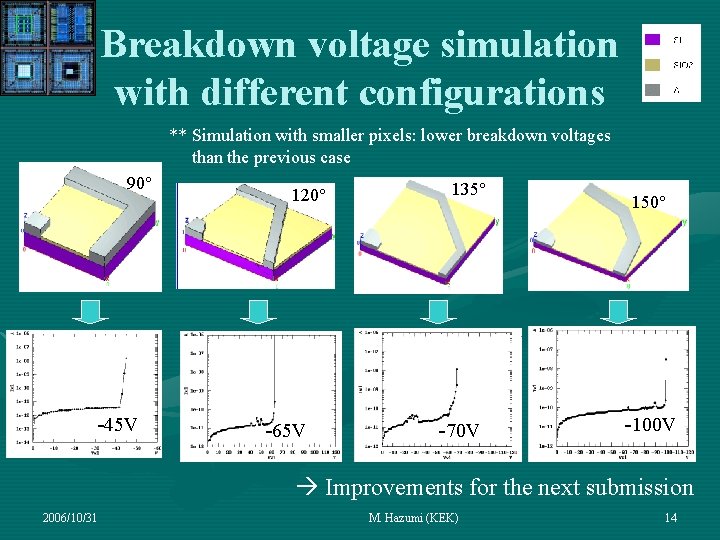

Breakdown voltage simulation with different configurations ** Simulation with smaller pixels: lower breakdown voltages than the previous case 90 -45 V 120 -65 V 135 -70 V 150 -100 V Improvements for the next submission 2006/10/31 M. Hazumi (KEK) 14

Effect of bias voltage on readout electronics 2006/10/31 M. Hazumi (KEK) 15

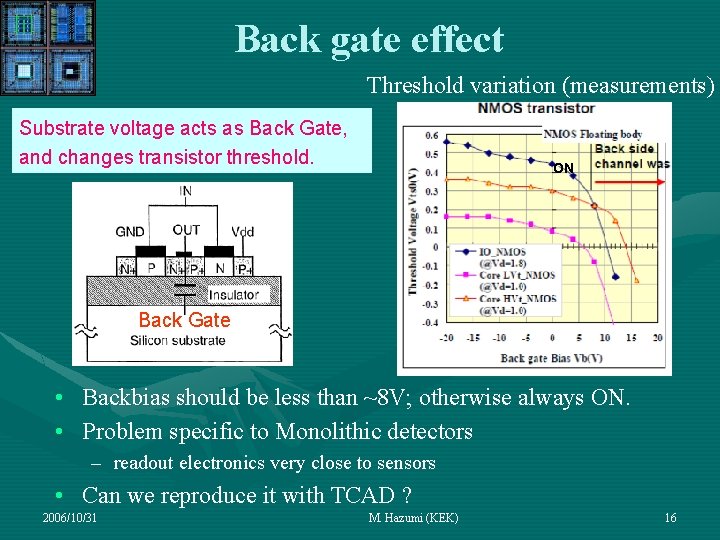

Back gate effect Threshold variation (measurements) Substrate voltage acts as Back Gate, and changes transistor threshold. ON Back Gate • Backbias should be less than ~8 V; otherwise always ON. • Problem specific to Monolithic detectors – readout electronics very close to sensors • Can we reproduce it with TCAD ? 2006/10/31 M. Hazumi (KEK) 16

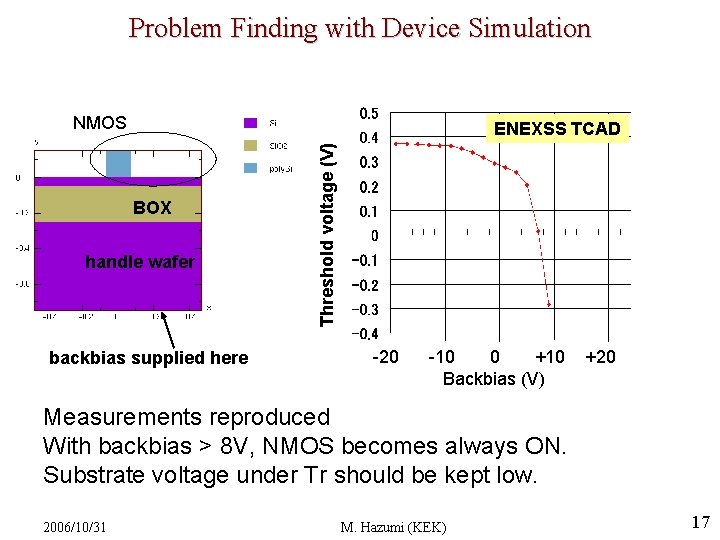

Problem Finding with Device Simulation NMOS BOX handle wafer backbias supplied here Threshold voltage (V) ENEXSS TCAD -20 -10 0 +10 Backbias (V) VB (V) +20 Measurements reproduced With backbias > 8 V, NMOS becomes always ON. Substrate voltage under Tr should be kept low. 2006/10/31 M. Hazumi (KEK) 17

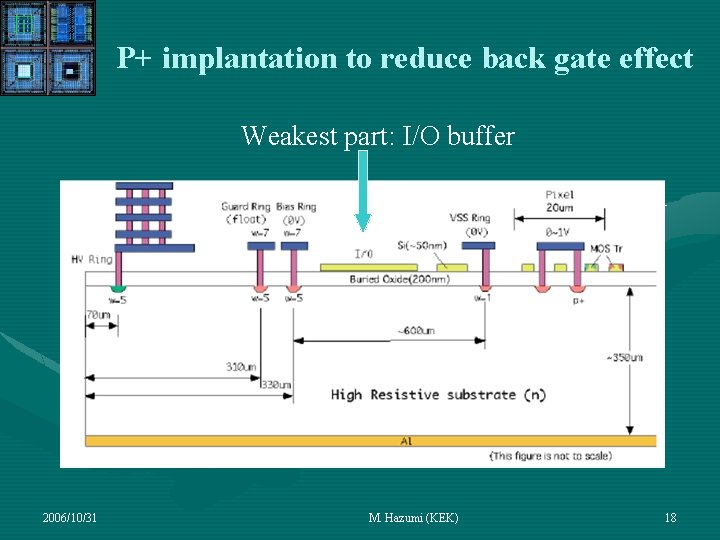

P+ implantation to reduce back gate effect Weakest part: I/O buffer 2006/10/31 M. Hazumi (KEK) 18

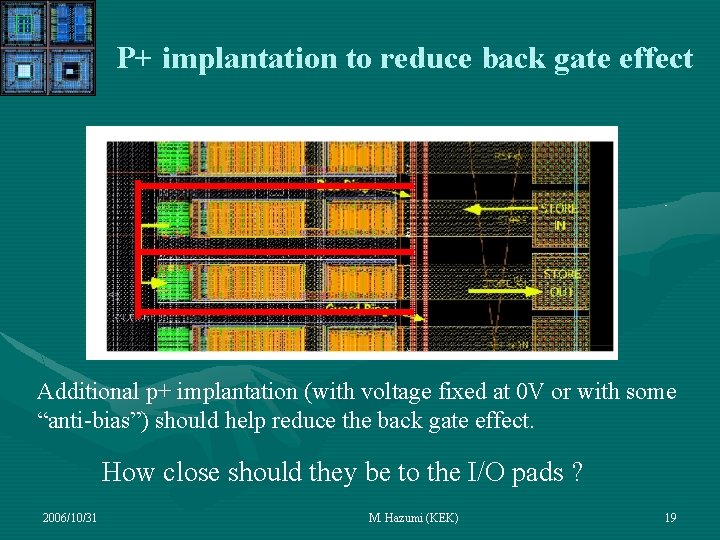

P+ implantation to reduce back gate effect Additional p+ implantation (with voltage fixed at 0 V or with some “anti-bias”) should help reduce the back gate effect. How close should they be to the I/O pads ? 2006/10/31 M. Hazumi (KEK) 19

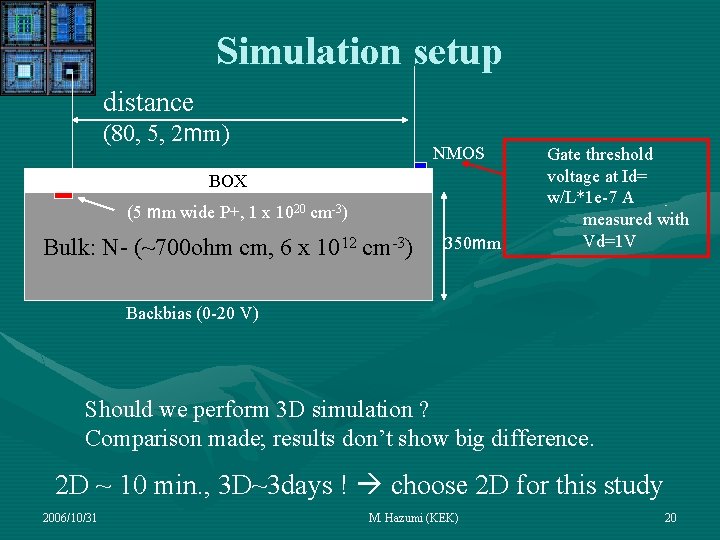

Simulation setup distance (80, 5, 2 mm) NMOS BOX (5 mm wide P+, 1 x 1020 cm-3) Bulk: N- (~700 ohm cm, 6 x 1012 cm-3) 350 mm Gate threshold voltage at Id= w/L*1 e-7 A measured with Vd=1 V Backbias (0 -20 V) Should we perform 3 D simulation ? Comparison made; results don’t show big difference. 2 D ~ 10 min. , 3 D~3 days ! choose 2 D for this study 2006/10/31 M. Hazumi (KEK) 20

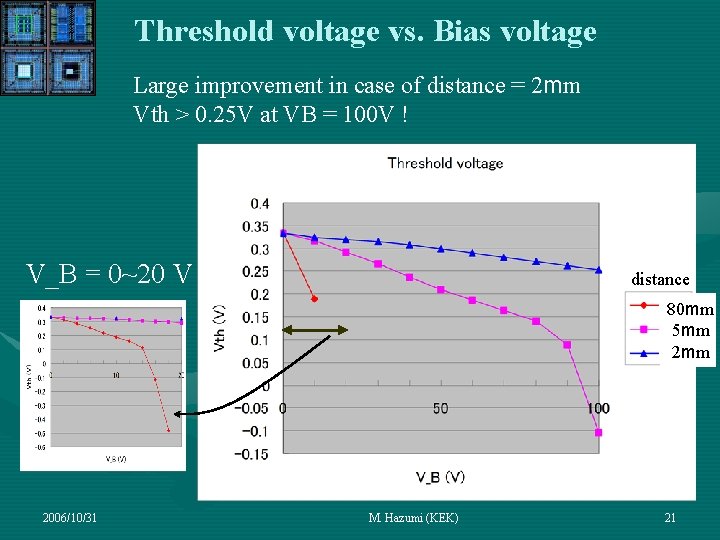

Threshold voltage vs. Bias voltage Large improvement in case of distance = 2 mm Vth > 0. 25 V at VB = 100 V ! V_B = 0~20 V distance 80 mm 5 mm 2006/10/31 M. Hazumi (KEK) 21

P-substrate option 2006/10/31 M. Hazumi (KEK) 22

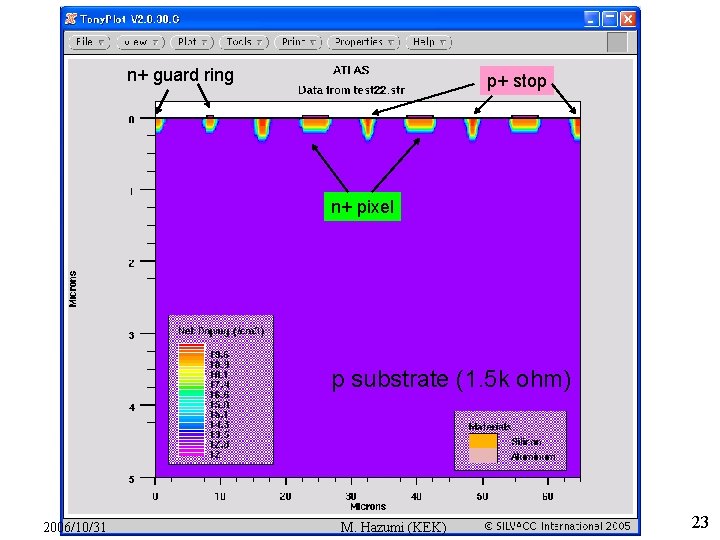

n+ guard ring p+ stop n+ pixel p substrate (1. 5 k ohm) 2006/10/31 M. Hazumi (KEK) 23

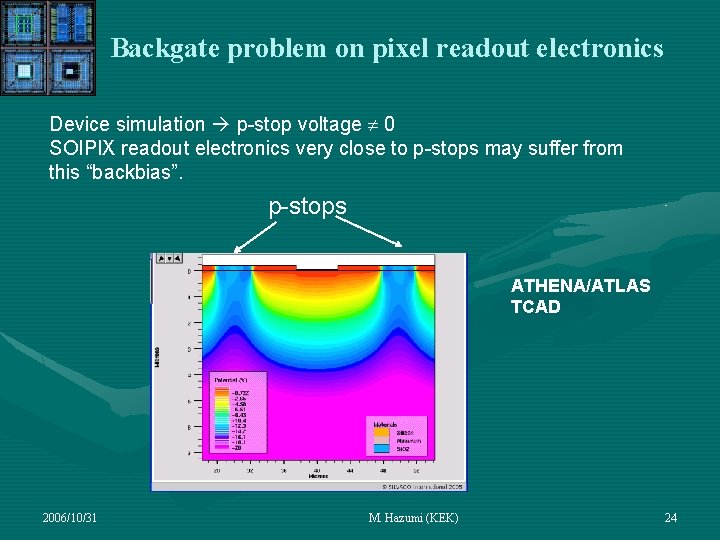

Backgate problem on pixel readout electronics Device simulation p-stop voltage 0 SOIPIX readout electronics very close to p-stops may suffer from this “backbias”. p-stops ATHENA/ATLAS TCAD 2006/10/31 M. Hazumi (KEK) 24

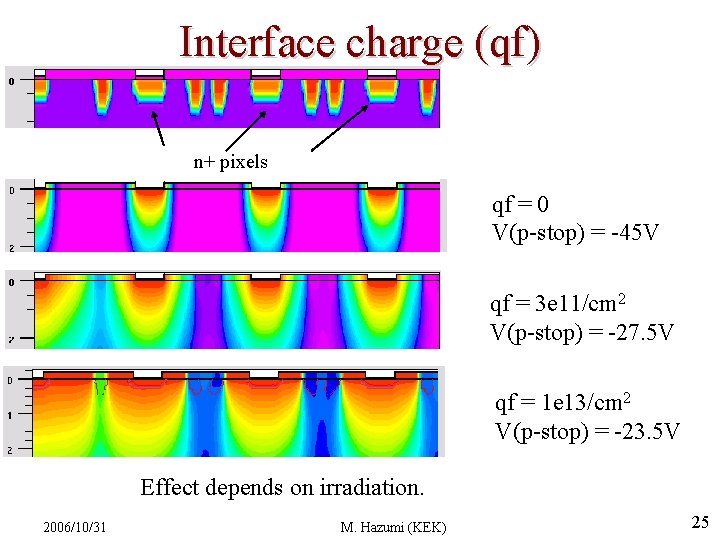

Interface charge (qf) n+ pixels qf = 0 V(p-stop) = -45 V qf = 3 e 11/cm 2 V(p-stop) = -27. 5 V qf = 1 e 13/cm 2 V(p-stop) = -23. 5 V Effect depends on irradiation. 2006/10/31 M. Hazumi (KEK) 25

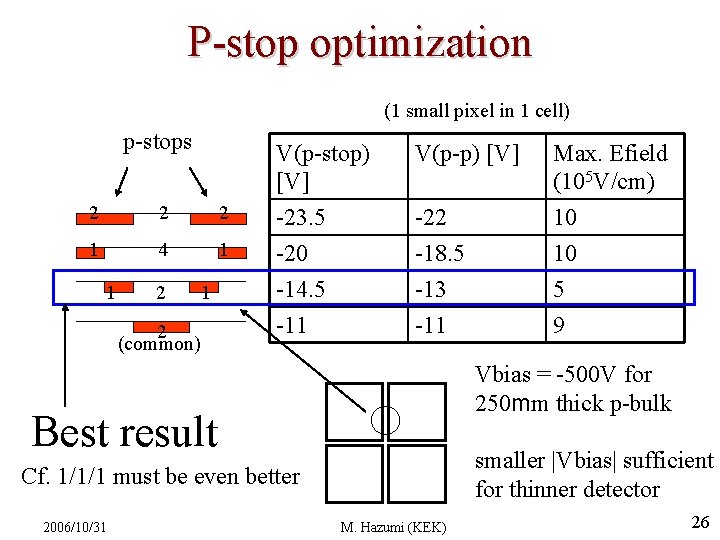

P-stop optimization (1 small pixel in 1 cell) p-stops 2 2 2 1 4 1 1 2 (common) V(p-stop) [V] V(p-p) [V] Max. Efield (105 V/cm) -23. 5 -20 -14. 5 -11 -22 -18. 5 -13 -11 10 10 5 9 Vbias = -500 V for 250 mm thick p-bulk Best result smaller |Vbias| sufficient for thinner detector Cf. 1/1/1 must be even better 2006/10/31 M. Hazumi (KEK) 26

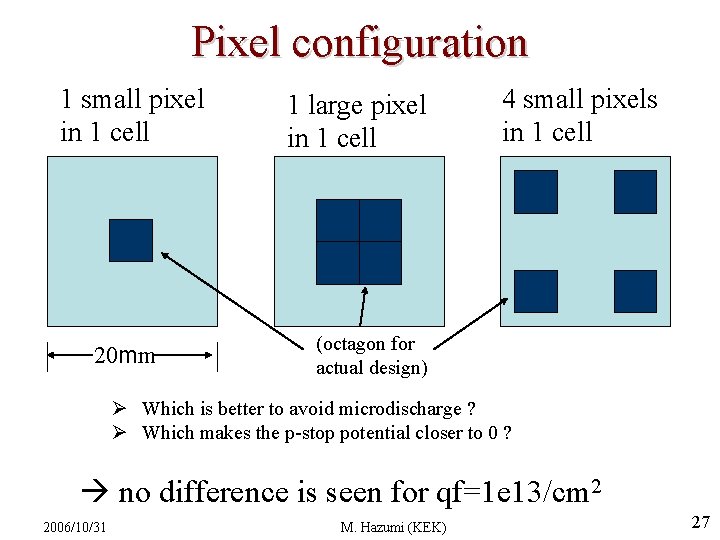

Pixel configuration 1 small pixel in 1 cell 20 mm 1 large pixel in 1 cell 4 small pixels in 1 cell (octagon for actual design) Ø Which is better to avoid microdischarge ? Ø Which makes the p-stop potential closer to 0 ? no difference is seen for qf=1 e 13/cm 2 2006/10/31 M. Hazumi (KEK) 27

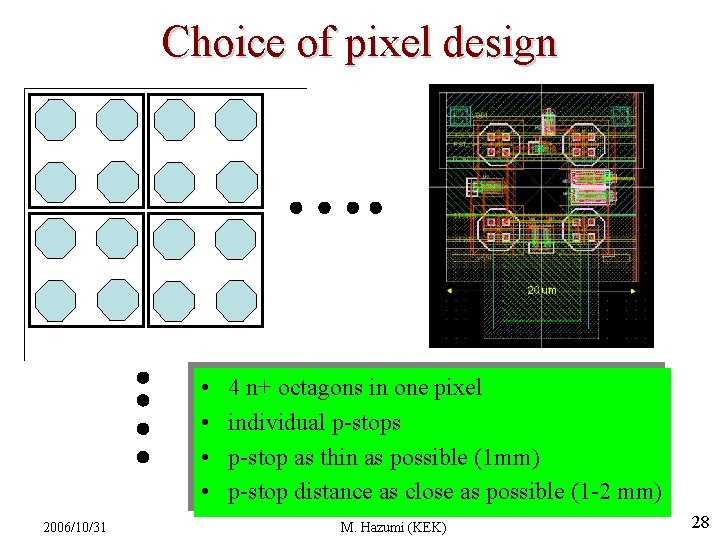

Choice of pixel design • • 2006/10/31 4 n+ octagons in one pixel individual p-stops p-stop as thin as possible (1 mm) p-stop distance as close as possible (1 -2 mm) M. Hazumi (KEK) 28

Summary • Handle wafer (i. e. sensor) simulation – Pixel and guard ring design optimization • Breakdown voltage well understood and new designs proposed – Problem finding/solving before fabrication • Effect of bias voltage on readout electronics – New P+ bias rings proposed for I/O pads – P-substrate option seems more complicated because of p-stops • TCAD is very useful for SOIPIX R&D ! 2006/10/31 M. Hazumi (KEK) 29

Backup Slides 2006/10/31 M. Hazumi (KEK) 30

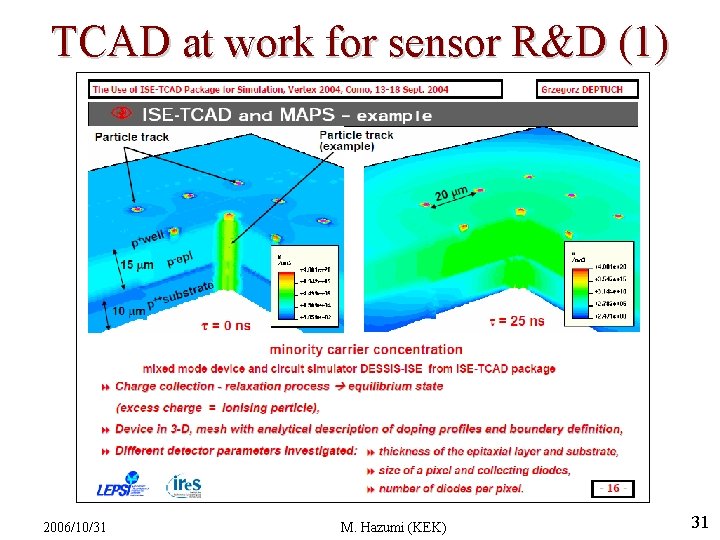

TCAD at work for sensor R&D (1) 2006/10/31 M. Hazumi (KEK) 31

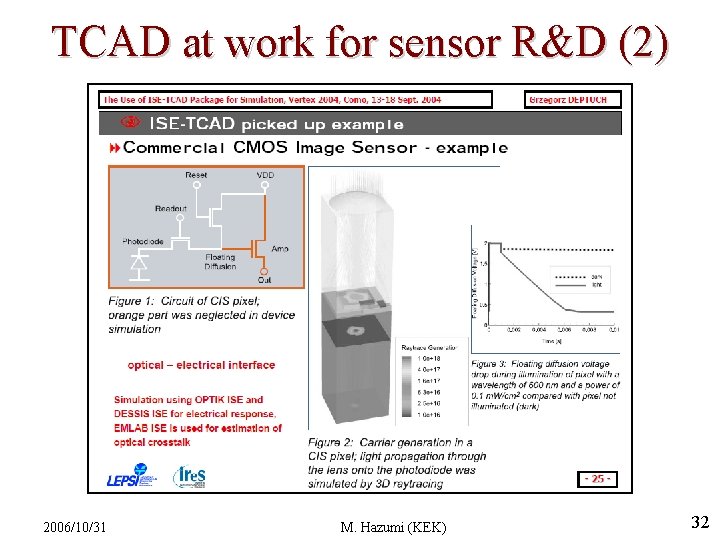

TCAD at work for sensor R&D (2) 2006/10/31 M. Hazumi (KEK) 32

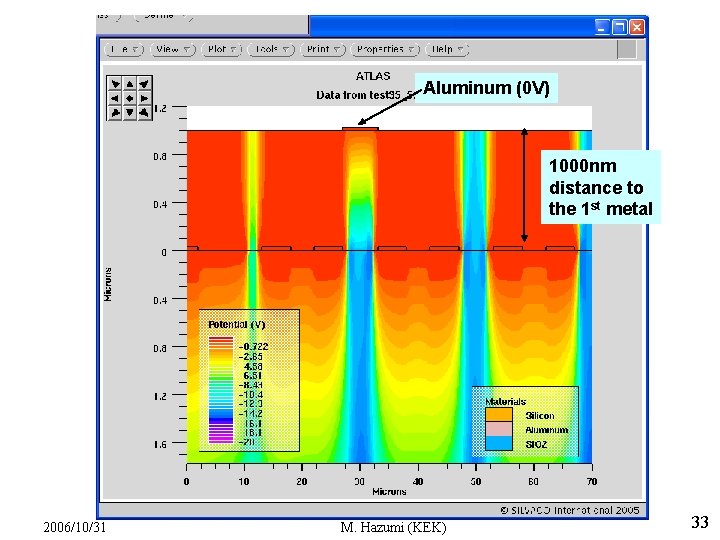

Aluminum (0 V) 1000 nm distance to the 1 st metal 2006/10/31 M. Hazumi (KEK) 33

End 2006/10/31 M. Hazumi (KEK) 34

- Slides: 34