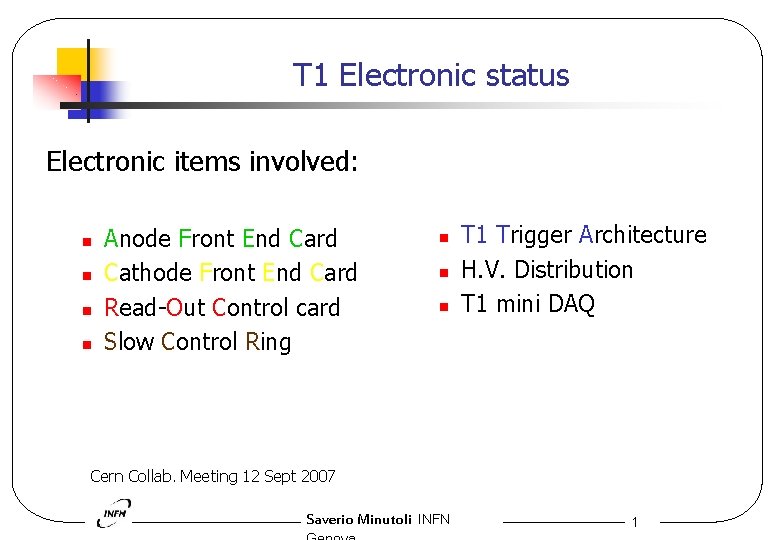

T 1 Electronic status Electronic items involved n

- Slides: 15

T 1 Electronic status Electronic items involved: n n Anode Front End Card Cathode Front End Card Read-Out Control card Slow Control Ring n n n T 1 Trigger Architecture H. V. Distribution T 1 mini DAQ Cern Collab. Meeting 12 Sept 2007 Saverio Minutoli INFN 1

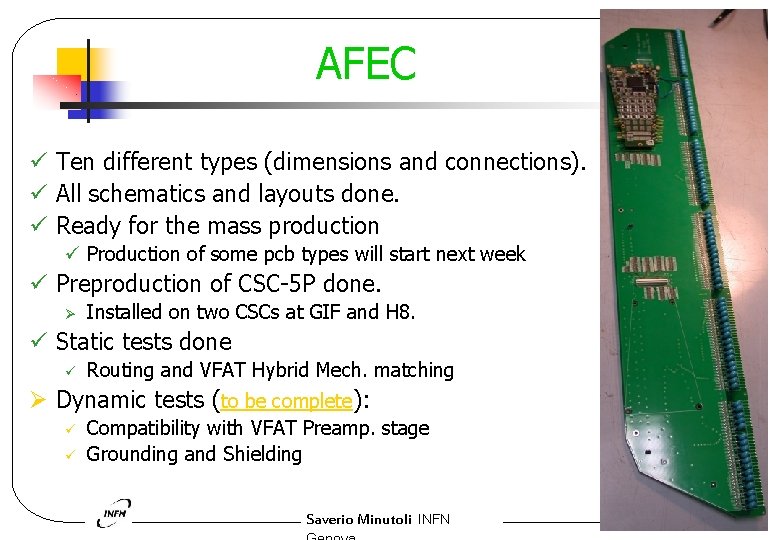

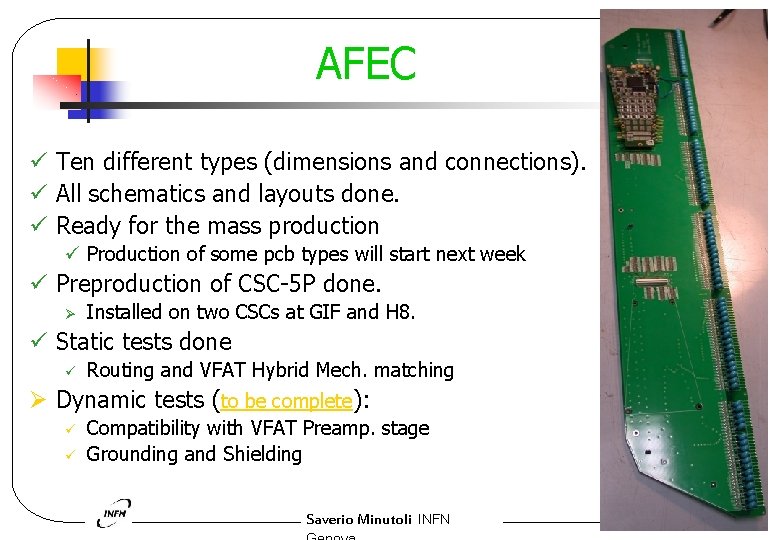

AFEC ü Ten different types (dimensions and connections). ü All schematics and layouts done. ü Ready for the mass production ü Production of some pcb types will start next week ü Preproduction of CSC-5 P done. Ø Installed on two CSCs at GIF and H 8. ü Static tests done ü Routing and VFAT Hybrid Mech. matching Ø Dynamic tests (to be complete): ü ü Compatibility with VFAT Preamp. stage Grounding and Shielding Saverio Minutoli INFN 2

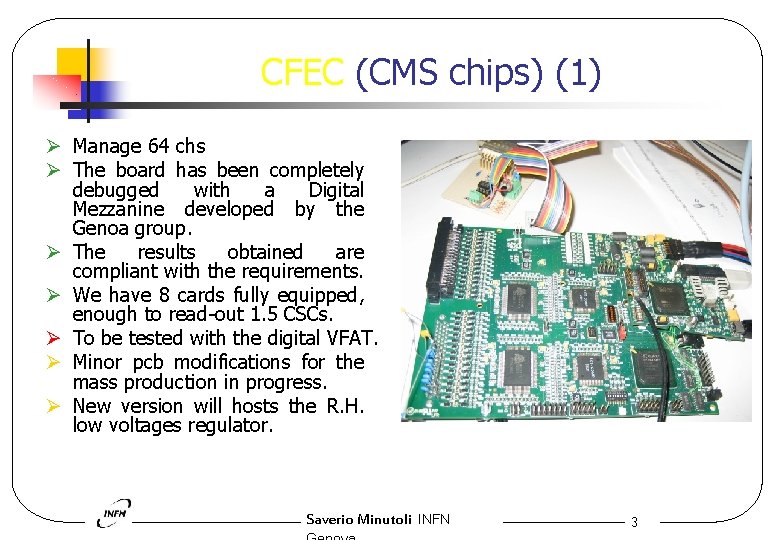

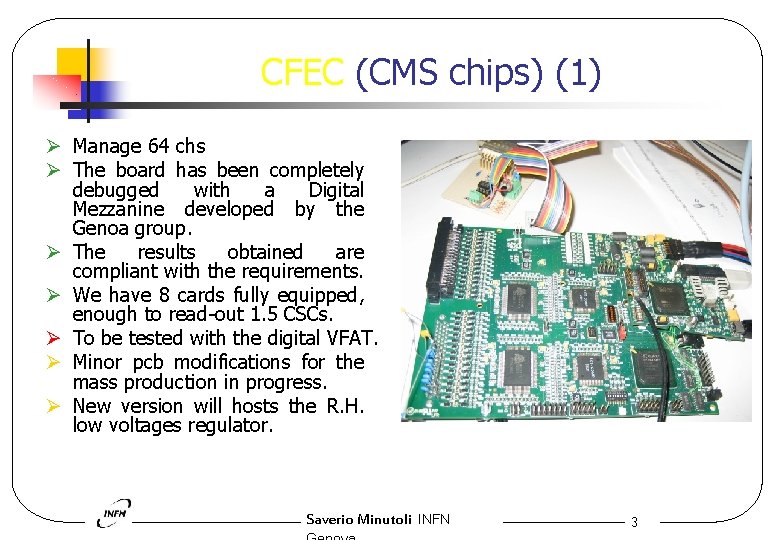

CFEC (CMS chips) (1) Ø Manage 64 chs Ø The board has been completely debugged with a Digital Mezzanine developed by the Genoa group. Ø The results obtained are compliant with the requirements. Ø We have 8 cards fully equipped, enough to read-out 1. 5 CSCs. Ø To be tested with the digital VFAT. Ø Minor pcb modifications for the mass production in progress. Ø New version will hosts the R. H. low voltages regulator. Saverio Minutoli INFN 3

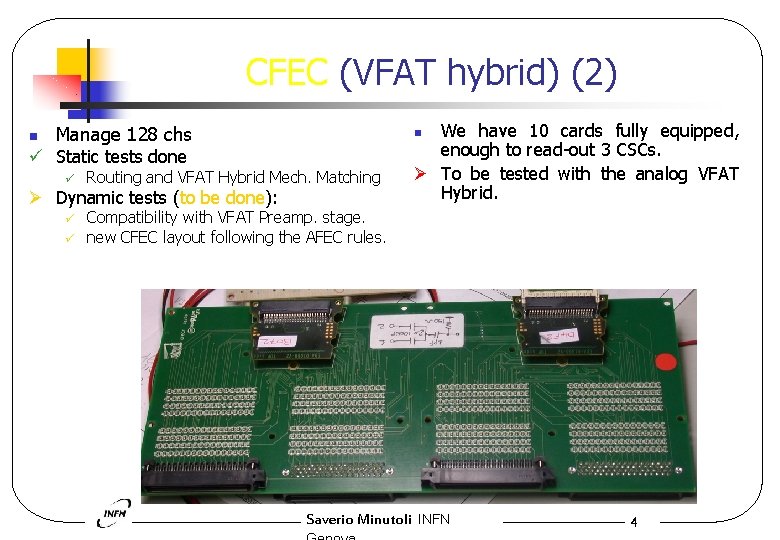

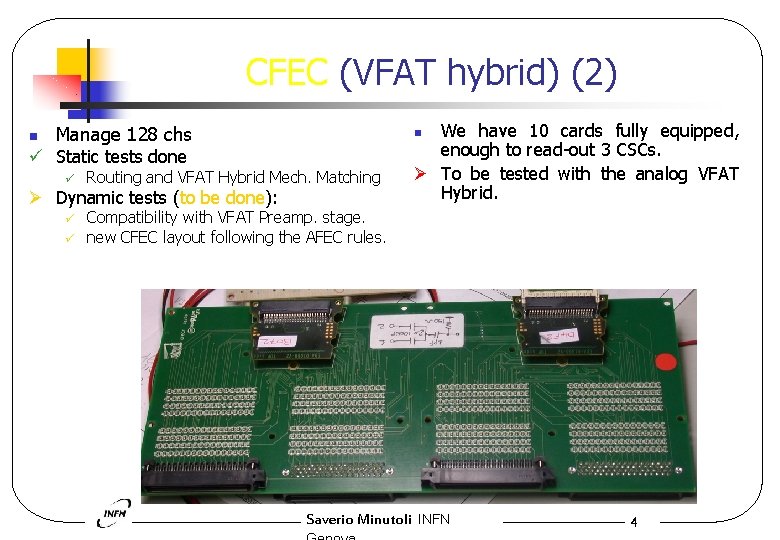

CFEC (VFAT hybrid) (2) n Manage 128 chs ü Static tests done ü Routing and VFAT Hybrid Mech. Matching Ø Dynamic tests (to be done): ü ü We have 10 cards fully equipped, enough to read-out 3 CSCs. Ø To be tested with the analog VFAT Hybrid. n Compatibility with VFAT Preamp. stage. new CFEC layout following the AFEC rules. Saverio Minutoli INFN 4

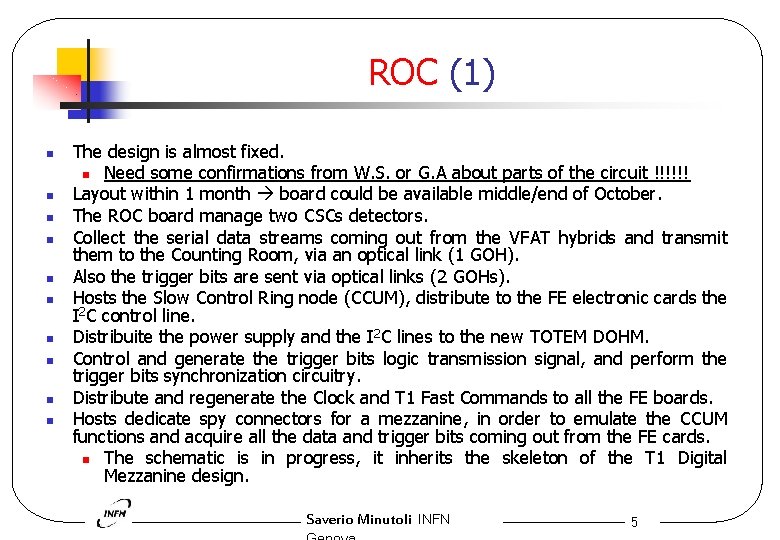

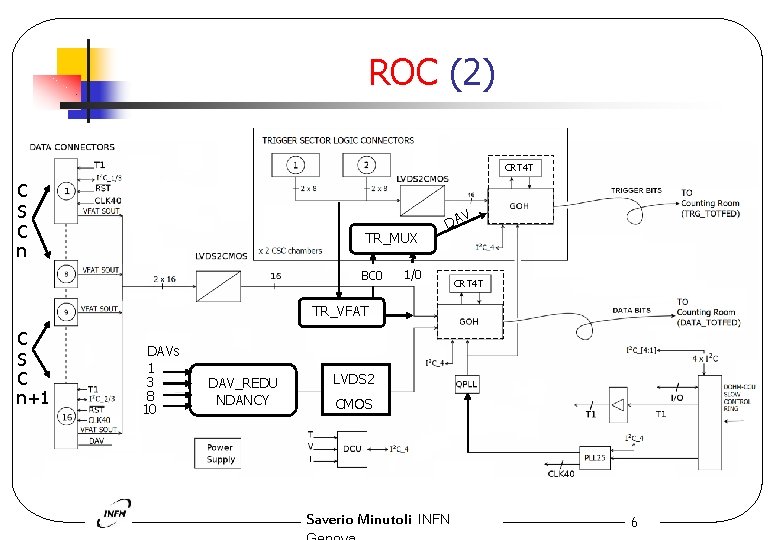

ROC (1) n n n n n The design is almost fixed. n Need some confirmations from W. S. or G. A about parts of the circuit !!!!!! Layout within 1 month board could be available middle/end of October. The ROC board manage two CSCs detectors. Collect the serial data streams coming out from the VFAT hybrids and transmit them to the Counting Room, via an optical link (1 GOH). Also the trigger bits are sent via optical links (2 GOHs). Hosts the Slow Control Ring node (CCUM), distribute to the FE electronic cards the I 2 C control line. Distribuite the power supply and the I 2 C lines to the new TOTEM DOHM. Control and generate the trigger bits logic transmission signal, and perform the trigger bits synchronization circuitry. Distribute and regenerate the Clock and T 1 Fast Commands to all the FE boards. Hosts dedicate spy connectors for a mezzanine, in order to emulate the CCUM functions and acquire all the data and trigger bits coming out from the FE cards. n The schematic is in progress, it inherits the skeleton of the T 1 Digital Mezzanine design. Saverio Minutoli INFN 5

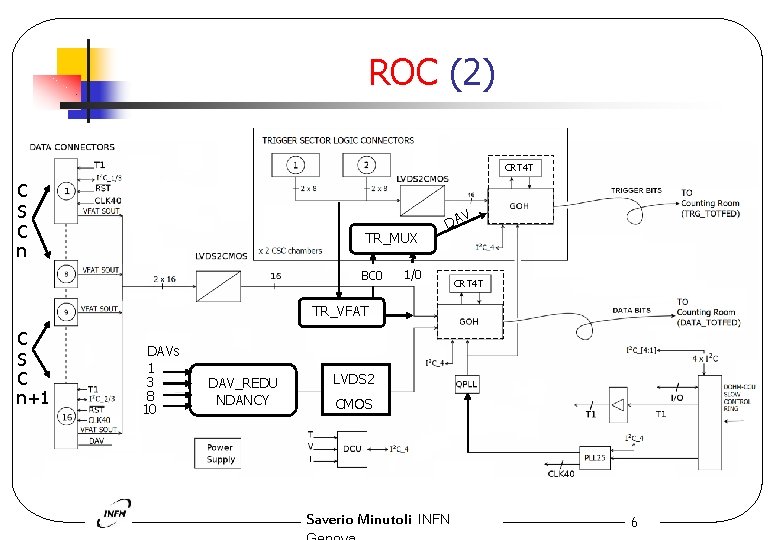

ROC (2) CRT 4 T C S C n V TR_MUX BC 0 DA 1/0 CRT 4 T TR_VFAT C S C n+1 DAVs 1 3 8 10 DAV_REDU NDANCY LVDS 2 CMOS Saverio Minutoli INFN 6

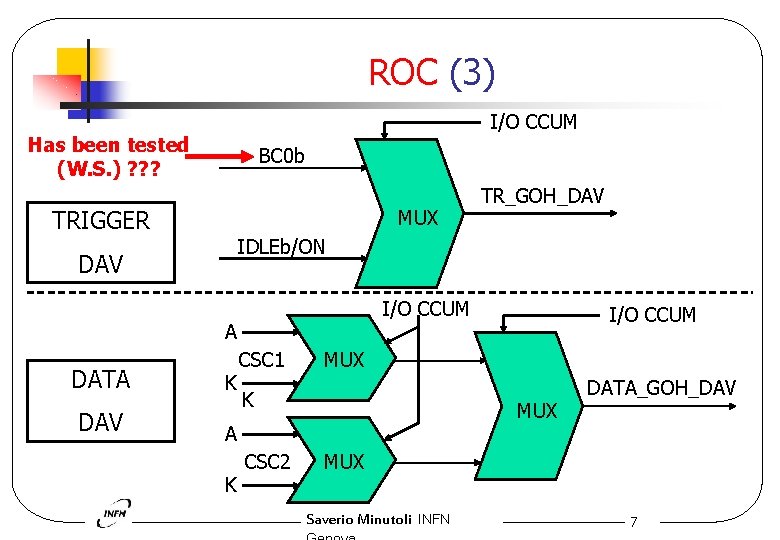

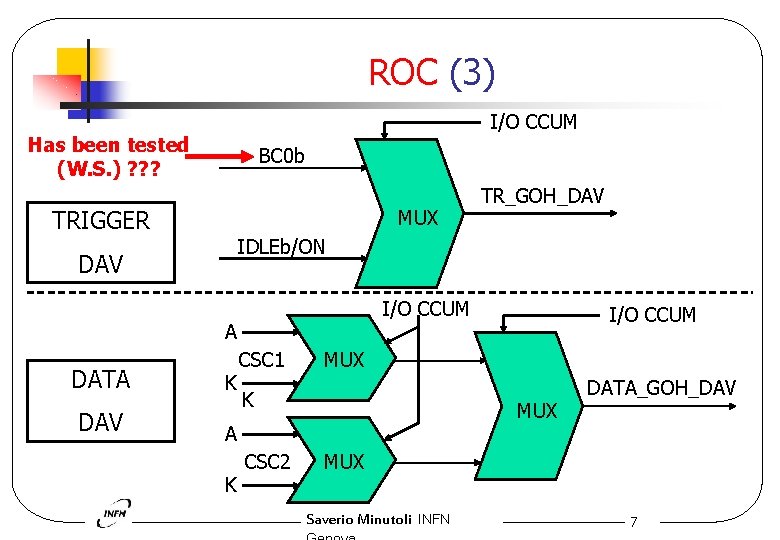

ROC (3) I/O CCUM Has been tested (W. S. ) ? ? ? BC 0 b TRIGGER MUX IDLEb/ON DAV I/O CCUM A DATA DAV TR_GOH_DAV K CSC 1 MUX K MUX A K CSC 2 I/O CCUM DATA_GOH_DAV MUX Saverio Minutoli INFN 7

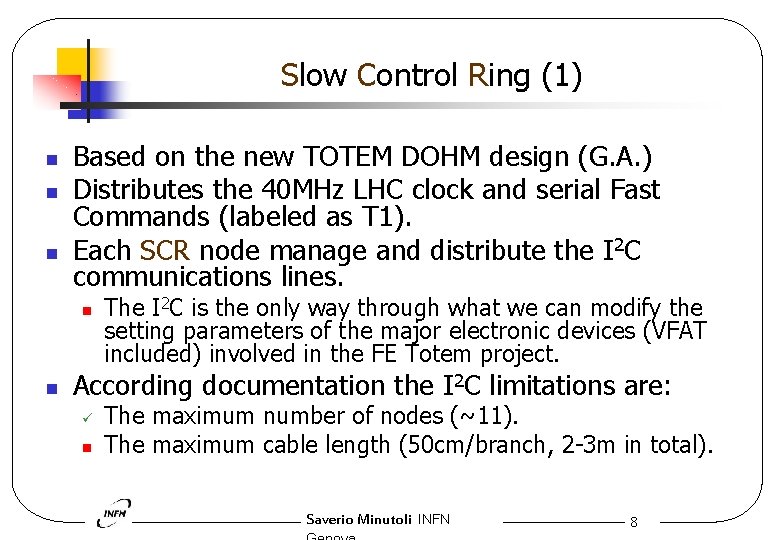

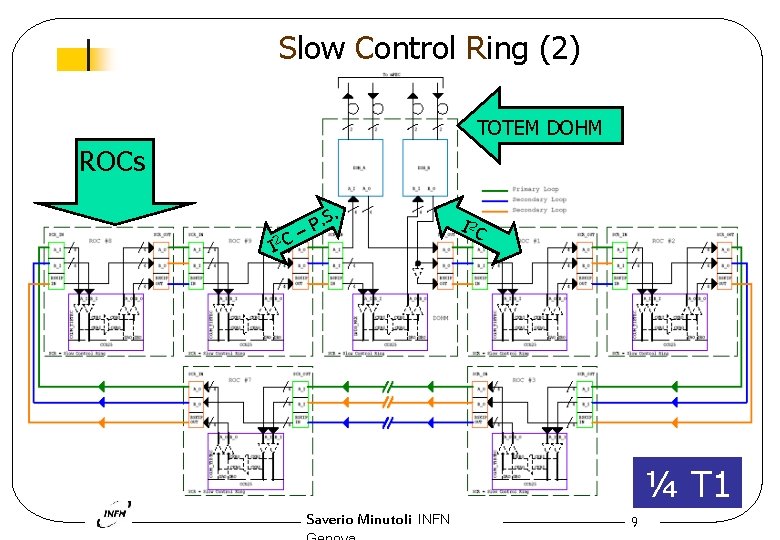

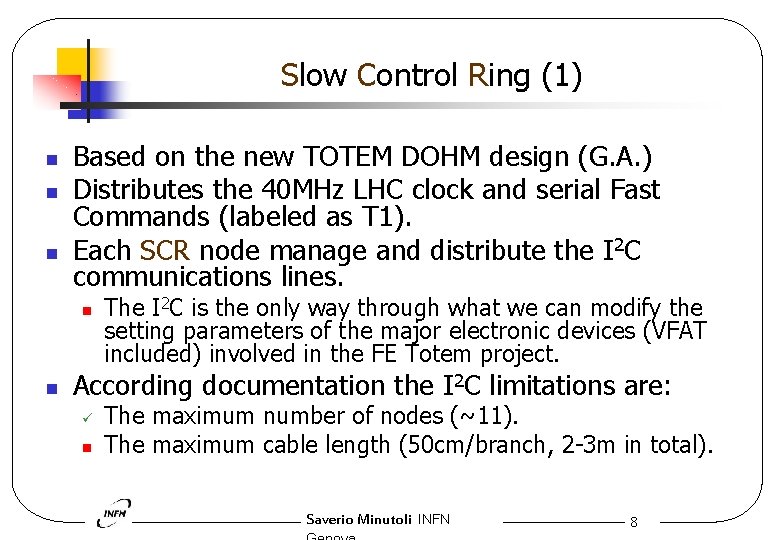

Slow Control Ring (1) n n n Based on the new TOTEM DOHM design (G. A. ) Distributes the 40 MHz LHC clock and serial Fast Commands (labeled as T 1). Each SCR node manage and distribute the I 2 C communications lines. n n The I 2 C is the only way through what we can modify the setting parameters of the major electronic devices (VFAT included) involved in the FE Totem project. According documentation the I 2 C limitations are: ü n The maximum number of nodes (~11). The maximum cable length (50 cm/branch, 2 -3 m in total). Saverio Minutoli INFN 8

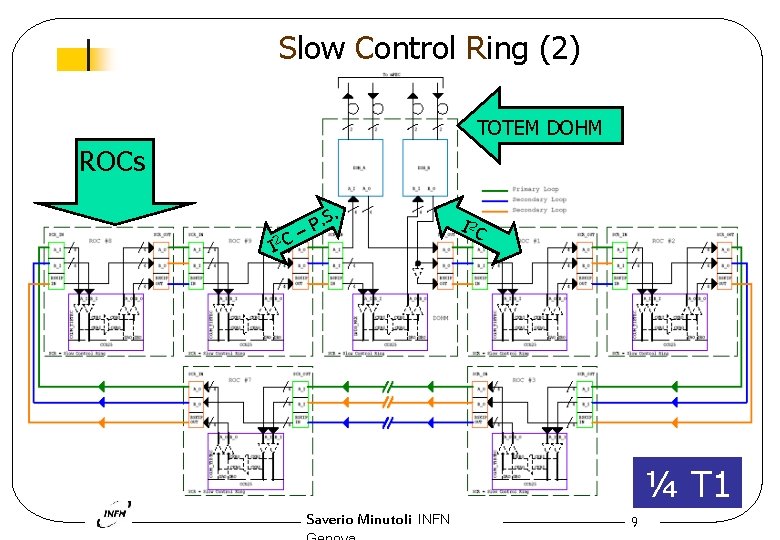

Slow Control Ring (2) TOTEM DOHM ROCs. I 2 C . S –P I 2 C ¼ T 1 Saverio Minutoli INFN 9

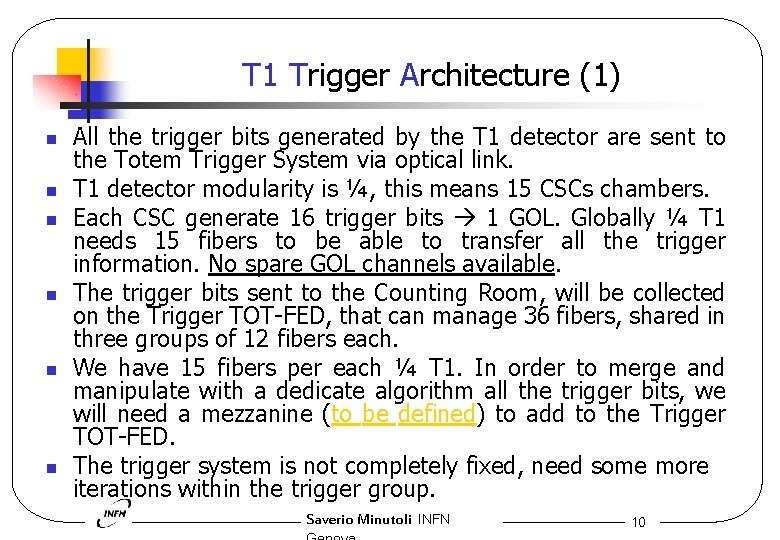

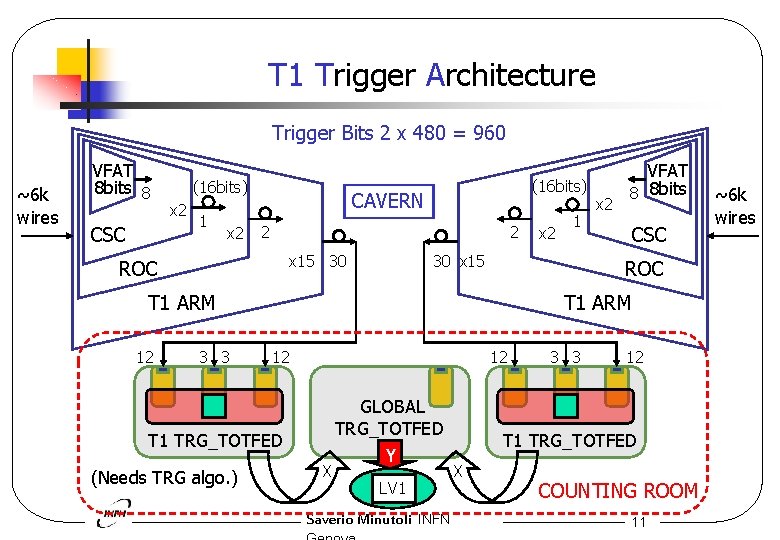

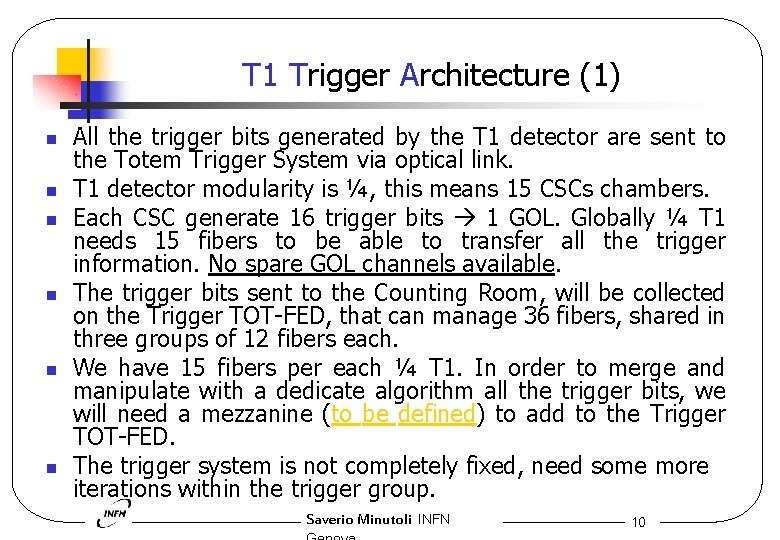

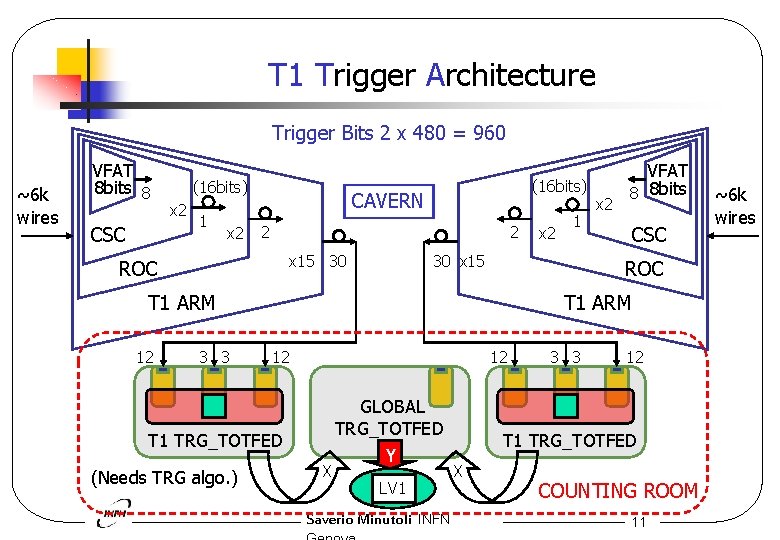

T 1 Trigger Architecture (1) n n n All the trigger bits generated by the T 1 detector are sent to the Totem Trigger System via optical link. T 1 detector modularity is ¼, this means 15 CSCs chambers. Each CSC generate 16 trigger bits 1 GOL. Globally ¼ T 1 needs 15 fibers to be able to transfer all the trigger information. No spare GOL channels available. The trigger bits sent to the Counting Room, will be collected on the Trigger TOT-FED, that can manage 36 fibers, shared in three groups of 12 fibers each. We have 15 fibers per each ¼ T 1. In order to merge and manipulate with a dedicate algorithm all the trigger bits, we will need a mezzanine (to be defined) to add to the Trigger TOT-FED. The trigger system is not completely fixed, need some more iterations within the trigger group. Saverio Minutoli INFN 10

T 1 Trigger Architecture Trigger Bits 2 x 480 = 960 ~6 k wires VFAT 8 bits 8 CSC (16 bits) x 2 1 x 2 (16 bits) CAVERN 2 2 x 15 30 ROC 3 3 CSC ROC T 1 ARM 12 12 T 1 TRG_TOTFED (Needs TRG algo. ) 1 30 x 15 T 1 ARM 12 x 2 VFAT 8 8 bits X GLOBAL TRG_TOTFED Y LV 1 Saverio Minutoli INFN 3 3 12 T 1 TRG_TOTFED X COUNTING ROOM 11 ~6 k wires

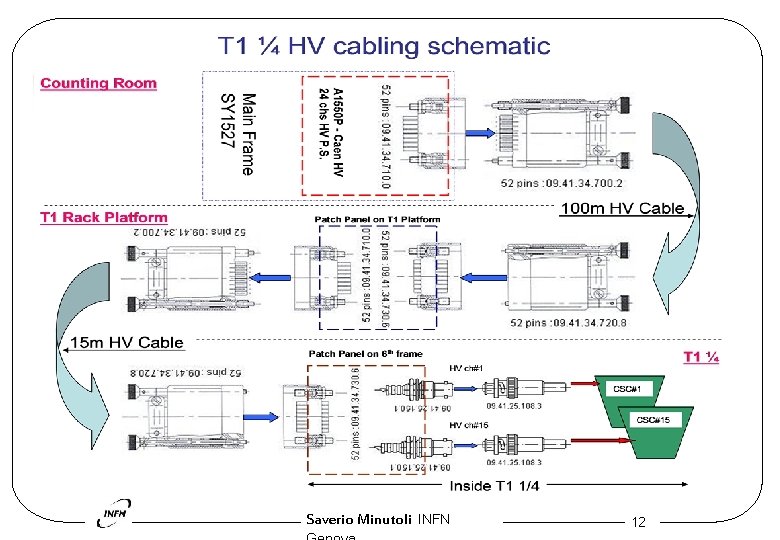

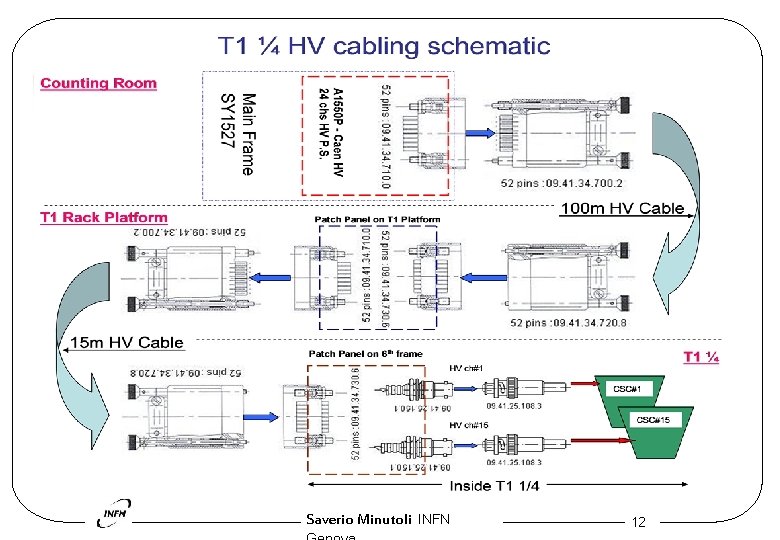

Saverio Minutoli INFN 12

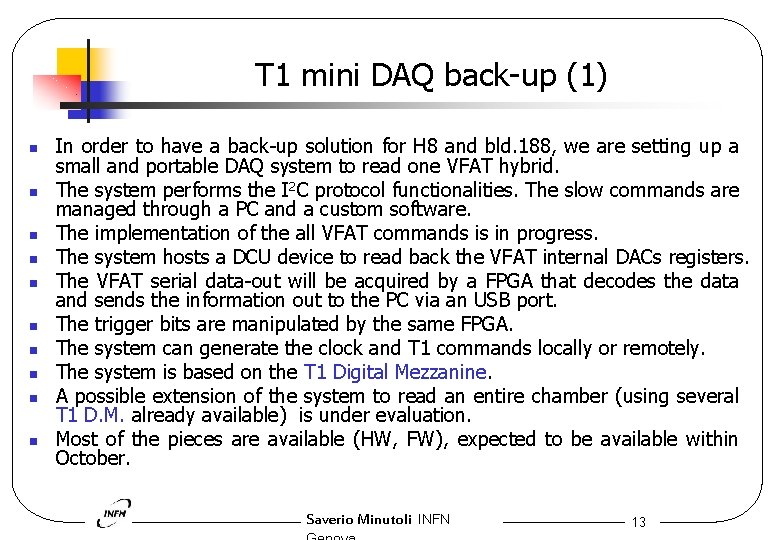

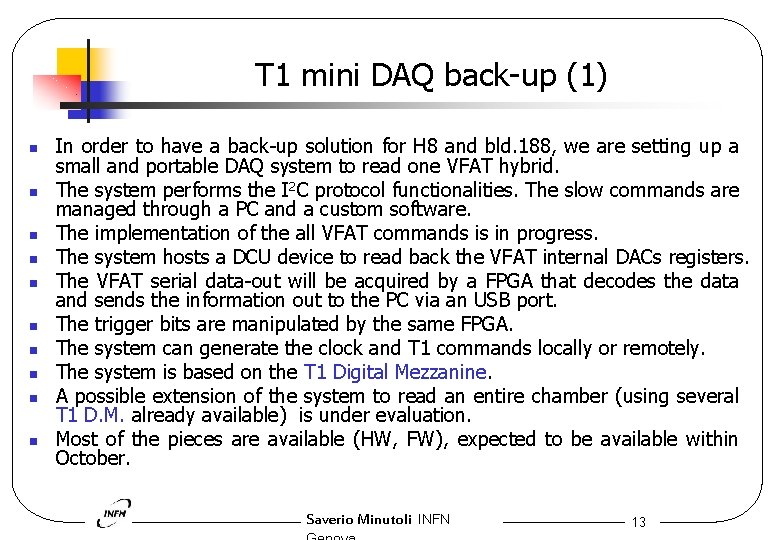

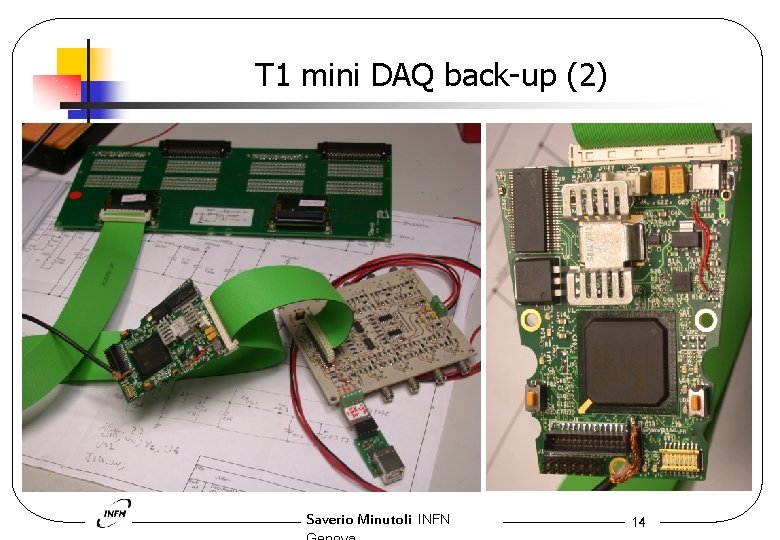

T 1 mini DAQ back-up (1) n n n n n In order to have a back-up solution for H 8 and bld. 188, we are setting up a small and portable DAQ system to read one VFAT hybrid. The system performs the I 2 C protocol functionalities. The slow commands are managed through a PC and a custom software. The implementation of the all VFAT commands is in progress. The system hosts a DCU device to read back the VFAT internal DACs registers. The VFAT serial data-out will be acquired by a FPGA that decodes the data and sends the information out to the PC via an USB port. The trigger bits are manipulated by the same FPGA. The system can generate the clock and T 1 commands locally or remotely. The system is based on the T 1 Digital Mezzanine. A possible extension of the system to read an entire chamber (using several T 1 D. M. already available) is under evaluation. Most of the pieces are available (HW, FW), expected to be available within October. Saverio Minutoli INFN 13

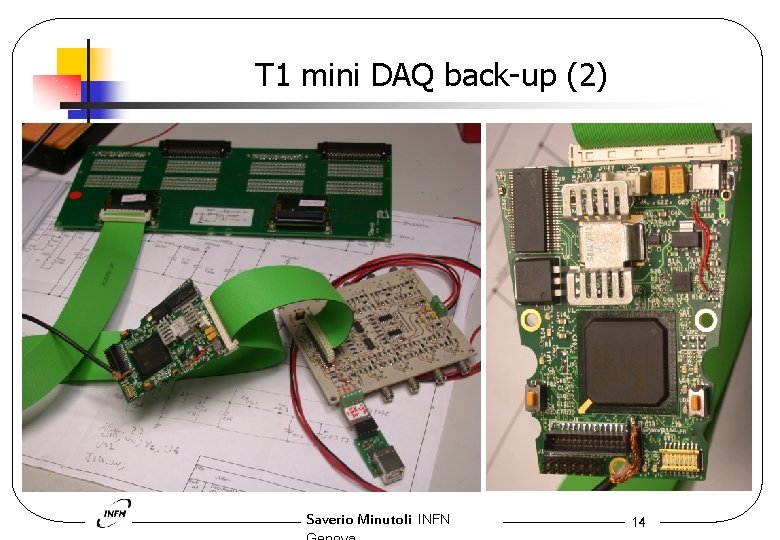

T 1 mini DAQ back-up (2) Saverio Minutoli INFN 14

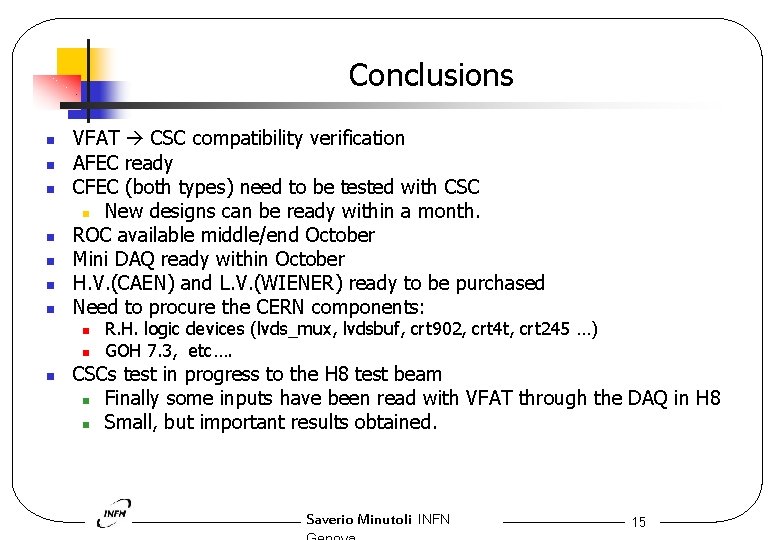

Conclusions n n n n VFAT CSC compatibility verification AFEC ready CFEC (both types) need to be tested with CSC n New designs can be ready within a month. ROC available middle/end October Mini DAQ ready within October H. V. (CAEN) and L. V. (WIENER) ready to be purchased Need to procure the CERN components: n n n R. H. logic devices (lvds_mux, lvdsbuf, crt 902, crt 4 t, crt 245 …) GOH 7. 3, etc…. CSCs test in progress to the H 8 test beam n Finally some inputs have been read with VFAT through the DAQ in H 8 n Small, but important results obtained. Saverio Minutoli INFN 15