Systme dexploitation Assembleur Semaine 05 Modes dadressage Les

Système d’exploitation : Assembleur Semaine 05 Modes d’adressage

Les différents modes d’adressage 1/6 • On appelle mode d'adressage la manière dont la donnée est spécifiée dans une instruction. Selon le mode d'adressage la taille de l'instruction peut varier de 1 à 4 octets. • Le mode d'adressage implicite correspond à une instruction ne comportant pas d'opérande. L'instruction est uniquement composée du code opération. Sa taille peut varier entre 1 octet et 2 octets selon l'opération. Ce type d'instruction porte généralement sur des registres. Les opérations d'incrémentation ou de décrémentation d'un registre ont un mode d'adressage implicite. • Exemple: – INC AX

Les différents modes d’adressage 2/6 • Le mode d'adressage immédiat On parle de mode d'adressage immédiat quand le code opérande contient une donnée. La taille de la donnée peut varier entre 1 et 2 octets. Ce type d'instruction met en jeu un registre et une valeur. La taille de l'opérande dépendra donc du type de registre mis en jeu (1 octet pour un registre 8 bits, 2 pour un registre de 16 bits). • Exemple: – MOV BX, 13 L'opérande 13 sera codée sur 16 bits puisqu'il faut l'affecter à un registre 16 bits (BX). – MOV AH, 11 L'opérande 11 sera codée sur 8 bits puisqu'il faut l'affecter à un registre 8 bits (AH). – dummy DB 5 ADD AL, dummy L'opérande 5 sera codée sur 8 bits puisqu'il faut l'affecter à un registre 8 bits (AL).

Les différents modes d’adressage 3/6 • Le mode d'adressage relatif met en jeu un champ opérande contenant un entier relatif (sa taille est donc un octet). Il est utilisé dans les opérations de saut (JMP), l'entier relatif étant appelé déplacement et correspondant à la longueur du saut que le processeur doit effectuer dans les instructions. • Exemple: – 0100 0103 0104 La valeur ADD AX, 02 h JMP 0100 h … du déplacement sera 0100 h-0104 h = -4

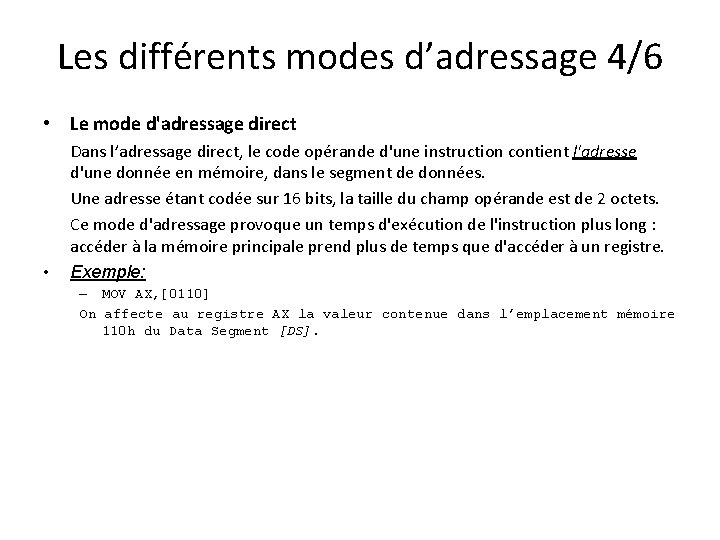

Les différents modes d’adressage 4/6 • Le mode d'adressage direct • Dans l’adressage direct, le code opérande d'une instruction contient l'adresse d'une donnée en mémoire, dans le segment de données. Une adresse étant codée sur 16 bits, la taille du champ opérande est de 2 octets. Ce mode d'adressage provoque un temps d'exécution de l'instruction plus long : accéder à la mémoire principale prend plus de temps que d'accéder à un registre. Exemple: – MOV AX, [0110] On affecte au registre AX la valeur contenue dans l’emplacement mémoire 110 h du Data Segment [DS].

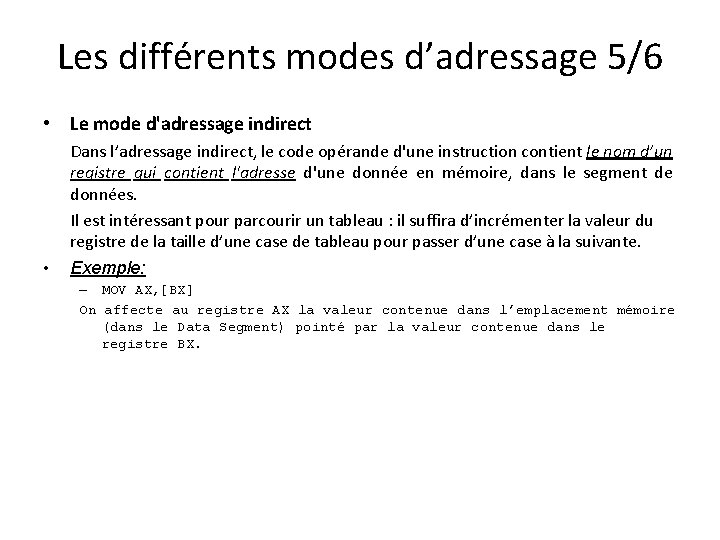

Les différents modes d’adressage 5/6 • Le mode d'adressage indirect • Dans l’adressage indirect, le code opérande d'une instruction contient le nom d’un registre qui contient l'adresse d'une donnée en mémoire, dans le segment de données. Il est intéressant pour parcourir un tableau : il suffira d’incrémenter la valeur du registre de la taille d’une case de tableau pour passer d’une case à la suivante. Exemple: – MOV AX, [BX] On affecte au registre AX la valeur contenue dans l’emplacement mémoire (dans le Data Segment) pointé par la valeur contenue dans le registre BX.

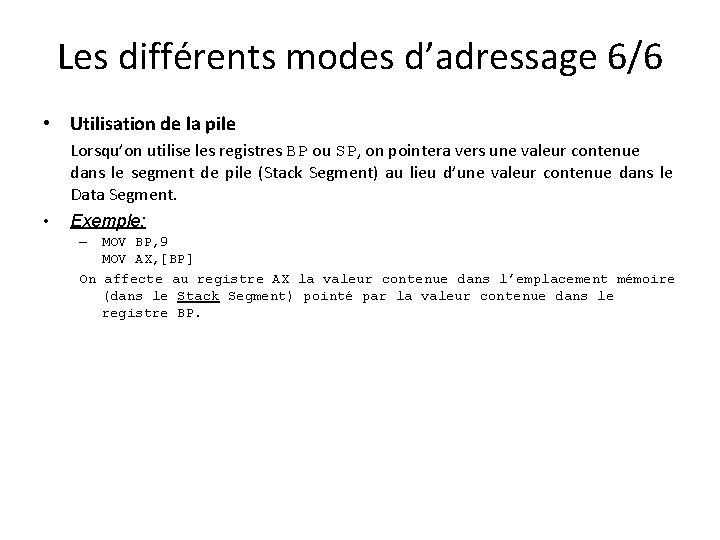

Les différents modes d’adressage 6/6 • Utilisation de la pile • Lorsqu’on utilise les registres BP ou SP, on pointera vers une valeur contenue dans le segment de pile (Stack Segment) au lieu d’une valeur contenue dans le Data Segment. Exemple: – MOV BP, 9 MOV AX, [BP] On affecte au registre AX la valeur contenue dans l’emplacement mémoire (dans le Stack Segment) pointé par la valeur contenue dans le registre BP.

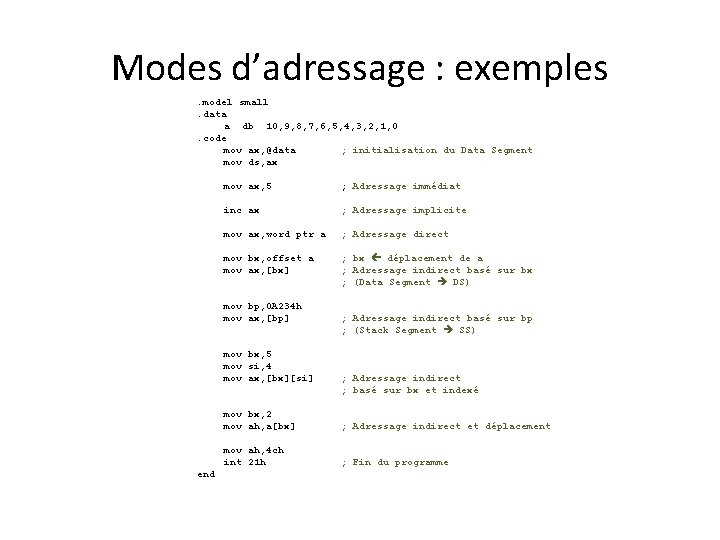

Modes d’adressage : exemples. model small. data a db 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0. code mov ax, @data ; initialisation du Data Segment mov ds, ax mov ax, 5 ; Adressage immédiat inc ax ; Adressage implicite mov ax, word ptr a ; Adressage direct mov bx, offset a mov ax, [bx] ; bx déplacement de a ; Adressage indirect basé sur bx ; (Data Segment DS) mov bp, 0 A 234 h mov ax, [bp] mov bx, 5 mov si, 4 mov ax, [bx][si] end ; Adressage indirect basé sur bp ; (Stack Segment SS) ; Adressage indirect ; basé sur bx et indexé mov bx, 2 mov ah, a[bx] ; Adressage indirect et déplacement mov ah, 4 ch int 21 h ; Fin du programme

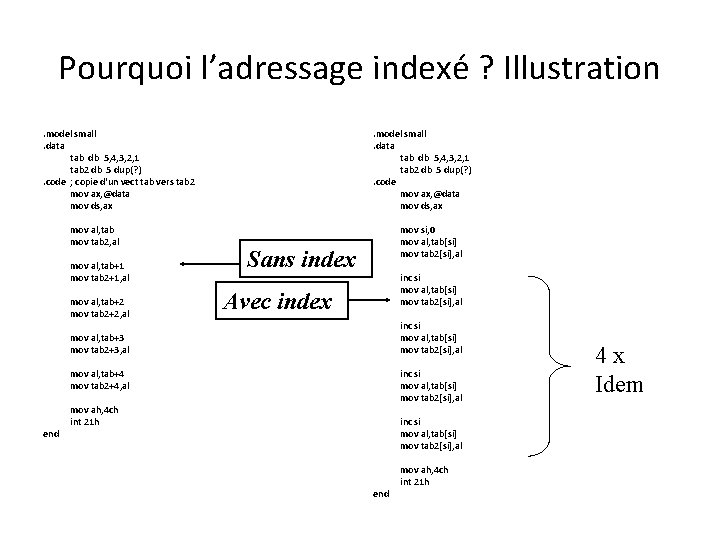

Pourquoi l’adressage indexé ? Illustration. model small. data tab db 5, 4, 3, 2, 1 tab 2 db 5 dup(? ). code ; copie d'un vect tab vers tab 2 mov ax, @data mov ds, ax mov al, tab mov tab 2, al mov al, tab+1 mov tab 2+1, al mov al, tab+2 mov tab 2+2, al . model small. data tab db 5, 4, 3, 2, 1 tab 2 db 5 dup(? ). code mov ax, @data mov ds, ax mov si, 0 mov al, tab[si] mov tab 2[si], al Sans index inc si mov al, tab[si] mov tab 2[si], al Avec index inc si mov al, tab[si] mov tab 2[si], al mov al, tab+3 mov tab 2+3, al mov al, tab+4 mov tab 2+4, al end inc si mov al, tab[si] mov tab 2[si], al mov ah, 4 ch int 21 h inc si mov al, tab[si] mov tab 2[si], al end mov ah, 4 ch int 21 h 4 x Idem

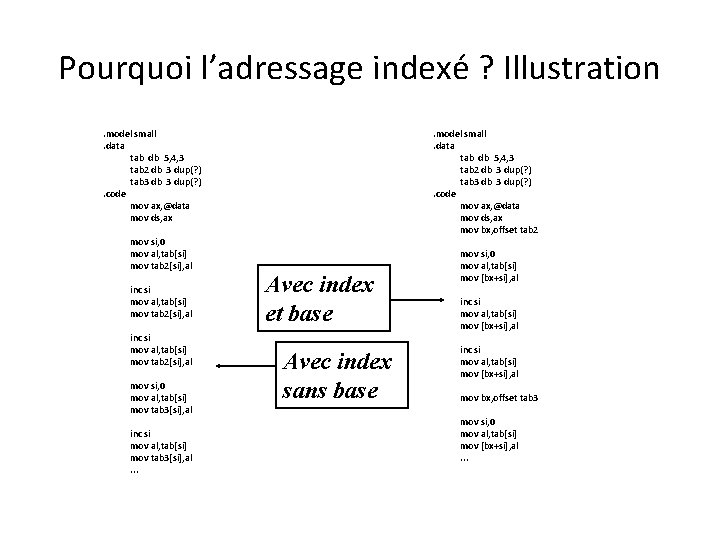

Pourquoi l’adressage indexé ? Illustration. model small. data tab db 5, 4, 3 tab 2 db 3 dup(? ) tab 3 dup(? ). code mov ax, @data mov ds, ax mov si, 0 mov al, tab[si] mov tab 2[si], al inc si mov al, tab[si] mov tab 2[si], al mov si, 0 mov al, tab[si] mov tab 3[si], al inc si mov al, tab[si] mov tab 3[si], al. . model small. data tab db 5, 4, 3 tab 2 db 3 dup(? ) tab 3 dup(? ). code mov ax, @data mov ds, ax mov bx, offset tab 2 Avec index et base Avec index sans base mov si, 0 mov al, tab[si] mov [bx+si], al inc si mov al, tab[si] mov [bx+si], al mov bx, offset tab 3 mov si, 0 mov al, tab[si] mov [bx+si], al. . .

- Slides: 10