Systems Engineering Project System Validation and Verification Using

- Slides: 27

Systems Engineering Project: System Validation and Verification Using SDL Ron Henry ENSE 623 November 30, 2004

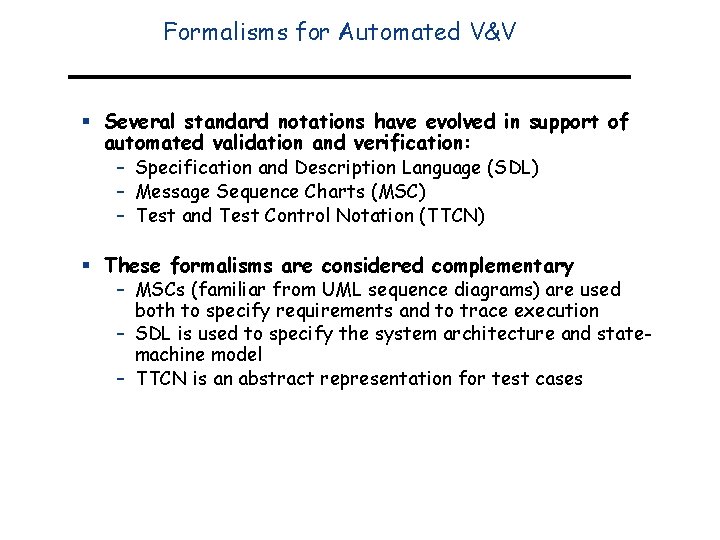

Formalisms for Automated V&V § Several standard notations have evolved in support of automated validation and verification: – Specification and Description Language (SDL) – Message Sequence Charts (MSC) – Test and Test Control Notation (TTCN) § These formalisms are considered complementary – MSCs (familiar from UML sequence diagrams) are used both to specify requirements and to trace execution – SDL is used to specify the system architecture and statemachine model – TTCN is an abstract representation for test cases

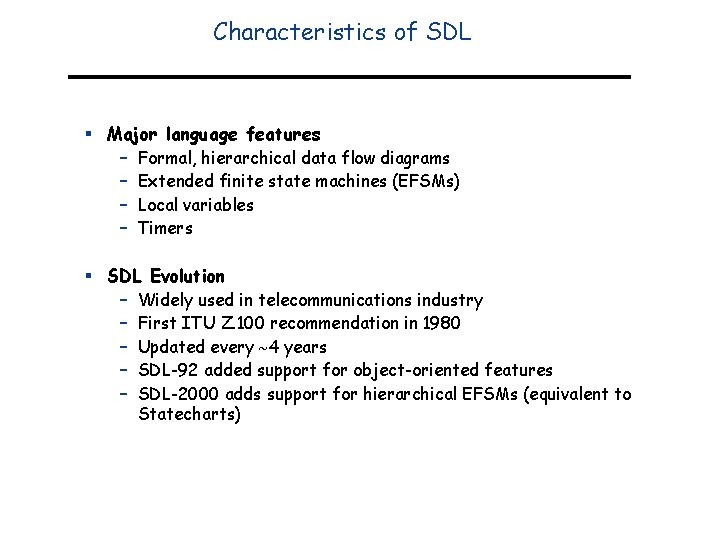

Characteristics of SDL § Major language features – – Formal, hierarchical data flow diagrams Extended finite state machines (EFSMs) Local variables Timers § SDL Evolution – – – Widely used in telecommunications industry First ITU Z. 100 recommendation in 1980 Updated every 4 years SDL-92 added support for object-oriented features SDL-2000 adds support for hierarchical EFSMs (equivalent to Statecharts)

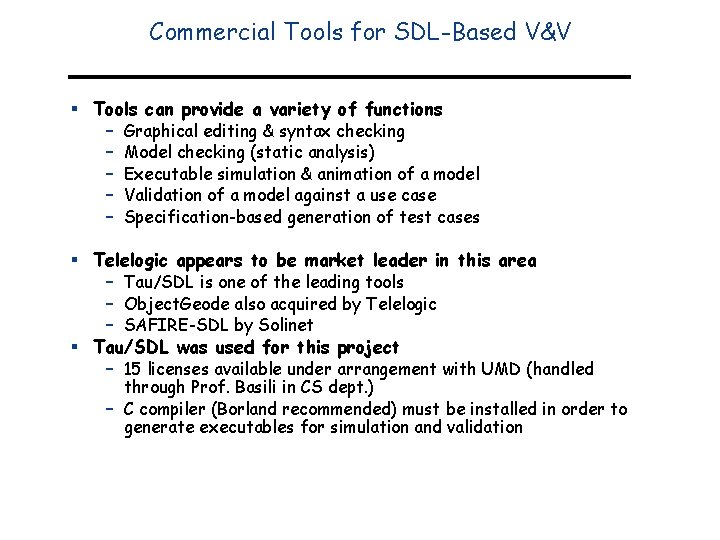

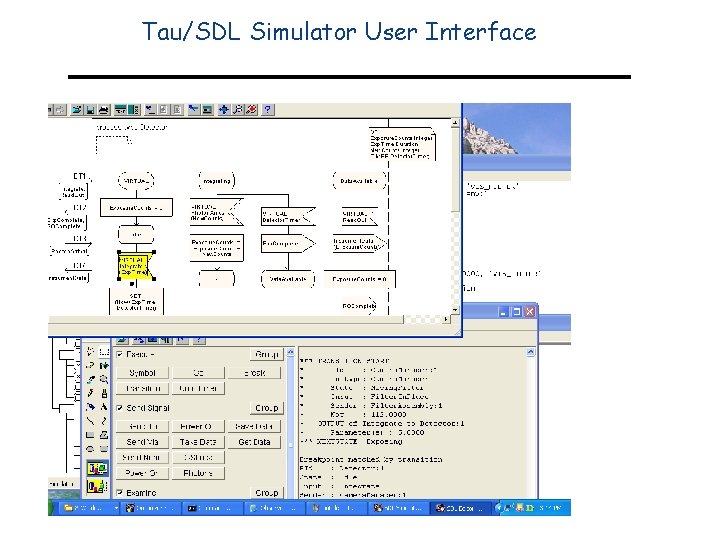

Commercial Tools for SDL-Based V&V § Tools can provide a variety of functions – – – Graphical editing & syntax checking Model checking (static analysis) Executable simulation & animation of a model Validation of a model against a use case Specification-based generation of test cases § Telelogic appears to be market leader in this area – Tau/SDL is one of the leading tools – Object. Geode also acquired by Telelogic – SAFIRE-SDL by Solinet § Tau/SDL was used for this project – 15 licenses available under arrangement with UMD (handled through Prof. Basili in CS dept. ) – C compiler (Borland recommended) must be installed in order to generate executables for simulation and validation

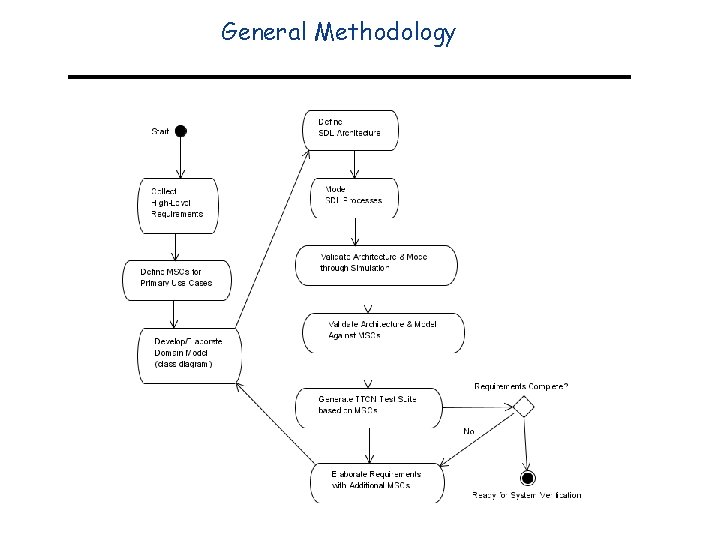

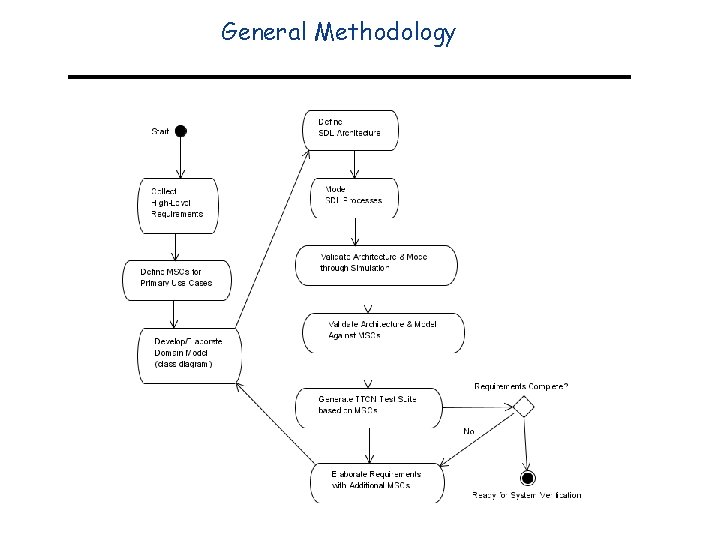

General Methodology

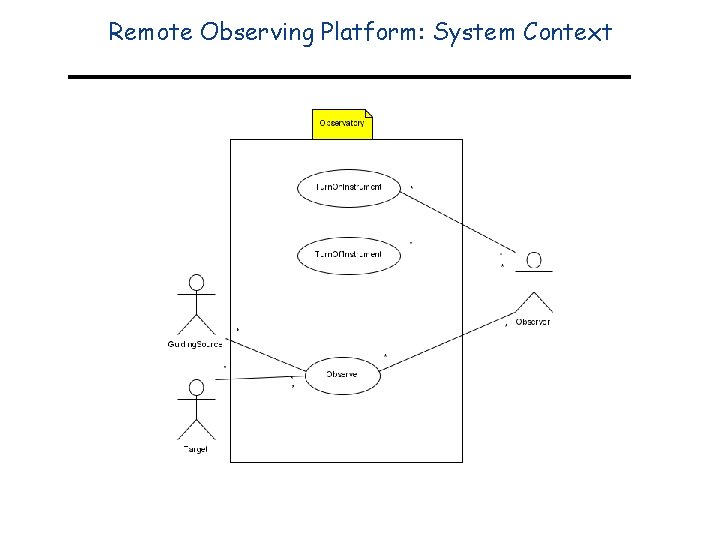

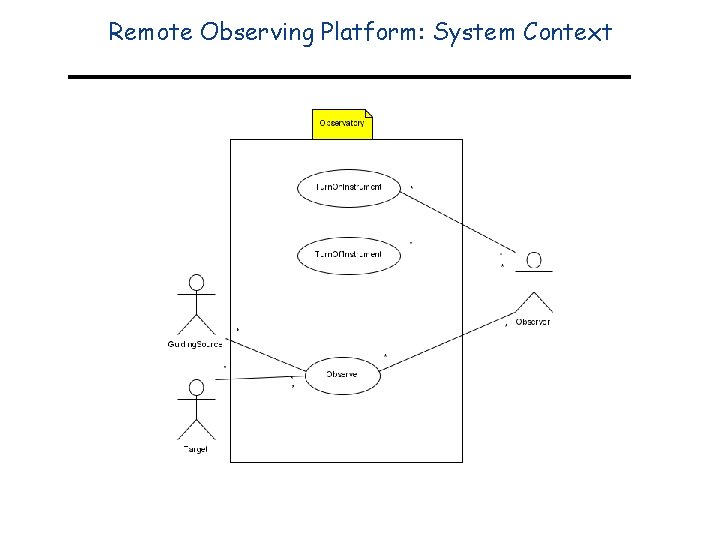

Remote Observing Platform: System Context

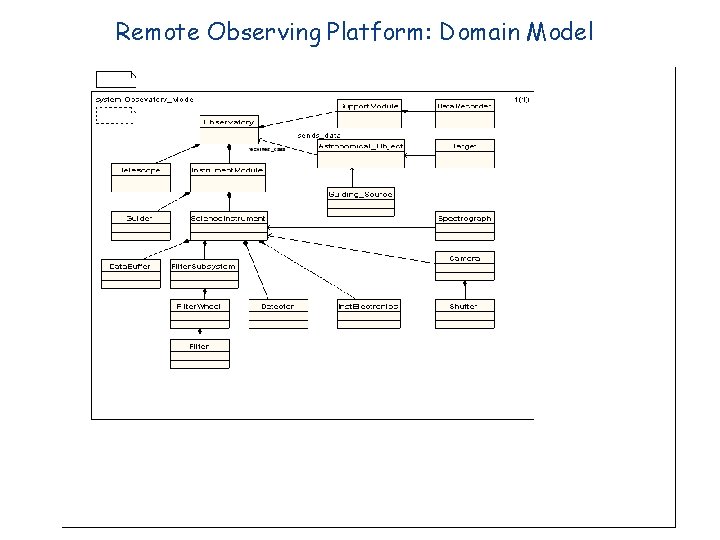

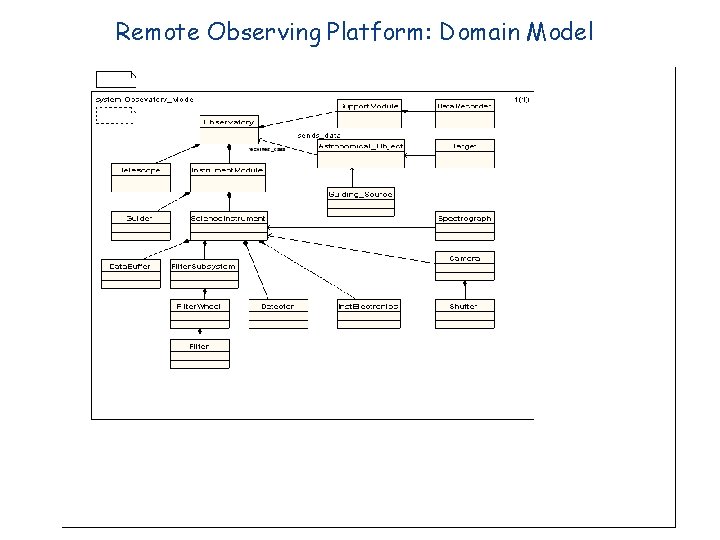

Remote Observing Platform: Domain Model

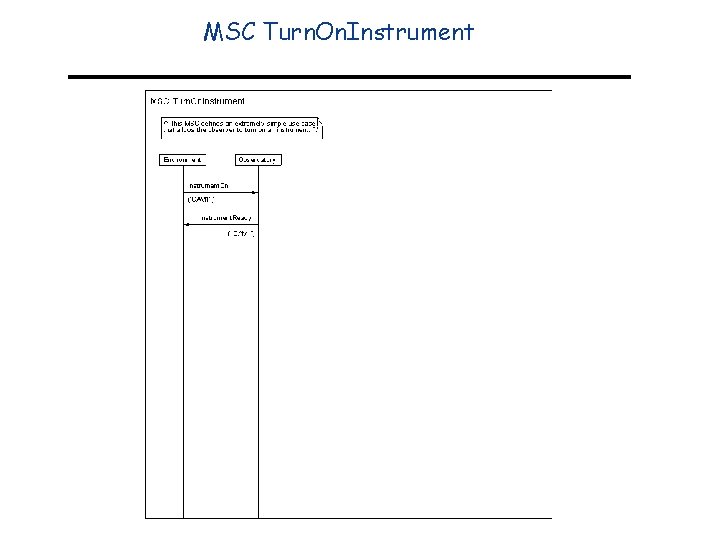

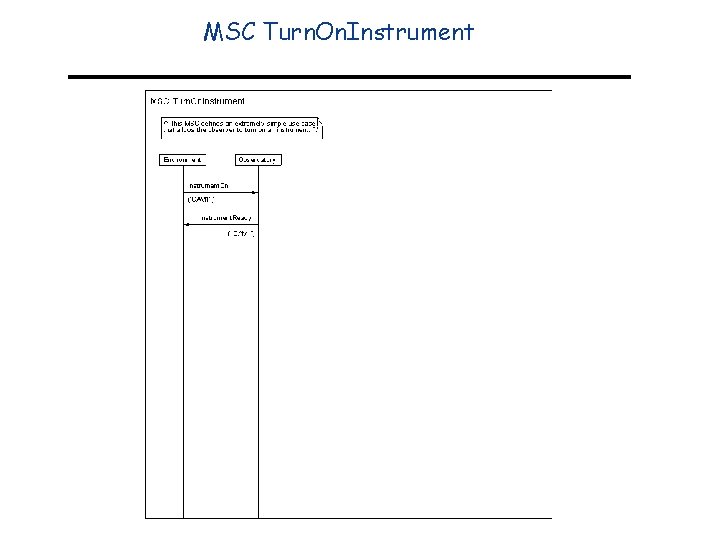

MSC Turn. On. Instrument

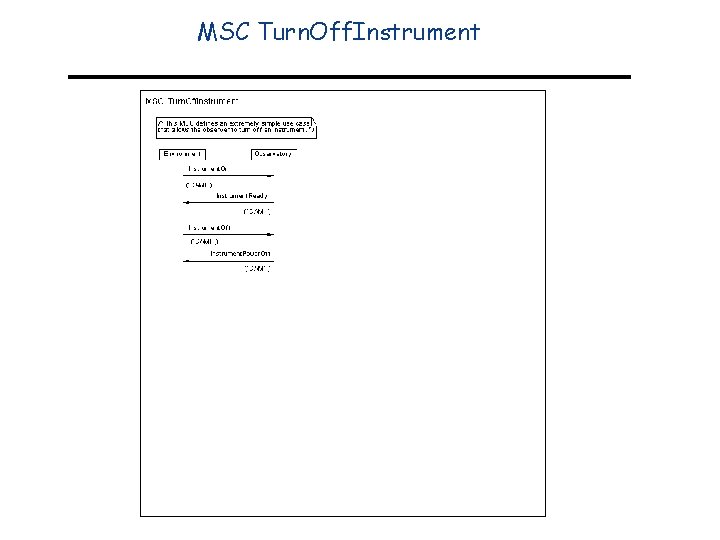

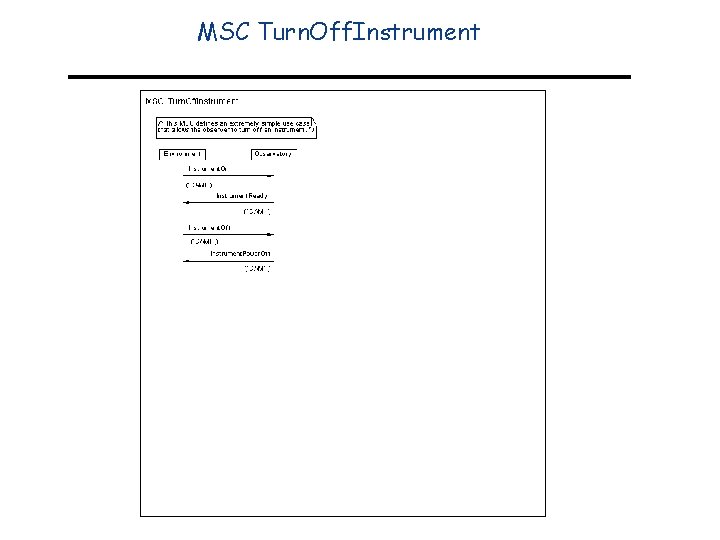

MSC Turn. Off. Instrument

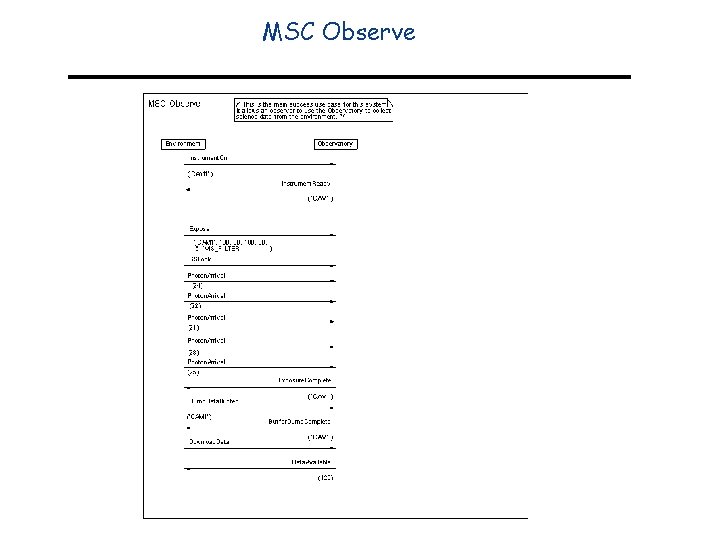

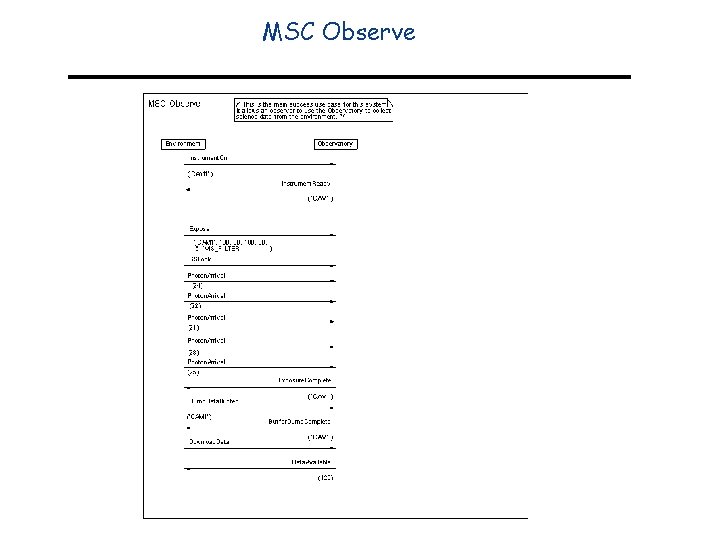

MSC Observe

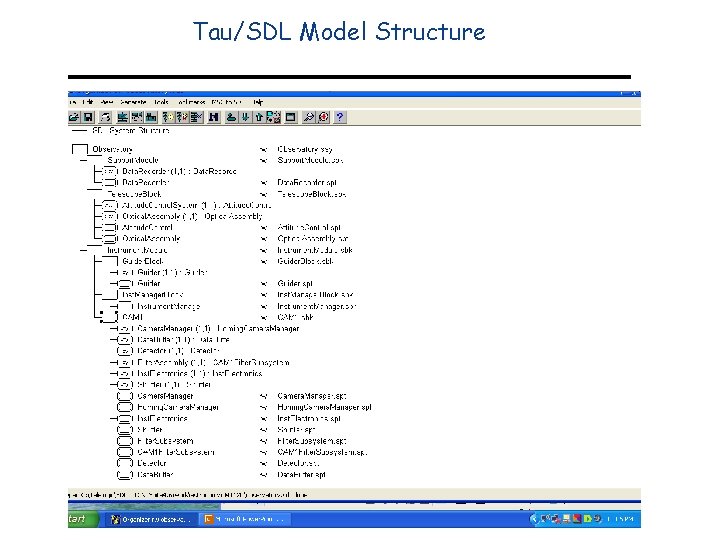

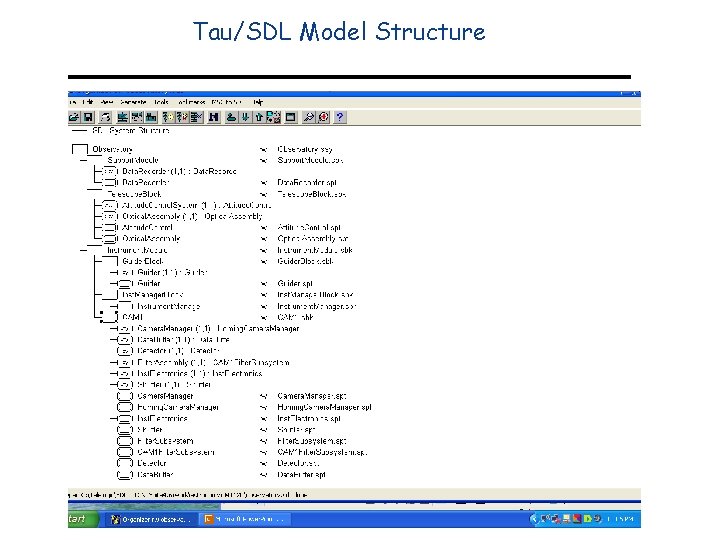

Tau/SDL Model Structure

Observatory System Diagram

Instrument. Module Block Diagram

CAM 1 Block Diagram

Shutter Process Diagram

Camera. Manager Process Diagram

Inheritance in SDL: Homing. Camera. Manager

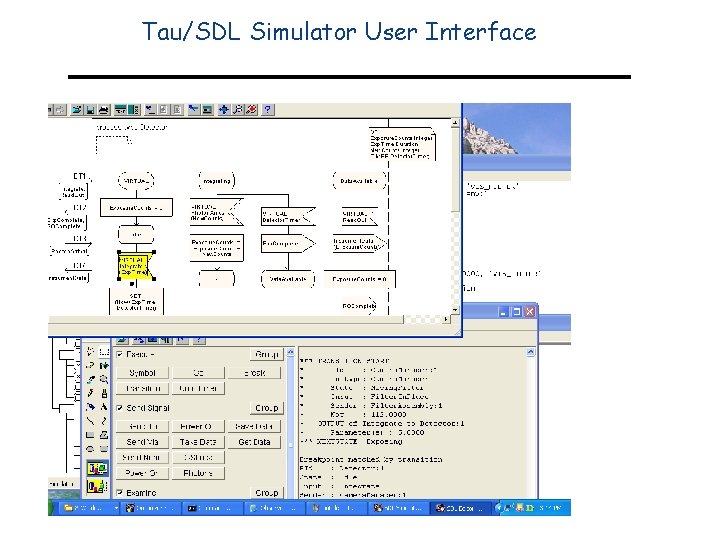

Tau/SDL Simulator User Interface

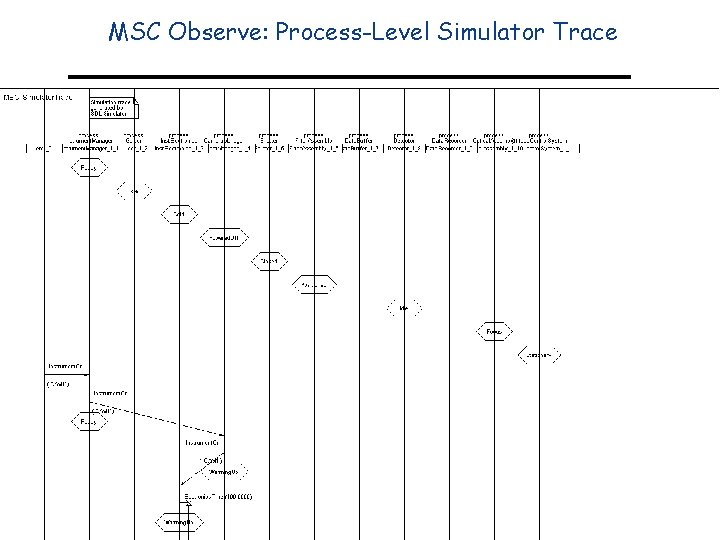

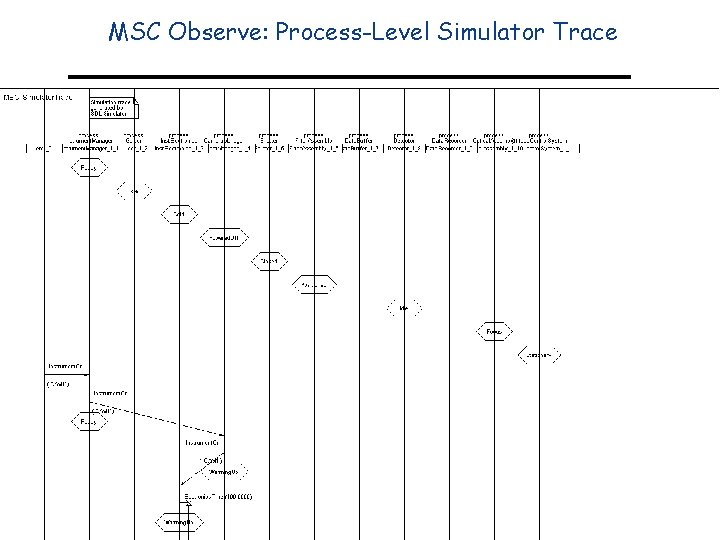

MSC Observe: Process-Level Simulator Trace

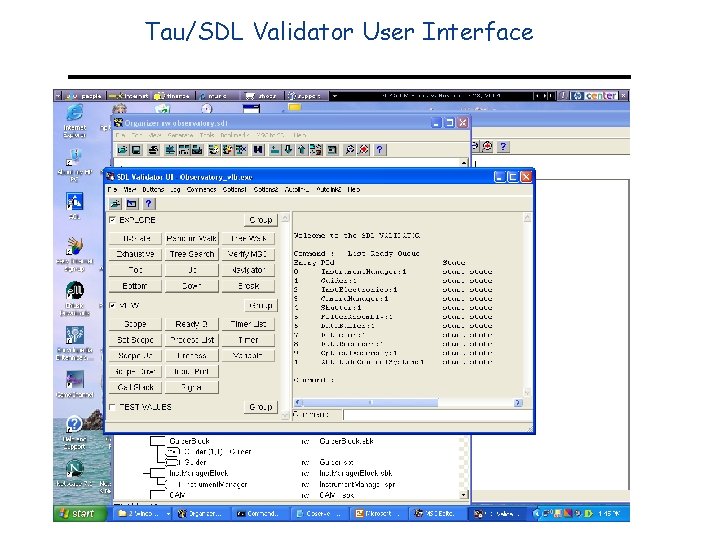

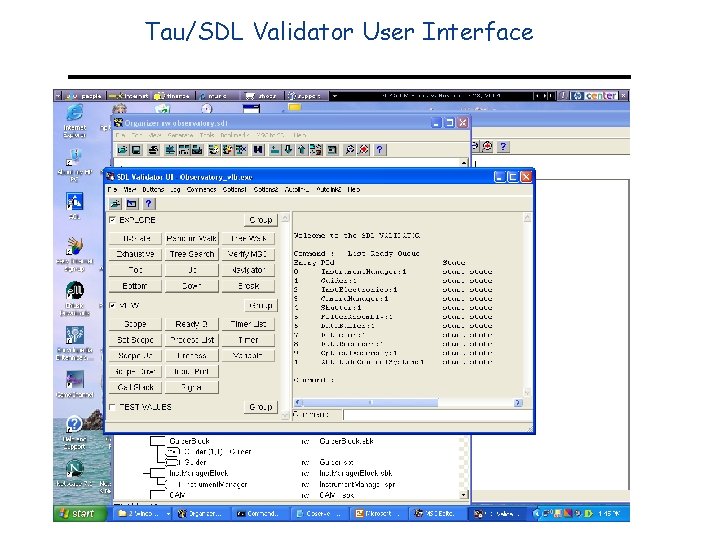

Tau/SDL Validator User Interface

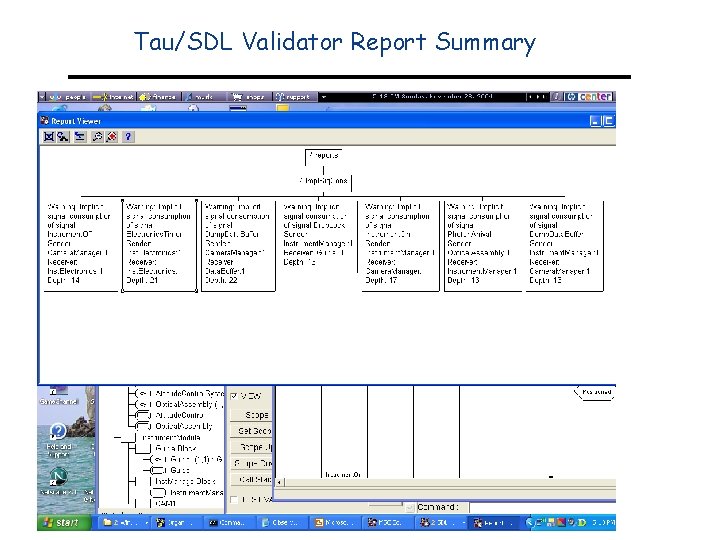

Tau/SDL Validator Report Summary

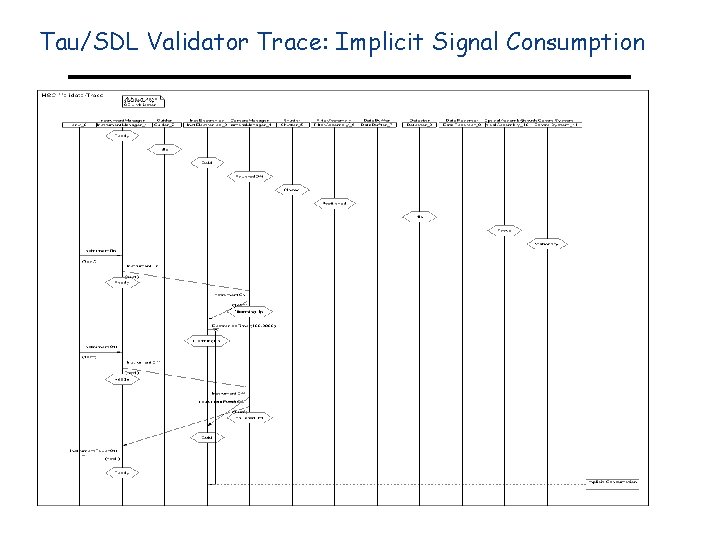

Tau/SDL Validator Trace: Implicit Signal Consumption

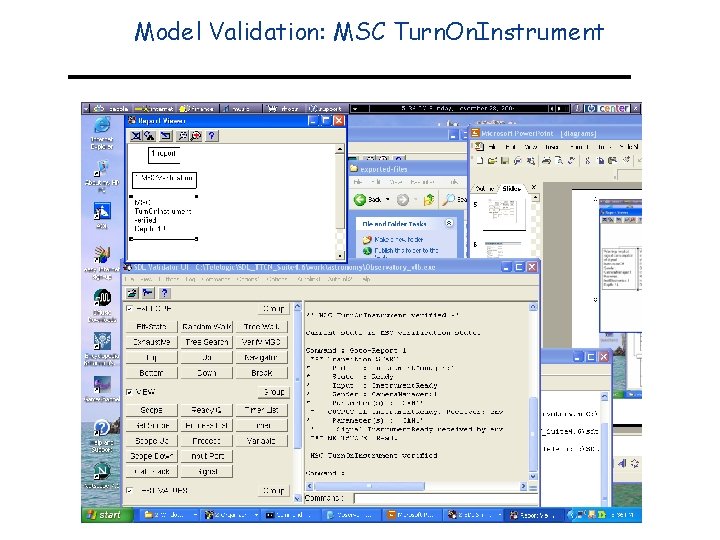

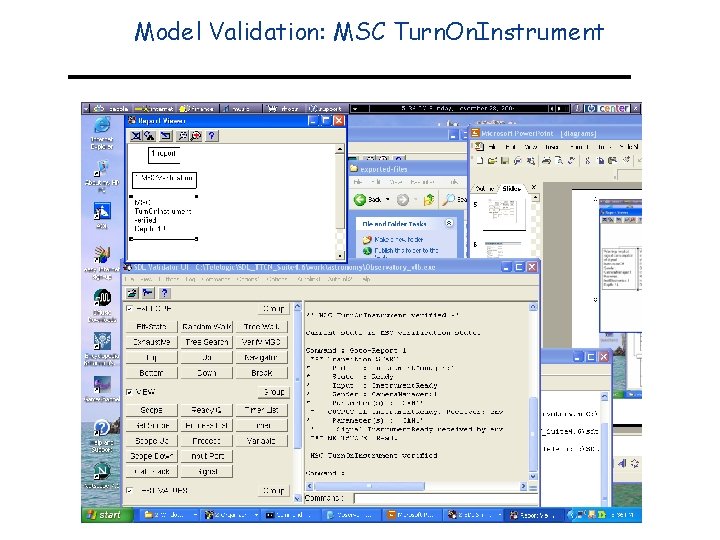

Model Validation: MSC Turn. On. Instrument

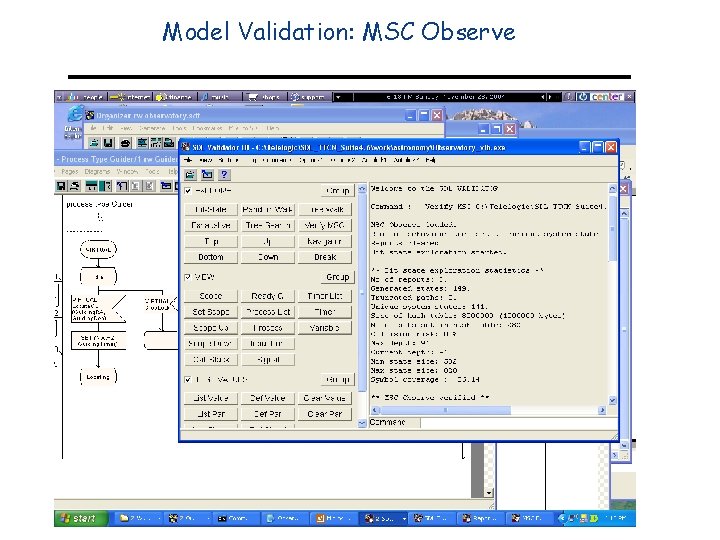

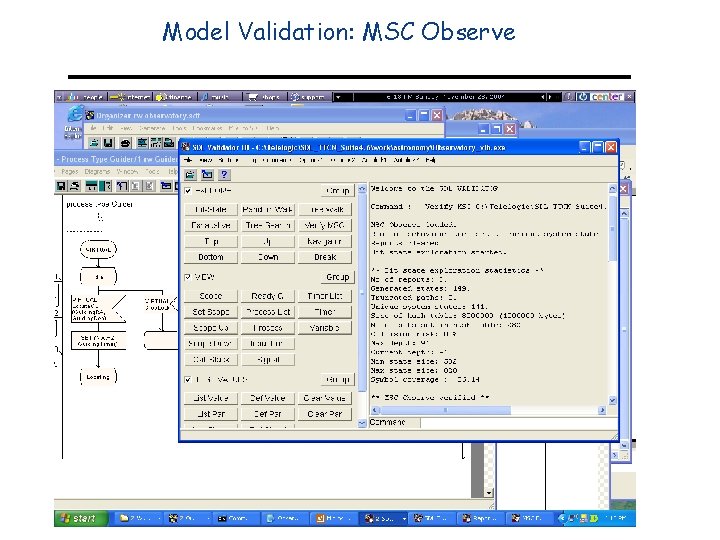

Model Validation: MSC Observe

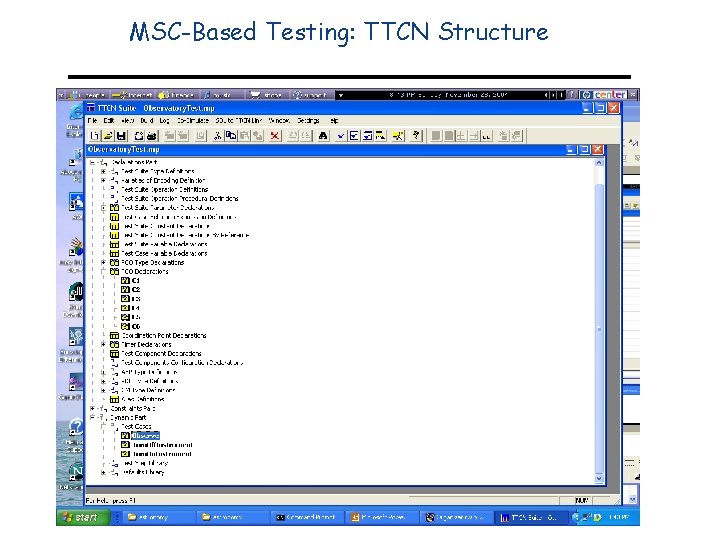

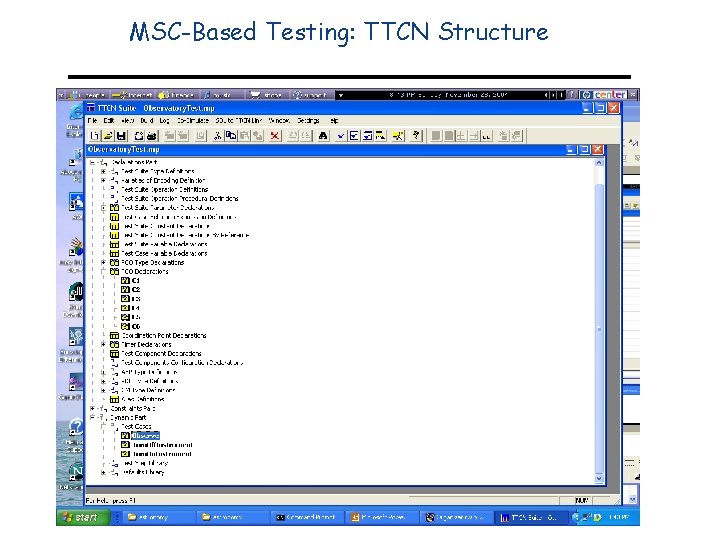

MSC-Based Testing: TTCN Structure

Test Case Generated from Observe MSC

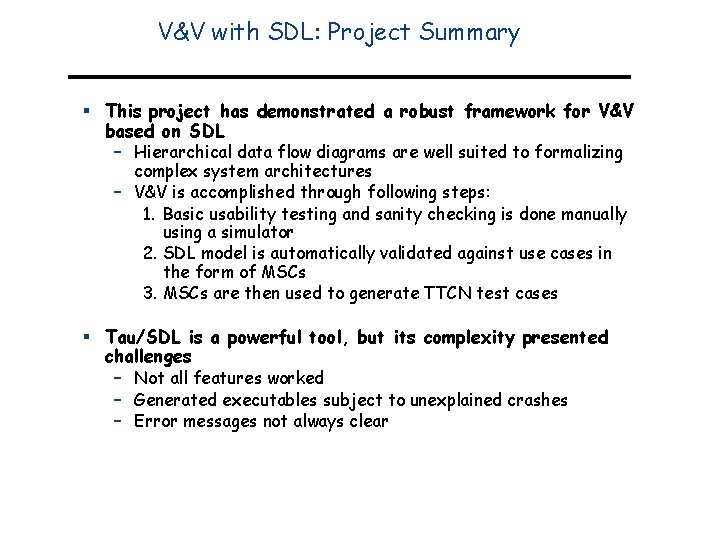

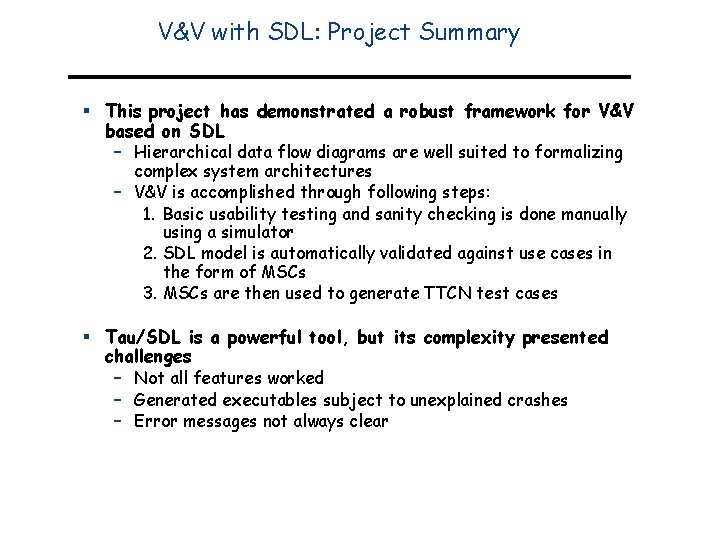

V&V with SDL: Project Summary § This project has demonstrated a robust framework for V&V based on SDL – Hierarchical data flow diagrams are well suited to formalizing complex system architectures – V&V is accomplished through following steps: 1. Basic usability testing and sanity checking is done manually using a simulator 2. SDL model is automatically validated against use cases in the form of MSCs 3. MSCs are then used to generate TTCN test cases § Tau/SDL is a powerful tool, but its complexity presented challenges – Not all features worked – Generated executables subject to unexplained crashes – Error messages not always clear