Systems Architecture II Systems Architecture I Review Jeremy

![Execution Steps 1 Instruction fetch – IR = Memory[PC]; – PC = PC + Execution Steps 1 Instruction fetch – IR = Memory[PC]; – PC = PC +](https://slidetodoc.com/presentation_image_h2/def484824f60cfab78154a4c22b97dad/image-41.jpg)

- Slides: 47

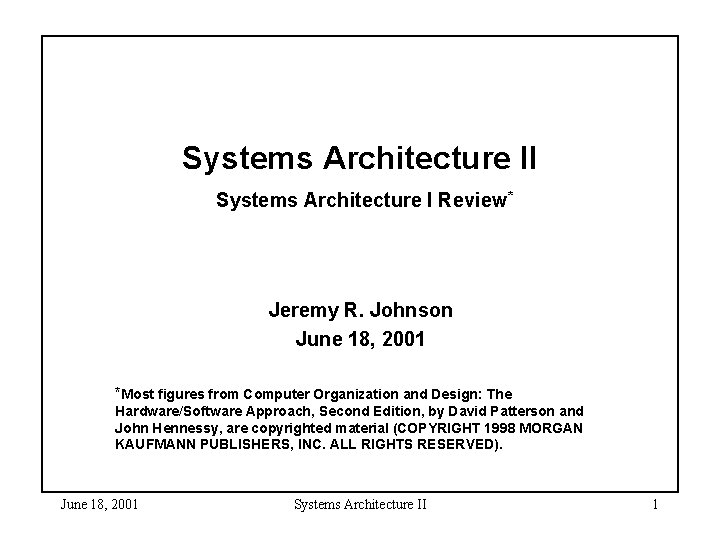

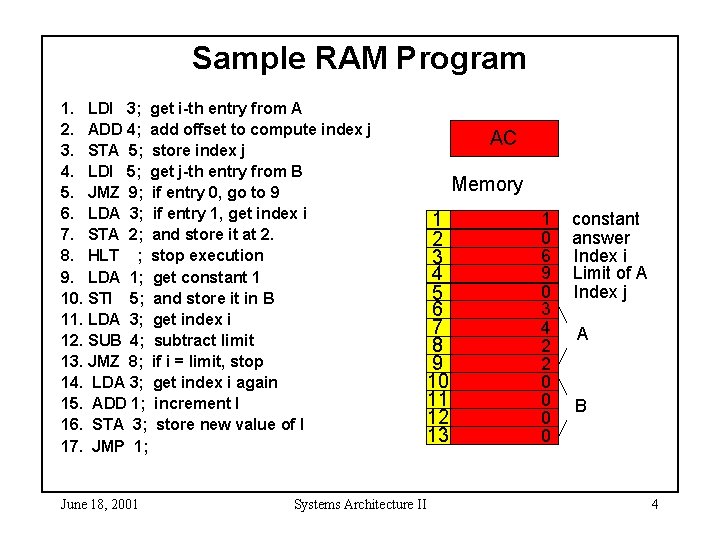

Systems Architecture II Systems Architecture I Review* Jeremy R. Johnson June 18, 2001 *Most figures from Computer Organization and Design: The Hardware/Software Approach, Second Edition, by David Patterson and John Hennessy, are copyrighted material (COPYRIGHT 1998 MORGAN KAUFMANN PUBLISHERS, INC. ALL RIGHTS RESERVED). June 18, 2001 Systems Architecture II 1

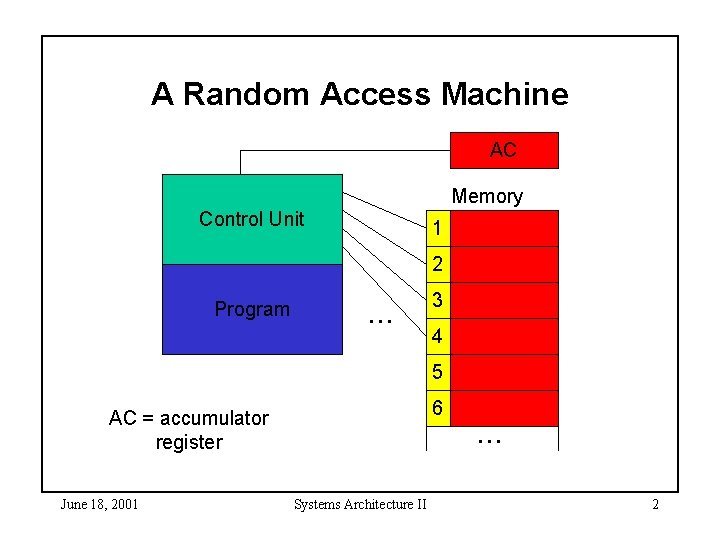

A Random Access Machine AC Memory Control Unit 1 2 Program . . . 3 4 5 6 AC = accumulator register June 18, 2001 Systems Architecture II . . . 2

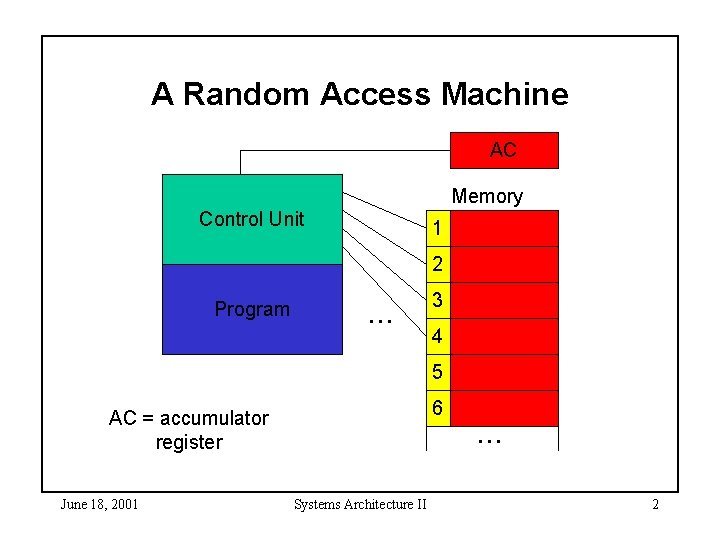

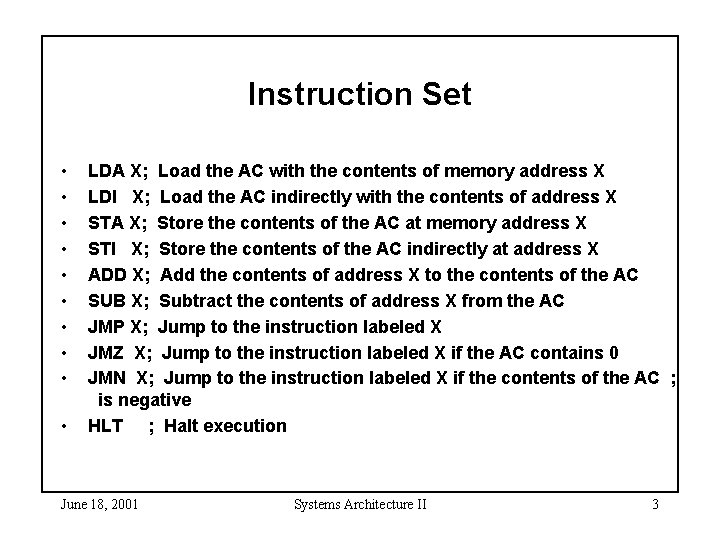

Instruction Set • • • LDA X; Load the AC with the contents of memory address X LDI X; Load the AC indirectly with the contents of address X STA X; Store the contents of the AC at memory address X STI X; Store the contents of the AC indirectly at address X ADD X; Add the contents of address X to the contents of the AC SUB X; Subtract the contents of address X from the AC JMP X; Jump to the instruction labeled X JMZ X; Jump to the instruction labeled X if the AC contains 0 JMN X; Jump to the instruction labeled X if the contents of the AC ; is negative HLT ; Halt execution June 18, 2001 Systems Architecture II 3

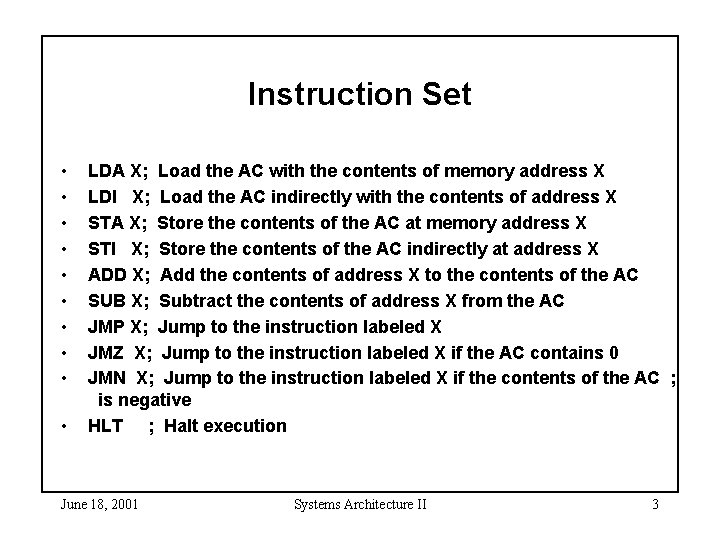

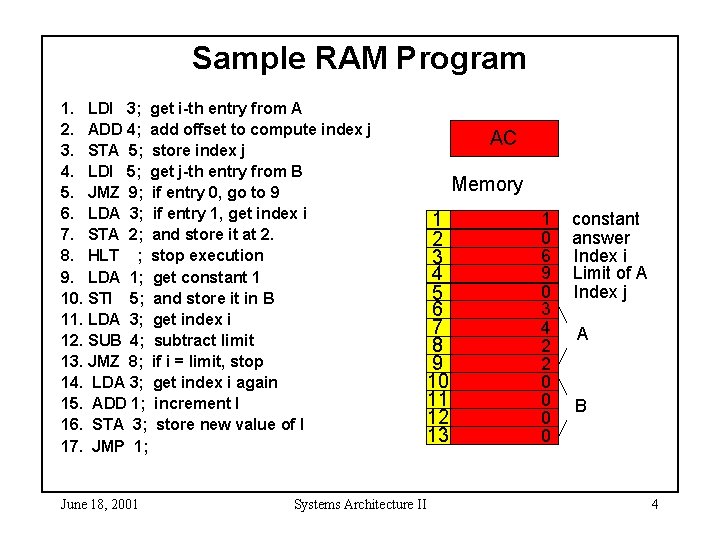

Sample RAM Program 1. LDI 3; get i-th entry from A 2. ADD 4; add offset to compute index j 3. STA 5; store index j 4. LDI 5; get j-th entry from B 5. JMZ 9; if entry 0, go to 9 6. LDA 3; if entry 1, get index i 7. STA 2; and store it at 2. 8. HLT ; stop execution 9. LDA 1; get constant 1 10. STI 5; and store it in B 11. LDA 3; get index i 12. SUB 4; subtract limit 13. JMZ 8; if i = limit, stop 14. LDA 3; get index i again 15. ADD 1; increment I 16. STA 3; store new value of I 17. JMP 1; June 18, 2001 Systems Architecture II AC Memory 1 2 3 4 5 6 7 8 9 10 11 12 13 1 0 6 9 0 3 4 2 2 0 0 constant answer Index i Limit of A Index j A B 4

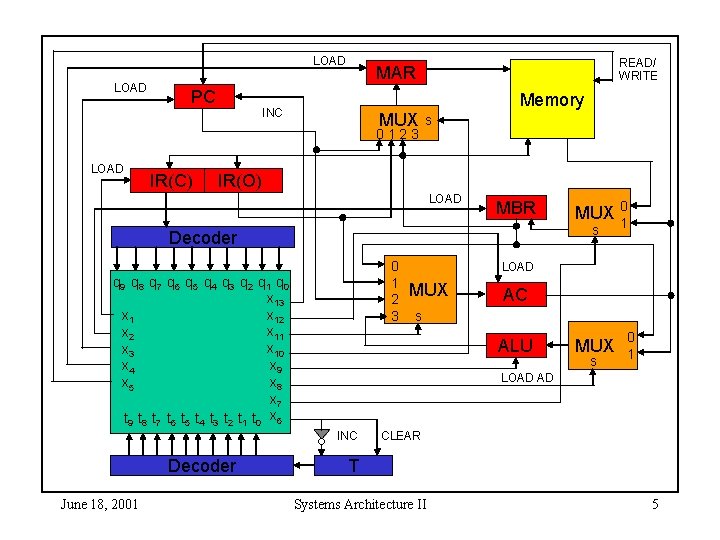

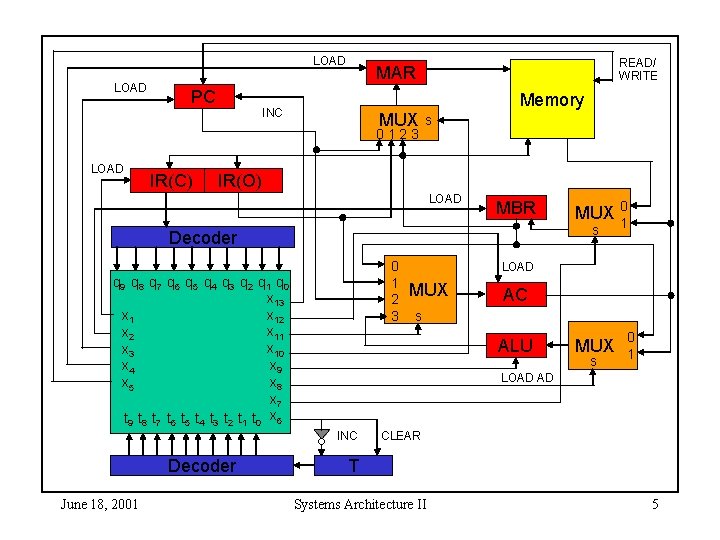

LOAD PC Memory INC MUX 0123 LOAD READ/ WRITE MAR IR(C) s IR(O) LOAD MBR s Decoder 0 1 2 3 q 9 q 8 q 7 q 6 q 5 q 4 q 3 q 2 q 1 q 0 x 13 x 12 x 11 x 2 x 10 x 3 x 9 x 4 x 8 x 5 x 7 t 9 t 8 t 7 t 6 t 5 t 4 t 3 t 2 t 1 t 0 x 6 June 18, 2001 1 LOAD MUX AC s ALU MUX s 0 1 LOAD AD INC Decoder MUX 0 CLEAR T Systems Architecture II 5

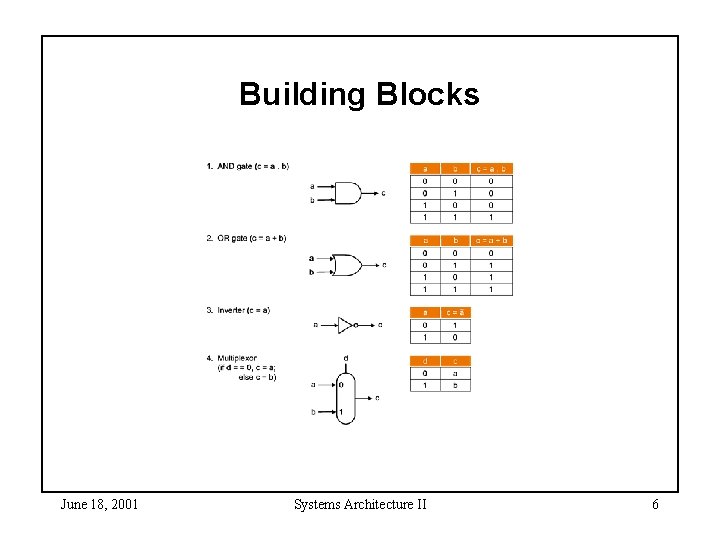

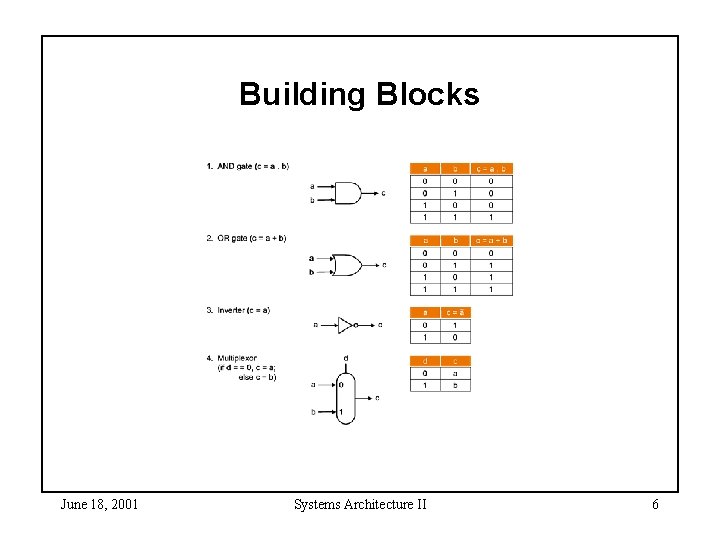

Building Blocks June 18, 2001 Systems Architecture II 6

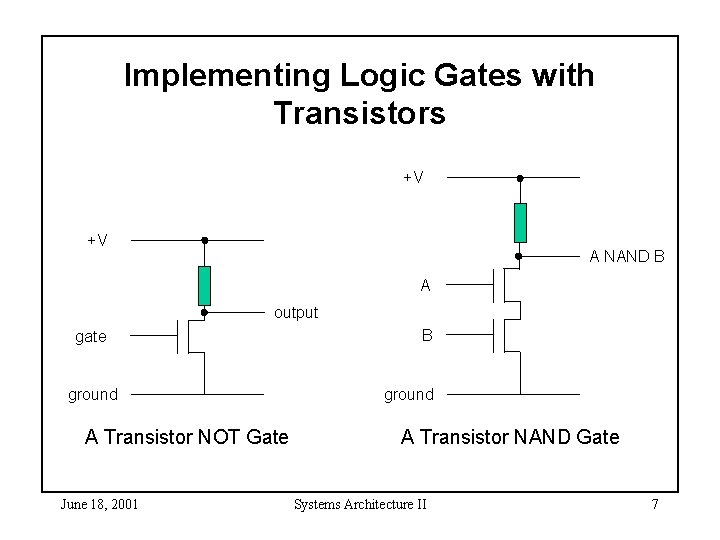

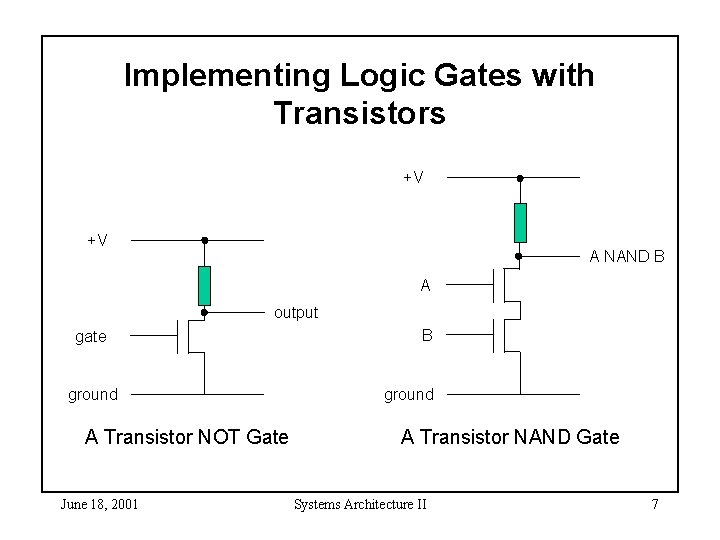

Implementing Logic Gates with Transistors +V +V A NAND B A output gate ground A Transistor NOT Gate June 18, 2001 B ground A Transistor NAND Gate Systems Architecture II 7

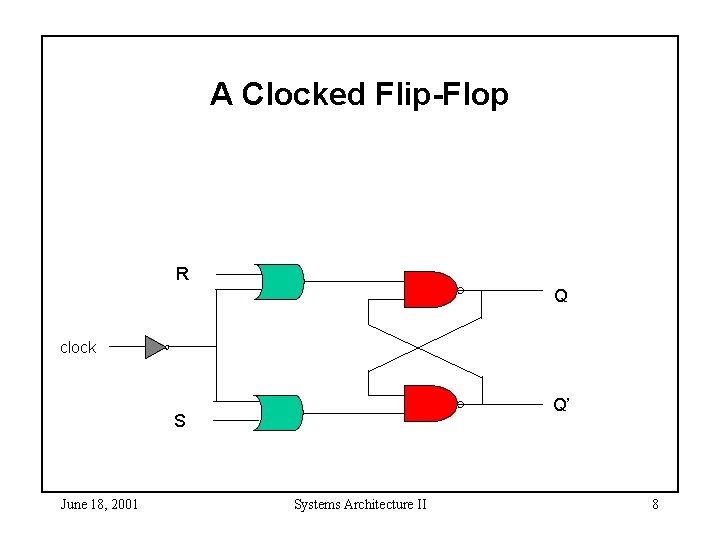

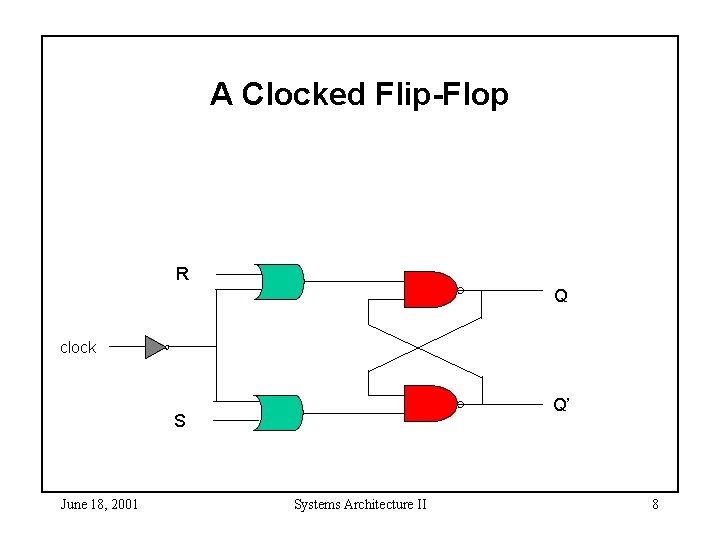

A Clocked Flip-Flop R Q clock Q’ S June 18, 2001 Systems Architecture II 8

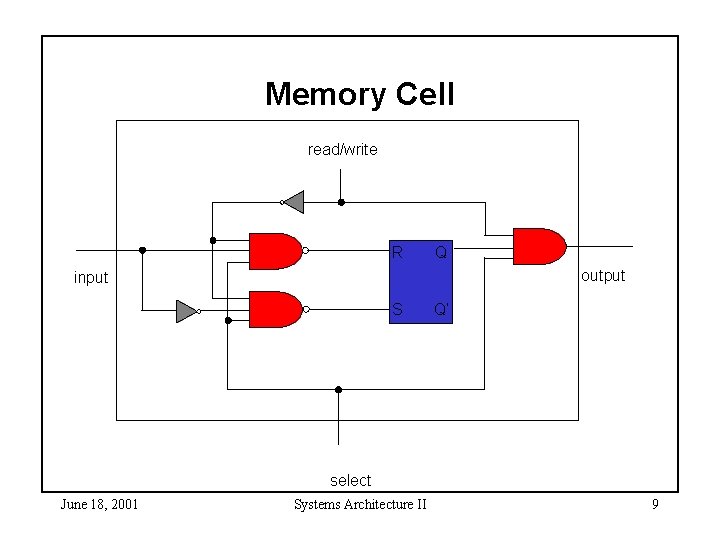

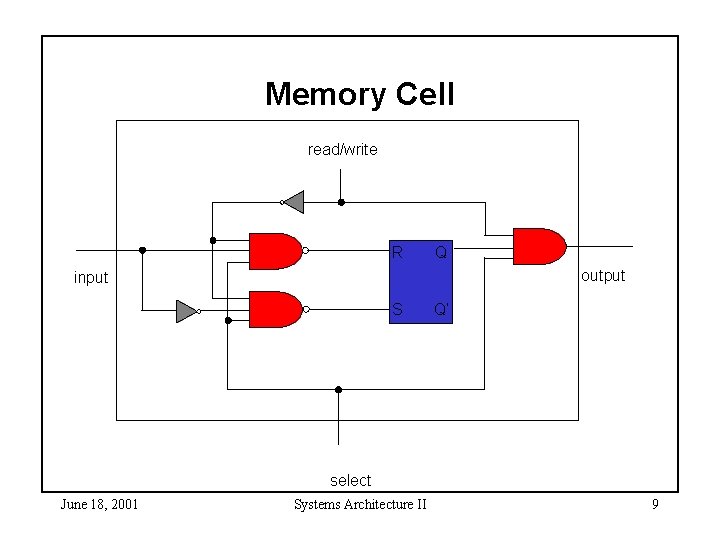

Memory Cell read/write R Q output input S Q’ select June 18, 2001 Systems Architecture II 9

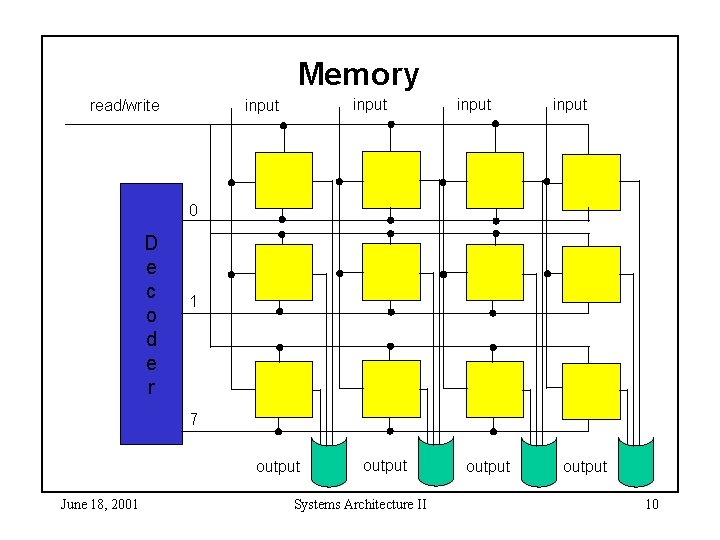

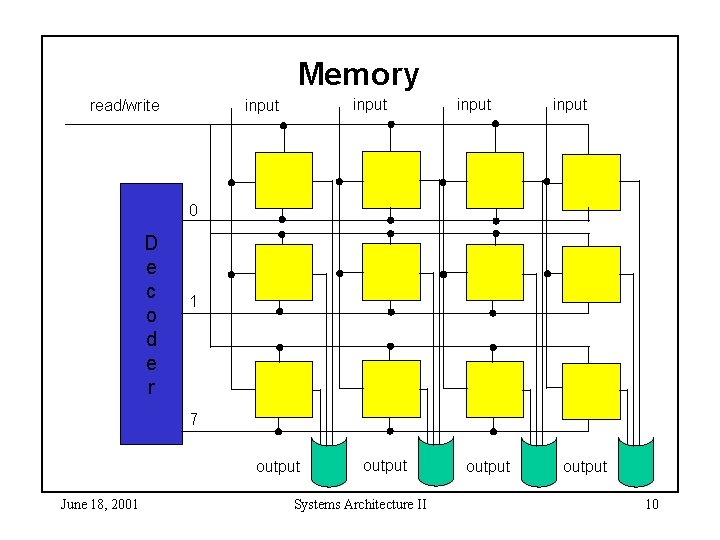

Memory read/write input 0 D e c o d e r 1 7 output June 18, 2001 output Systems Architecture II output 10

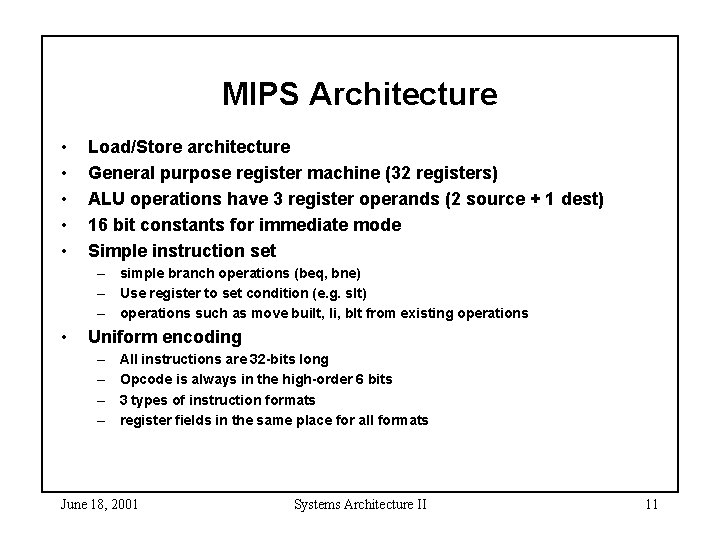

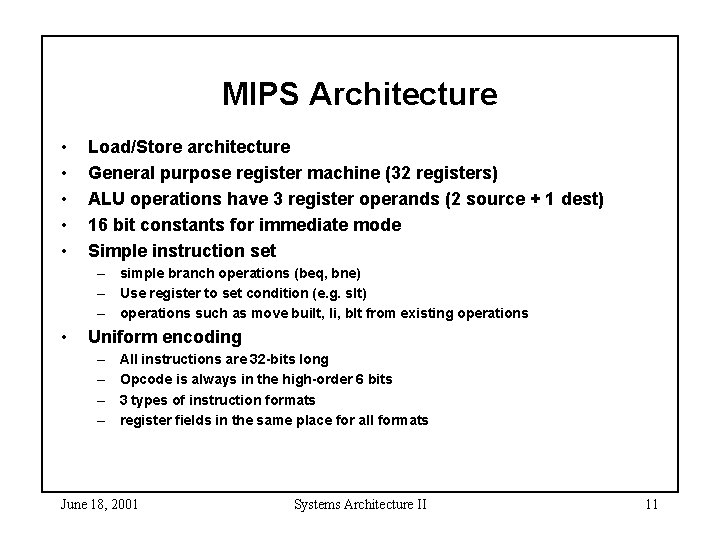

MIPS Architecture • • • Load/Store architecture General purpose register machine (32 registers) ALU operations have 3 register operands (2 source + 1 dest) 16 bit constants for immediate mode Simple instruction set – simple branch operations (beq, bne) – Use register to set condition (e. g. slt) – operations such as move built, li, blt from existing operations • Uniform encoding – – All instructions are 32 -bits long Opcode is always in the high-order 6 bits 3 types of instruction formats register fields in the same place for all formats June 18, 2001 Systems Architecture II 11

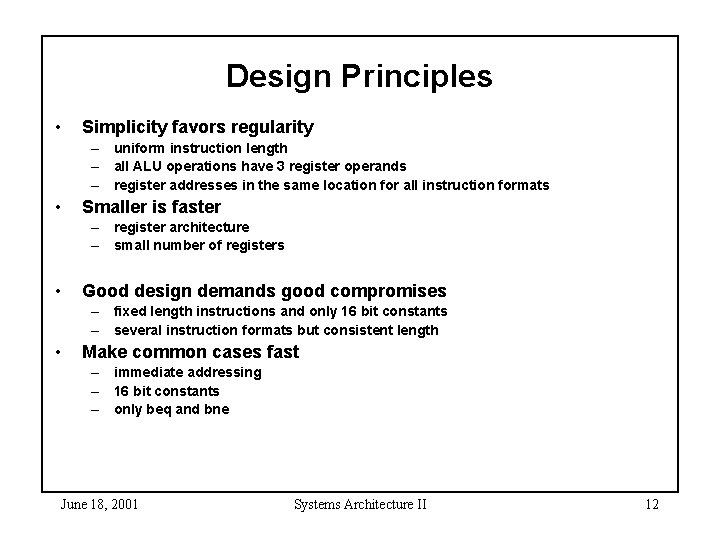

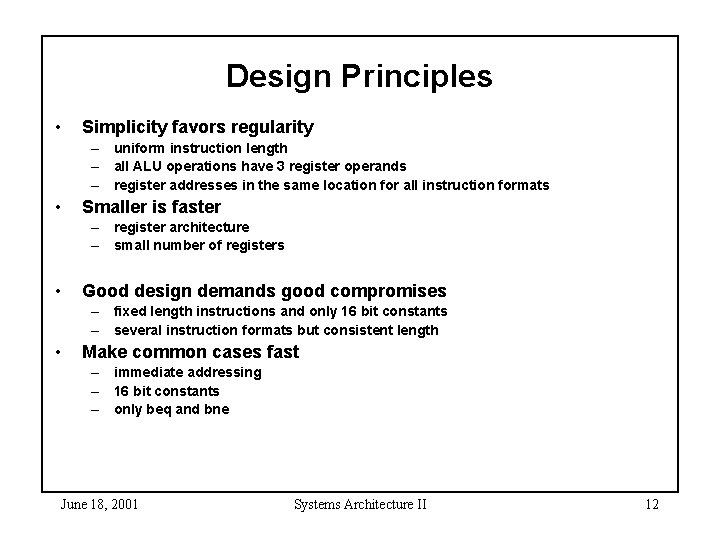

Design Principles • Simplicity favors regularity – uniform instruction length – all ALU operations have 3 register operands – register addresses in the same location for all instruction formats • Smaller is faster – register architecture – small number of registers • Good design demands good compromises – fixed length instructions and only 16 bit constants – several instruction formats but consistent length • Make common cases fast – immediate addressing – 16 bit constants – only beq and bne June 18, 2001 Systems Architecture II 12

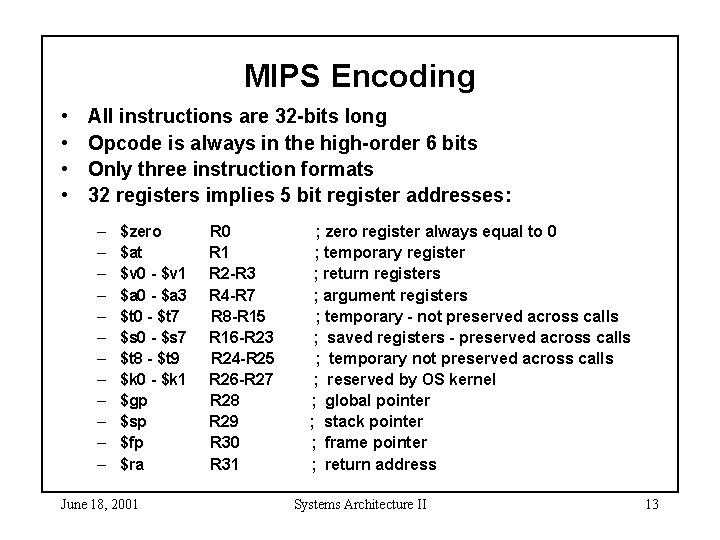

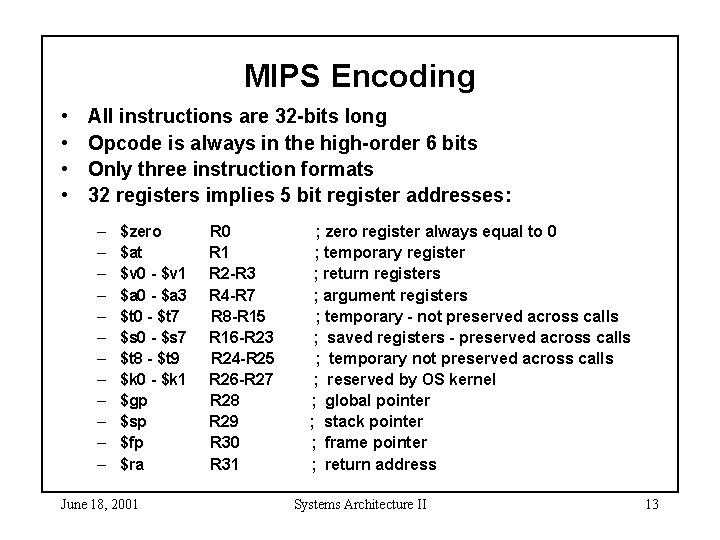

MIPS Encoding • • All instructions are 32 -bits long Opcode is always in the high-order 6 bits Only three instruction formats 32 registers implies 5 bit register addresses: – – – $zero $at $v 0 - $v 1 $a 0 - $a 3 $t 0 - $t 7 $s 0 - $s 7 $t 8 - $t 9 $k 0 - $k 1 $gp $sp $fp $ra June 18, 2001 R 0 R 1 R 2 -R 3 R 4 -R 7 R 8 -R 15 R 16 -R 23 R 24 -R 25 R 26 -R 27 R 28 R 29 R 30 R 31 ; zero register always equal to 0 ; temporary register ; return registers ; argument registers ; temporary - not preserved across calls ; saved registers - preserved across calls ; temporary not preserved across calls ; reserved by OS kernel ; global pointer ; stack pointer ; frame pointer ; return address Systems Architecture II 13

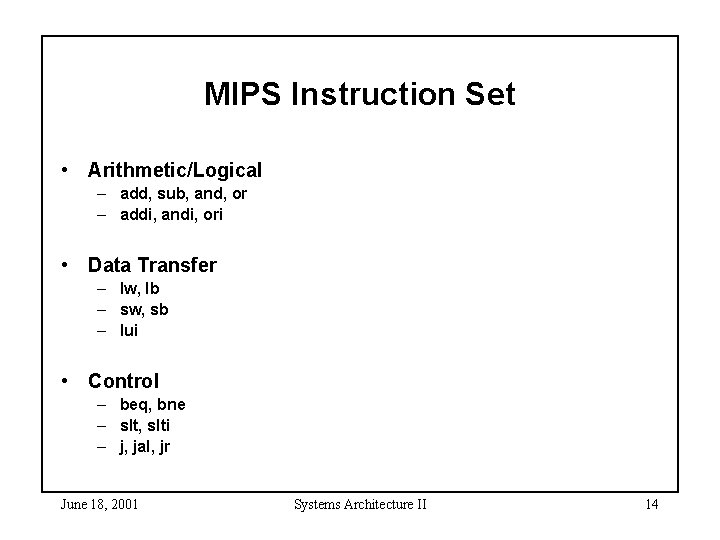

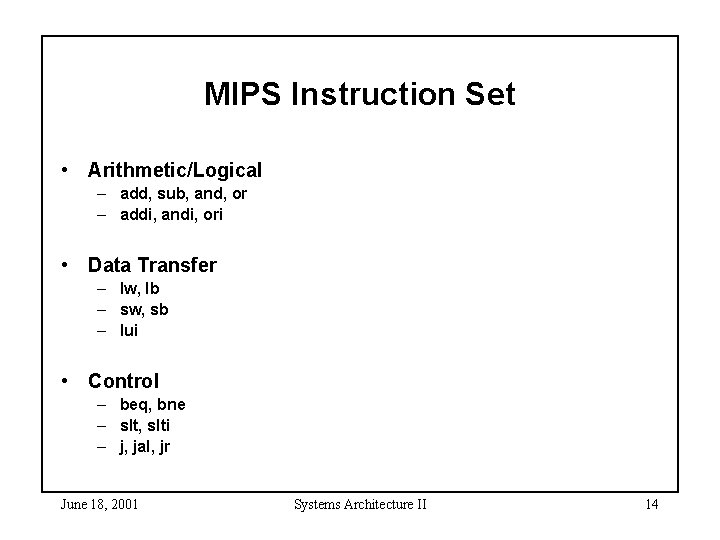

MIPS Instruction Set • Arithmetic/Logical – add, sub, and, or – addi, andi, ori • Data Transfer – lw, lb – sw, sb – lui • Control – beq, bne – slt, slti – j, jal, jr June 18, 2001 Systems Architecture II 14

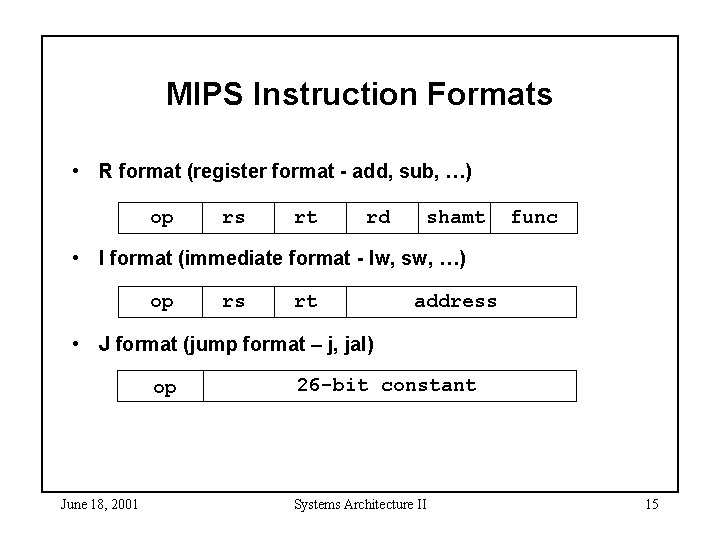

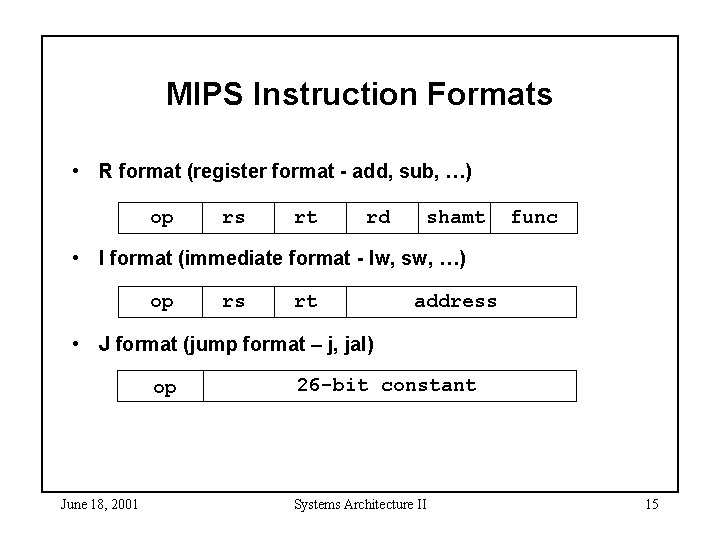

MIPS Instruction Formats • R format (register format - add, sub, …) op rs rt rd shamt func • I format (immediate format - lw, sw, …) op rs rt address • J format (jump format – j, jal) op June 18, 2001 26 -bit constant Systems Architecture II 15

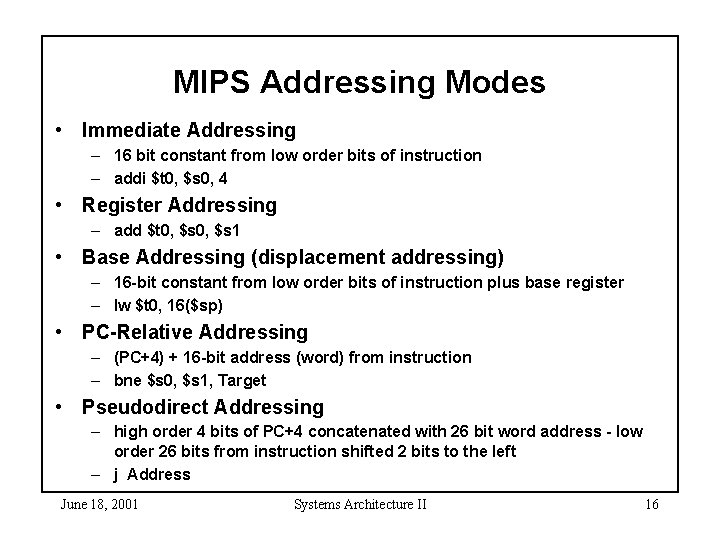

MIPS Addressing Modes • Immediate Addressing – 16 bit constant from low order bits of instruction – addi $t 0, $s 0, 4 • Register Addressing – add $t 0, $s 1 • Base Addressing (displacement addressing) – 16 -bit constant from low order bits of instruction plus base register – lw $t 0, 16($sp) • PC-Relative Addressing – (PC+4) + 16 -bit address (word) from instruction – bne $s 0, $s 1, Target • Pseudodirect Addressing – high order 4 bits of PC+4 concatenated with 26 bit word address - low order 26 bits from instruction shifted 2 bits to the left – j Address June 18, 2001 Systems Architecture II 16

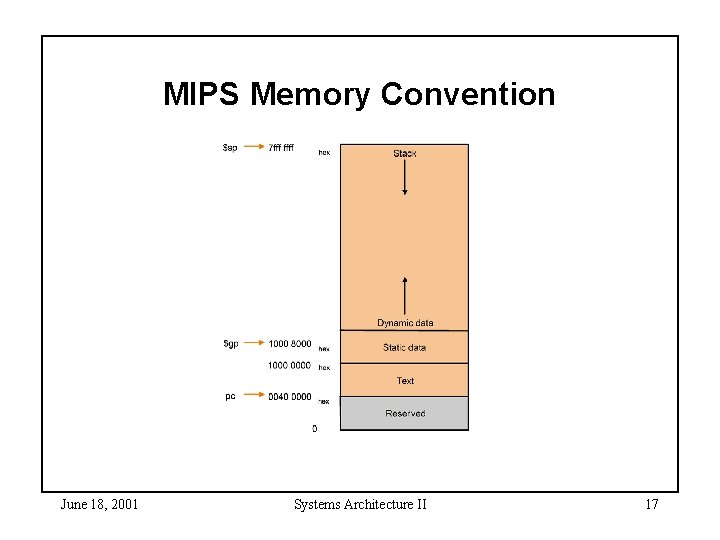

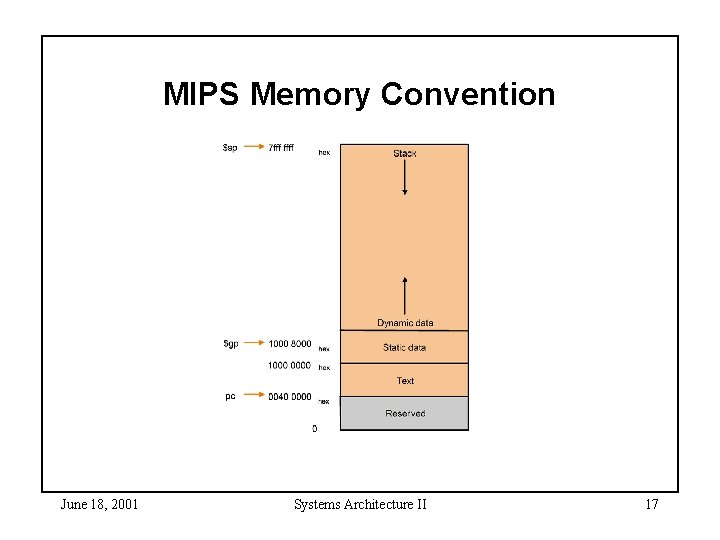

MIPS Memory Convention June 18, 2001 Systems Architecture II 17

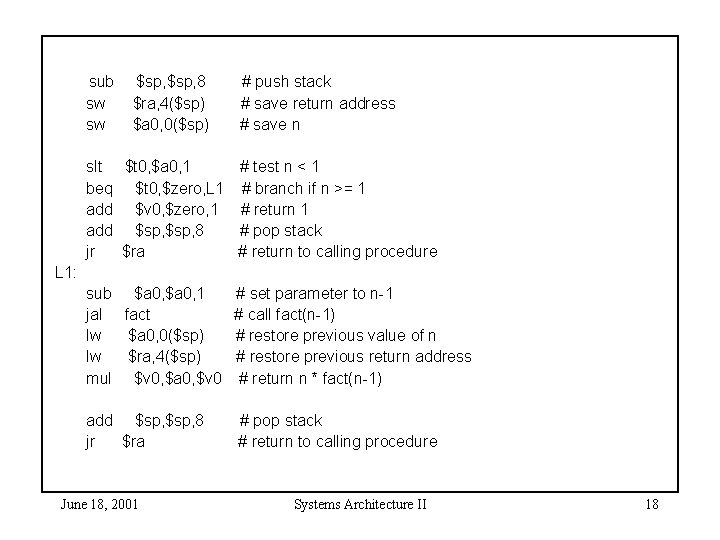

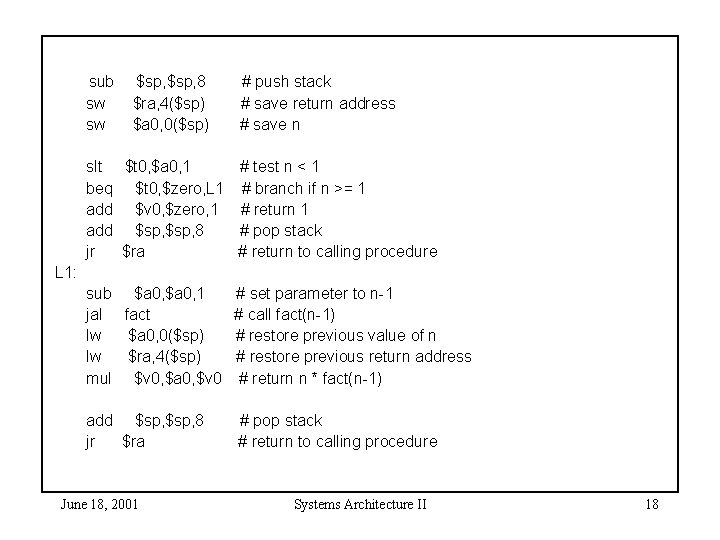

sub sw sw $sp, 8 $ra, 4($sp) $a 0, 0($sp) # push stack # save return address # save n slt $t 0, $a 0, 1 # test n < 1 beq $t 0, $zero, L 1 # branch if n >= 1 add $v 0, $zero, 1 # return 1 add $sp, 8 # pop stack jr $ra # return to calling procedure L 1: sub $a 0, 1 jal fact lw $a 0, 0($sp) lw $ra, 4($sp) mul $v 0, $a 0, $v 0 # set parameter to n-1 # call fact(n-1) # restore previous value of n # restore previous return address # return n * fact(n-1) add $sp, 8 jr $ra # pop stack # return to calling procedure June 18, 2001 Systems Architecture II 18

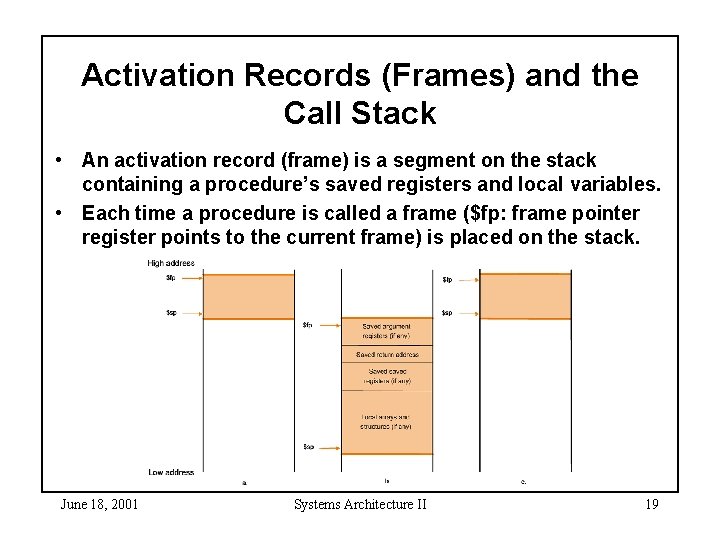

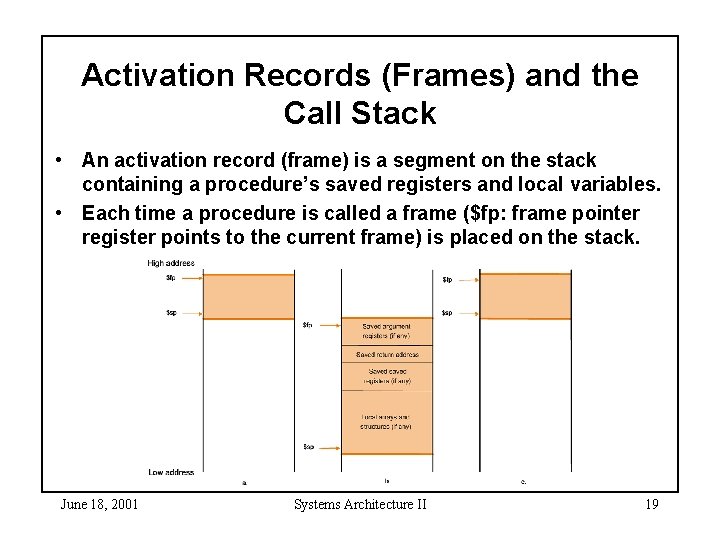

Activation Records (Frames) and the Call Stack • An activation record (frame) is a segment on the stack containing a procedure’s saved registers and local variables. • Each time a procedure is called a frame ($fp: frame pointer register points to the current frame) is placed on the stack. June 18, 2001 Systems Architecture II 19

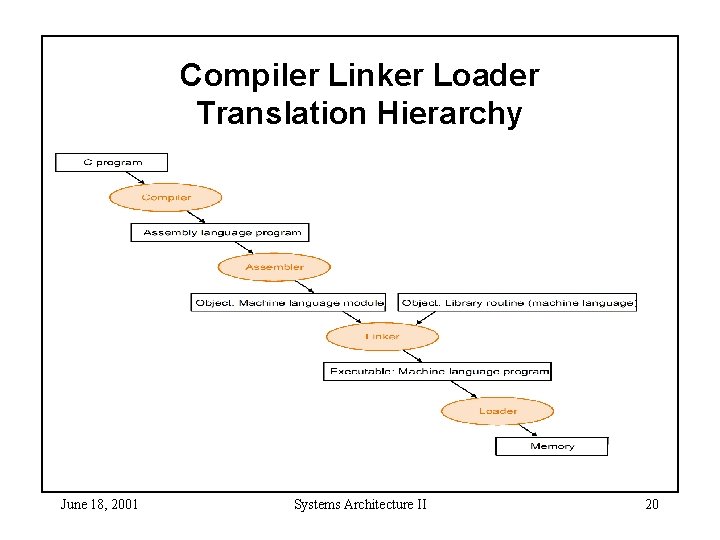

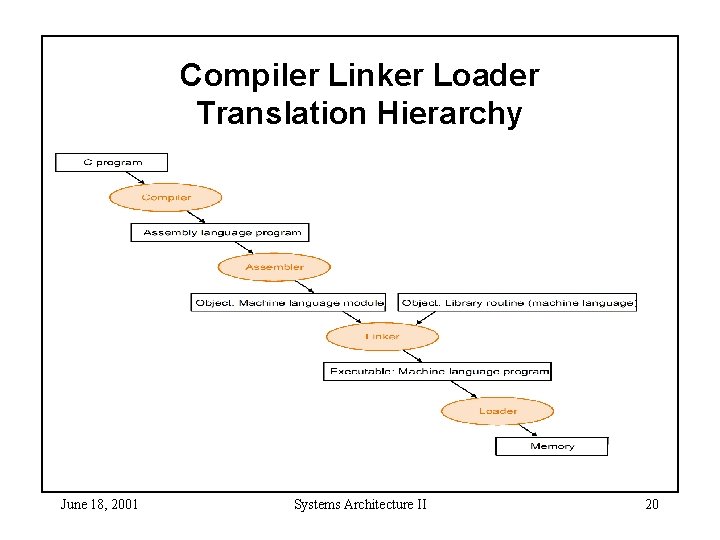

Compiler Linker Loader Translation Hierarchy June 18, 2001 Systems Architecture II 20

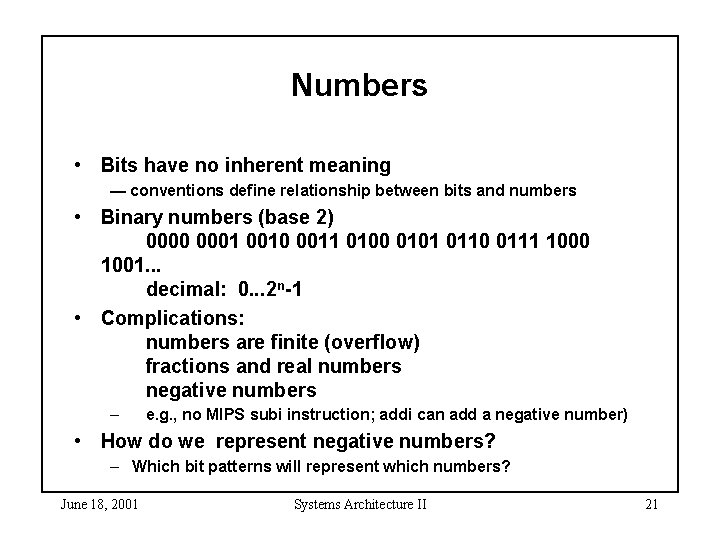

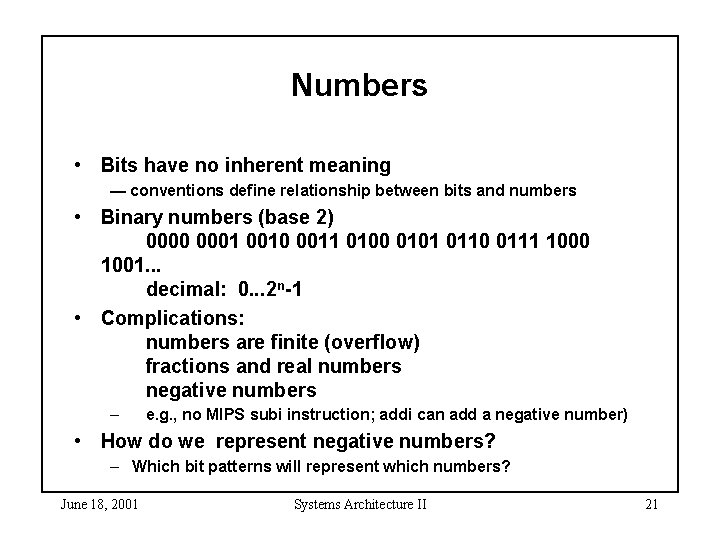

Numbers • Bits have no inherent meaning — conventions define relationship between bits and numbers • Binary numbers (base 2) 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001. . . decimal: 0. . . 2 n-1 • Complications: numbers are finite (overflow) fractions and real numbers negative numbers – e. g. , no MIPS subi instruction; addi can add a negative number) • How do we represent negative numbers? – Which bit patterns will represent which numbers? June 18, 2001 Systems Architecture II 21

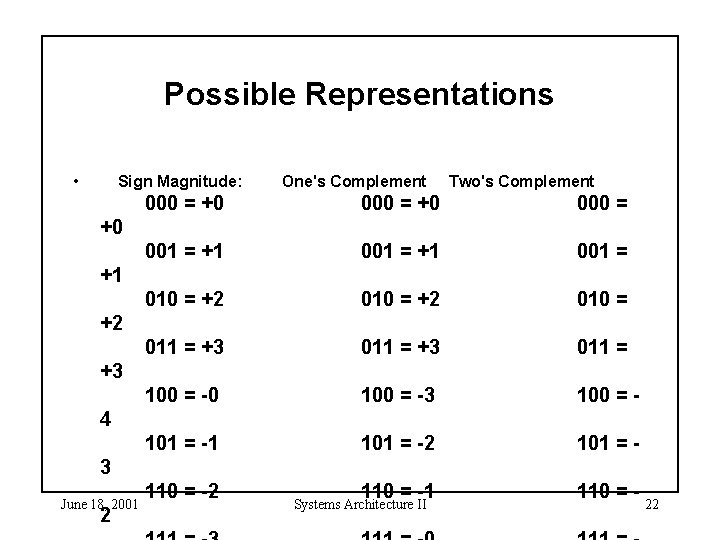

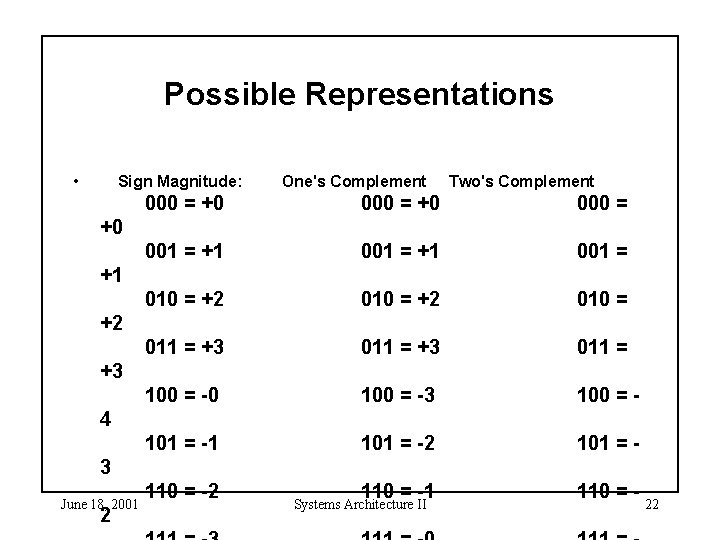

Possible Representations • Sign Magnitude: One's Complement Two's Complement 000 = +0 000 = 001 = +1 001 = 010 = +2 010 = 011 = +3 011 = 100 = -0 100 = -3 100 = - 101 = -1 101 = -2 101 = - 110 = -1 110 = - +0 +1 +2 +3 4 3 June 18, 2001 2 110 = -2 Systems Architecture II 22

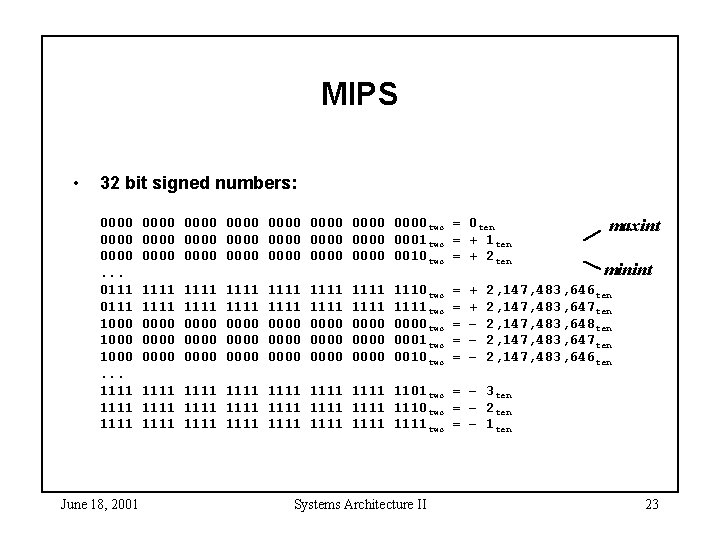

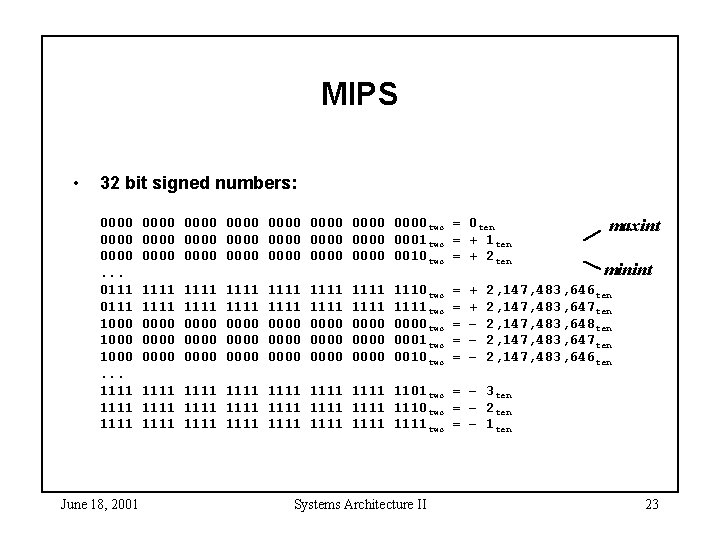

MIPS • 32 bit signed numbers: 0000. . . 0111 1000. . . 1111 June 18, 2001 0000 0000 two = 0 ten 0000 0000 0001 two = + 1 ten 0000 0000 0010 two = + 2 ten 1111 1111 0000 0000 0000 1111 0000 0000 1110 two 1111 two 0000 two 0001 two 0010 two = = = + + – – – maxint minint 2, 147, 483, 646 ten 2, 147, 483, 647 ten 2, 147, 483, 648 ten 2, 147, 483, 647 ten 2, 147, 483, 646 ten 1111 1111 1101 two = – 3 ten 1111 1111 1110 two = – 2 ten 1111 1111 two = – 1 ten Systems Architecture II 23

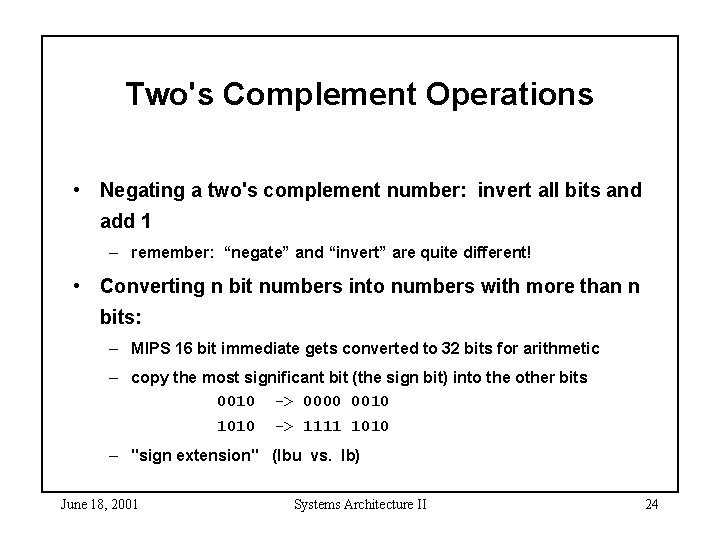

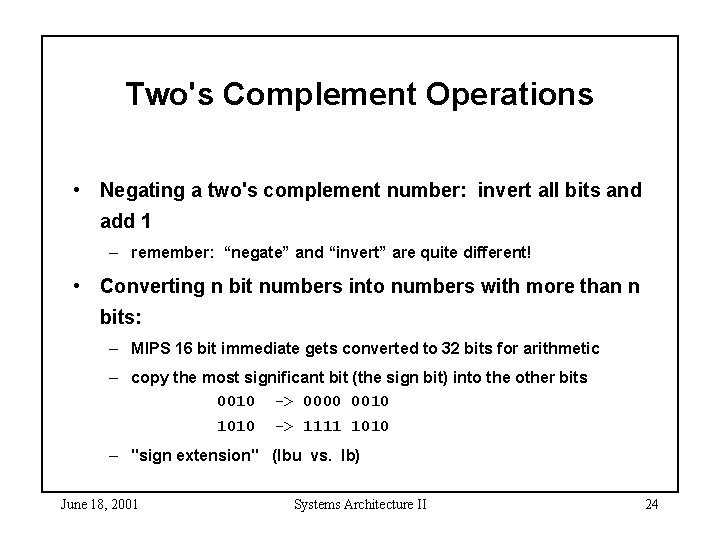

Two's Complement Operations • Negating a two's complement number: invert all bits and add 1 – remember: “negate” and “invert” are quite different! • Converting n bit numbers into numbers with more than n bits: – MIPS 16 bit immediate gets converted to 32 bits for arithmetic – copy the most significant bit (the sign bit) into the other bits 0010 -> 0000 0010 1010 -> 1111 1010 – "sign extension" (lbu vs. lb) June 18, 2001 Systems Architecture II 24

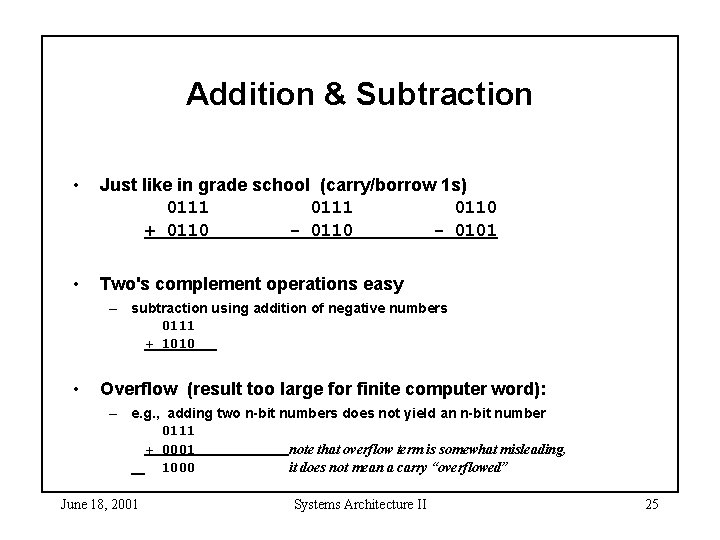

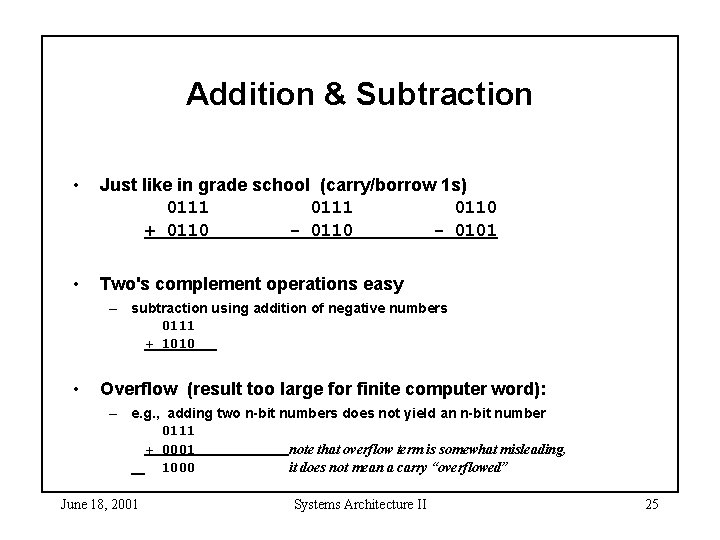

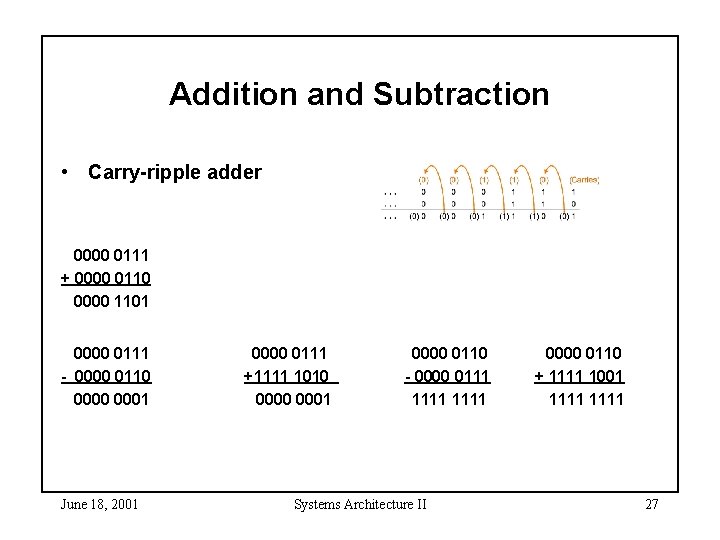

Addition & Subtraction • Just like in grade school (carry/borrow 1 s) 0111 0110 + 0110 - 0101 • Two's complement operations easy – subtraction using addition of negative numbers 0111 + 1010 • Overflow (result too large for finite computer word): – e. g. , adding two n-bit numbers does not yield an n-bit number 0111 + 0001 note that overflow term is somewhat misleading, 1000 it does not mean a carry “overflowed” June 18, 2001 Systems Architecture II 25

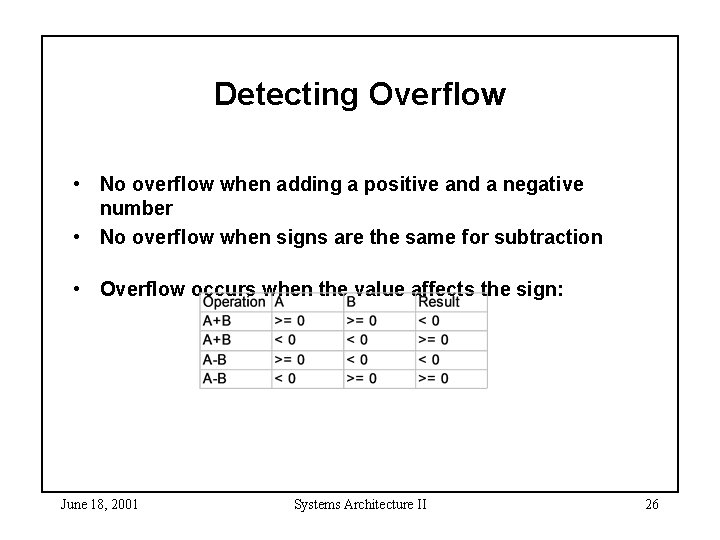

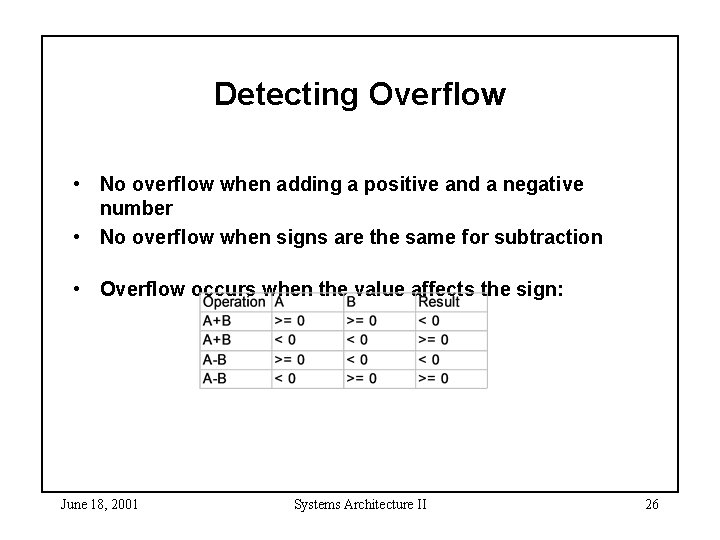

Detecting Overflow • No overflow when adding a positive and a negative number • No overflow when signs are the same for subtraction • Overflow occurs when the value affects the sign: June 18, 2001 Systems Architecture II 26

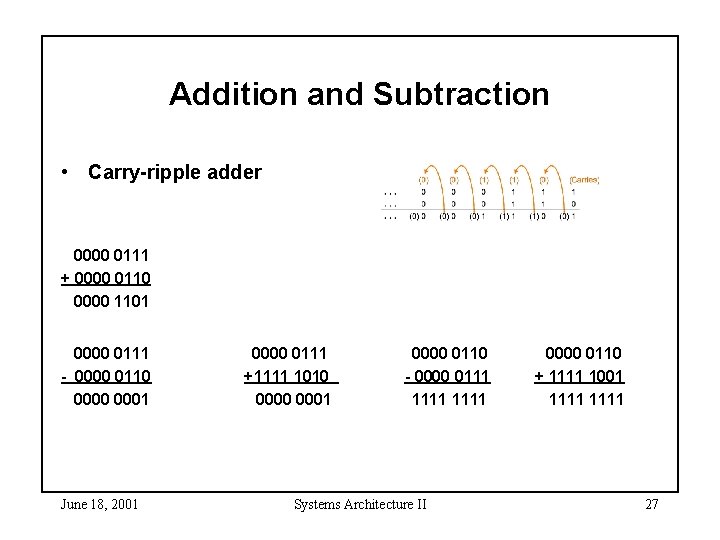

Addition and Subtraction • Carry-ripple adder 0000 0111 + 0000 0110 0000 1101 0000 0111 - 0000 0110 0001 June 18, 2001 0000 0111 +1111 1010 0001 0000 0110 - 0000 0111 1111 Systems Architecture II 0000 0110 + 1111 1001 1111 27

Logical Operations • • Shift left << Shift right >> Shift right arithmetic Bitwise and & Bitwise or | Bitwise complement (not) ~ Exclusive or ^ June 18, 2001 Systems Architecture II sll sra and, andi or, ori not (pseudo) xor, xori 28

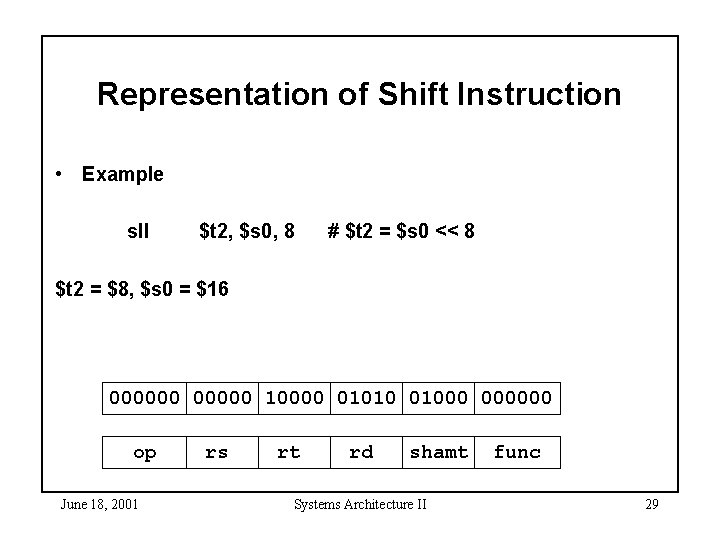

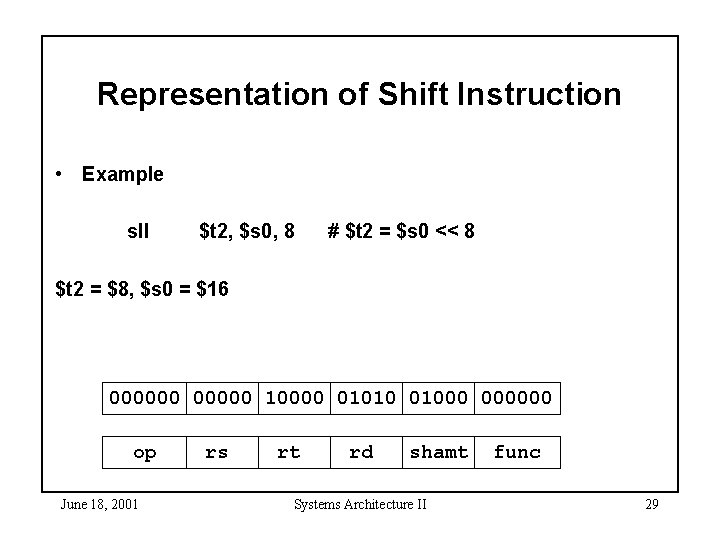

Representation of Shift Instruction • Example sll $t 2, $s 0, 8 # $t 2 = $s 0 << 8 $t 2 = $8, $s 0 = $16 000000 10000 01010 01000 000000 op June 18, 2001 rs rt rd shamt Systems Architecture II func 29

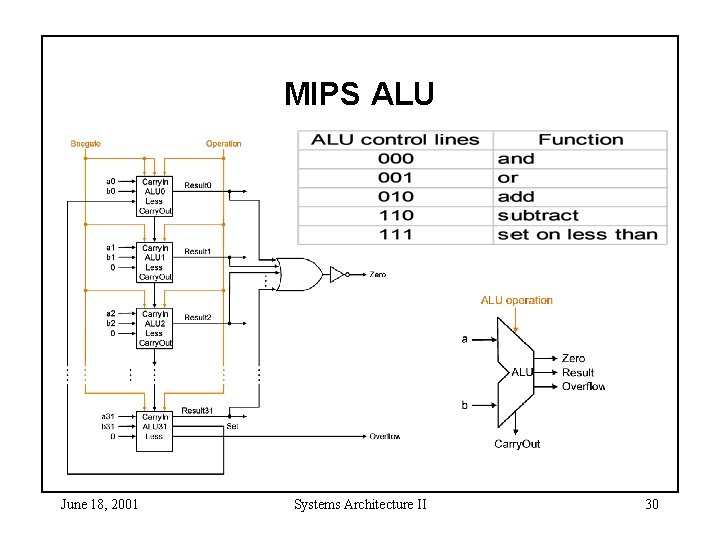

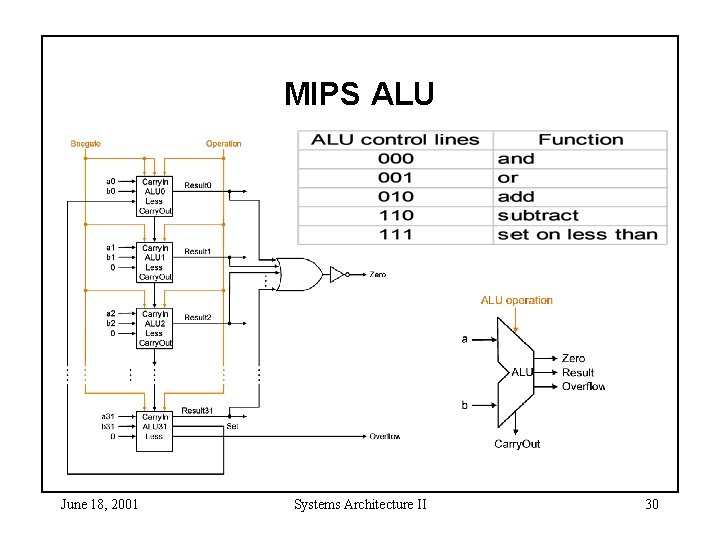

MIPS ALU June 18, 2001 Systems Architecture II 30

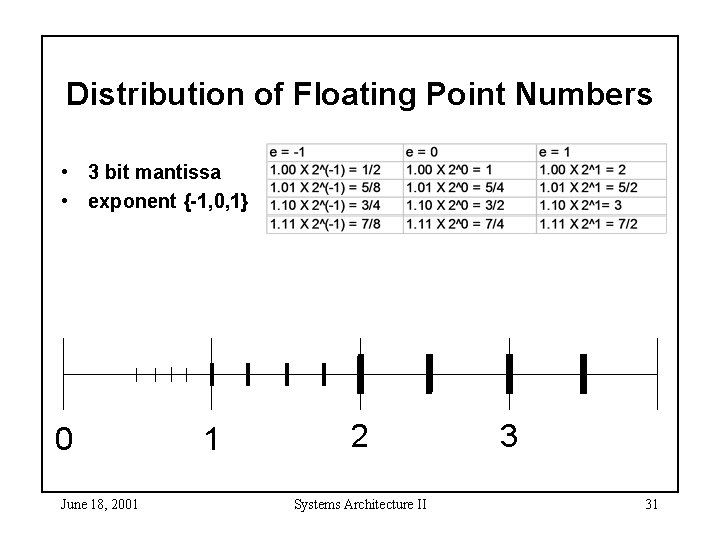

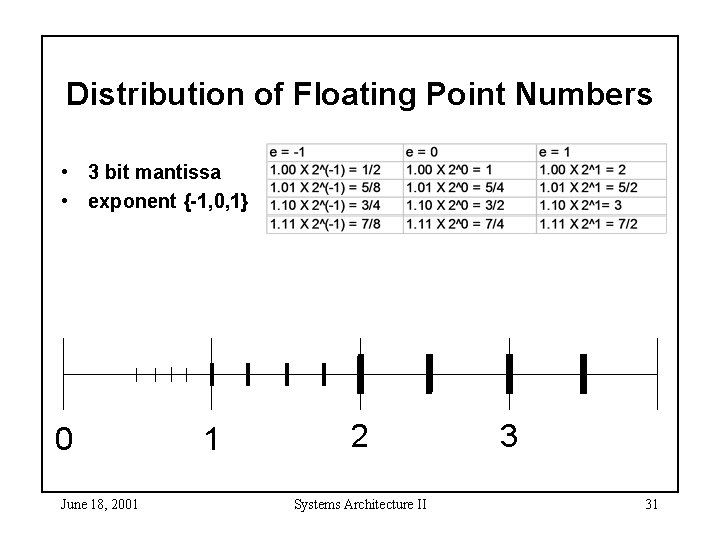

Distribution of Floating Point Numbers • 3 bit mantissa • exponent {-1, 0, 1} 0 June 18, 2001 1 2 Systems Architecture II 3 31

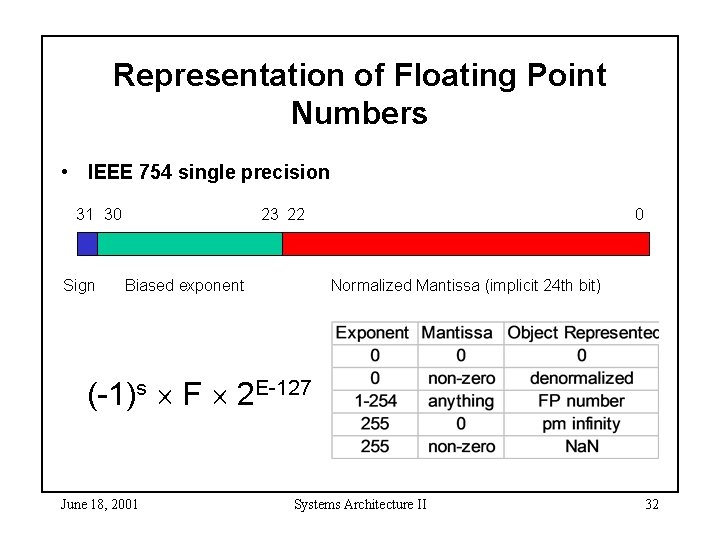

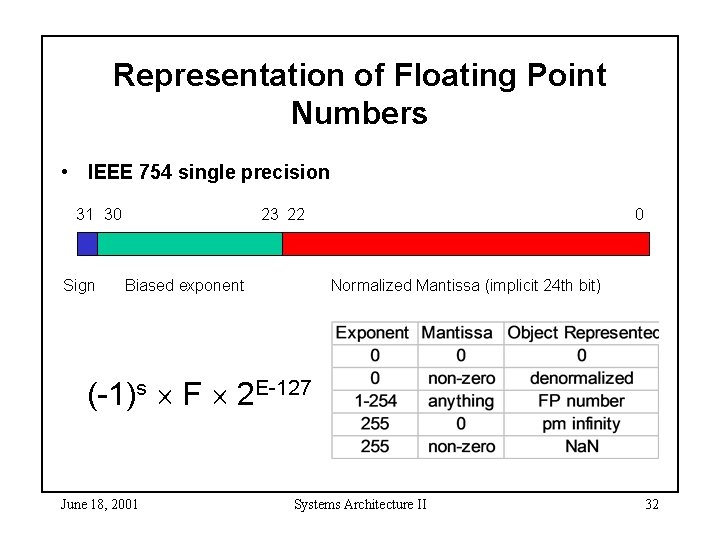

Representation of Floating Point Numbers • IEEE 754 single precision 31 30 Sign 23 22 Biased exponent 0 Normalized Mantissa (implicit 24 th bit) (-1)s F 2 E-127 June 18, 2001 Systems Architecture II 32

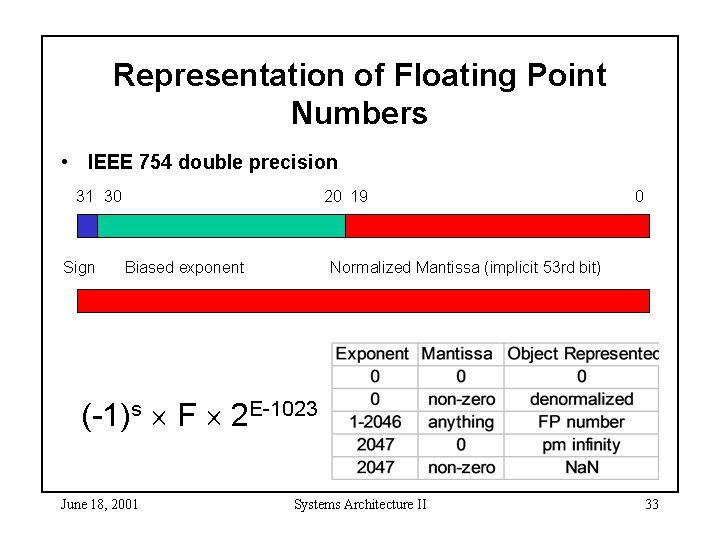

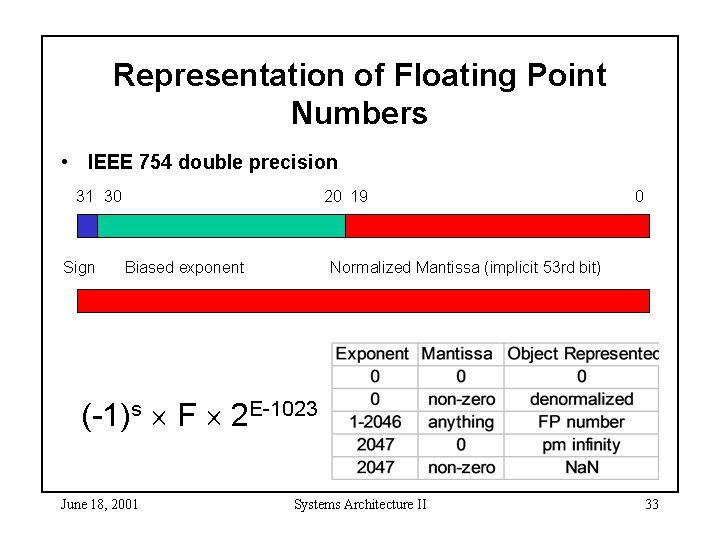

Representation of Floating Point Numbers • IEEE 754 double precision 31 30 Sign 20 19 Biased exponent 0 Normalized Mantissa (implicit 53 rd bit) (-1)s F 2 E-1023 June 18, 2001 Systems Architecture II 33

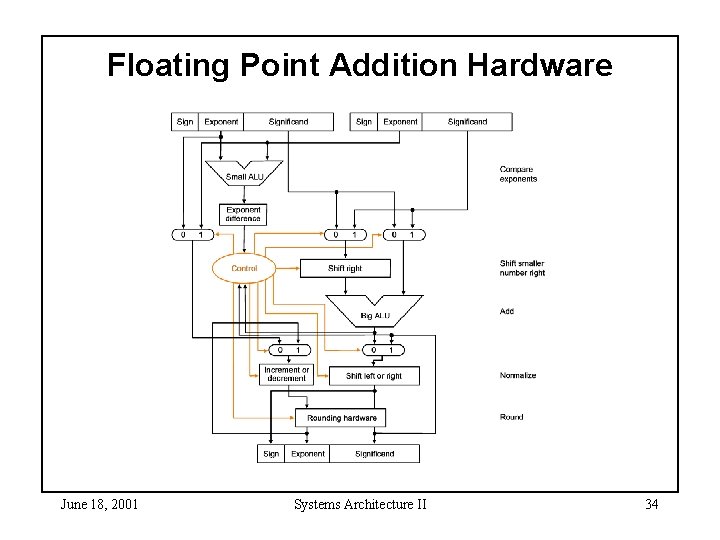

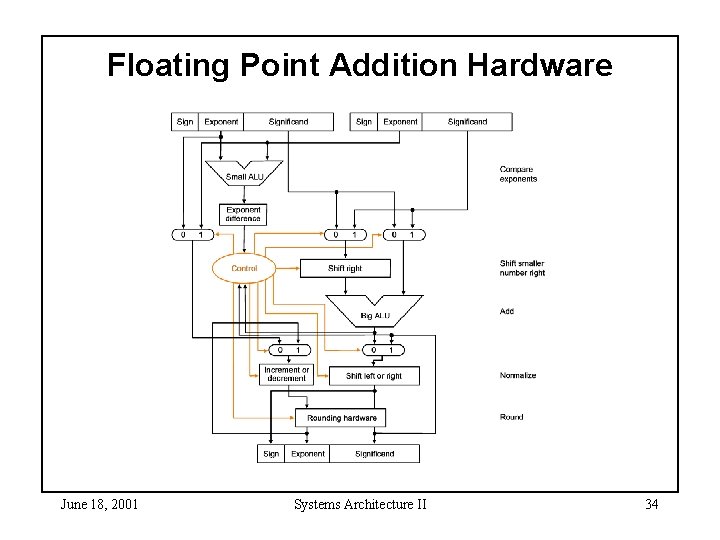

Floating Point Addition Hardware June 18, 2001 Systems Architecture II 34

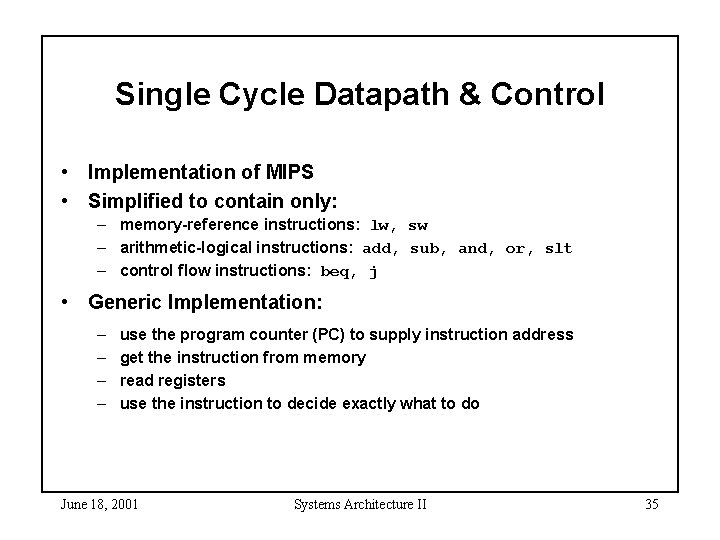

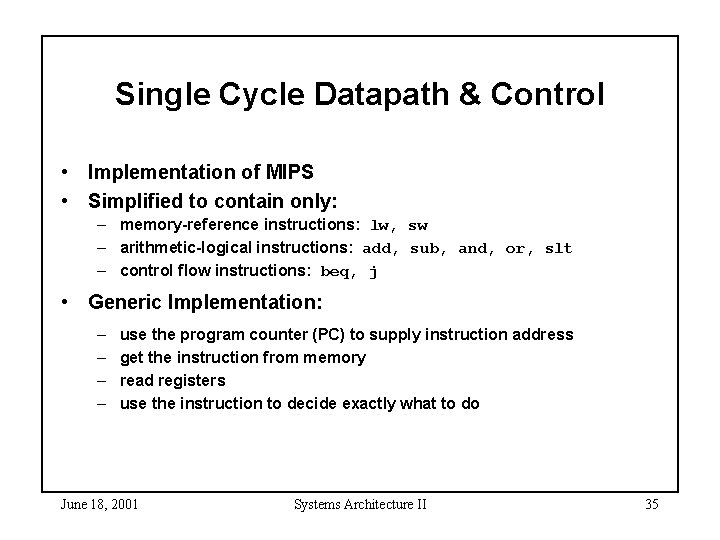

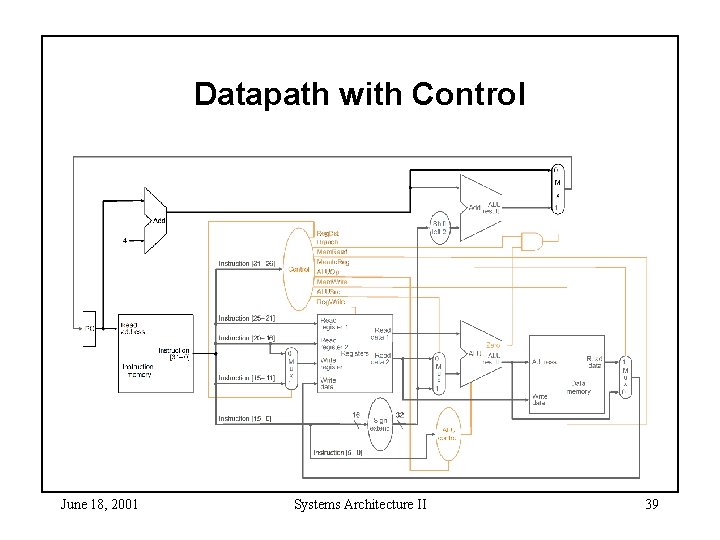

Single Cycle Datapath & Control • Implementation of MIPS • Simplified to contain only: – memory-reference instructions: lw, sw – arithmetic-logical instructions: add, sub, and, or, slt – control flow instructions: beq, j • Generic Implementation: – – use the program counter (PC) to supply instruction address get the instruction from memory read registers use the instruction to decide exactly what to do June 18, 2001 Systems Architecture II 35

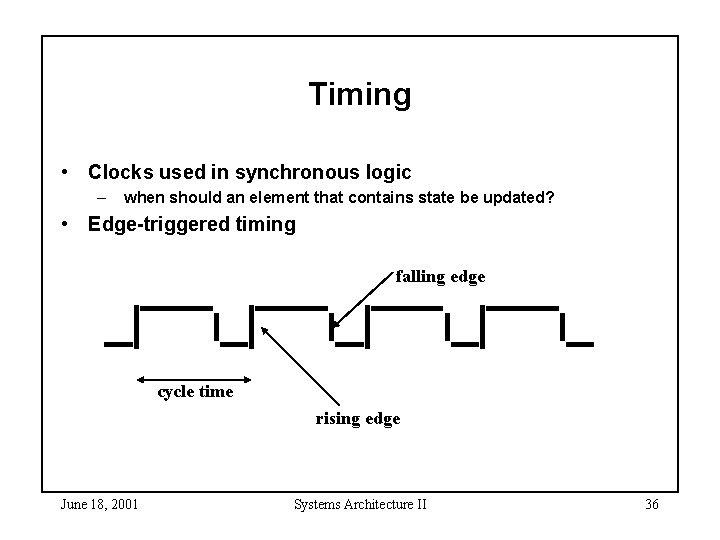

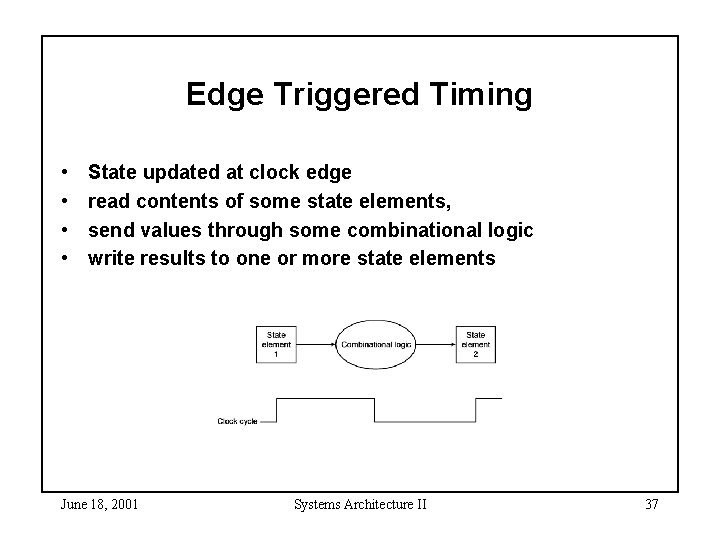

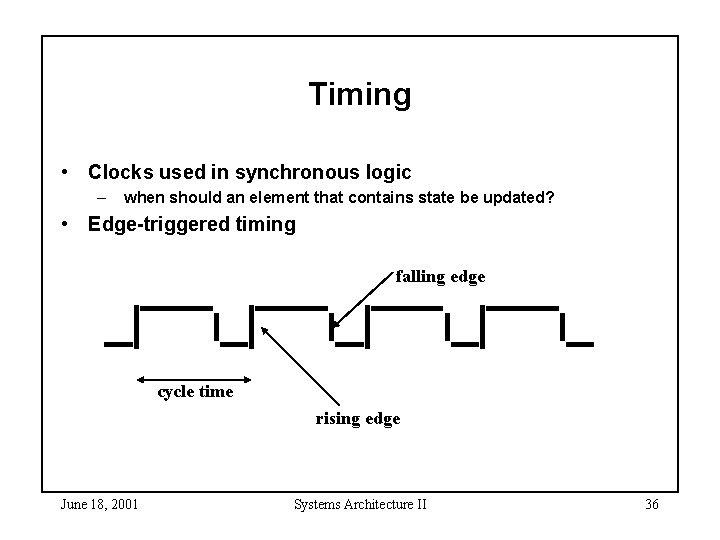

Timing • Clocks used in synchronous logic – when should an element that contains state be updated? • Edge-triggered timing falling edge cycle time rising edge June 18, 2001 Systems Architecture II 36

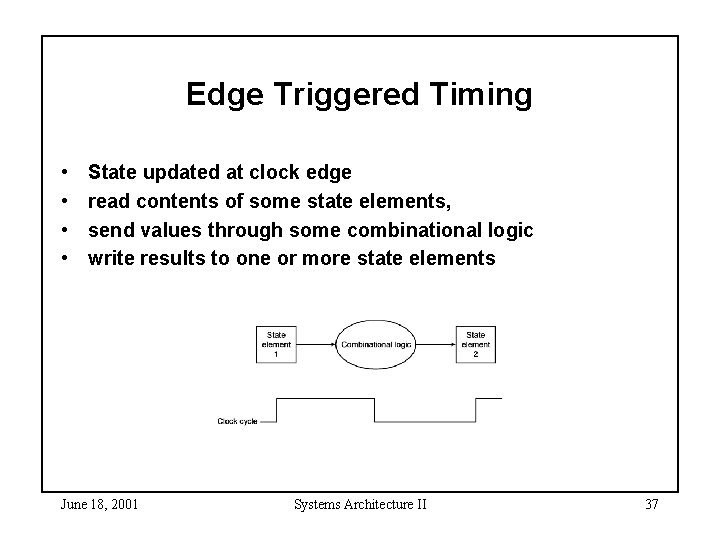

Edge Triggered Timing • • State updated at clock edge read contents of some state elements, send values through some combinational logic write results to one or more state elements June 18, 2001 Systems Architecture II 37

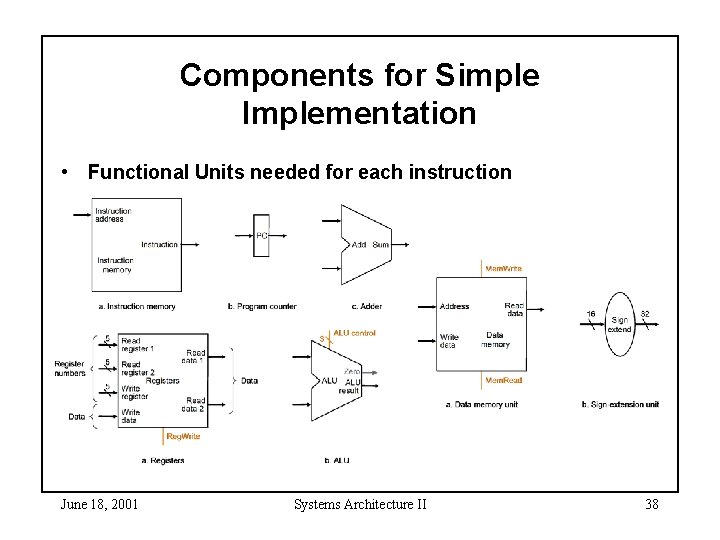

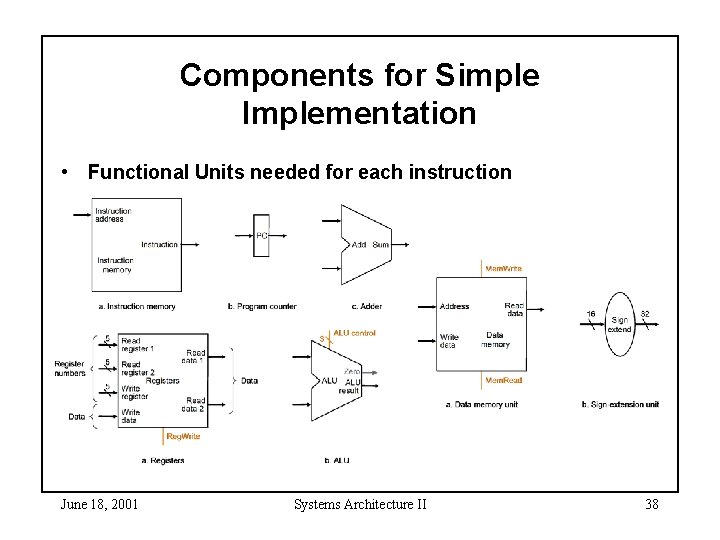

Components for Simple Implementation • Functional Units needed for each instruction June 18, 2001 Systems Architecture II 38

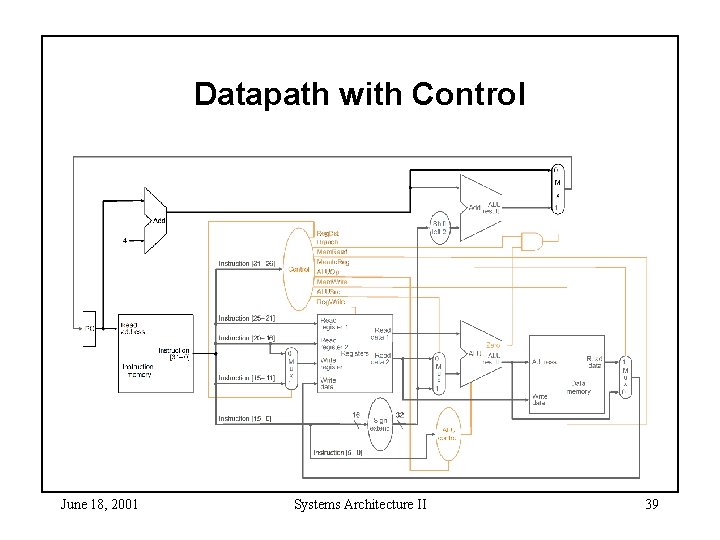

Datapath with Control June 18, 2001 Systems Architecture II 39

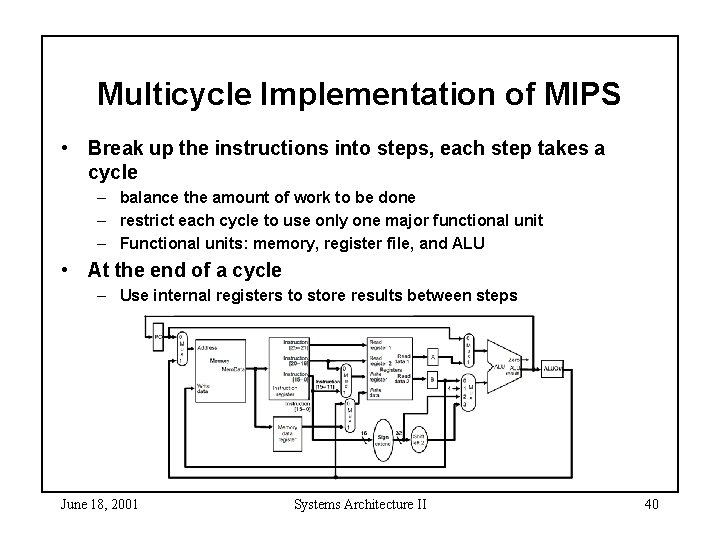

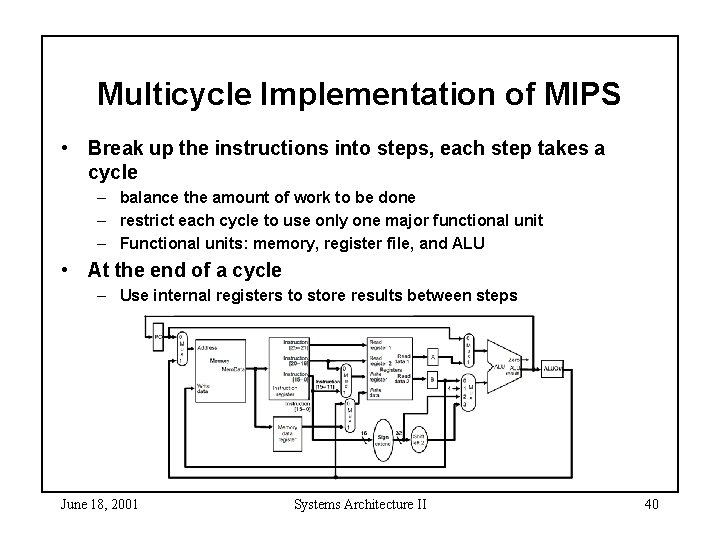

Multicycle Implementation of MIPS • Break up the instructions into steps, each step takes a cycle – balance the amount of work to be done – restrict each cycle to use only one major functional unit – Functional units: memory, register file, and ALU • At the end of a cycle – Use internal registers to store results between steps June 18, 2001 Systems Architecture II 40

![Execution Steps 1 Instruction fetch IR MemoryPC PC PC Execution Steps 1 Instruction fetch – IR = Memory[PC]; – PC = PC +](https://slidetodoc.com/presentation_image_h2/def484824f60cfab78154a4c22b97dad/image-41.jpg)

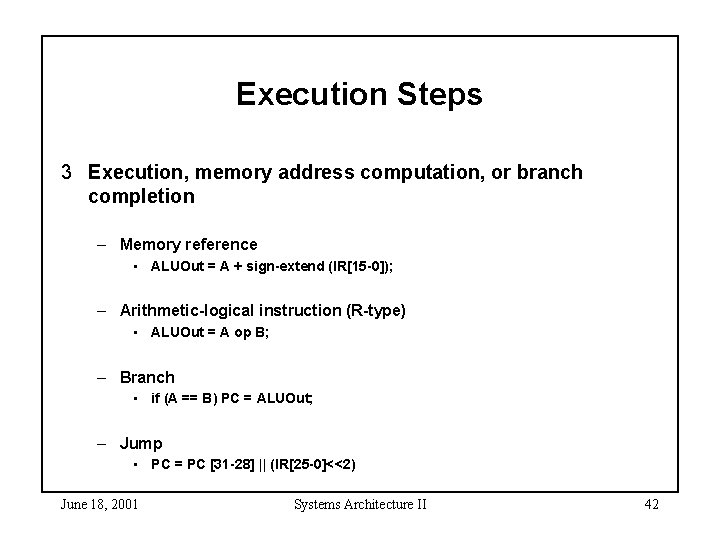

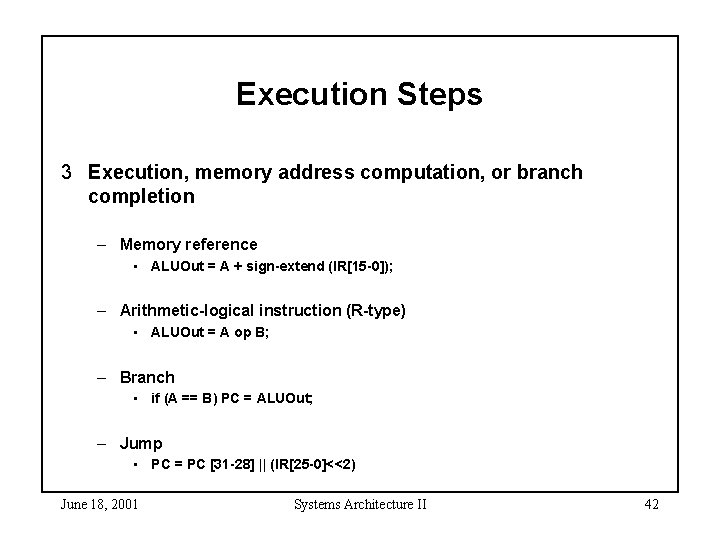

Execution Steps 1 Instruction fetch – IR = Memory[PC]; – PC = PC + 4; 2 Instruction decode and register fetch – A = Reg[IR[25 -21]]; – B = Reg[IR[20 -16]]; – ALUOut = PC + (sign-extend (IR[15 -0]) << 2); June 18, 2001 Systems Architecture II 41

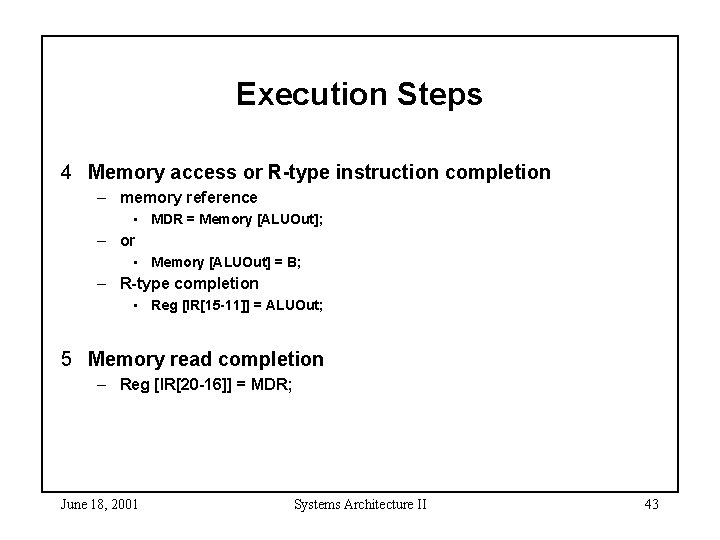

Execution Steps 3 Execution, memory address computation, or branch completion – Memory reference • ALUOut = A + sign-extend (IR[15 -0]); – Arithmetic-logical instruction (R-type) • ALUOut = A op B; – Branch • if (A == B) PC = ALUOut; – Jump • PC = PC [31 -28] || (IR[25 -0]<<2) June 18, 2001 Systems Architecture II 42

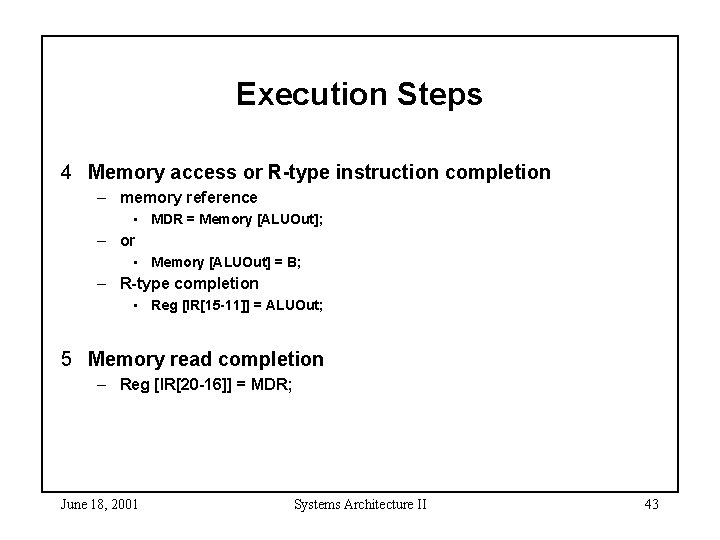

Execution Steps 4 Memory access or R-type instruction completion – memory reference • MDR = Memory [ALUOut]; – or • Memory [ALUOut] = B; – R-type completion • Reg [IR[15 -11]] = ALUOut; 5 Memory read completion – Reg [IR[20 -16]] = MDR; June 18, 2001 Systems Architecture II 43

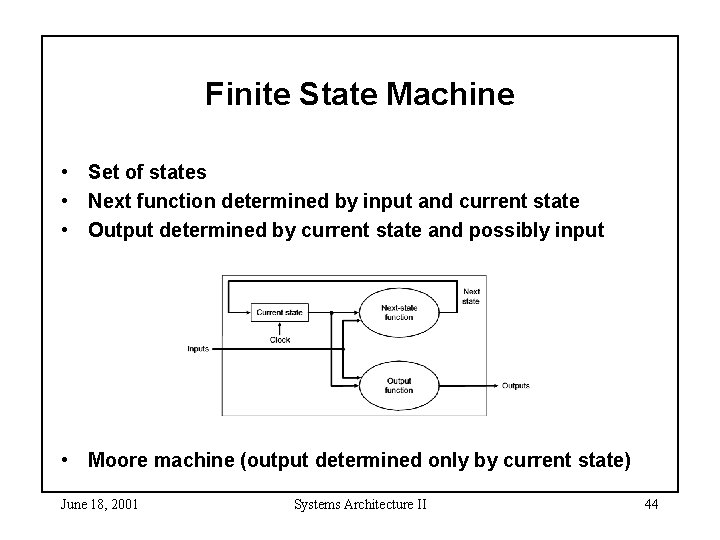

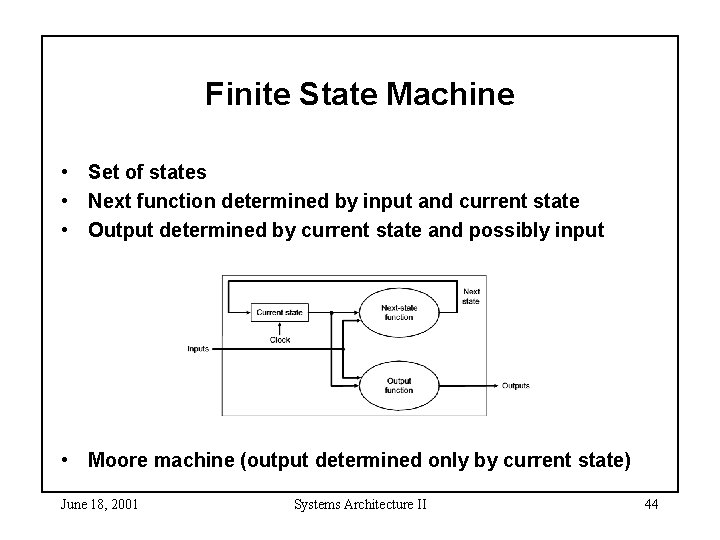

Finite State Machine • Set of states • Next function determined by input and current state • Output determined by current state and possibly input • Moore machine (output determined only by current state) June 18, 2001 Systems Architecture II 44

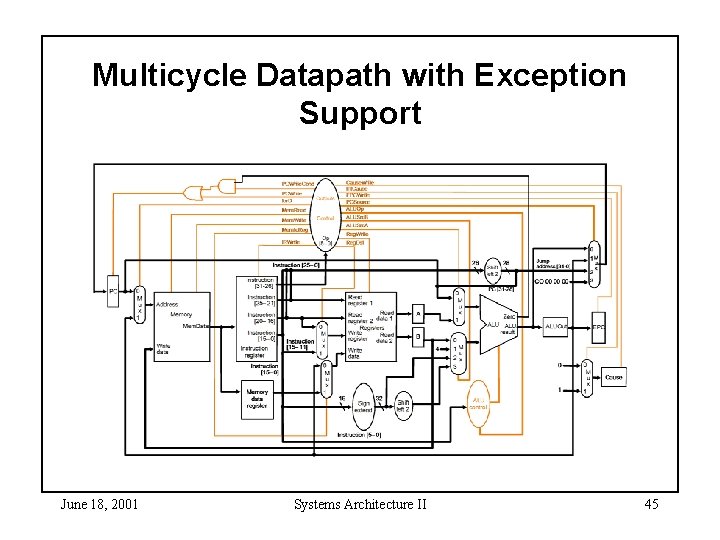

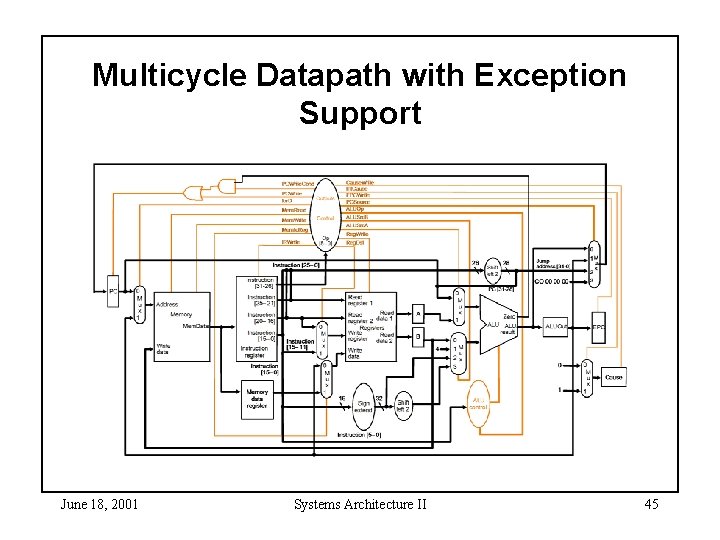

Multicycle Datapath with Exception Support June 18, 2001 Systems Architecture II 45

Multicycle Control with Exceptions June 18, 2001 Systems Architecture II 46

Implementation June 18, 2001 Systems Architecture II 47