System Level Flows for So C Architecture Analysis

![Register Modeling – Array [] syntax sugar – Register callbacks (pre, post) – Register Register Modeling – Array [] syntax sugar – Register callbacks (pre, post) – Register](https://slidetodoc.com/presentation_image_h2/7e08c845d17840f46cf67b0ba2042cad/image-7.jpg)

- Slides: 17

System Level Flows for So. C Architecture Analysis and Design Latest Trends and Best Practices In the domain of ESL methodologies So. C Architecture, Co-Design, Co-Verification & Raising the abstraction of chip design through High-Level Synthesis Enabled by using C, C++, System. C, TLM 2. 0 along with traditional RTL flows 1

System Level Flows for So. C Architecture Analysis and Design Agenda Defining a System. C Methodology for your Company Swaminathan Ramachandran, Director – Technology, Circuit. Sutra Technologies System Flows in a “hybrid” Environment – Intel's Approach Udupi Prasanna, Intel Using HLS to Migrate Open source Software Algorithms to Semiconductor Chip designs System. C Methodology for RISC-V Ecosystem Umesh Sisodia, CEO, Circuit. Sutra Technologies 2

Defining a System. C Methodology for your Company Swaminathan Ramachandran Director - Technology 3

Virtual Platform Development • Virtual Platforms have proved invaluable in the following fields: – Pre-silicon software development – Architectural Exploration – Verification and Validation • System. C/TLM 2. 0 has become the de-facto industry standard for development and exchange of IPs and Virtual Platforms. – Based on C++: fast, multi-paradigm, vast library, trained engineers – Open source: market acceptability, continuous improvements – EDA Tool Support: Vanilla C++ IDEs to specialized tools and debuggers 4

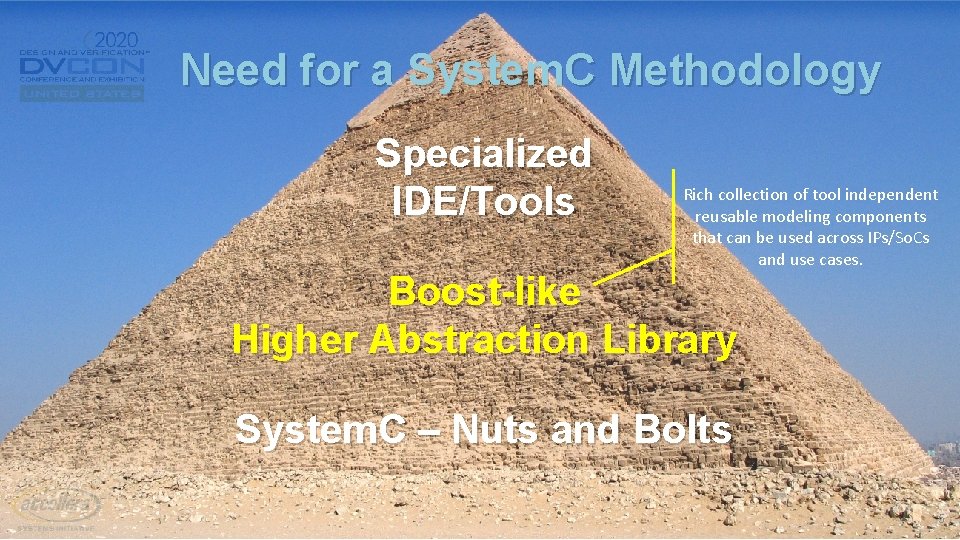

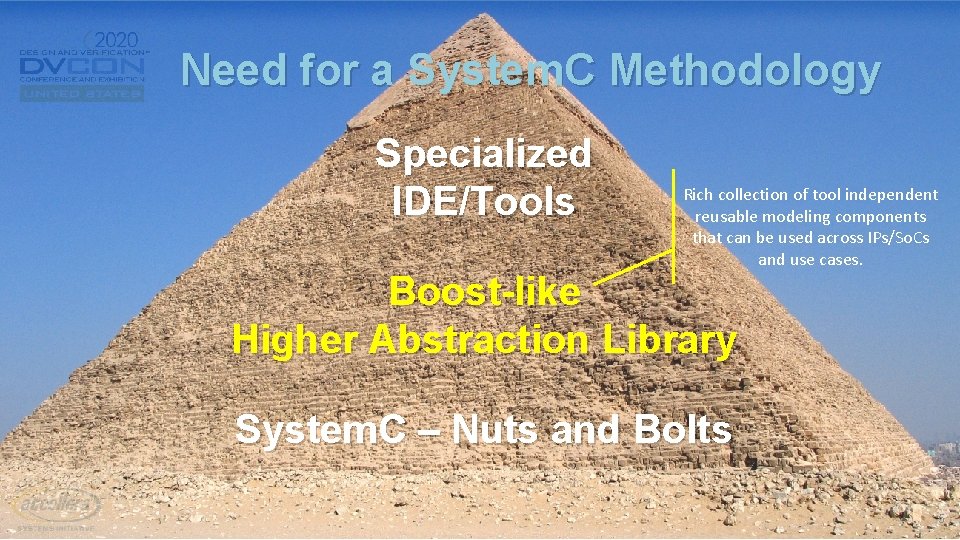

Need for a System. C Methodology Specialized IDE/Tools Rich collection of tool independent reusable modeling components that can be used across IPs/So. Cs and use cases. Boost-like Higher Abstraction Library System. C – Nuts and Bolts 5

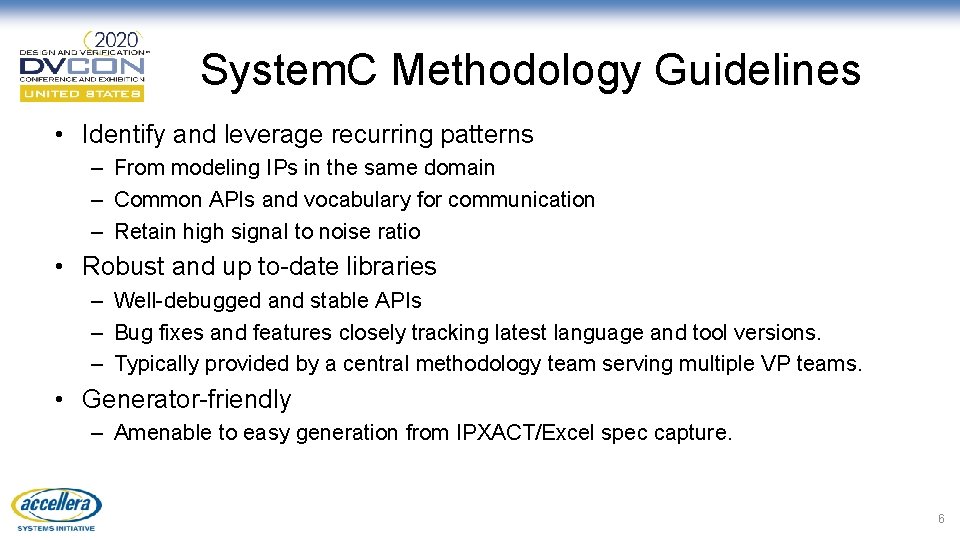

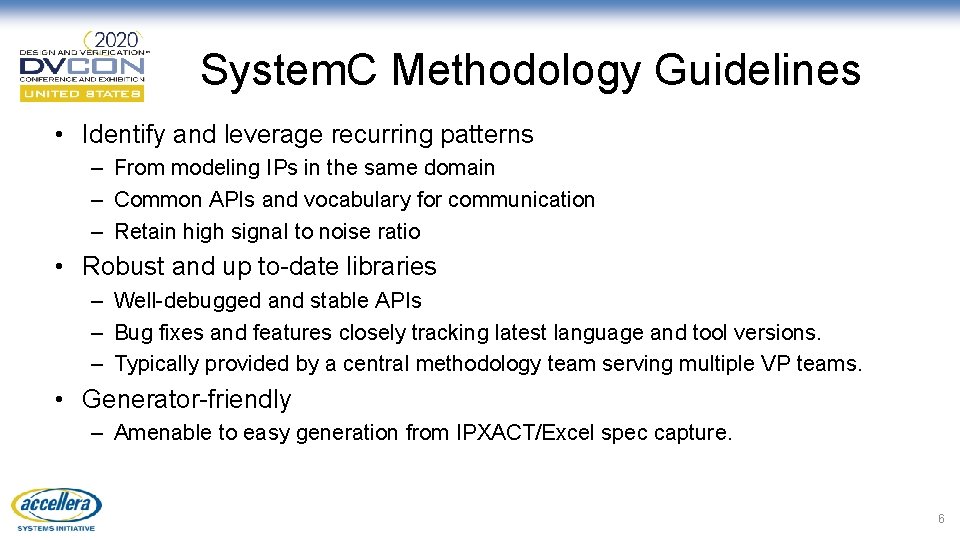

System. C Methodology Guidelines • Identify and leverage recurring patterns – From modeling IPs in the same domain – Common APIs and vocabulary for communication – Retain high signal to noise ratio • Robust and up to-date libraries – Well-debugged and stable APIs – Bug fixes and features closely tracking latest language and tool versions. – Typically provided by a central methodology team serving multiple VP teams. • Generator-friendly – Amenable to easy generation from IPXACT/Excel spec capture. 6

![Register Modeling Array syntax sugar Register callbacks pre post Register Register Modeling – Array [] syntax sugar – Register callbacks (pre, post) – Register](https://slidetodoc.com/presentation_image_h2/7e08c845d17840f46cf67b0ba2042cad/image-7.jpg)

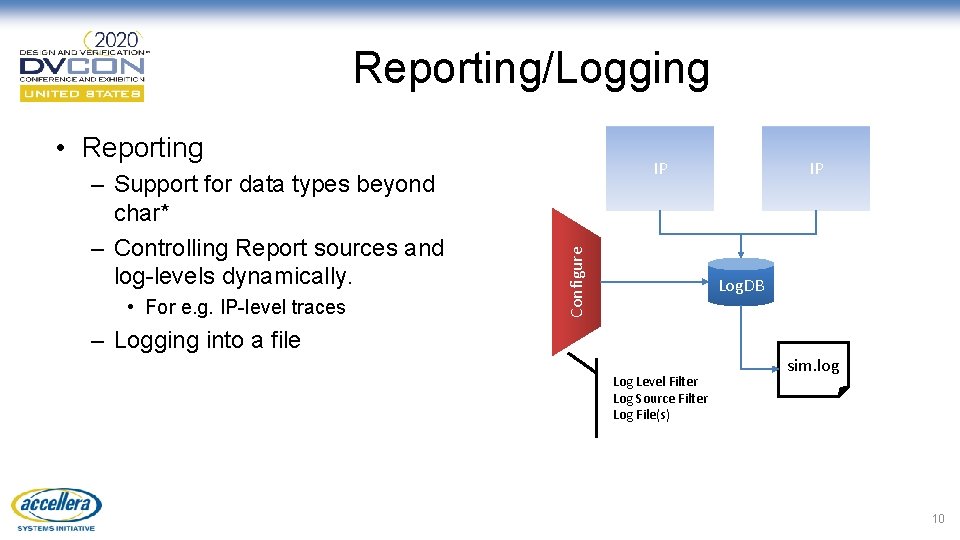

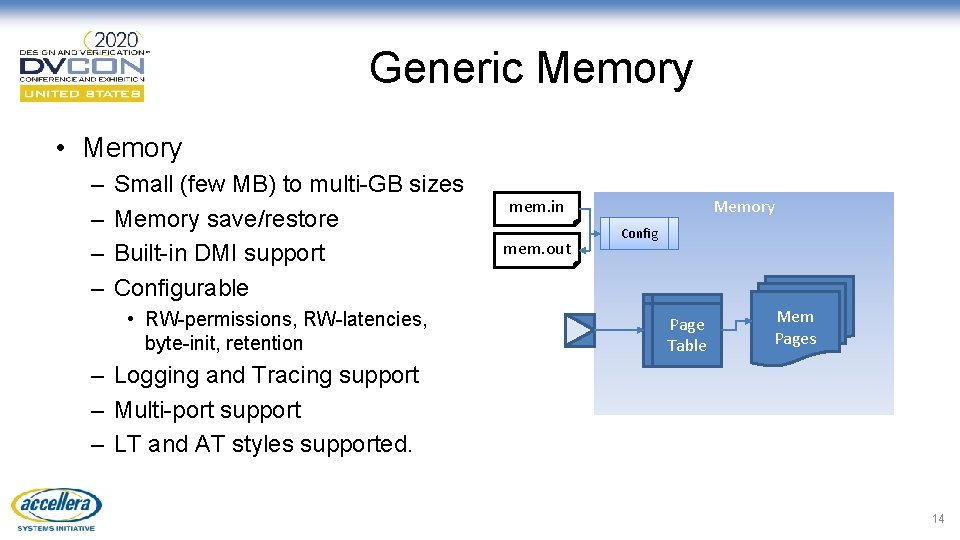

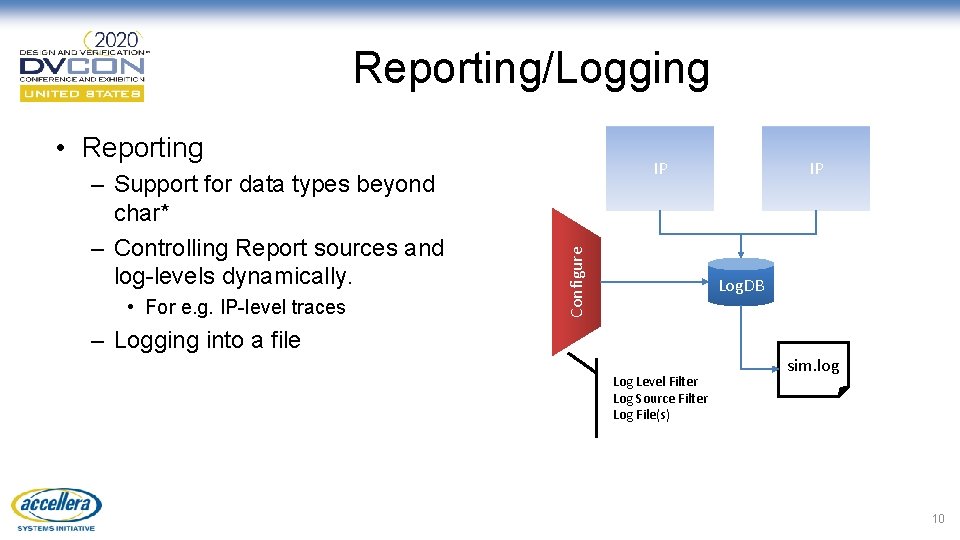

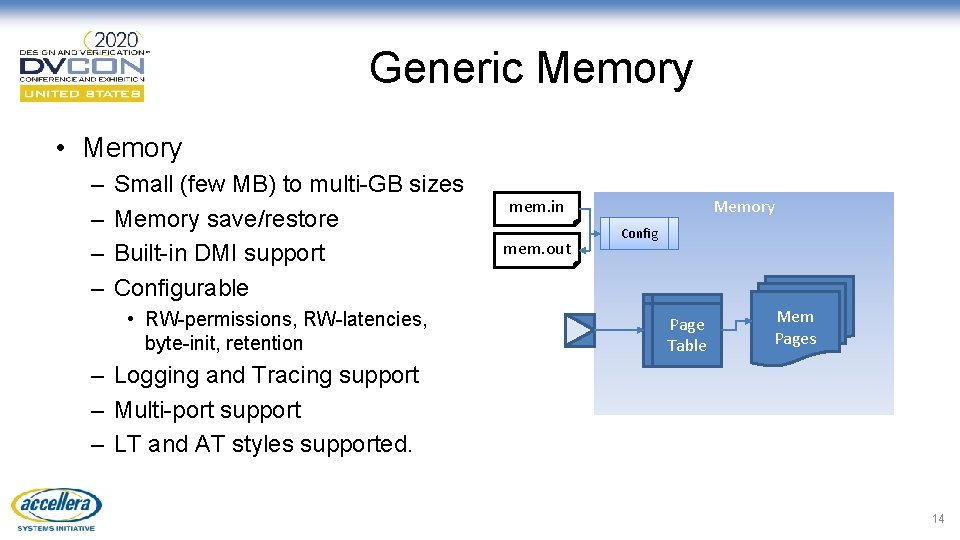

Register Modeling – Array [] syntax sugar – Register callbacks (pre, post) – Register Trace STS 0 x 104 CNTL post-callback Bit 0 0 x 100 Bitfield(s) pre-callback Bit 1 Bit 0 Register Bit 1 Address Map RSVD • Normal • Debug tlm_target_socket<> – IPXACT permission and access control modeling – Register access Register Bank IP -- GAP -0 x 10 C DATA 1 Data • Register Modeling 7

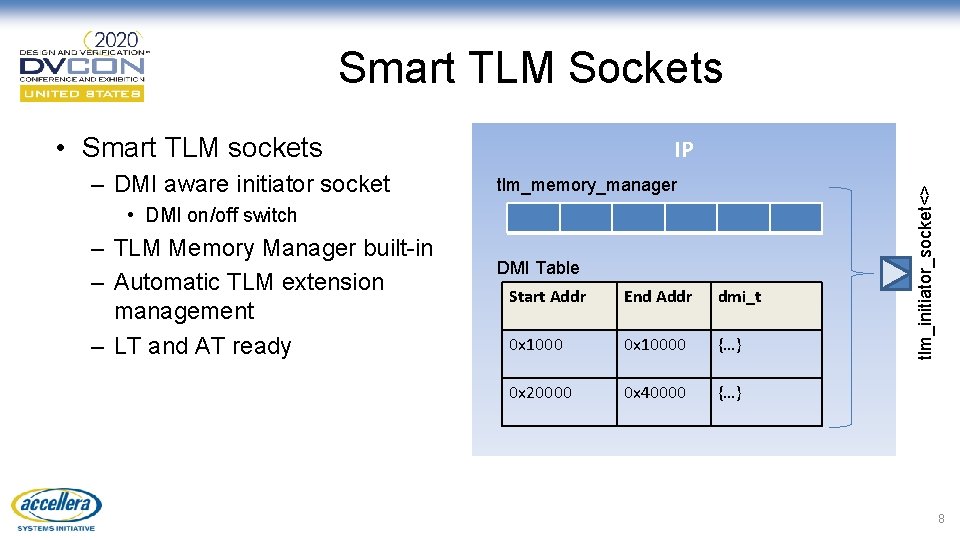

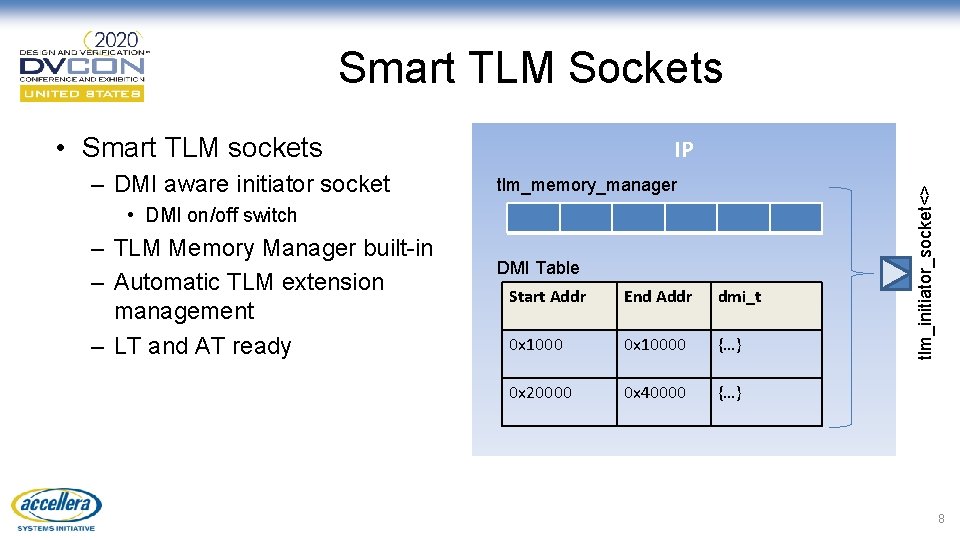

Smart TLM Sockets • Smart TLM sockets tlm_memory_manager • DMI on/off switch – TLM Memory Manager built-in – Automatic TLM extension management – LT and AT ready DMI Table Start Addr End Addr dmi_t 0 x 10000 {…} 0 x 20000 0 x 40000 {…} tlm_initiator_socket<> – DMI aware initiator socket IP 8

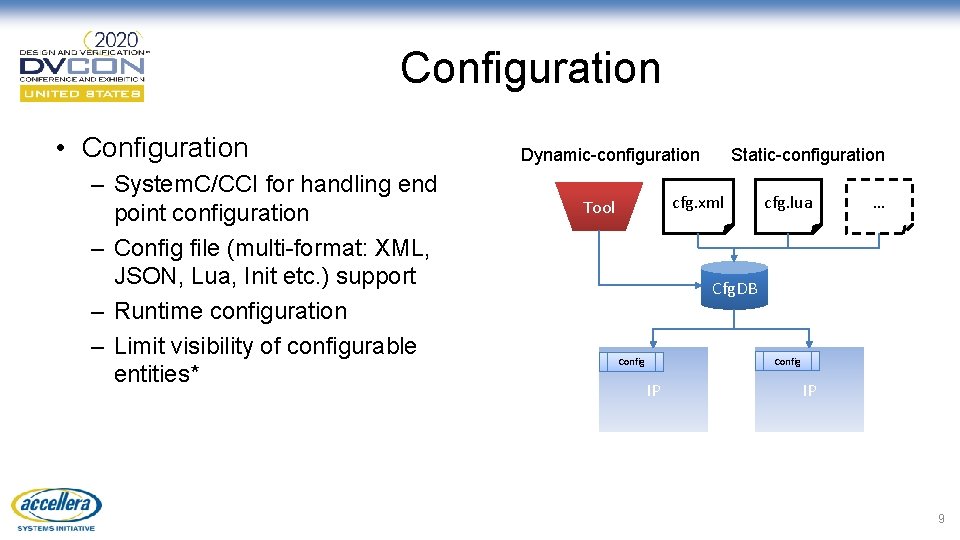

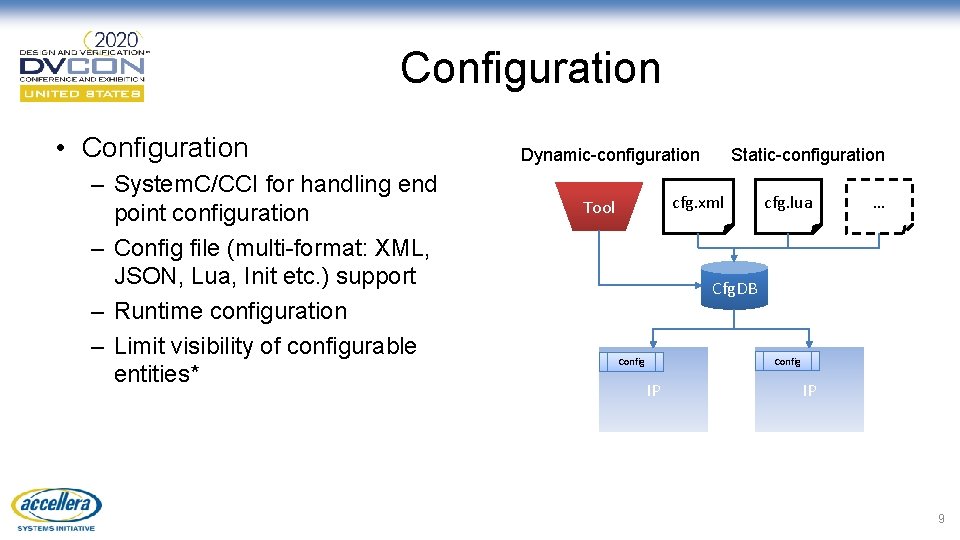

Configuration • Configuration – System. C/CCI for handling end point configuration – Config file (multi-format: XML, JSON, Lua, Init etc. ) support – Runtime configuration – Limit visibility of configurable entities* Dynamic-configuration Static-configuration cfg. xml Tool cfg. lua … Cfg. DB Config IP IP 9

Reporting/Logging • Reporting • For e. g. IP-level traces Configure – Support for data types beyond char* – Controlling Report sources and log-levels dynamically. IP IP Log. DB – Logging into a file Log Level Filter Log Source Filter Log File(s) sim. log 10

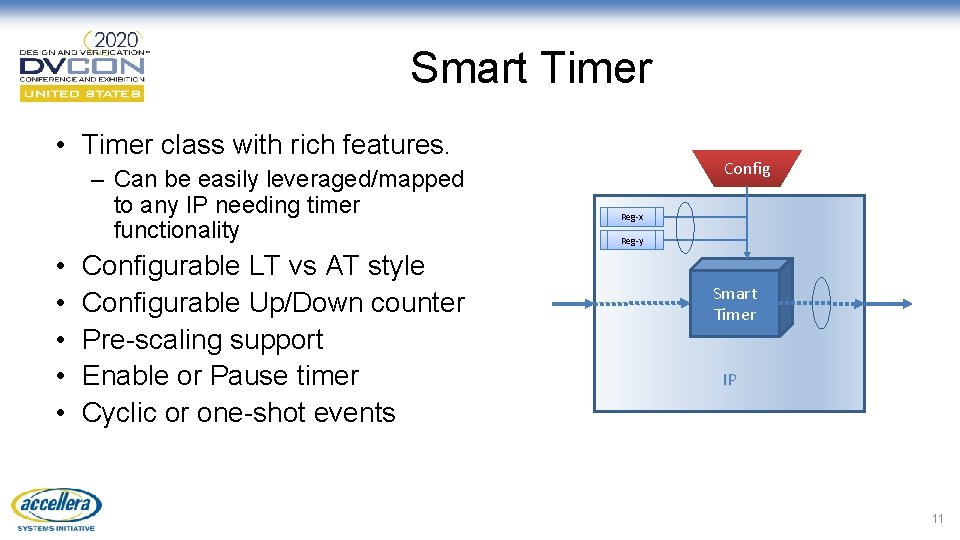

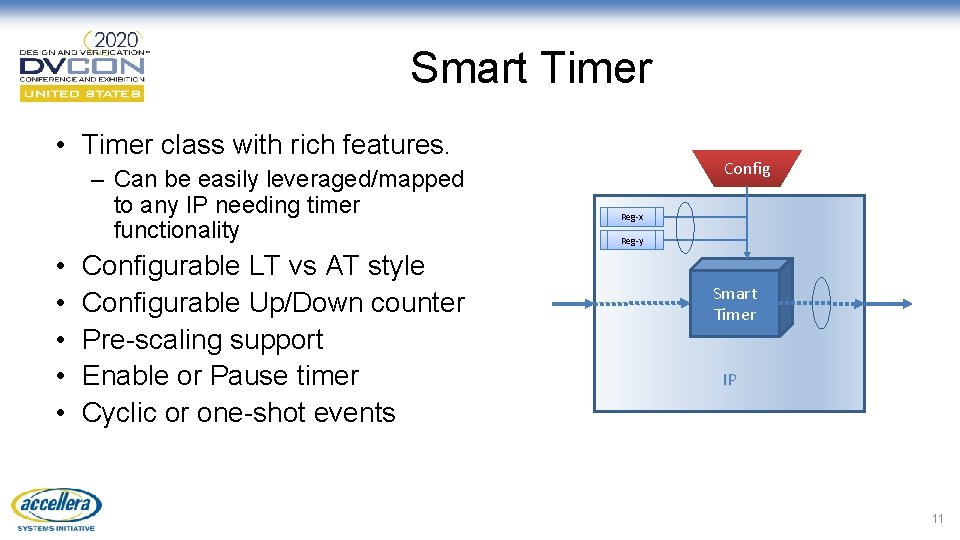

Smart Timer • Timer class with rich features. – Can be easily leveraged/mapped to any IP needing timer functionality • • • Configurable LT vs AT style Configurable Up/Down counter Pre-scaling support Enable or Pause timer Cyclic or one-shot events Config Reg-x Reg-y Smart Timer IP 11

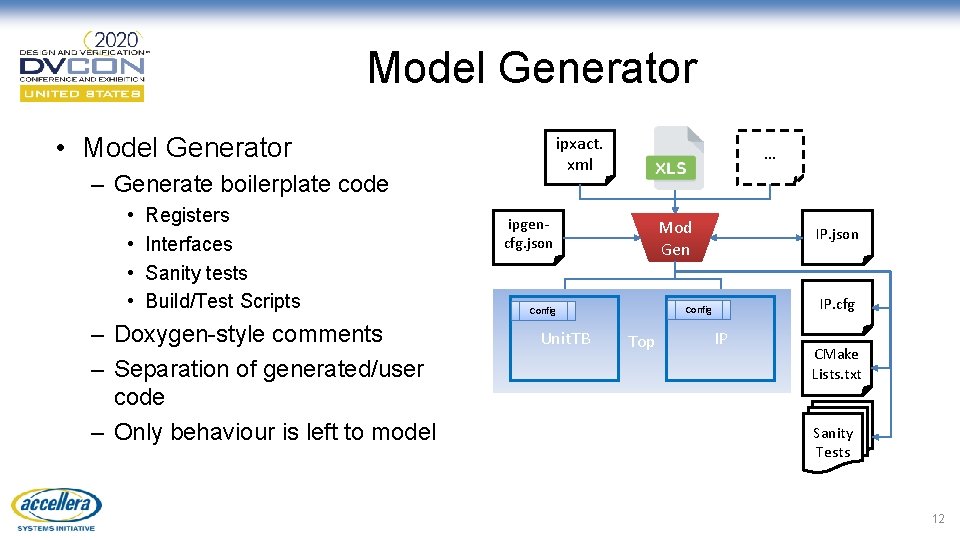

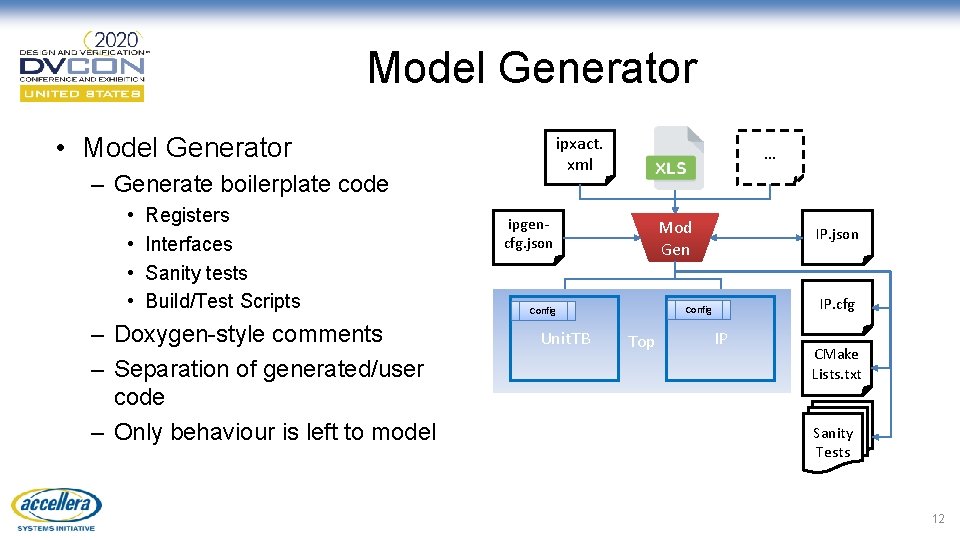

Model Generator • Model Generator ipxact. xml – Generate boilerplate code • • Registers Interfaces Sanity tests Build/Test Scripts – Doxygen-style comments – Separation of generated/user code – Only behaviour is left to model … ipgencfg. json Mod Gen IP. cfg Config Unit. TB IP. json Top IP CMake Lists. txt Sanity Tests 12

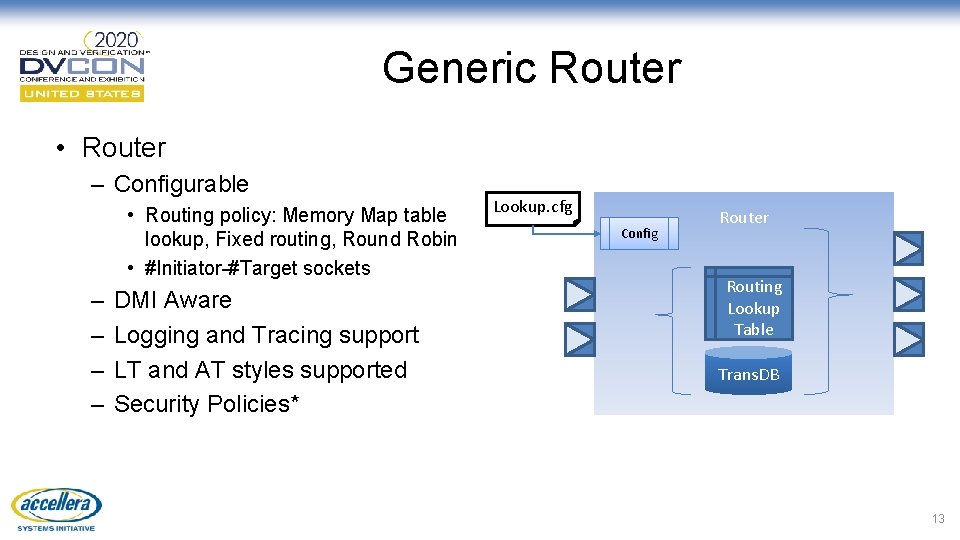

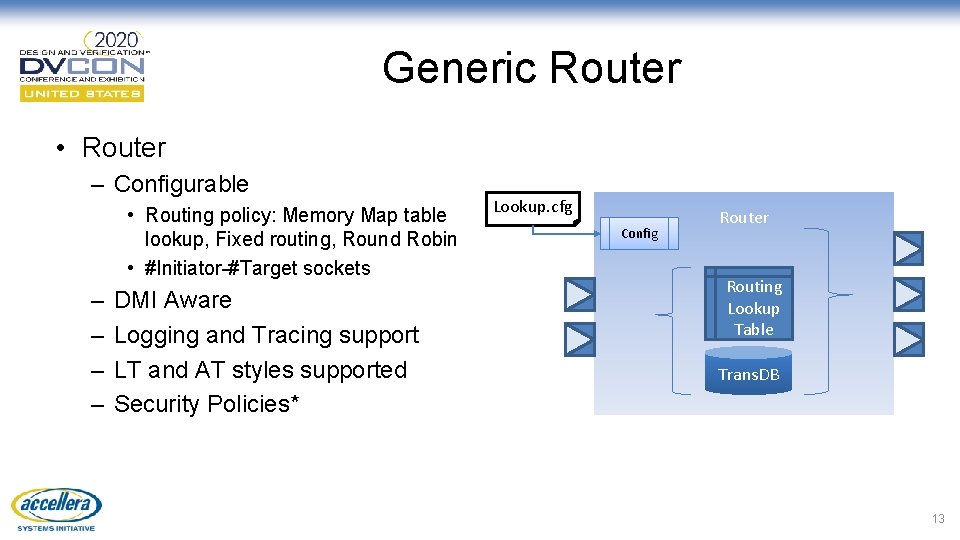

Generic Router • Router – Configurable • Routing policy: Memory Map table lookup, Fixed routing, Round Robin • #Initiator-#Target sockets – – DMI Aware Logging and Tracing support LT and AT styles supported Security Policies* Lookup. cfg Config Router Routing Lookup Table Trans. DB 13

Generic Memory • Memory – – Small (few MB) to multi-GB sizes Memory save/restore Built-in DMI support Configurable • RW-permissions, RW-latencies, byte-init, retention Memory mem. in mem. out Config Page Table Mem Pages – Logging and Tracing support – Multi-port support – LT and AT styles supported. 14

VP Development: Nice to have • Python Frontend – Interface System. C IPs with Python – Easier to use for testing teams without knowing nitty-gritty of System. C – Less code • Faster to write • Lesser bugs • OS agnostic libraries – TCP/IP Server-Client – UART host terminal connection • … 15

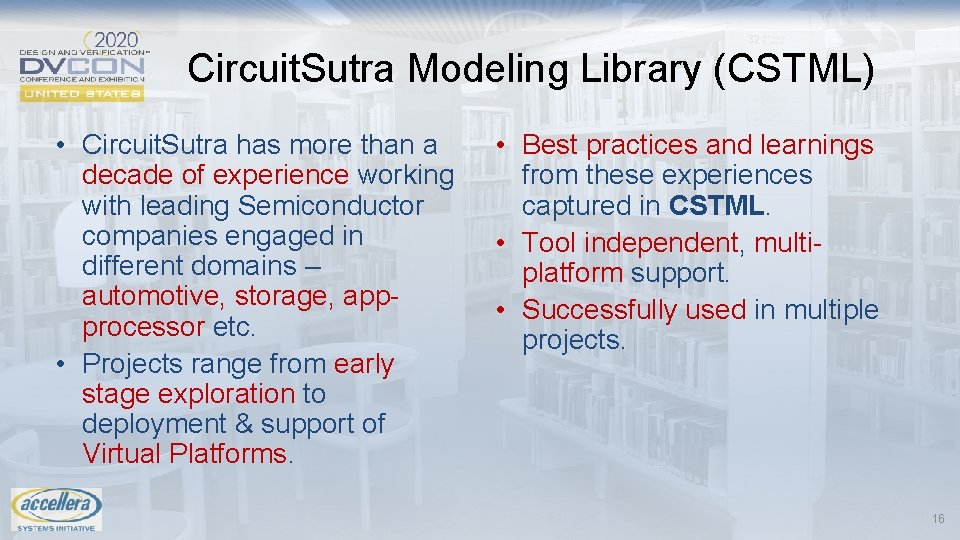

Circuit. Sutra Modeling Library (CSTML) • Circuit. Sutra has more than a decade of experience working with leading Semiconductor companies engaged in different domains – automotive, storage, appprocessor etc. • Projects range from early stage exploration to deployment & support of Virtual Platforms. • Best practices and learnings from these experiences captured in CSTML. • Tool independent, multiplatform support. • Successfully used in multiple projects. 16

Thank you for your time. 17