SYS Module System Clocks FXTAL BCLK Reset Circuit

SYS Module System Clocks FXTAL BCLK Reset Circuit Reset Conditions Bootstrap Initialization 1 -1

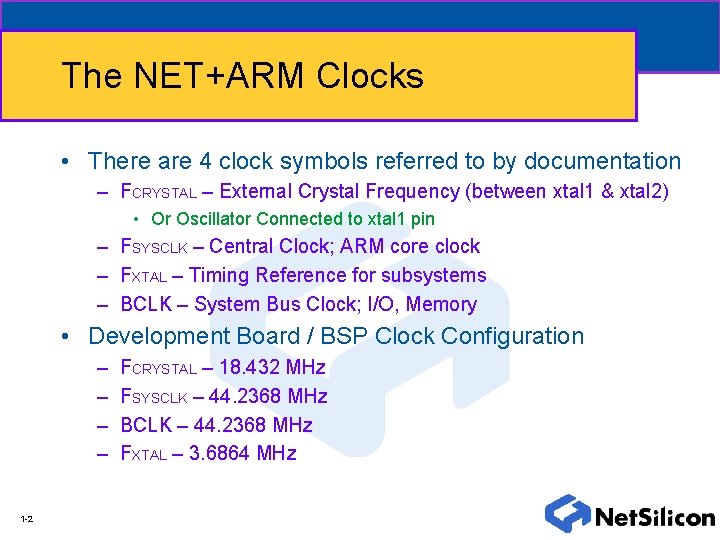

The NET+ARM Clocks • There are 4 clock symbols referred to by documentation – FCRYSTAL – External Crystal Frequency (between xtal 1 & xtal 2) • Or Oscillator Connected to xtal 1 pin – FSYSCLK – Central Clock; ARM core clock – FXTAL – Timing Reference for subsystems – BCLK – System Bus Clock; I/O, Memory • Development Board / BSP Clock Configuration – – 1 -2 FCRYSTAL – 18. 432 MHz FSYSCLK – 44. 2368 MHz BCLK – 44. 2368 MHz FXTAL – 3. 6864 MHz

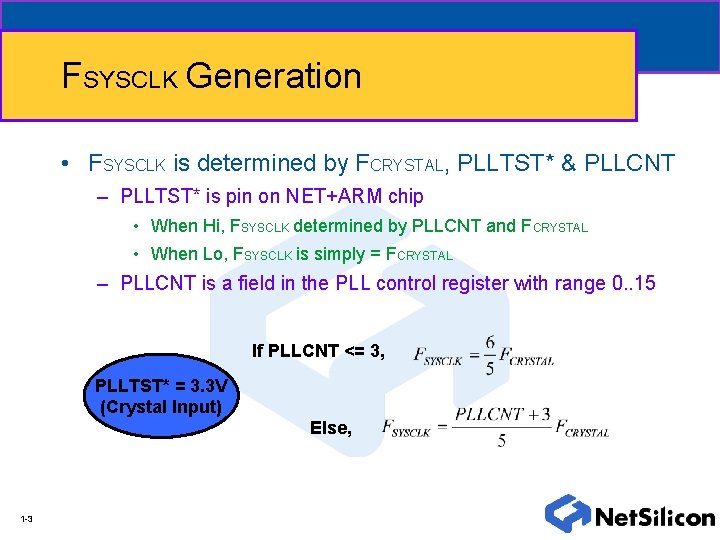

FSYSCLK Generation • FSYSCLK is determined by FCRYSTAL, PLLTST* & PLLCNT – PLLTST* is pin on NET+ARM chip • When Hi, FSYSCLK determined by PLLCNT and FCRYSTAL • When Lo, FSYSCLK is simply = FCRYSTAL – PLLCNT is a field in the PLL control register with range 0. . 15 If PLLCNT <= 3, PLLTST* = 3. 3 V (Crystal Input) Else, 1 -3

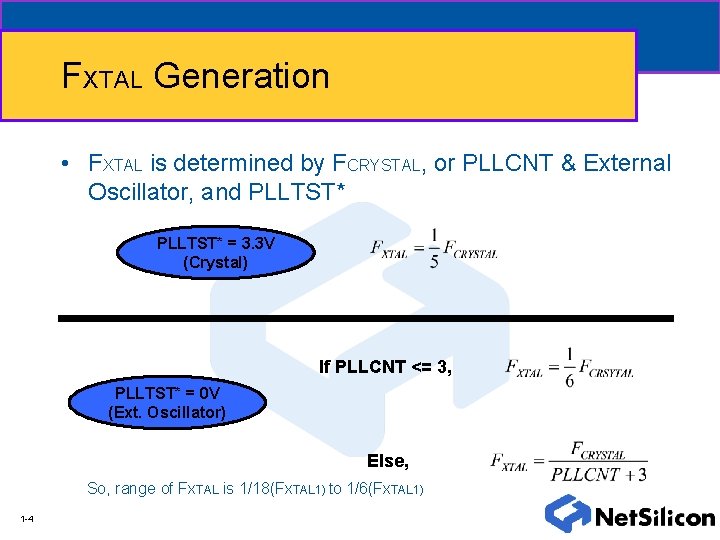

FXTAL Generation • FXTAL is determined by FCRYSTAL, or PLLCNT & External Oscillator, and PLLTST* = 3. 3 V (Crystal) If PLLCNT <= 3, PLLTST* = 0 V (Ext. Oscillator) Else, So, range of FXTAL is 1/18(FXTAL 1) to 1/6(FXTAL 1) 1 -4

BCLK • The System Bus Clock, BCLK is controlled by the two bit configuration field, BSPEED, in the System Control Register, as a fraction of FSYSCLK: – 00 – ¼ Speed – 01 – ½ Speed – 10 – Full Speed – 11 – Reserved • Note: The reset condition is ’ 00’ 1 -5

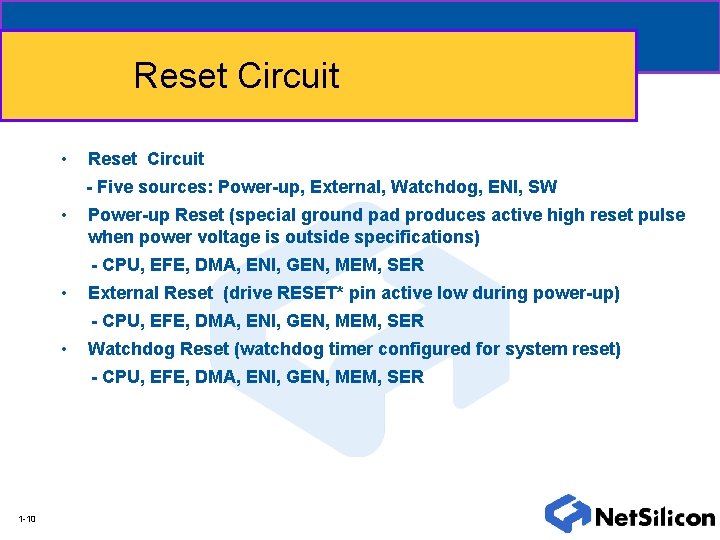

Reset Circuit • Reset Circuit - Five sources: Power-up, External, Watchdog, ENI, SW • Power-up Reset (special ground pad produces active high reset pulse when power voltage is outside specifications) - CPU, EFE, DMA, ENI, GEN, MEM, SER • External Reset (drive RESET* pin active low during power-up) - CPU, EFE, DMA, ENI, GEN, MEM, SER • Watchdog Reset (watchdog timer configured for system reset) - CPU, EFE, DMA, ENI, GEN, MEM, SER 1 -6

SYS Module • ENI Reset - CPU, EFE, DMA, GEN, SER • Software Reset - EFE, DMA, GEN, SER 1 -7

SYS Module • The following GEN Module register fields are not affected by ENI or Software Reset: - BSPEED, BCLKD (general control register) - Port. A, Port. B, Port. C 1 -8

Hardware reset requirements From the Hardware Reference Guide • Vcc becomes stable (3. 0 – 3. 6 Volts) • Reset pin is de-asserted 40 msec later • Or reset line is pulsed for 1 usec while running • Recommend using reset part on board 1 -9

Reset Circuit • Reset Circuit - Five sources: Power-up, External, Watchdog, ENI, SW • Power-up Reset (special ground pad produces active high reset pulse when power voltage is outside specifications) - CPU, EFE, DMA, ENI, GEN, MEM, SER • External Reset (drive RESET* pin active low during power-up) - CPU, EFE, DMA, ENI, GEN, MEM, SER • Watchdog Reset (watchdog timer configured for system reset) - CPU, EFE, DMA, ENI, GEN, MEM, SER 1 -10

After reset is de-asserted • 512 clocks after reset goes away, NET+ARM starts fetching instructions from CS 0, location 0 x 0 • During this time, the entire memory map is CS 0 • Execution from FLASH only • Program Execution begins 1 -11

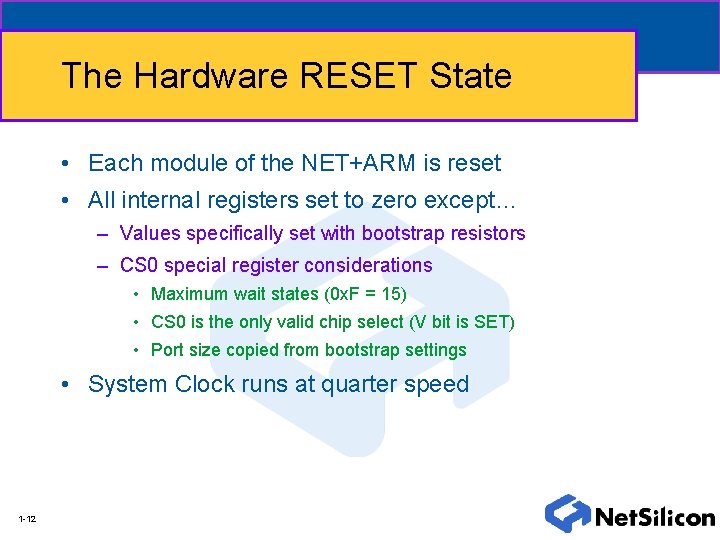

The Hardware RESET State • Each module of the NET+ARM is reset • All internal registers set to zero except… – Values specifically set with bootstrap resistors – CS 0 special register considerations • Maximum wait states (0 x. F = 15) • CS 0 is the only valid chip select (V bit is SET) • Port size copied from bootstrap settings • System Clock runs at quarter speed 1 -12

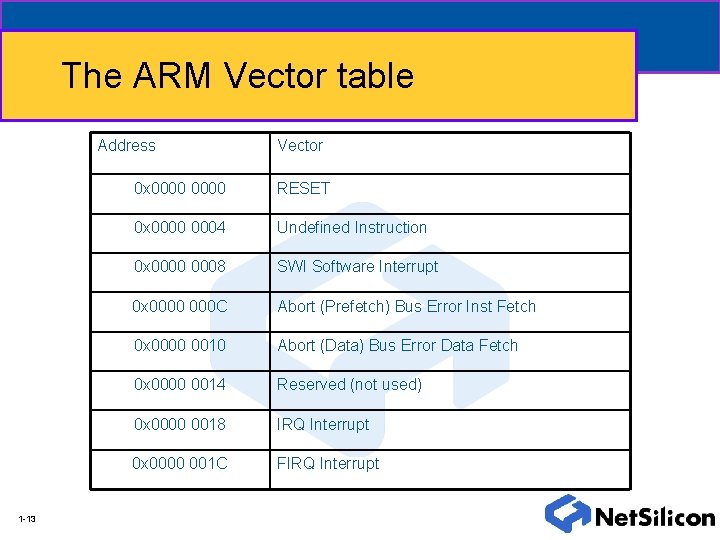

The ARM Vector table Address 1 -13 Vector 0 x 0000 RESET 0 x 0000 0004 Undefined Instruction 0 x 0000 0008 SWI Software Interrupt 0 x 0000 000 C Abort (Prefetch) Bus Error Inst Fetch 0 x 0000 0010 Abort (Data) Bus Error Data Fetch 0 x 0000 0014 Reserved (not used) 0 x 0000 0018 IRQ Interrupt 0 x 0000 001 C FIRQ Interrupt

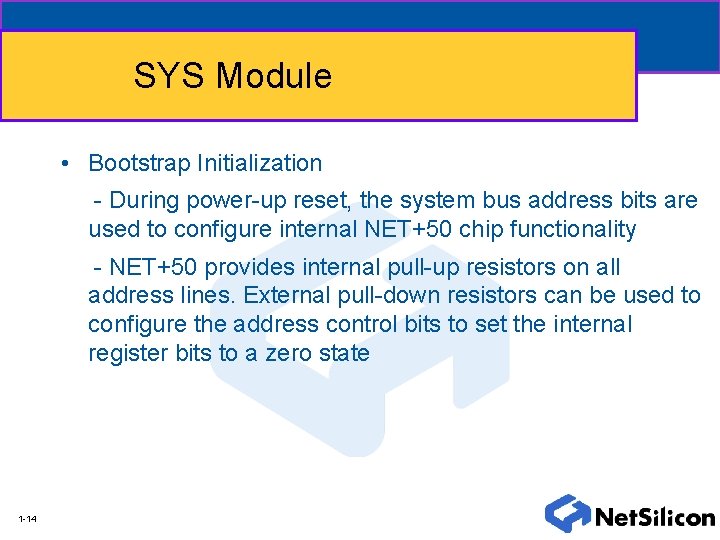

SYS Module • Bootstrap Initialization - During power-up reset, the system bus address bits are used to configure internal NET+50 chip functionality - NET+50 provides internal pull-up resistors on all address lines. External pull-down resistors can be used to configure the address control bits to set the internal register bits to a zero state 1 -14

![SYS Module • Bootstrap Initialization ADDR[27] Endian configuration 0 Little-endian 1 Big-endian Note: Inverted SYS Module • Bootstrap Initialization ADDR[27] Endian configuration 0 Little-endian 1 Big-endian Note: Inverted](http://slidetodoc.com/presentation_image/7cb6d05cb49d4753f189aecf2799bba9/image-15.jpg)

SYS Module • Bootstrap Initialization ADDR[27] Endian configuration 0 Little-endian 1 Big-endian Note: Inverted endian bit is loaded into LENDIAN (bit 31) of System Control Register ADDR[26] CPU Bootstrap 0 CPU disabled (GEN_BUSER set to 1) 1 CPU enabled (GEN_BUSER set to 0) 1 -15

![SYS Module • Bootstrap Initialization ADDR[25] Bus Arbitration (GEN_IARB) 0 Use External system bus SYS Module • Bootstrap Initialization ADDR[25] Bus Arbitration (GEN_IARB) 0 Use External system bus](http://slidetodoc.com/presentation_image/7cb6d05cb49d4753f189aecf2799bba9/image-16.jpg)

SYS Module • Bootstrap Initialization ADDR[25] Bus Arbitration (GEN_IARB) 0 Use External system bus arbiter 1 Use Internal system bus arbiter ADDR[24: 23] CS 0 Bootstrap “ 00” Bootstrap disabled “ 01” 32 -bit SRAM port; 15 wait states “ 10” 32 -bit DRAM port; 15 wait states “ 11” 16 -bit SRAM port; 15 wait states 1 -16

![SYS Module • Bootstrap Initialization ADDR[22: 20] ENI Configuration ( sets ENIMODE bits of SYS Module • Bootstrap Initialization ADDR[22: 20] ENI Configuration ( sets ENIMODE bits of](http://slidetodoc.com/presentation_image/7cb6d05cb49d4753f189aecf2799bba9/image-17.jpg)

SYS Module • Bootstrap Initialization ADDR[22: 20] ENI Configuration ( sets ENIMODE bits of General Control Register) “ 000” GPIO mode “ 001” 1284 mode “ 010” Reserved “ 011” Reserved “ 100” 16 -bit Shared Ram mode “ 101” 8 -bit Shared Ram mode “ 110” 16 -bit FIFO mode, w/ 8 K Shared Ram “ 111” 8 -bit FIFO mode, w/8 K Shared Ram 1 -17

![SYS Module • Bootstrap Initialization ADDR[19: 09] GEN_ID Setting ( sets GEN_ID bits of SYS Module • Bootstrap Initialization ADDR[19: 09] GEN_ID Setting ( sets GEN_ID bits of](http://slidetodoc.com/presentation_image/7cb6d05cb49d4753f189aecf2799bba9/image-18.jpg)

SYS Module • Bootstrap Initialization ADDR[19: 09] GEN_ID Setting ( sets GEN_ID bits of System Status Register) user-defined for application-specific configuration ADDR[08] Reserved ADDR[07] ENI Control PSIO* (ENI Control Register) 0 PSIO* 1 Normal Note: Inverted address bit is loaded into PSIO (bit 9) of ENI Control Register 1 -18

![SYS Module • Bootstrap Initialization ADDR[06] ENI Control WR_OC 0 Output Driver is TTL SYS Module • Bootstrap Initialization ADDR[06] ENI Control WR_OC 0 Output Driver is TTL](http://slidetodoc.com/presentation_image/7cb6d05cb49d4753f189aecf2799bba9/image-19.jpg)

SYS Module • Bootstrap Initialization ADDR[06] ENI Control WR_OC 0 Output Driver is TTL 1 Output Driver is “Open Collector” ADDR[05] ENI Control DINT 2* 0 INT 2* pin configured for pulsed interrupt from ENI 1 PINT 1* or PINT 2* selectable by ENI ADDR[04] ENI Control I_OC 1 -19 0 Output Driver is TTL 1 Output Driver is “Open Collector”

![SYS Module • Bootstrap Initialization ADDR[03] ENI Control DMAE* 0 Enable DACK*, DRQO*, DRQ SYS Module • Bootstrap Initialization ADDR[03] ENI Control DMAE* 0 Enable DACK*, DRQO*, DRQ](http://slidetodoc.com/presentation_image/7cb6d05cb49d4753f189aecf2799bba9/image-20.jpg)

SYS Module • Bootstrap Initialization ADDR[03] ENI Control DMAE* 0 Enable DACK*, DRQO*, DRQ 1* for FIFO mode 1 Disable FIFO mode DMA ADDR[02] Reserved ADDR[01] ENI Control EPACK* 0 ACK pin is configured as active low Data Acknowledgement signal 1 ACK pin is configured as active low WAIT signal ADDR[00] ENI Control PULINT* 0 Interrupts are issued via pulsed interrupt register 1 Interrupts are issued via STSINT or VDAINT bits 1 -20

- Slides: 20