Synthesis using Synopsys Design Compiler ECE 111 Setmaxdelay

- Slides: 10

Synthesis using Synopsys Design Compiler ECE 111

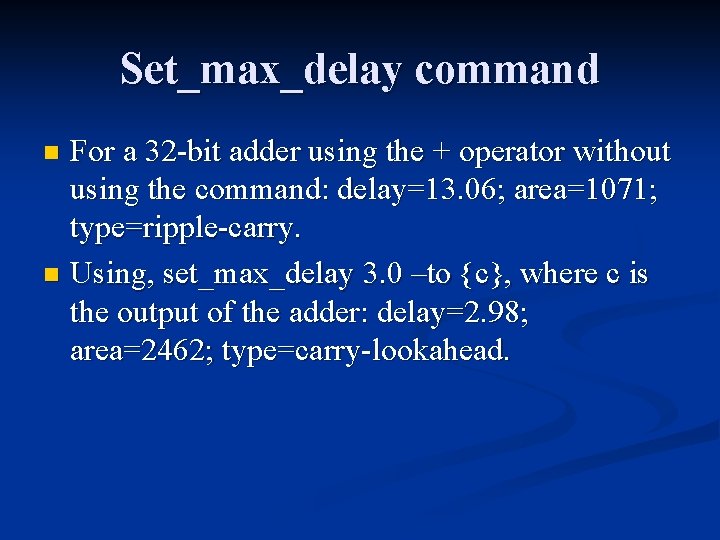

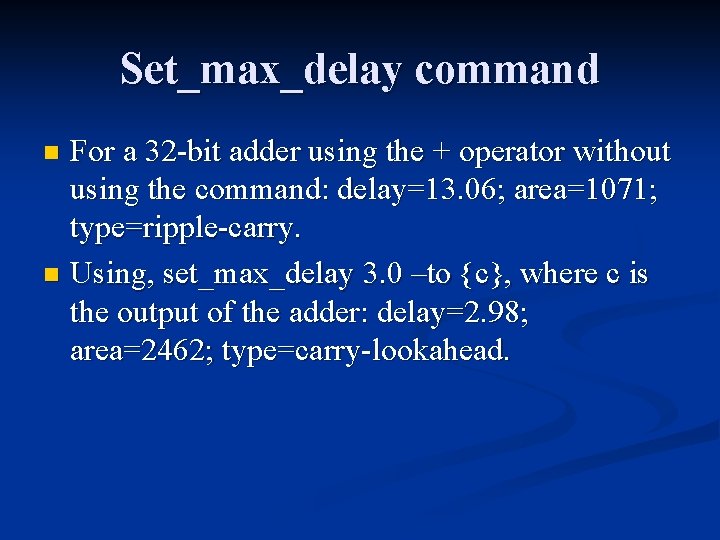

Set_max_delay command For a 32 -bit adder using the + operator without using the command: delay=13. 06; area=1071; type=ripple-carry. n Using, set_max_delay 3. 0 –to {c}, where c is the output of the adder: delay=2. 98; area=2462; type=carry-lookahead. n

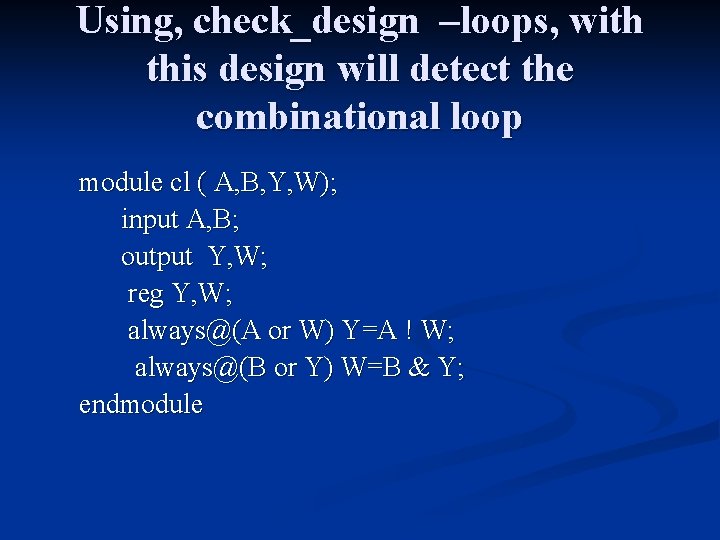

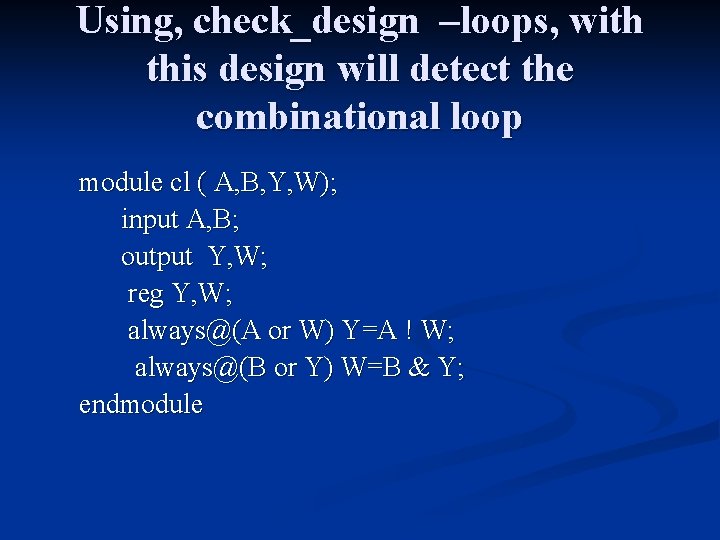

Using, check_design –loops, with this design will detect the combinational loop module cl ( A, B, Y, W); input A, B; output Y, W; reg Y, W; always@(A or W) Y=A ! W; always@(B or Y) W=B & Y; endmodule

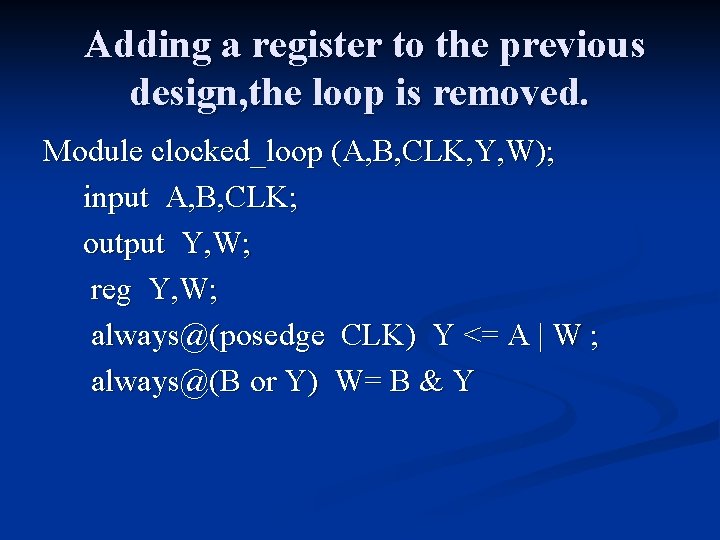

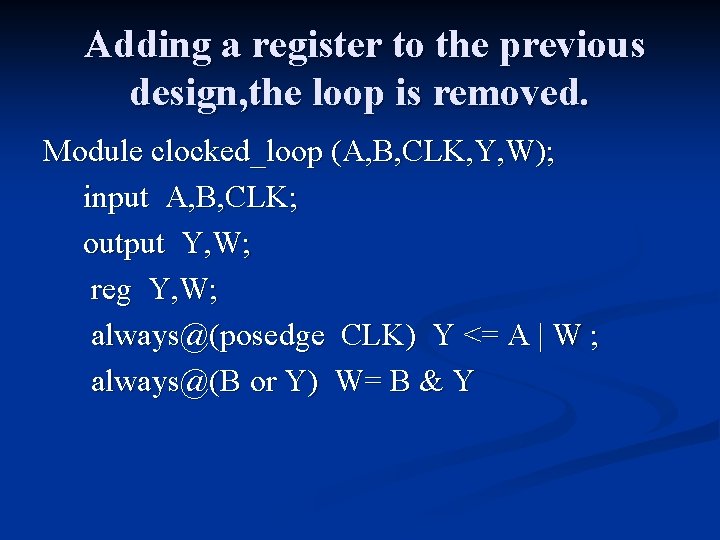

Adding a register to the previous design, the loop is removed. Module clocked_loop (A, B, CLK, Y, W); input A, B, CLK; output Y, W; reg Y, W; always@(posedge CLK) Y <= A | W ; always@(B or Y) W= B & Y

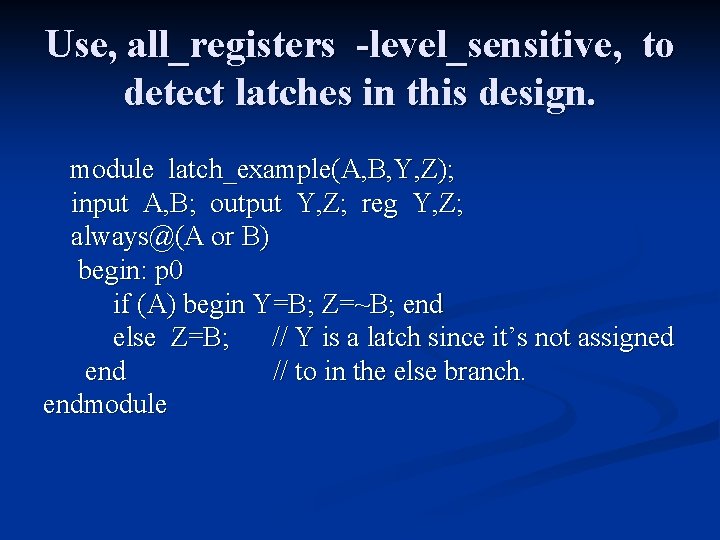

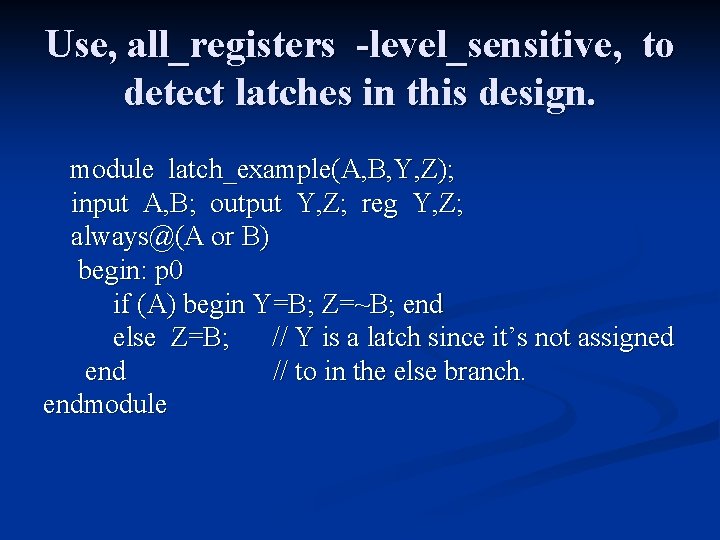

Use, all_registers -level_sensitive, to detect latches in this design. module latch_example(A, B, Y, Z); input A, B; output Y, Z; reg Y, Z; always@(A or B) begin: p 0 if (A) begin Y=B; Z=~B; end else Z=B; // Y is a latch since it’s not assigned end // to in the else branch. endmodule

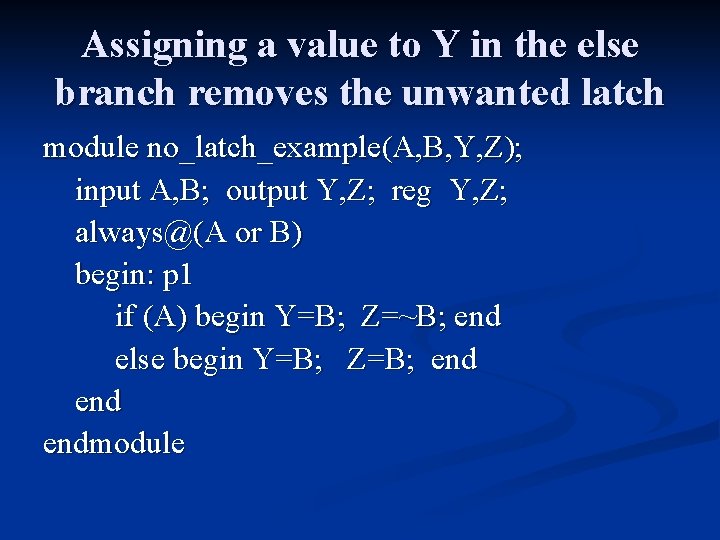

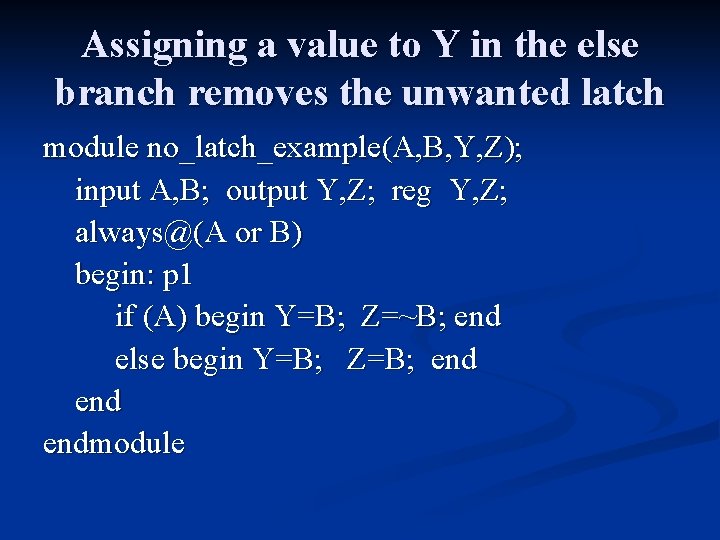

Assigning a value to Y in the else branch removes the unwanted latch module no_latch_example(A, B, Y, Z); input A, B; output Y, Z; reg Y, Z; always@(A or B) begin: p 1 if (A) begin Y=B; Z=~B; end else begin Y=B; Z=B; end endmodule

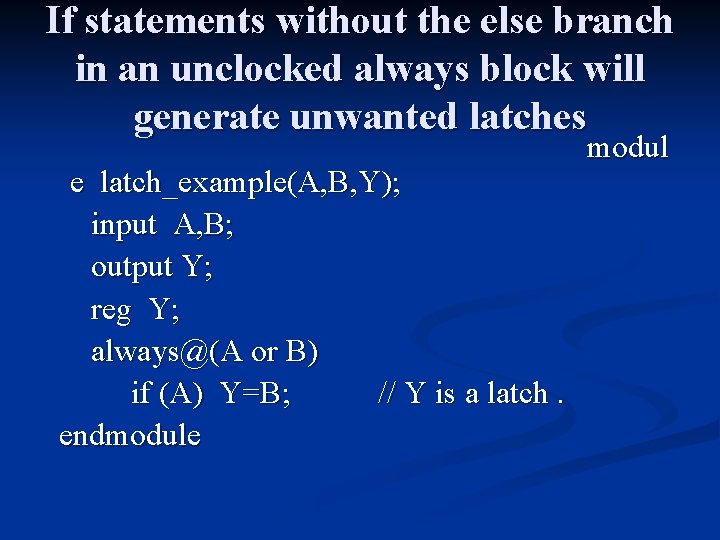

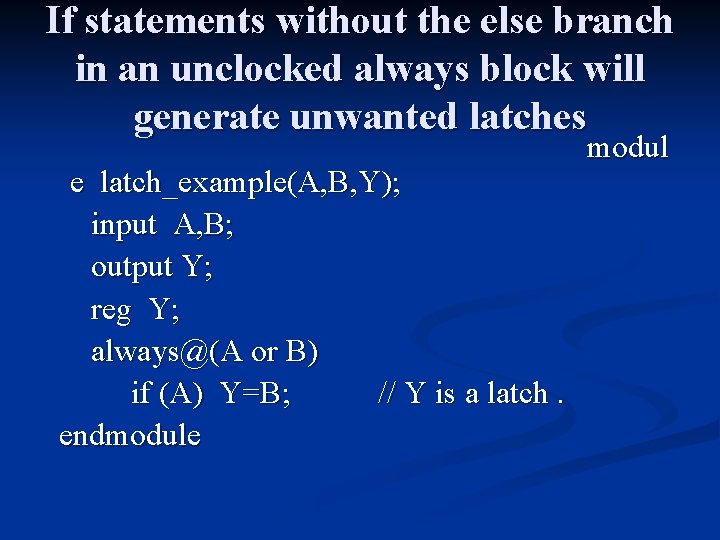

If statements without the else branch in an unclocked always block will generate unwanted latches e latch_example(A, B, Y); input A, B; output Y; reg Y; always@(A or B) if (A) Y=B; // Y is a latch. endmodule modul

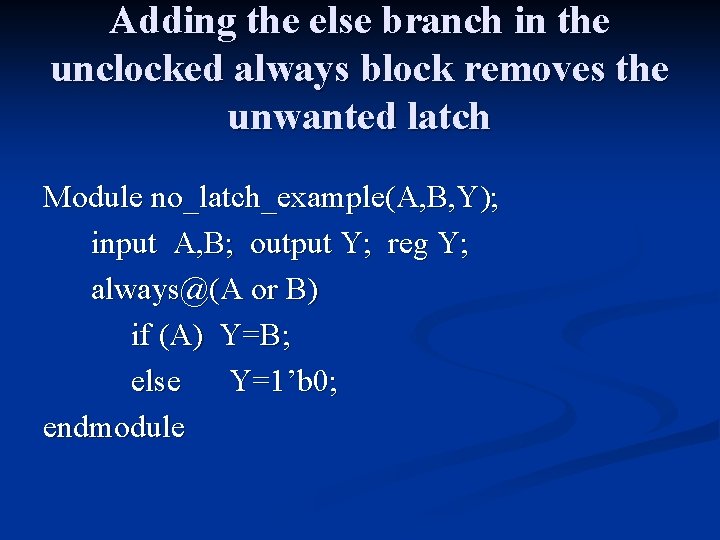

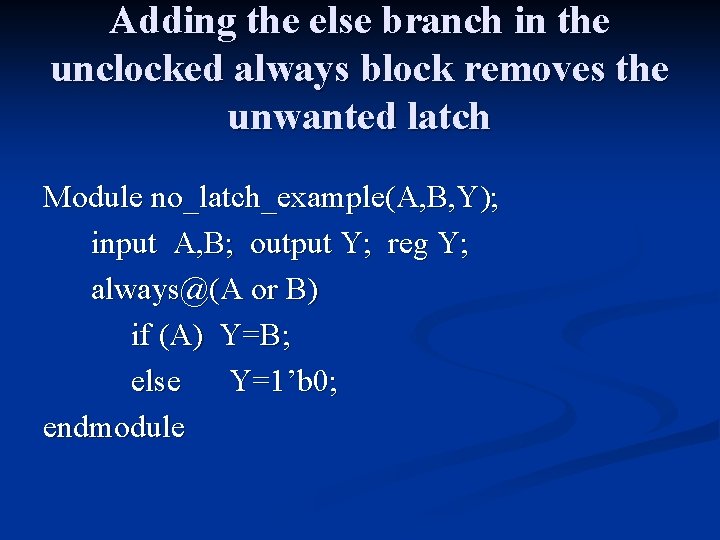

Adding the else branch in the unclocked always block removes the unwanted latch Module no_latch_example(A, B, Y); input A, B; output Y; reg Y; always@(A or B) if (A) Y=B; else Y=1’b 0; endmodule

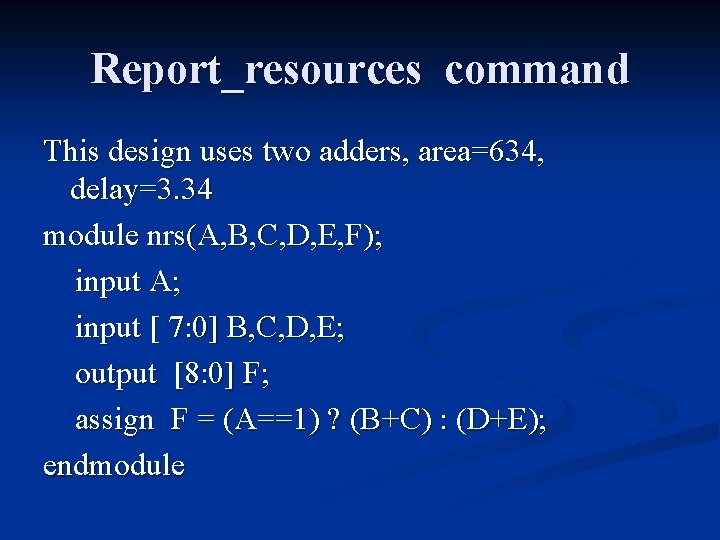

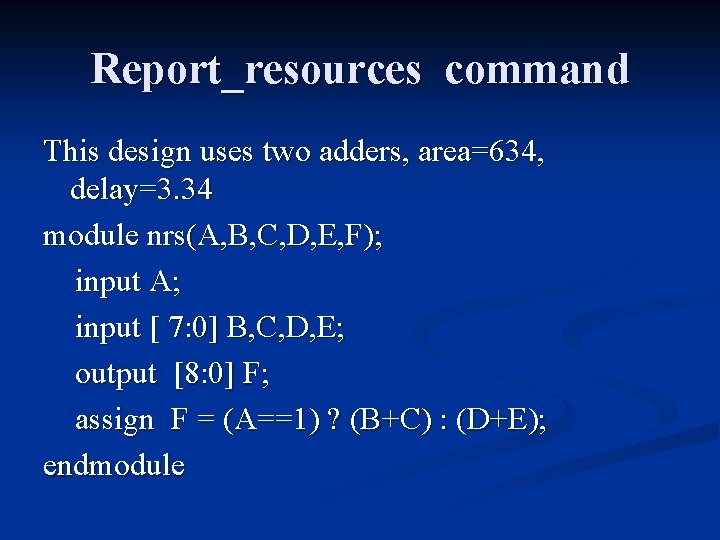

Report_resources command This design uses two adders, area=634, delay=3. 34 module nrs(A, B, C, D, E, F); input A; input [ 7: 0] B, C, D, E; output [8: 0] F; assign F = (A==1) ? (B+C) : (D+E); endmodule

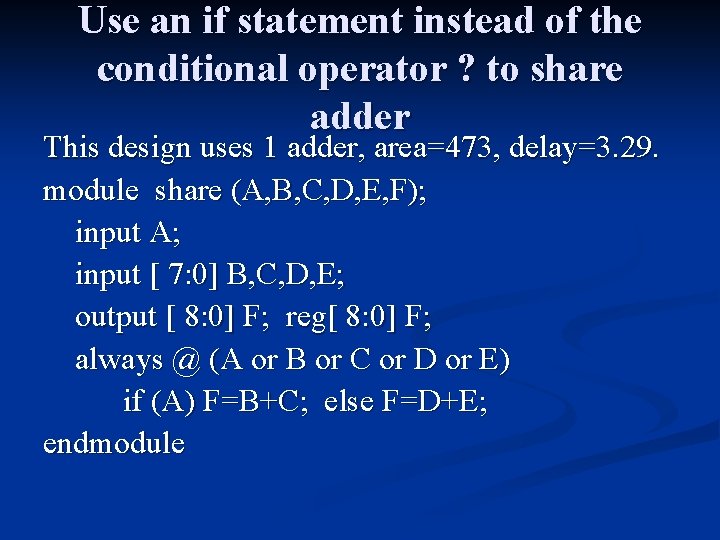

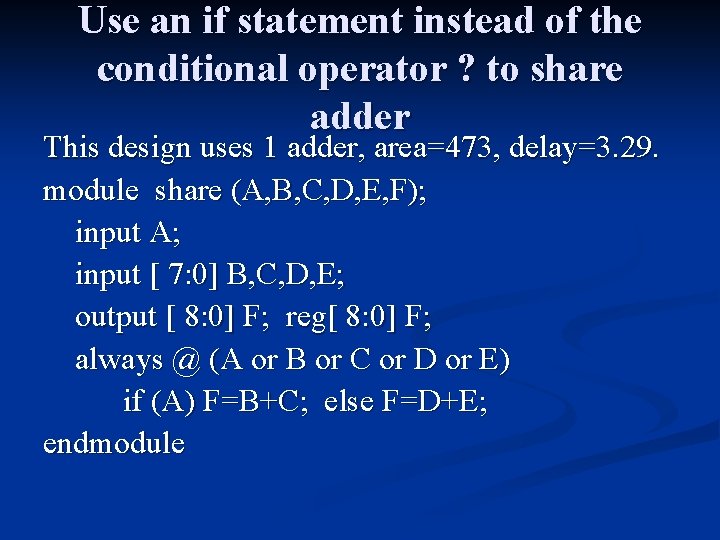

Use an if statement instead of the conditional operator ? to share adder This design uses 1 adder, area=473, delay=3. 29. module share (A, B, C, D, E, F); input A; input [ 7: 0] B, C, D, E; output [ 8: 0] F; reg[ 8: 0] F; always @ (A or B or C or D or E) if (A) F=B+C; else F=D+E; endmodule