Synthesis Techniques FPGA Design Flow Workshop 2003 Xilinx

- Slides: 30

Synthesis Techniques FPGA Design Flow Workshop © 2003 Xilinx, Inc. All Rights Reserved

Objectives After completing this module, you will be able to: • • • Select a proper coding style to create efficient FPGA designs Specify Xilinx resources that need to be instantiated for various FPGA synthesis tools Describe an approach to using your synthesis tool to obtain higher performance Synthesis Techniques - 6 - 3 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

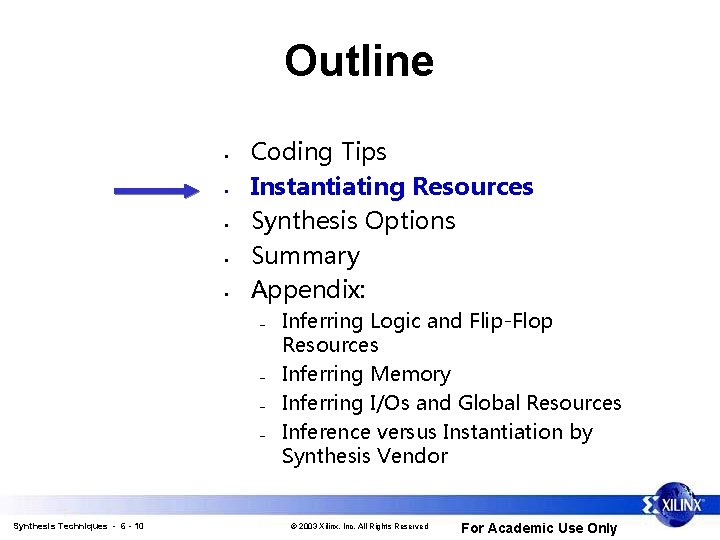

Outline • • • Coding Tips Instantiating Resources Synthesis Options Summary Appendix: – – Synthesis Techniques - 6 - 4 Inferring Logic and Flip-Flop Resources Inferring Memory Inferring I/Os and Global Resources Inference versus Instantiation by Synthesis Vendor © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Instantiation versus Inference • Instantiate a component when you must dictate exactly which resource is needed – – • Xilinx recommends inference whenever possible – • Synthesis tool is unable to infer the resource Synthesis tool fails to infer the resource Inference makes your code more portable Xilinx recommends using the CORE Generator™ system to create ALUs, fast multipliers, FIR filters, etc. for instantiation Synthesis Techniques - 6 - 5 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

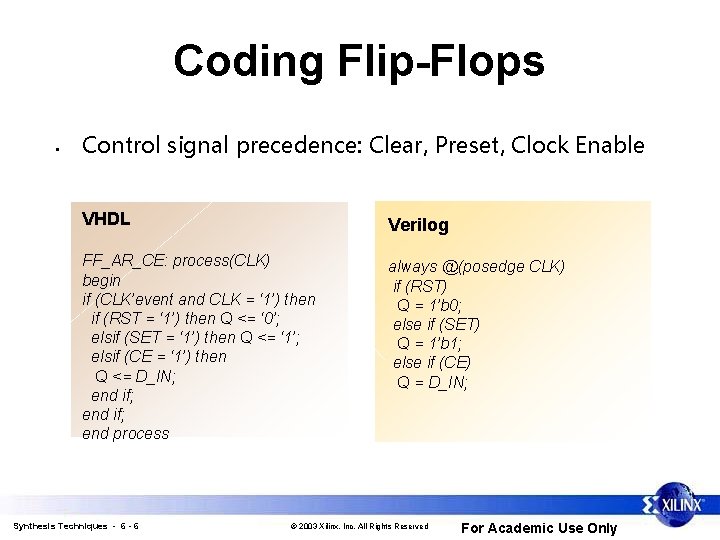

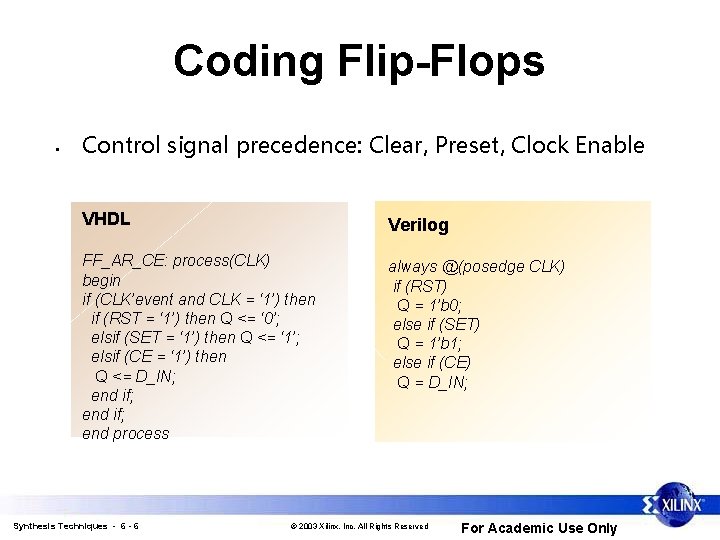

Coding Flip-Flops • Control signal precedence: Clear, Preset, Clock Enable VHDL Verilog FF_AR_CE: process(CLK) begin if (CLK’event and CLK = ‘ 1’) then if (RST = ‘ 1’) then Q <= ‘ 0’; elsif (SET = ‘ 1’) then Q <= ‘ 1’; elsif (CE = ‘ 1’) then Q <= D_IN; end if; end process always @(posedge CLK) if (RST) Q = 1’b 0; else if (SET) Q = 1’b 1; else if (CE) Q = D_IN; Synthesis Techniques - 6 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

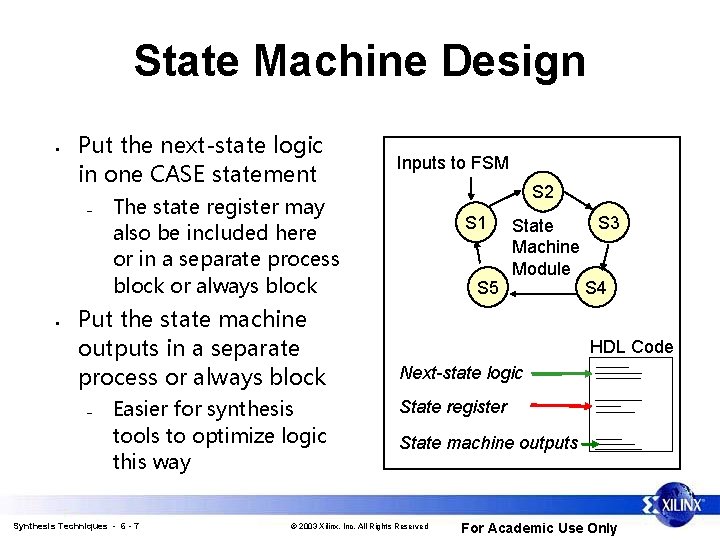

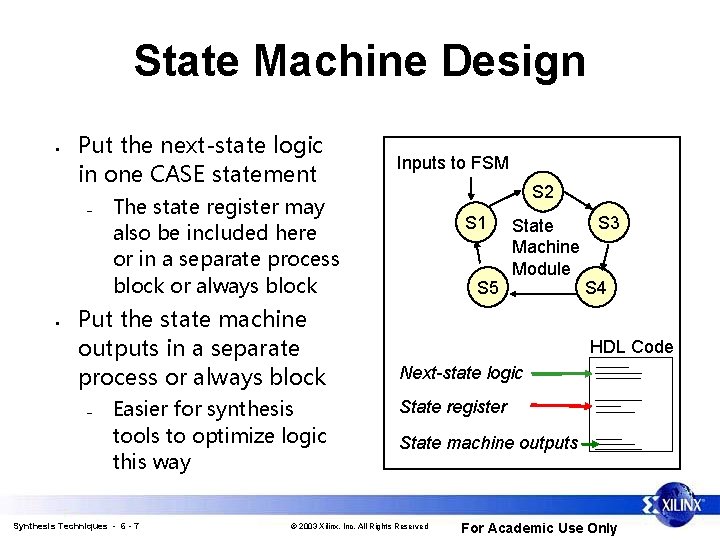

State Machine Design • Put the next-state logic in one CASE statement – • S 2 The state register may also be included here or in a separate process block or always block Put the state machine outputs in a separate process or always block – Inputs to FSM Easier for synthesis tools to optimize logic this way Synthesis Techniques - 6 - 7 S 1 S 3 State Machine Module S 5 S 4 HDL Code Next-state logic State register State machine outputs © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

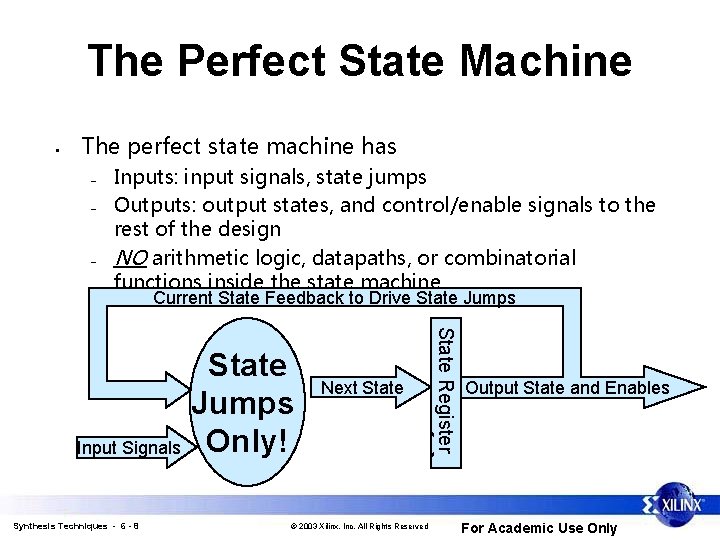

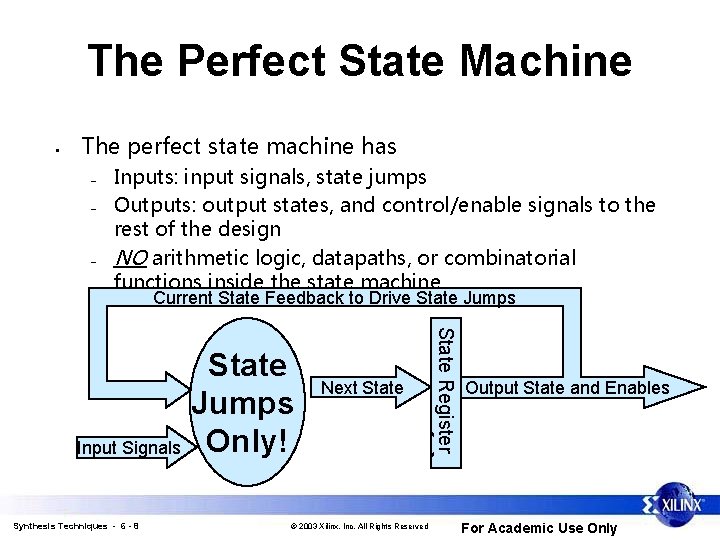

The Perfect State Machine • The perfect state machine has – – – Inputs: input signals, state jumps Outputs: output states, and control/enable signals to the rest of the design NO arithmetic logic, datapaths, or combinatorial functions inside the state machine Current State Feedback to Drive State Jumps Synthesis Techniques - 6 - 8 Next State © 2003 Xilinx, Inc. All Rights Reserved State Register Input Signals State Jumps Only! Output State and Enables For Academic Use Only

State Machine Encoding • Use enumerated types to define state vectors (VHDL) – • Use one-hot encoding for high-performance state machines – – • Most synthesis tools have commands to extract and reencode state machines described in this way Uses more registers, but simplifies next-state logic Experiment to discover how your synthesis tool chooses the default encoding scheme Register state machine outputs for higher performance Synthesis Techniques - 6 - 9 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Outline • • • Coding Tips Instantiating Resources Synthesis Options Summary Appendix: – – Synthesis Techniques - 6 - 10 Inferring Logic and Flip-Flop Resources Inferring Memory Inferring I/Os and Global Resources Inference versus Instantiation by Synthesis Vendor © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Instantiation Tips • Use instantiation only when it is necessary to access device features or increase performance or decrease area – • Exceptions are noted at the end of this section Limit the location of instantiated components to a few source files, to make it easier to locate these components when porting the code Synthesis Techniques - 6 - 11 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

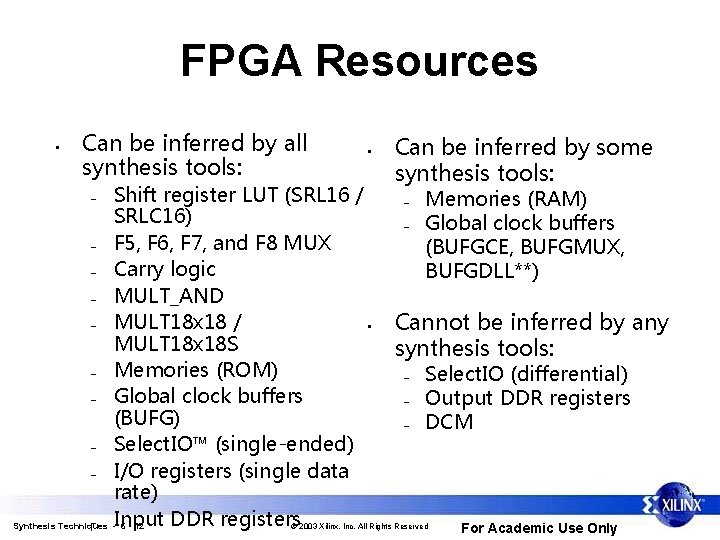

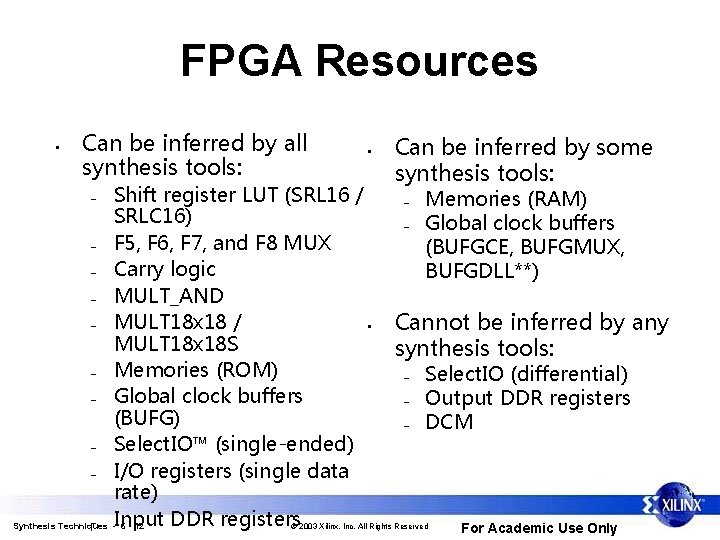

FPGA Resources • Can be inferred by all synthesis tools: • Shift register LUT (SRL 16 / SRLC 16) – F 5, F 6, F 7, and F 8 MUX – Carry logic – MULT_AND – MULT 18 x 18 / • MULT 18 x 18 S – Memories (ROM) – Global clock buffers (BUFG) – Select. IO (single-ended) – I/O registers (single data rate) – DDR registers Synthesis Techniques -Input 6 - 12 – Can be inferred by some synthesis tools: – – Memories (RAM) Global clock buffers (BUFGCE, BUFGMUX, BUFGDLL**) Cannot be inferred by any synthesis tools: – – – Select. IO (differential) Output DDR registers DCM © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

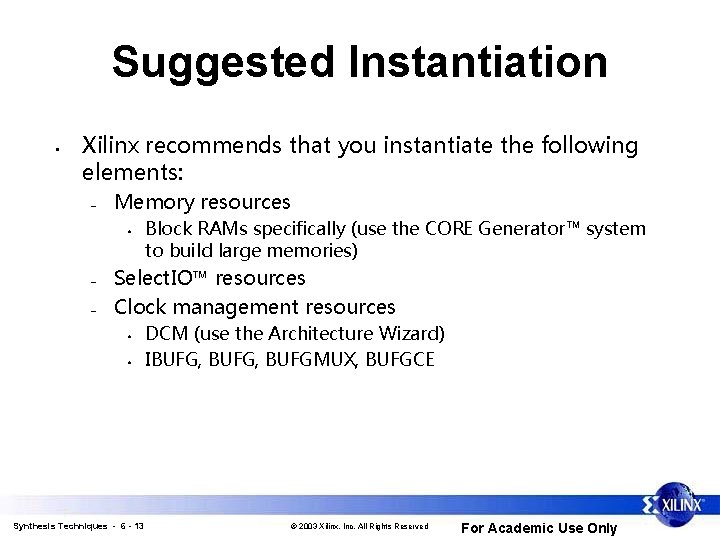

Suggested Instantiation • Xilinx recommends that you instantiate the following elements: – Memory resources • – – Block RAMs specifically (use the CORE Generator™ system to build large memories) Select. IO resources Clock management resources • • Synthesis Techniques - 6 - 13 DCM (use the Architecture Wizard) IBUFG, BUFGMUX, BUFGCE © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

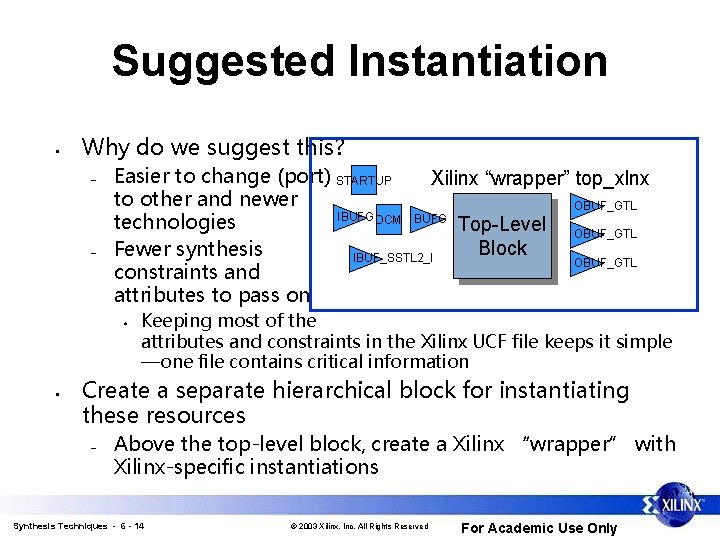

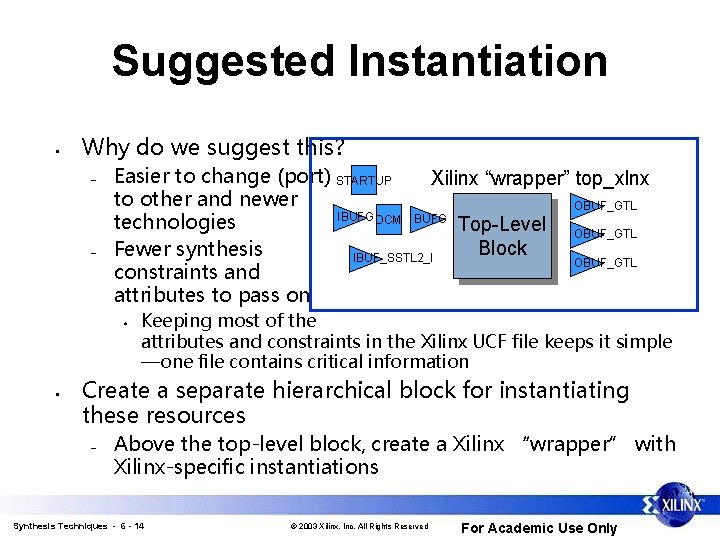

Suggested Instantiation • Why do we suggest this? – – Easier to change (port) STARTUP Xilinx “wrapper” top_xlnx to other and newer OBUF_GTL IBUFG DCM BUFG technologies Top-Level OBUF_GTL Block Fewer synthesis IBUF_SSTL 2_I OBUF_GTL constraints and attributes to pass on • • Keeping most of the attributes and constraints in the Xilinx UCF file keeps it simple —one file contains critical information Create a separate hierarchical block for instantiating these resources – Above the top-level block, create a Xilinx “wrapper” with Xilinx-specific instantiations Synthesis Techniques - 6 - 14 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Outline • • • Coding Tips Instantiating Resources Synthesis Options Summary Appendix: – – Synthesis Techniques - 6 - 15 Inferring Logic and Flip-Flop Resources Inferring Memory Inferring I/Os and Global Resources Inference versus Instantiation by Synthesis Vendor © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Synthesis Options • There are many synthesis options that can help you obtain your performance and area objectives: – – – – – Timing Driven Synthesis Timing Constraint Editor FSM Extraction Retiming Register Duplication Hierarchy Management Schematic Viewer Error Navigation Cross Probing Physical Optimization Synthesis Techniques - 6 - 16 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Timing Driven Synthesis • Timing driven synthesis uses performance objectives to drive the optimization of the design – – Based on your performance objectives, the tools will try several algorithms to attempt to meet performance while keeping the amount of resources in mind Performance objectives are provided to the synthesis tool via timing constraints Synthesis Techniques - 6 - 17 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

FSM Extraction • Finite State Machine (FSM) extraction optimizes your state machine by re-encoding and optimizing your design based on the number of states and inputs – By default, the tools will use FSM extraction Synthesis Techniques - 6 - 18 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

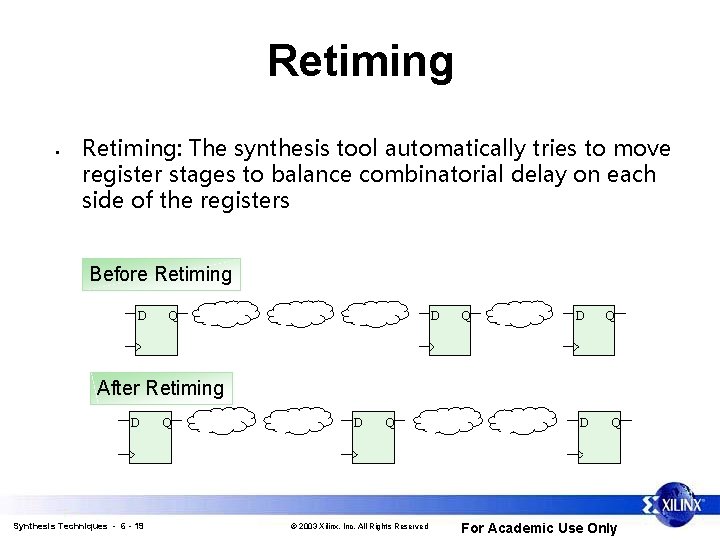

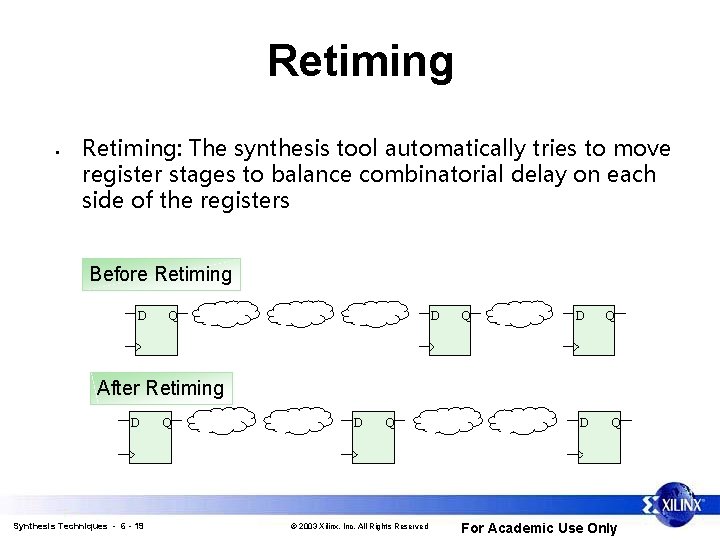

Retiming • Retiming: The synthesis tool automatically tries to move register stages to balance combinatorial delay on each side of the registers Before Retiming D Q D Q After Retiming D Synthesis Techniques - 6 - 19 Q D Q © 2003 Xilinx, Inc. All Rights Reserved D Q For Academic Use Only

Register Duplication • • • Register duplication is used to reduce fanout on registers (to improve delays) Register duplication of the output 3 -state register is used so that the IOB 3 -state register can be moved inside the IOB to reduce clk-to-output delays Xilinx recommends manual register duplication – Most synthesis vendors create signals <signal_name>_rep 0, _rep 1, etc. • • – Implementation tools pack these signals into the same slice Not necessarily wrong, but it may prohibit a register from being moved closer to its destination When manually duplicating registers, do NOT use a number at the end • Example: <signal_name>_0 dup, <signal_name>_1 dup Synthesis Techniques - 6 - 20 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Hierarchy Management • The basic settings are: – – • • Flatten the design: Allows total combinatorial optimization across all boundaries Maintain hierarchy: Preserves hierarchy without allowing optimization of combinatorial logic across boundaries If you have followed the synchronous design guidelines, use the setting -maintain hierarchy If you have not followed the synchronous design guidelines, use the setting - flatten the design Synthesis Techniques - 6 - 21 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Hierarchy Preservation Benefits • • • Easily locate problems in the code based on the hierarchical instance names contained within static timing analysis reports Enables floorplanning and incremental design flow The primary issue is optimization of combinatorial logic across hierarchical boundaries – The easiest way to eliminate this problem is to register the outputs of leaf-level blocks Synthesis Techniques - 6 - 22 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Schematic Viewer • Allows you to view synthesis results graphically – – • Check the number of logic levels between flip-flops Quickly locate net and instance names Works best when hierarchy has been preserved during synthesis Synthesis Techniques - 6 - 23 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Error Navigation and Cross Probing • Error Navigation – • Allows you to click on errors in Xilinx reports and crossnavigate to the problem area by using the synthesis tool You must set some environment variables for this to work – For more information, see application note XAPP 406 Synthesis Techniques - 6 - 24 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Increasing Productivity • • Use synchronous design techniques Preserve hierarchy during synthesis – • Use timing-driven synthesis if your tool supports it – • Check the synthesis report for performance estimates After implementation, look at timing reports and identify critical paths – – • Aids in debugging and cross-referencing to report files Double-check the HDL coding style for these paths Try some of the synthesis options discussed earlier For paths that continually fail to meet timing, add path -specific constraints during synthesis – Add corresponding path-specific constraints for implementation Synthesis Techniques - 6 - 25 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Outline • • • Coding Tips Instantiating Resources Synthesis Options Summary Appendix: – – Synthesis Techniques - 6 - 26 Inferring Logic and Flip-Flop Resources Inferring Memory Inferring I/Os and Global Resources Inference vs. Instantiation by Synthesis Vendor © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Review Questions • • Which encoding scheme is preferred for highperformance state machines? Which Xilinx resources, generally, must be instantiated? List a few of the options that the synthesis tools provide to help you to increase performance What is the synthesis approach presented here for obtaining higher performance? Synthesis Techniques - 6 - 28 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Answers • Which encoding scheme is preferred for highperformance state machines? – • One-hot Which Xilinx resources generally must be instantiated? – – – Double-data-rate output registers Differential I/O BUFGMUX BUFGCE DCM Complex block RAMs Synthesis Techniques - 6 - 29 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Answers • List a few of the options that the synthesis tools provide to help you to increase performance – – – • Timing driven synthesis FSM extraction Retiming Register duplication Physical optimization What is the synthesis approach presented here for obtaining higher performance? – – – Follow synchronous design techniques Preserve hierarchy during synthesis Use timing-driven synthesis Synthesis Techniques - 6 - 30 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Summary • • Your HDL coding style can affect synthesis results Infer functions whenever possible Use one-hot encoding to improve design performance When coding a state machine, separate the next-state logic from the state machine output equations Most resources are inferable, either directly or with an attribute Take advantage of the synthesis options provided to help you meet your timing objectives Use synchronous design techniques and timing-driven synthesis to achieve higher performance (more on this later) Synthesis Techniques - 6 - 31 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only

Where Can I Learn More? • Synthesis & Simulation Design Guide: – • User Guides: – • http: //support. xilinx. com > Documentation Technical Tips: http: //support. xilinx. com > Tech Tips – • http: //support. xilinx. com > Software Manuals Click Xilinx Synthesis Technology, Synopsys FPGA and Design Compiler, or Synplicity Synthesis documentation or online help Synthesis Techniques - 6 - 32 © 2003 Xilinx, Inc. All Rights Reserved For Academic Use Only