SYNTHESIS Issues in synthesizable VHDL descriptions from VHDL

SYNTHESIS Issues in synthesizable VHDL descriptions (from VHDL Answers to FAQ by Ben Cohen) 1 EDA Lab. Dept. of Computer Engineering C. N. U.

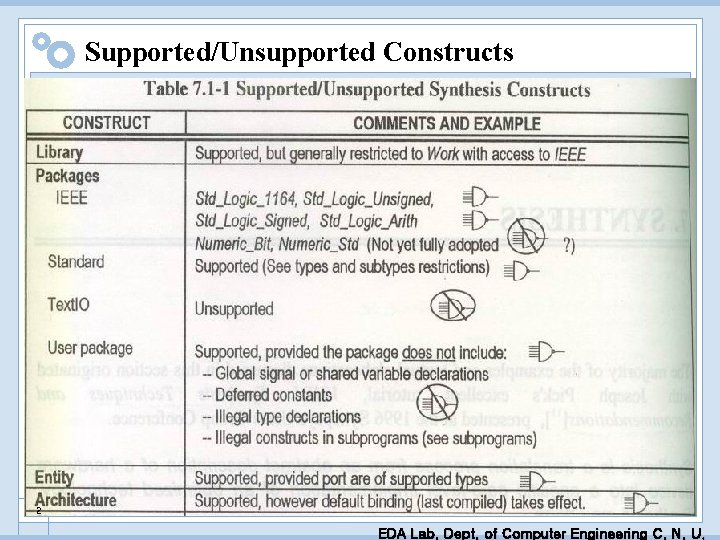

Supported/Unsupported Constructs 2 EDA Lab. Dept. of Computer Engineering C. N. U.

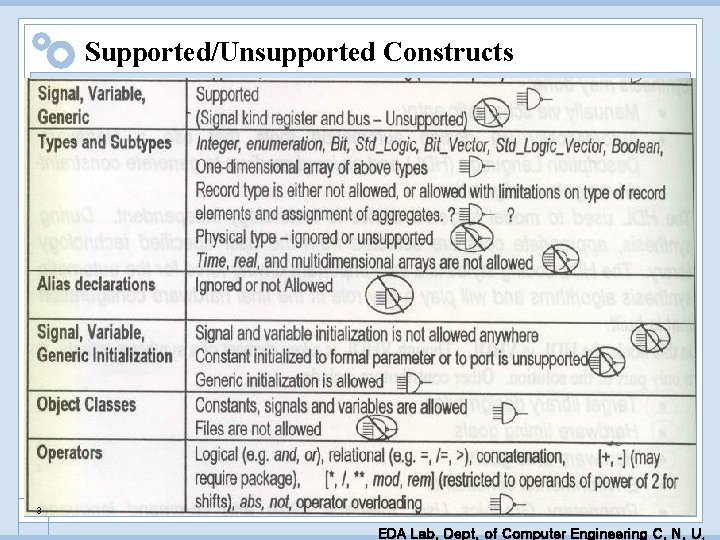

Supported/Unsupported Constructs 3 EDA Lab. Dept. of Computer Engineering C. N. U.

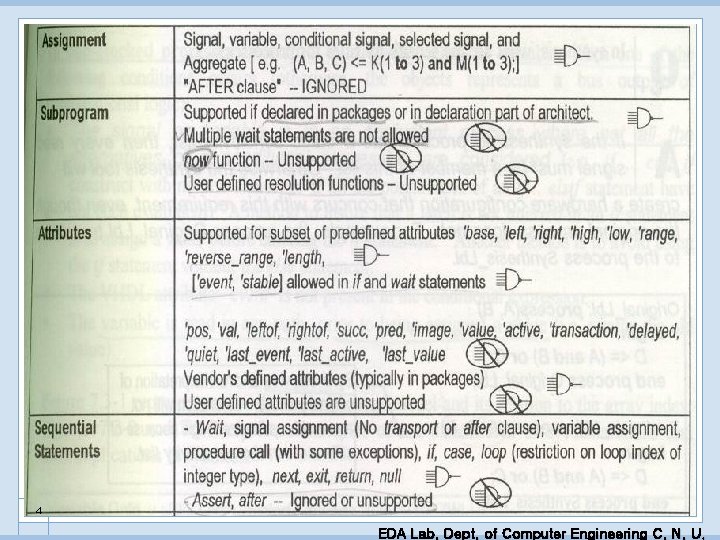

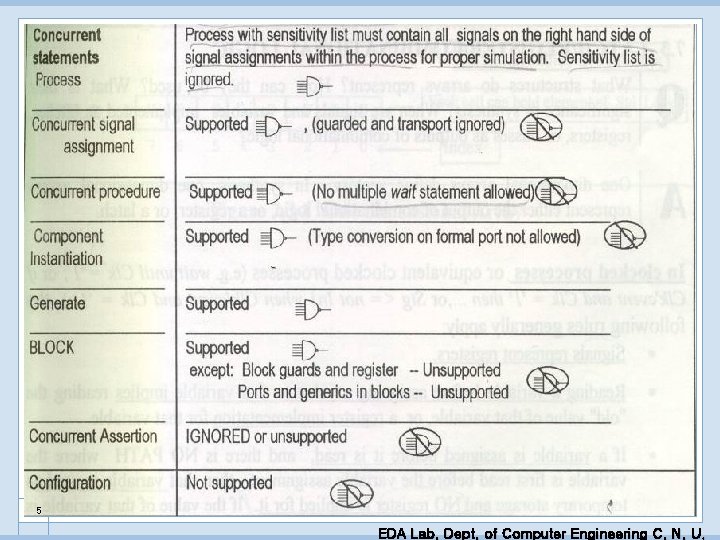

4 EDA Lab. Dept. of Computer Engineering C. N. U.

5 EDA Lab. Dept. of Computer Engineering C. N. U.

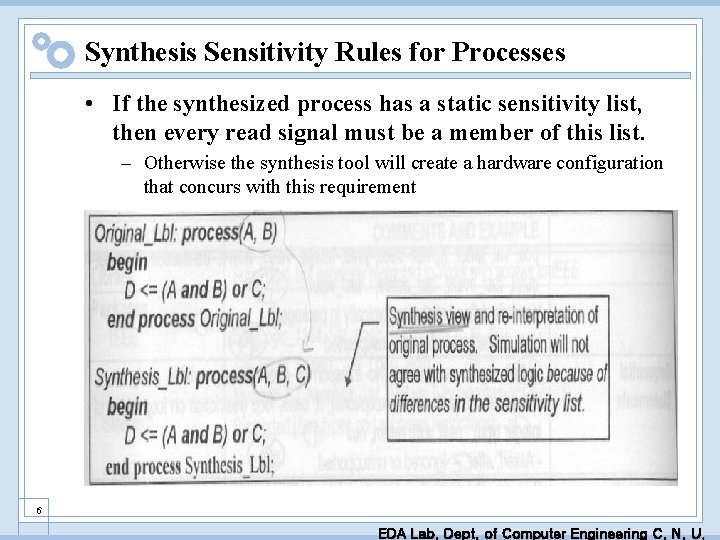

Synthesis Sensitivity Rules for Processes • If the synthesized process has a static sensitivity list, then every read signal must be a member of this list. – Otherwise the synthesis tool will create a hardware configuration that concurs with this requirement 6 EDA Lab. Dept. of Computer Engineering C. N. U.

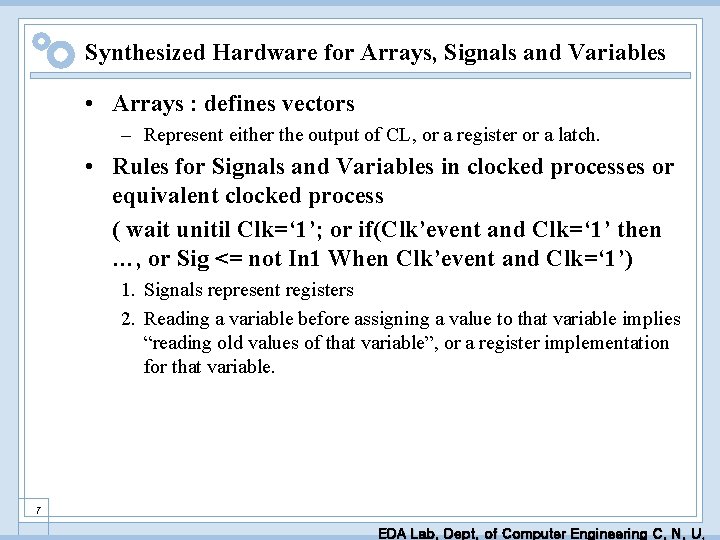

Synthesized Hardware for Arrays, Signals and Variables • Arrays : defines vectors – Represent either the output of CL, or a register or a latch. • Rules for Signals and Variables in clocked processes or equivalent clocked process ( wait unitil Clk=‘ 1’; or if(Clk’event and Clk=‘ 1’ then …, or Sig <= not In 1 When Clk’event and Clk=‘ 1’) 1. Signals represent registers 2. Reading a variable before assigning a value to that variable implies “reading old values of that variable”, or a register implementation for that variable. 7 EDA Lab. Dept. of Computer Engineering C. N. U.

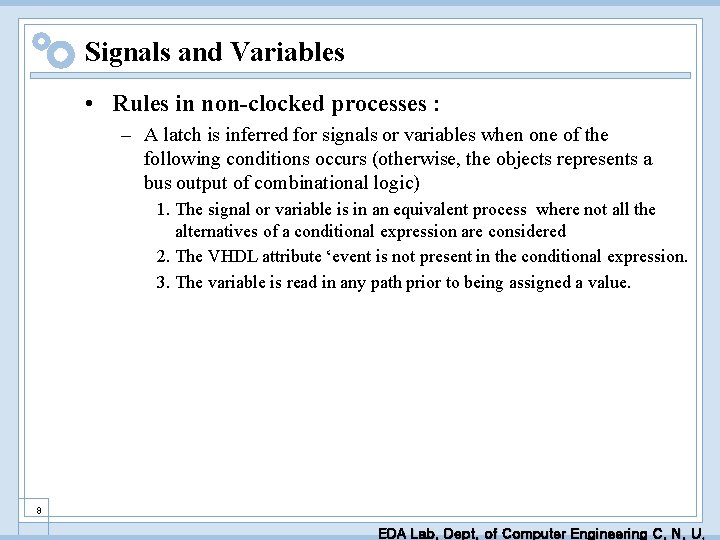

Signals and Variables • Rules in non-clocked processes : – A latch is inferred for signals or variables when one of the following conditions occurs (otherwise, the objects represents a bus output of combinational logic) 1. The signal or variable is in an equivalent process where not all the alternatives of a conditional expression are considered 2. The VHDL attribute ‘event is not present in the conditional expression. 3. The variable is read in any path prior to being assigned a value. 8 EDA Lab. Dept. of Computer Engineering C. N. U.

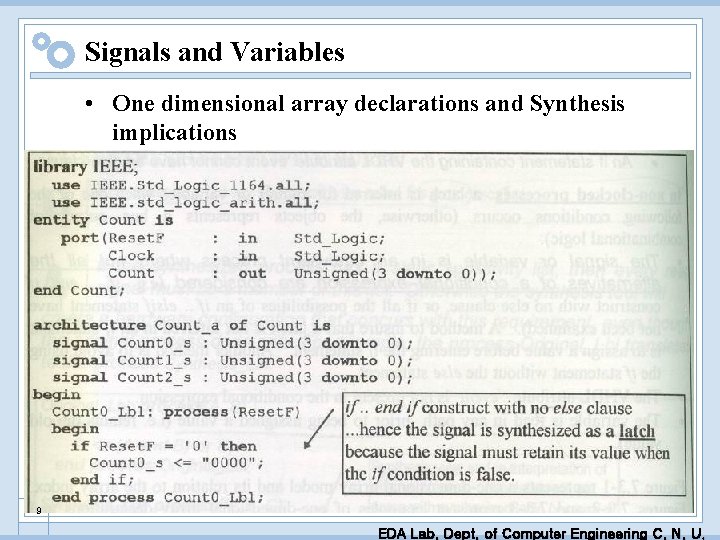

Signals and Variables • One dimensional array declarations and Synthesis implications 9 EDA Lab. Dept. of Computer Engineering C. N. U.

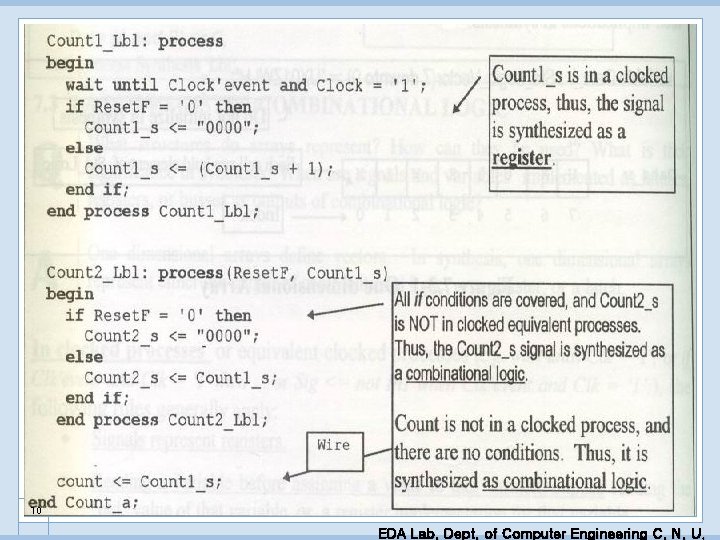

10 EDA Lab. Dept. of Computer Engineering C. N. U.

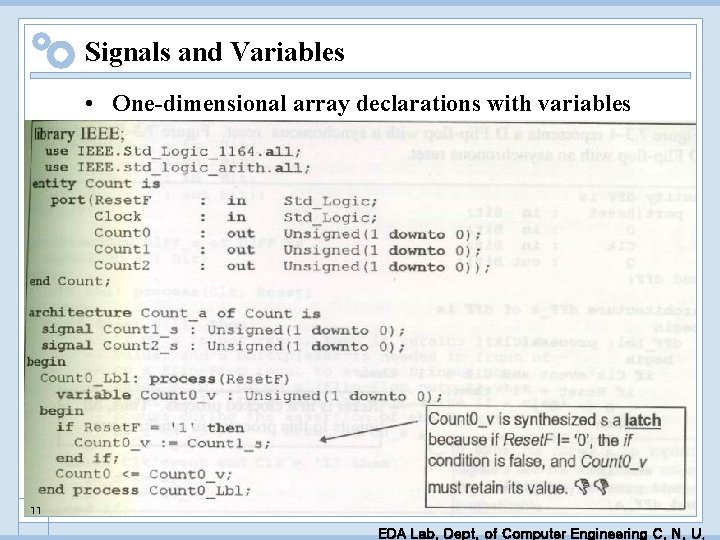

Signals and Variables • One-dimensional array declarations with variables 11 EDA Lab. Dept. of Computer Engineering C. N. U.

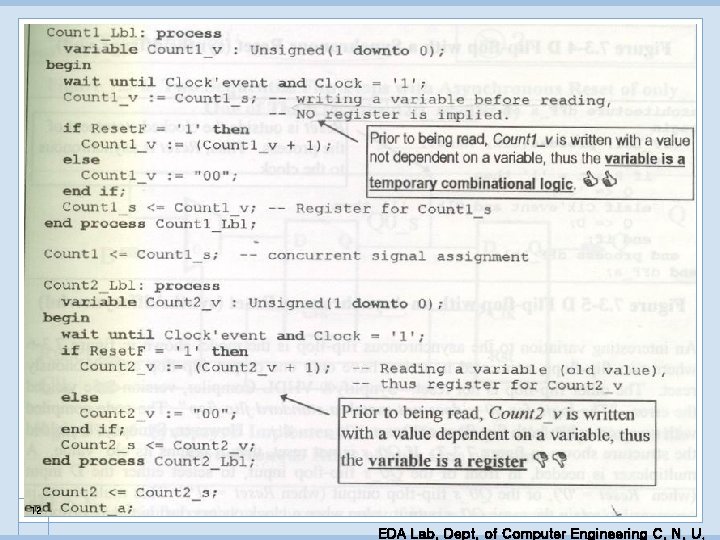

12 EDA Lab. Dept. of Computer Engineering C. N. U.

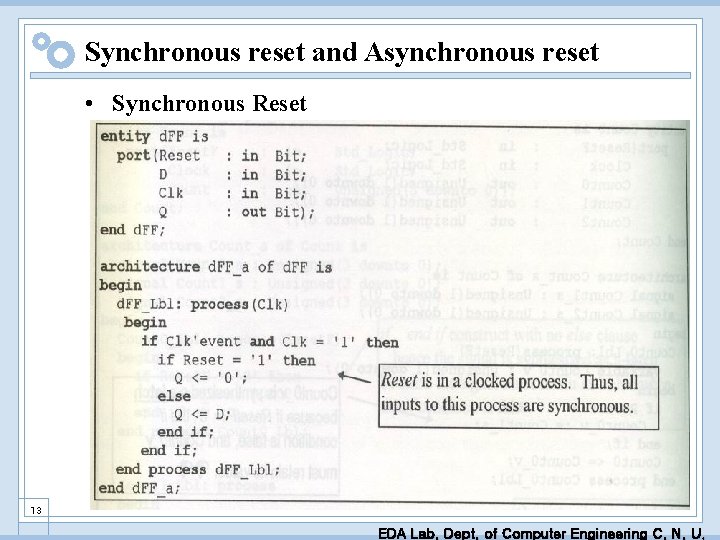

Synchronous reset and Asynchronous reset • Synchronous Reset 13 EDA Lab. Dept. of Computer Engineering C. N. U.

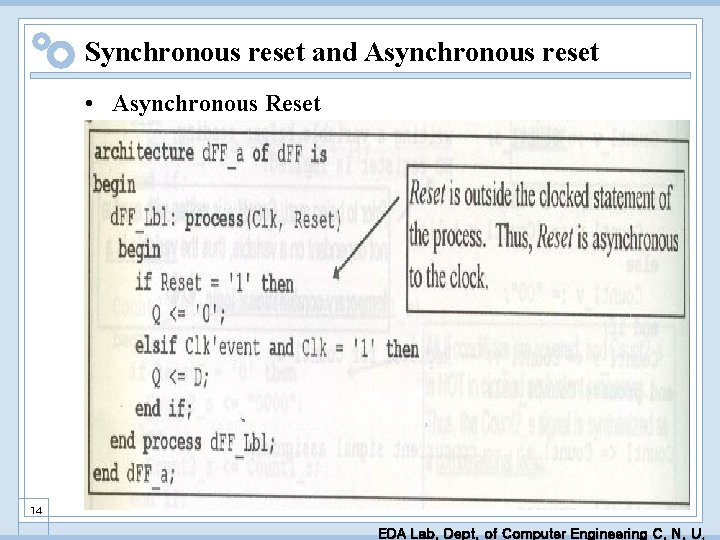

Synchronous reset and Asynchronous reset • Asynchronous Reset 14 EDA Lab. Dept. of Computer Engineering C. N. U.

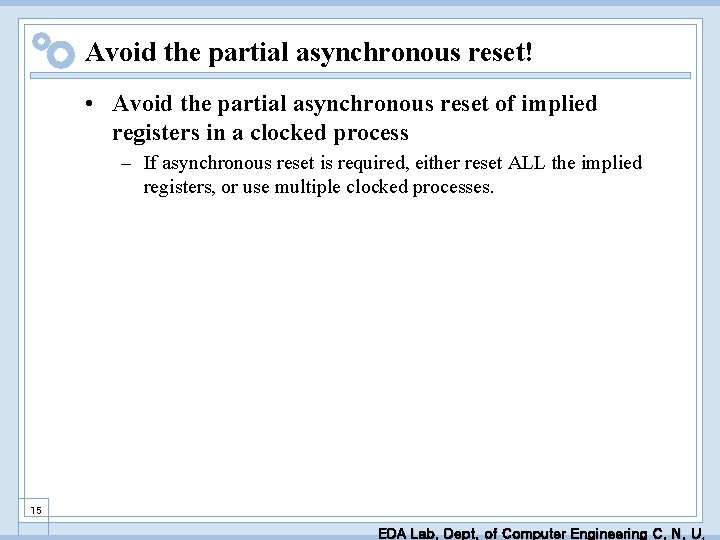

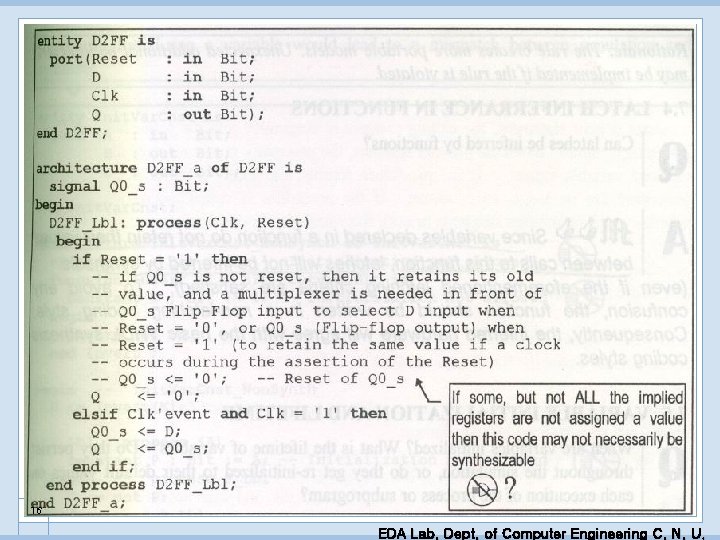

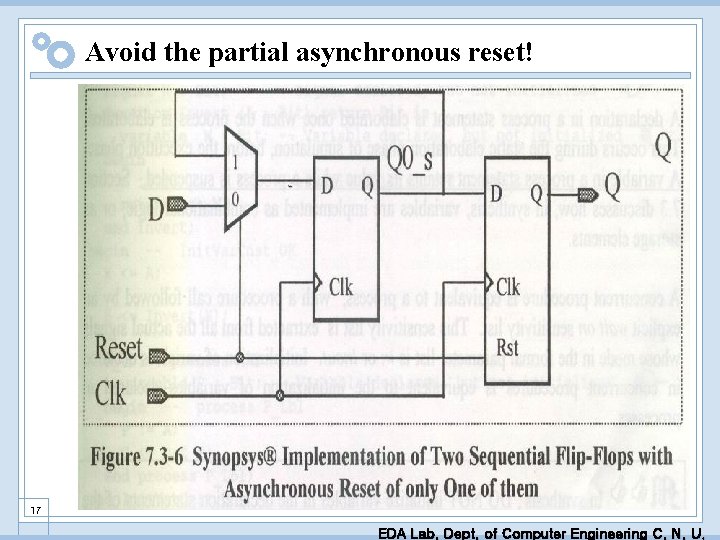

Avoid the partial asynchronous reset! • Avoid the partial asynchronous reset of implied registers in a clocked process – If asynchronous reset is required, either reset ALL the implied registers, or use multiple clocked processes. 15 EDA Lab. Dept. of Computer Engineering C. N. U.

16 EDA Lab. Dept. of Computer Engineering C. N. U.

Avoid the partial asynchronous reset! 17 EDA Lab. Dept. of Computer Engineering C. N. U.

Latch inference in functions? • Since variables declared in a function do not retain their values between calls to this function, latches will not be inferred by synthesis. – Even if the latching criteria are satisfied. • To avoid any confusion, the function should be writeen in a non-latching coding style. To agreewith the basic VHDL synthesis coding style. 18 EDA Lab. Dept. of Computer Engineering C. N. U.

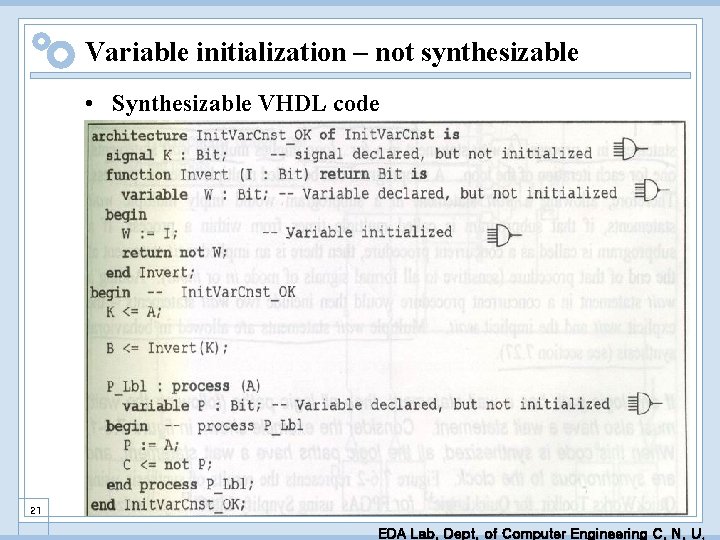

Variable initialization and Lifetime • Variables are initialized when, and only when, its declaration is elaborated. • Concurrent procedure is equivalent to a process. Its sensitivity list is extracted from all the actual signals whose mode is in or inout. • In synthesis, DO NOT initialize variables in the declaration statements of the variables. – Instead, declare the variable UNINITIALIZED, and in the body of the process or subprogram, write an initialization statement(e. g. My_variable : = 0; ) • In synthesis, DO NOT declare constants that are initialized to values of formal parameters or ports. 19 EDA Lab. Dept. of Computer Engineering C. N. U.

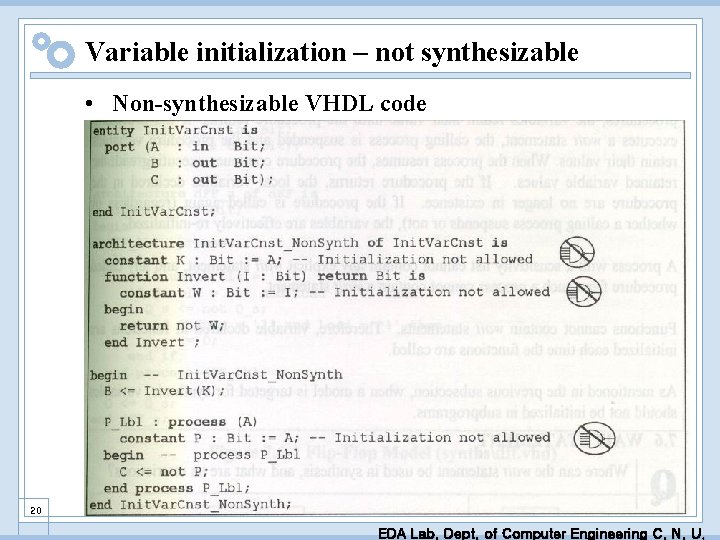

Variable initialization – not synthesizable • Non-synthesizable VHDL code 20 EDA Lab. Dept. of Computer Engineering C. N. U.

Variable initialization – not synthesizable • Synthesizable VHDL code 21 EDA Lab. Dept. of Computer Engineering C. N. U.

Wait statement • A process with a sensitivity list cannot contain any explit ‘wait’ statement, any called procedure from such a process cannot contain a ‘wait’ statement. • ‘wait’ statement can be used anywhere in a process except in a ‘for … loop’ statement or in a subprogram. – In most synthesizers, there can only be a sinlge ‘wait’ statement in a process. Allowing a ‘wait’ statement in a subprogram would imply multiple ‘wait’ statements, if that subprogram is called multiple times from within a process. • If a subprogram is called as a concurrent procedure, then there is an implied wait statement at the end of that procedure. Adding a ‘wait’ would then include two ‘wait’ statements. • Multiple ‘wait’ statements are allowed in behavioral synthesis. 22 EDA Lab. Dept. of Computer Engineering C. N. U.

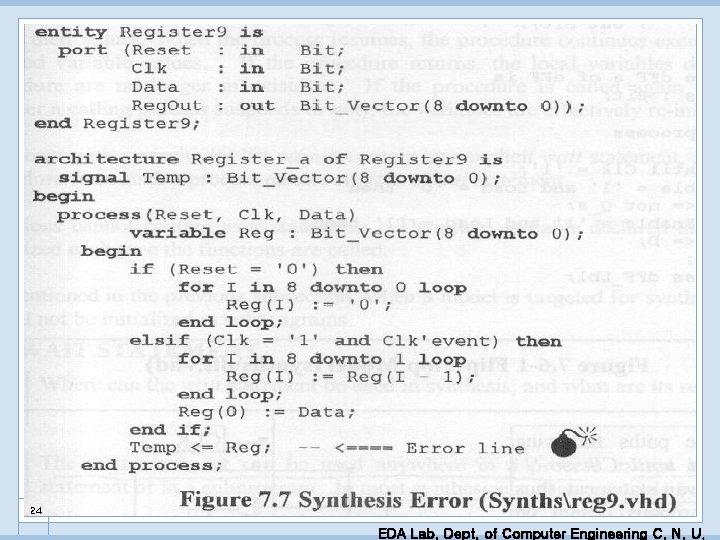

Defining Shift Registers in Synthesis • Given the following code, synopsys tool yields an elaborate Error “Tried to use a synchronized value. ” Where is the error ? 23 EDA Lab. Dept. of Computer Engineering C. N. U.

24 EDA Lab. Dept. of Computer Engineering C. N. U.

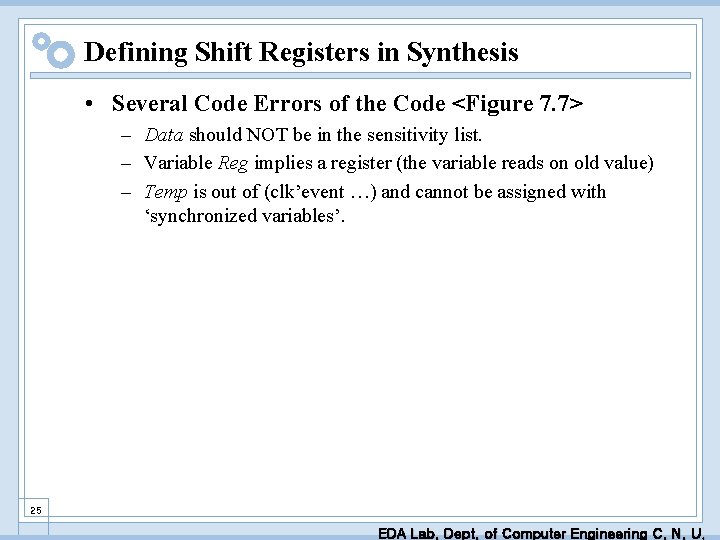

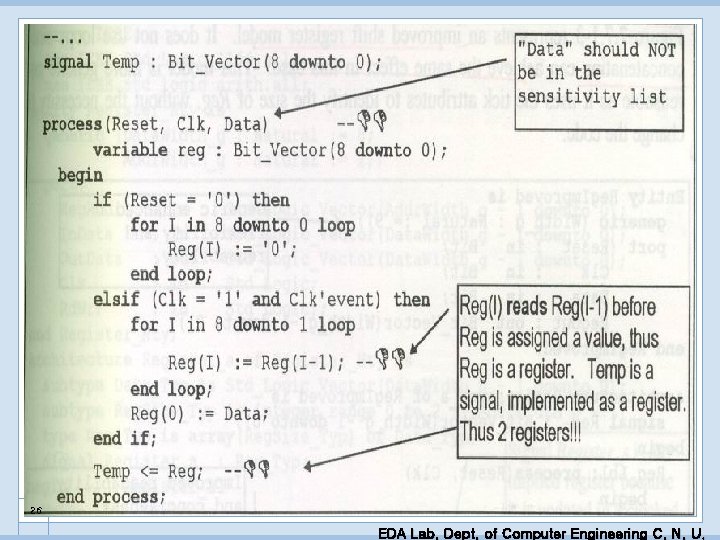

Defining Shift Registers in Synthesis • Several Code Errors of the Code <Figure 7. 7> – Data should NOT be in the sensitivity list. – Variable Reg implies a register (the variable reads on old value) – Temp is out of (clk’event …) and cannot be assigned with ‘synchronized variables’. 25 EDA Lab. Dept. of Computer Engineering C. N. U.

26 EDA Lab. Dept. of Computer Engineering C. N. U.

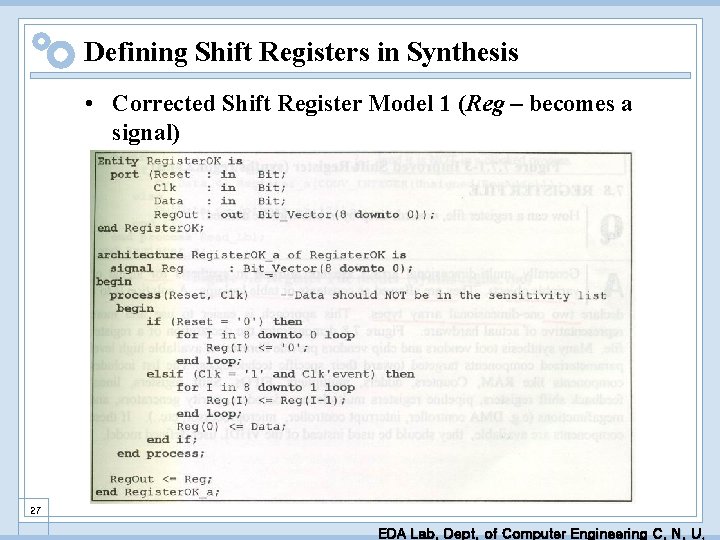

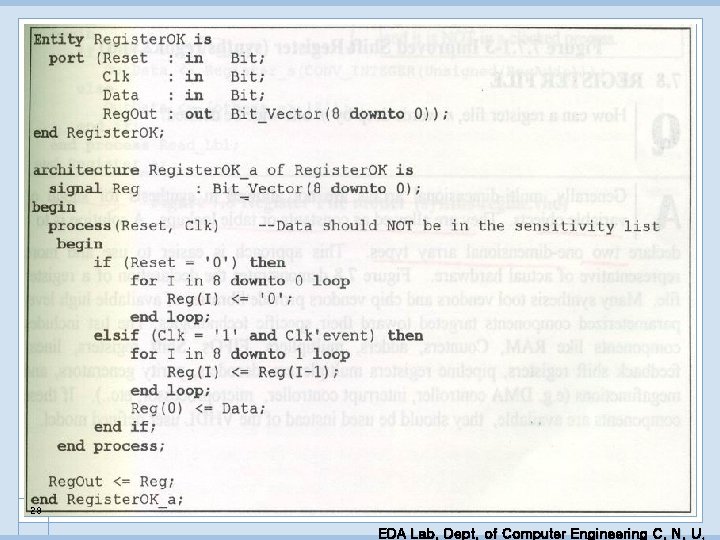

Defining Shift Registers in Synthesis • Corrected Shift Register Model 1 (Reg – becomes a signal) 27 EDA Lab. Dept. of Computer Engineering C. N. U.

28 EDA Lab. Dept. of Computer Engineering C. N. U.

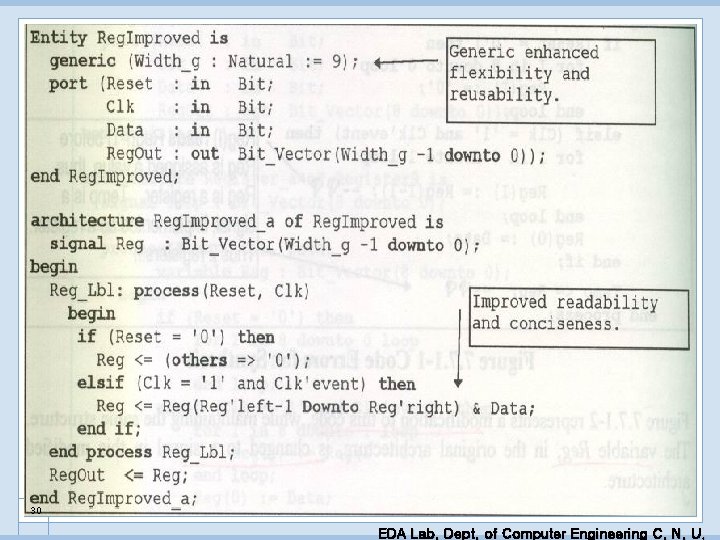

Defining Shift Registers in Synthesis • Improved Shift Register Model (concatenation operator is used) 29 EDA Lab. Dept. of Computer Engineering C. N. U.

30 EDA Lab. Dept. of Computer Engineering C. N. U.

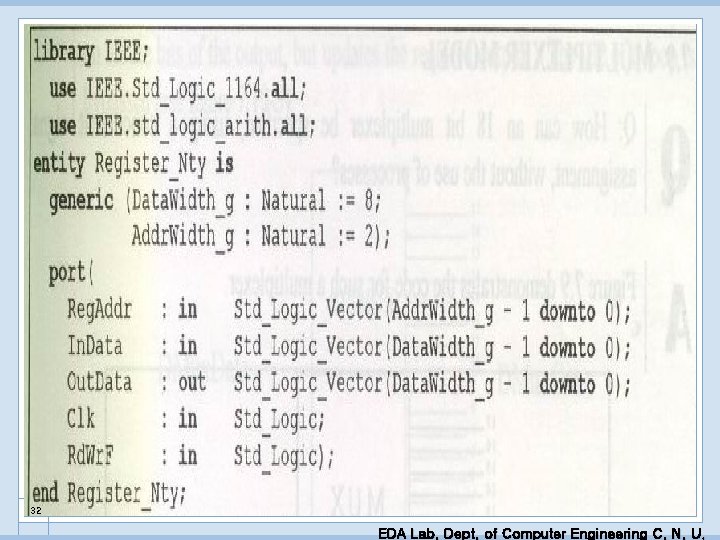

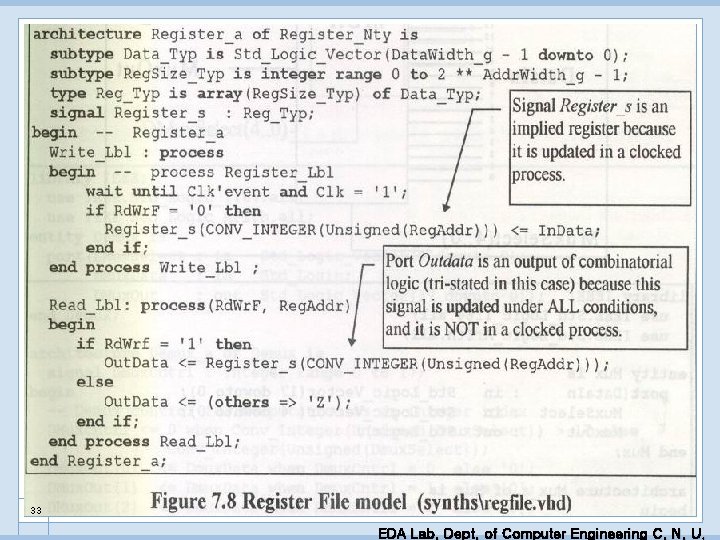

Register File • n words deep by m bit wide register file – Multi-dim arrays: • not allowed in synthesis for signals or variable objects • allowed as constants or table lookups. – User-defined Register File • Use two one-dim. Array types • Figure 7. 8 – Use high-level parameterized components like RAM, Counters, adders, multipliers, FIFOs, LESRs, pipeline registers multipliers, if they are available 31 EDA Lab. Dept. of Computer Engineering C. N. U.

32 EDA Lab. Dept. of Computer Engineering C. N. U.

33 EDA Lab. Dept. of Computer Engineering C. N. U.

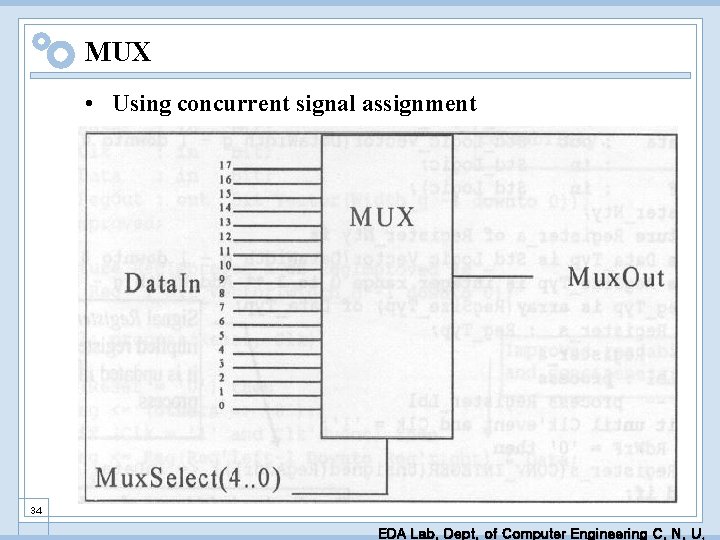

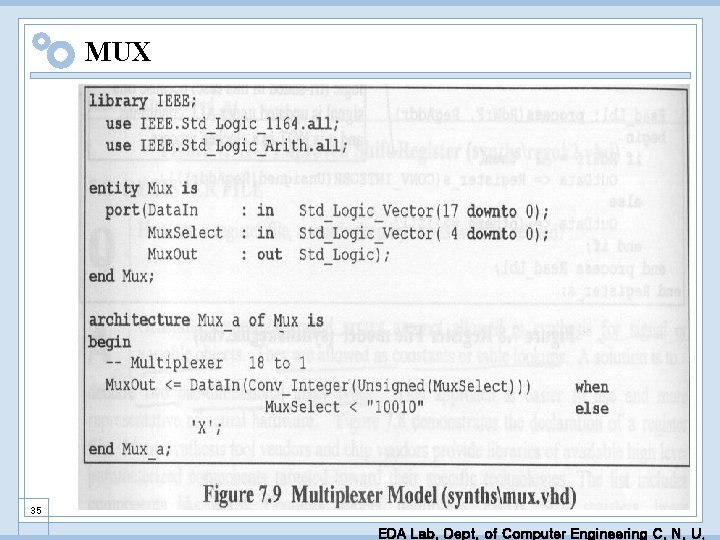

MUX • Using concurrent signal assignment 34 EDA Lab. Dept. of Computer Engineering C. N. U.

MUX 35 EDA Lab. Dept. of Computer Engineering C. N. U.

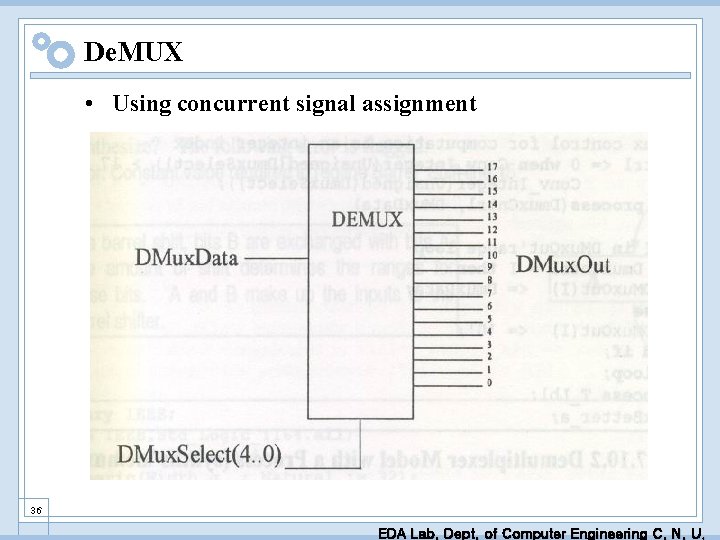

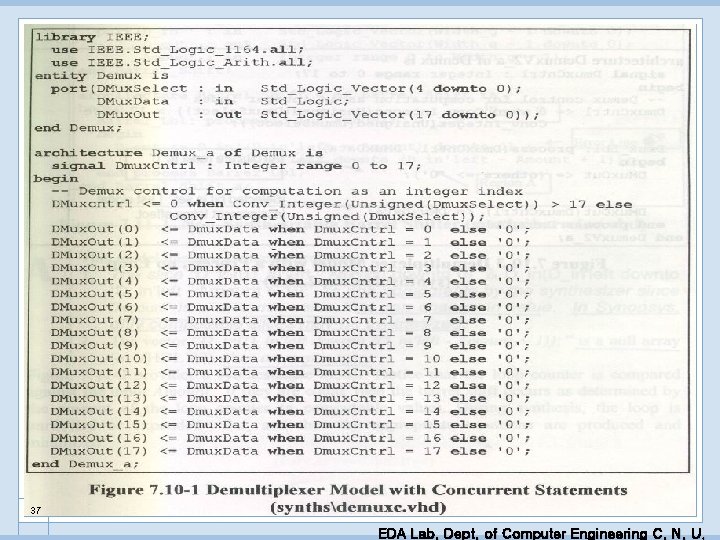

De. MUX • Using concurrent signal assignment 36 EDA Lab. Dept. of Computer Engineering C. N. U.

De. MUX 37 EDA Lab. Dept. of Computer Engineering C. N. U.

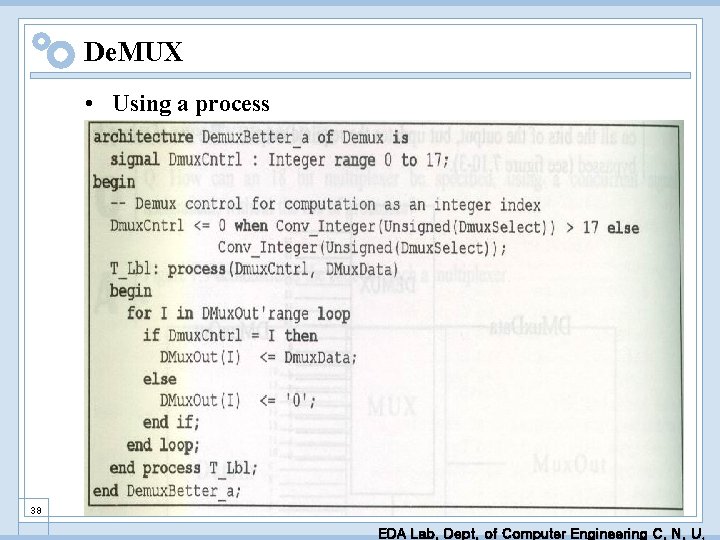

De. MUX • Using a process 38 EDA Lab. Dept. of Computer Engineering C. N. U.

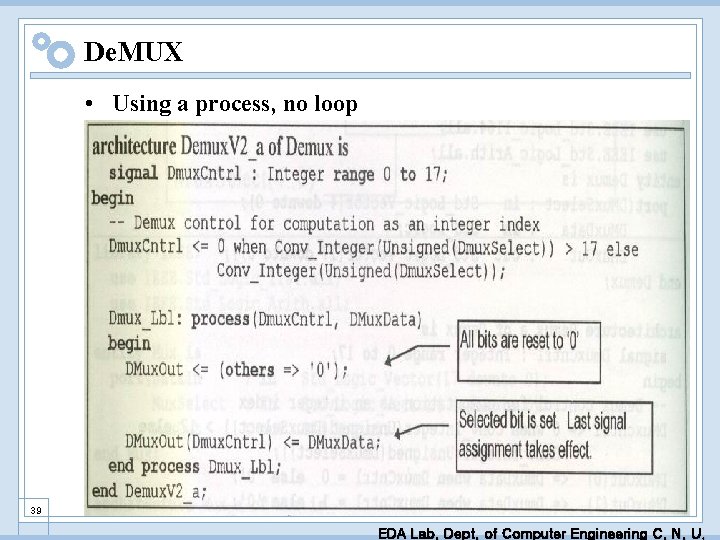

De. MUX • Using a process, no loop 39 EDA Lab. Dept. of Computer Engineering C. N. U.

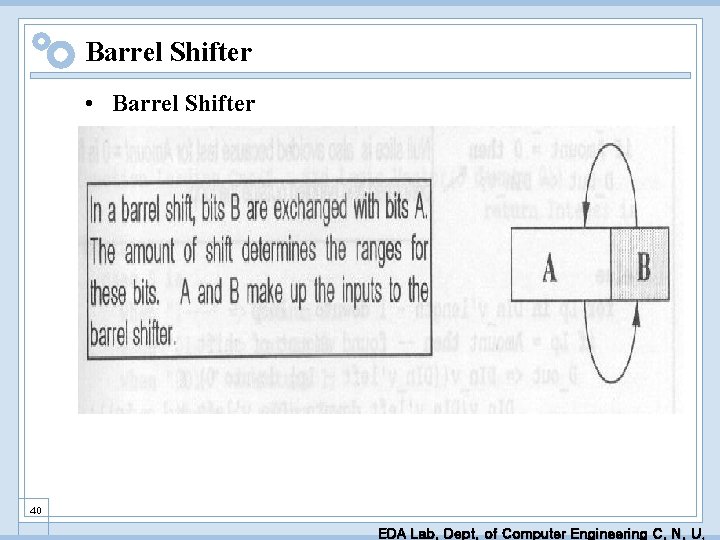

Barrel Shifter • Barrel Shifter 40 EDA Lab. Dept. of Computer Engineering C. N. U.

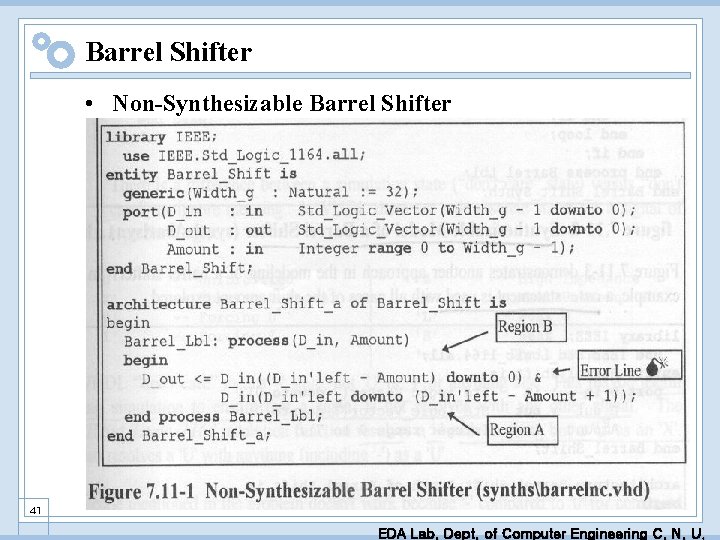

Barrel Shifter • Non-Synthesizable Barrel Shifter 41 EDA Lab. Dept. of Computer Engineering C. N. U.

Barrel Shifter • Synthesis problems 1. The Slice “D_in((D_in’left – Amount) downto 0) & …” is noncompatable (Amount is a dynamic value) 2. The vector “D_in(D_in’left downto (D_in’left – Amount + 1))” is a null array when amount is zero. 42 EDA Lab. Dept. of Computer Engineering C. N. U.

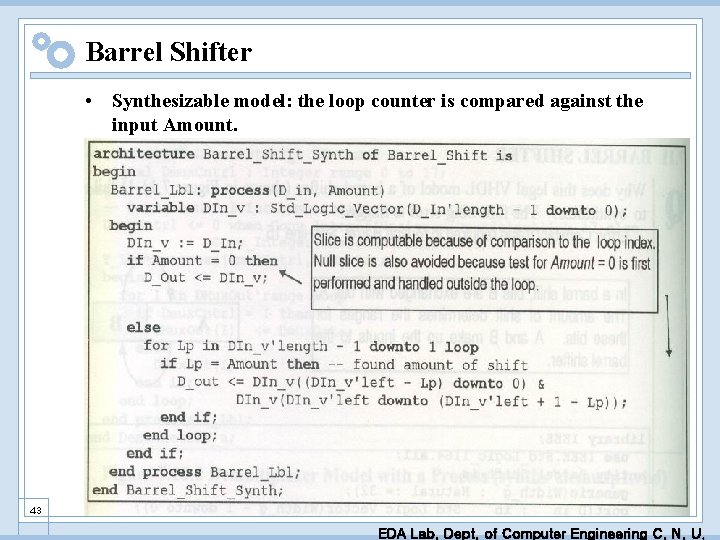

Barrel Shifter • Synthesizable model: the loop counter is compared against the input Amount. 43 EDA Lab. Dept. of Computer Engineering C. N. U.

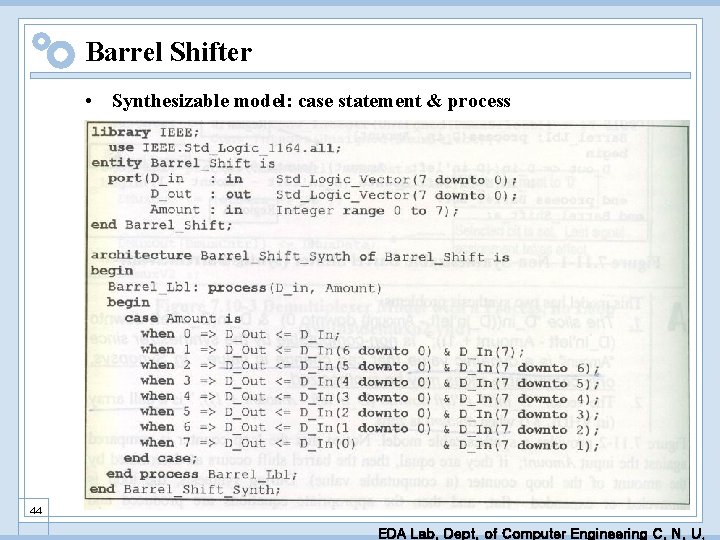

Barrel Shifter • Synthesizable model: case statement & process 44 EDA Lab. Dept. of Computer Engineering C. N. U.

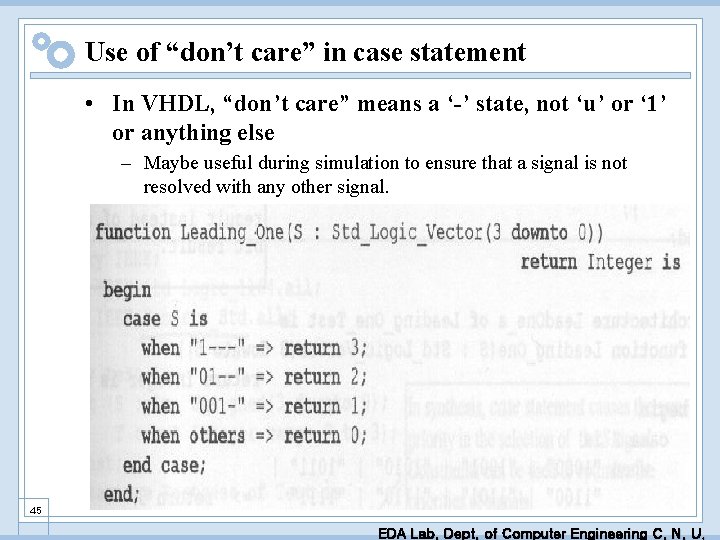

Use of “don’t care” in case statement • In VHDL, “don’t care” means a ‘-’ state, not ‘u’ or ‘ 1’ or anything else – Maybe useful during simulation to ensure that a signal is not resolved with any other signal. 45 EDA Lab. Dept. of Computer Engineering C. N. U.

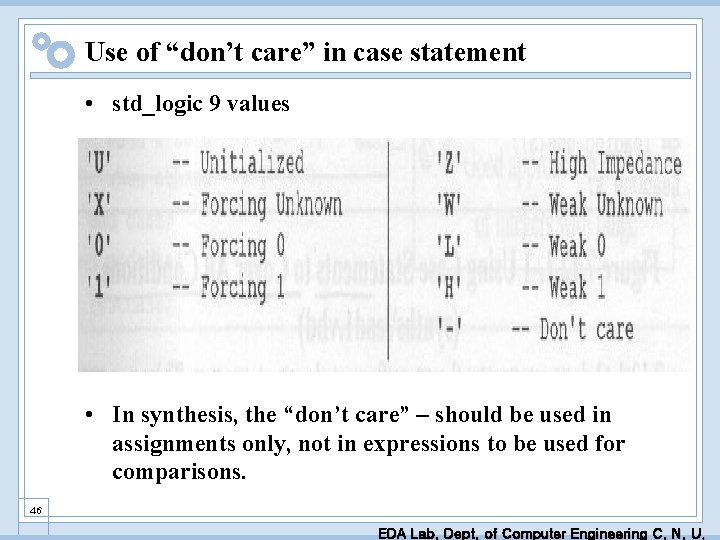

Use of “don’t care” in case statement • std_logic 9 values • In synthesis, the “don’t care” – should be used in assignments only, not in expressions to be used for comparisons. 46 EDA Lab. Dept. of Computer Engineering C. N. U.

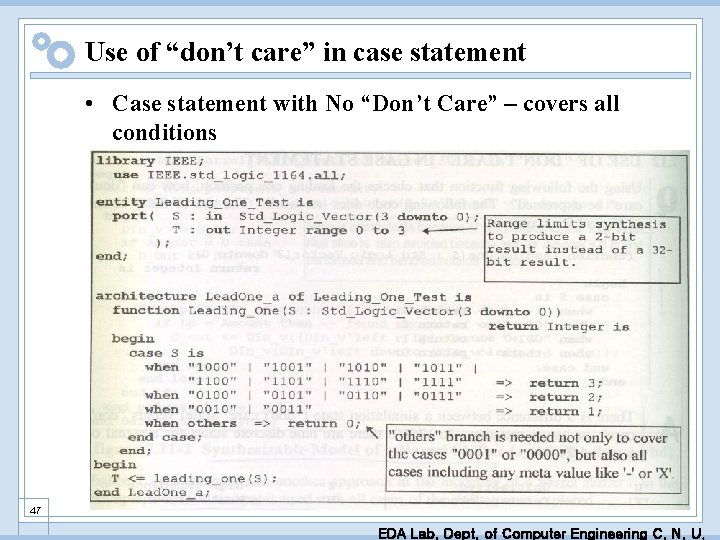

Use of “don’t care” in case statement • Case statement with No “Don’t Care” – covers all conditions 47 EDA Lab. Dept. of Computer Engineering C. N. U.

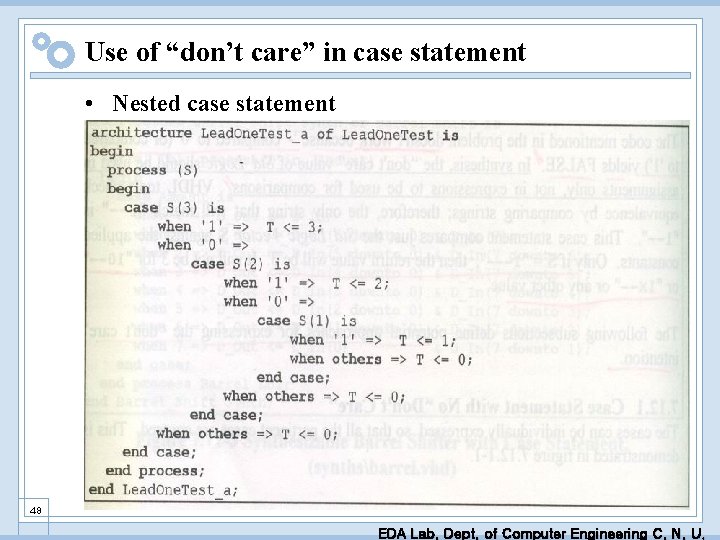

Use of “don’t care” in case statement • Nested case statement 48 EDA Lab. Dept. of Computer Engineering C. N. U.

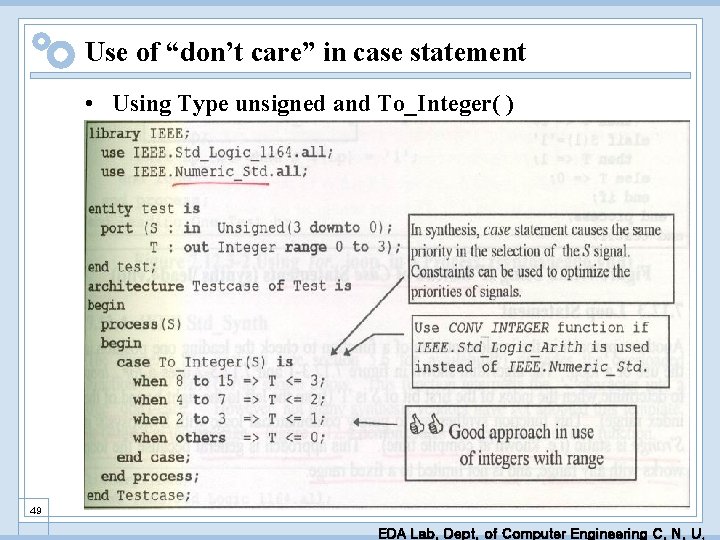

Use of “don’t care” in case statement • Using Type unsigned and To_Integer( ) 49 EDA Lab. Dept. of Computer Engineering C. N. U.

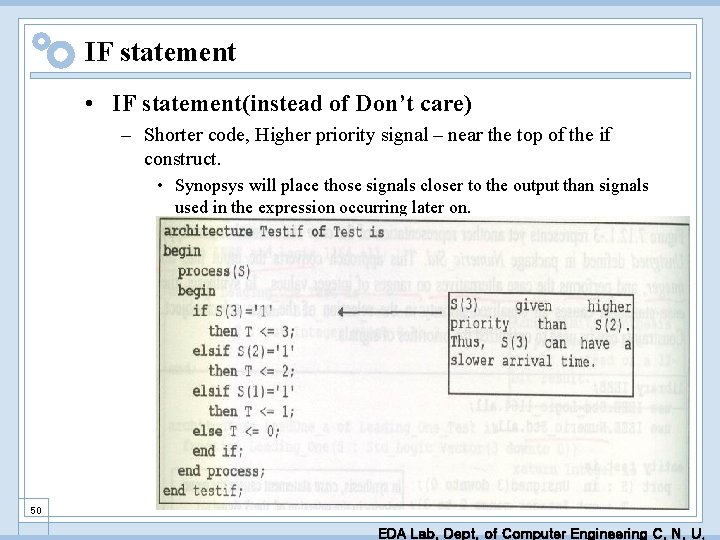

IF statement • IF statement(instead of Don’t care) – Shorter code, Higher priority signal – near the top of the if construct. • Synopsys will place those signals closer to the output than signals used in the expression occurring later on. 50 EDA Lab. Dept. of Computer Engineering C. N. U.

Loop statement • Loop statement(to check leading one position) – Function Leading_one: purely combinational logic if S’range is static. 51 EDA Lab. Dept. of Computer Engineering C. N. U.

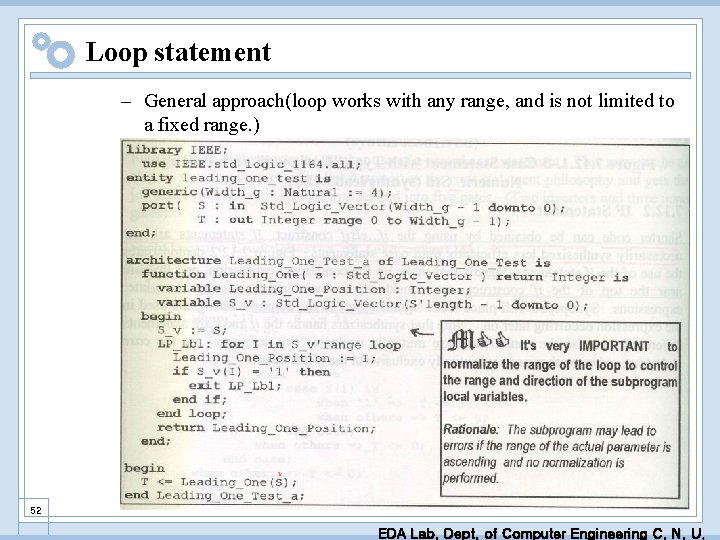

Loop statement – General approach(loop works with any range, and is not limited to a fixed range. ) 52 EDA Lab. Dept. of Computer Engineering C. N. U.

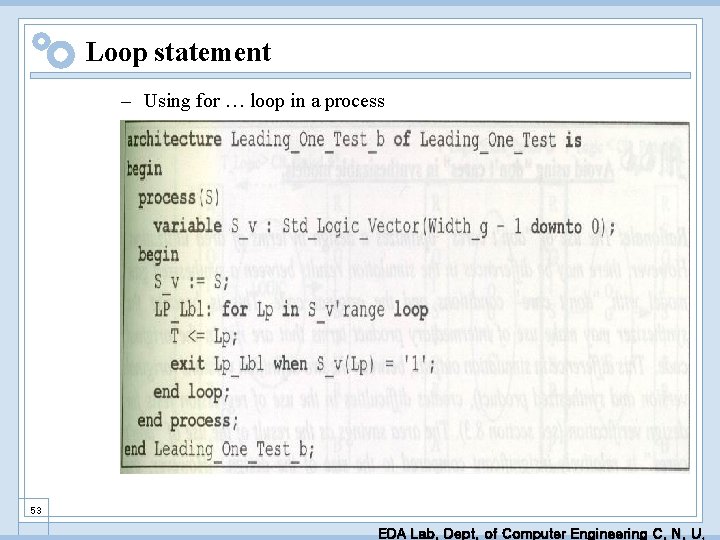

Loop statement – Using for … loop in a process 53 EDA Lab. Dept. of Computer Engineering C. N. U.

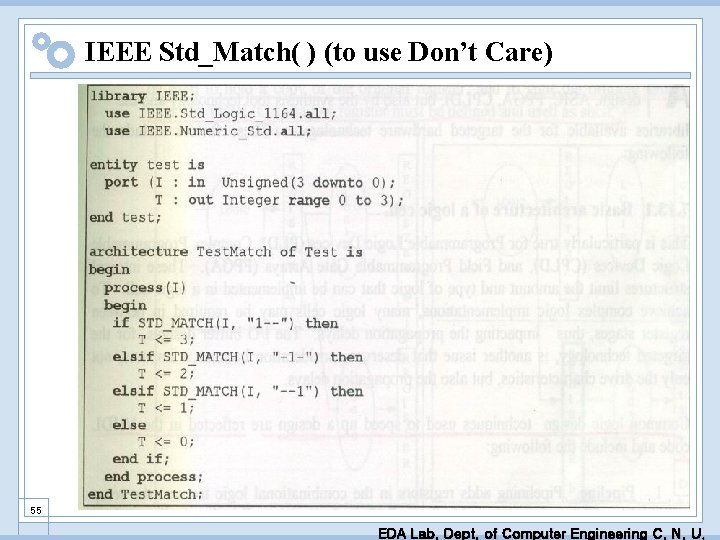

IEEE Std_Match( ) (to use Don’t Care) • Overloaded function STD_MATCH( ) in Numeric_Std package – – Interprets the ‘-’ into a true “don’t care”. An application of this function. Figure 7. 12. 4(55 페이지) Problem • Not many vendors have yet adopted this template. 54 EDA Lab. Dept. of Computer Engineering C. N. U.

IEEE Std_Match( ) (to use Don’t Care) 55 EDA Lab. Dept. of Computer Engineering C. N. U.

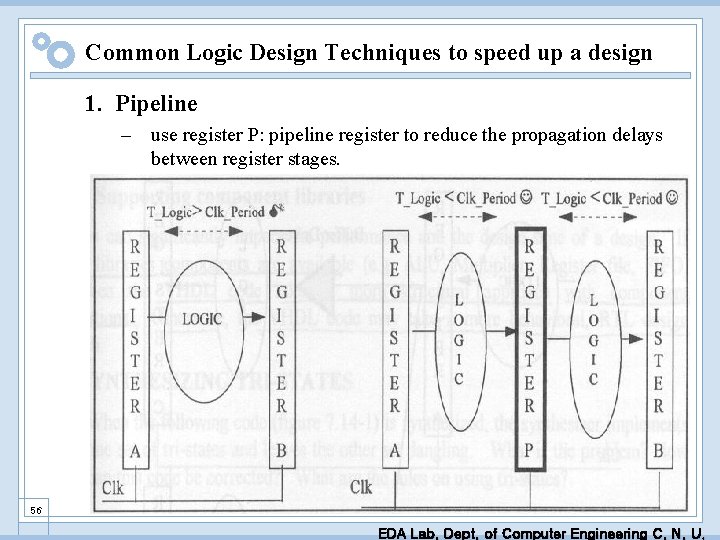

Common Logic Design Techniques to speed up a design 1. Pipeline – use register P: pipeline register to reduce the propagation delays between register stages. 56 EDA Lab. Dept. of Computer Engineering C. N. U.

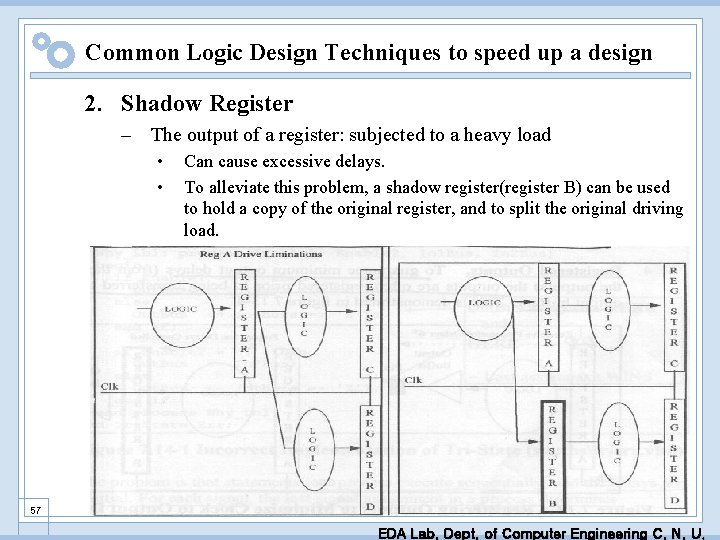

Common Logic Design Techniques to speed up a design 2. Shadow Register – The output of a register: subjected to a heavy load • • Can cause excessive delays. To alleviate this problem, a shadow register(register B) can be used to hold a copy of the original register, and to split the original driving load. 57 EDA Lab. Dept. of Computer Engineering C. N. U.

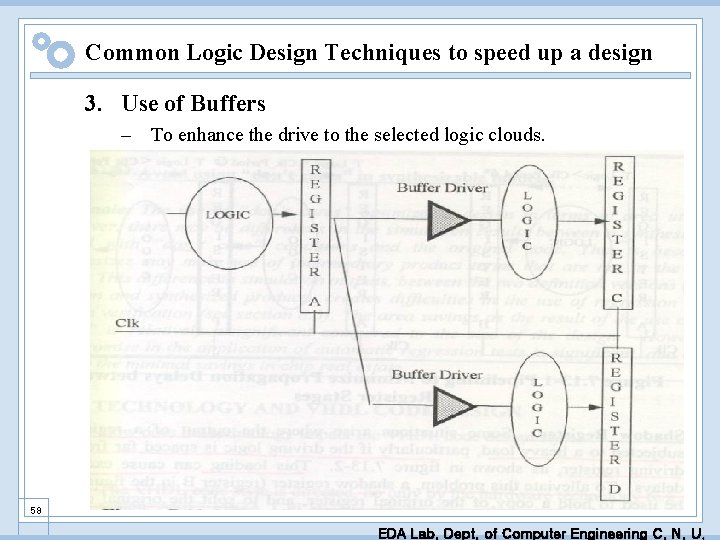

Common Logic Design Techniques to speed up a design 3. Use of Buffers – To enhance the drive to the selected logic clouds. 58 EDA Lab. Dept. of Computer Engineering C. N. U.

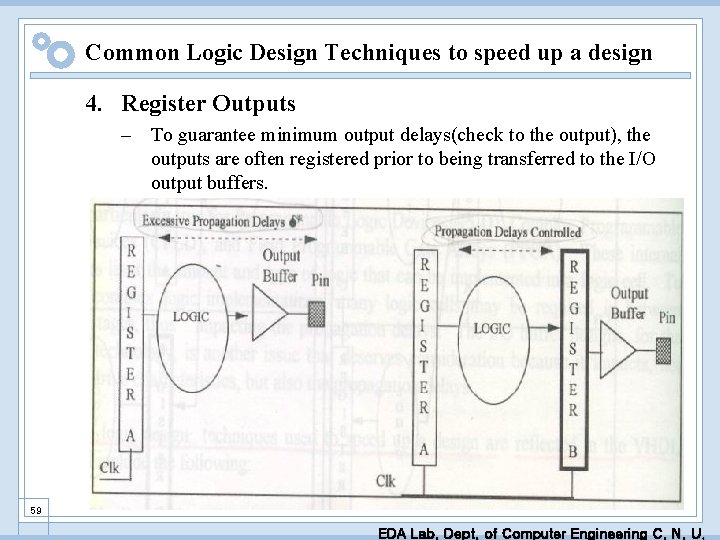

Common Logic Design Techniques to speed up a design 4. Register Outputs – To guarantee minimum output delays(check to the output), the outputs are often registered prior to being transferred to the I/O output buffers. 59 EDA Lab. Dept. of Computer Engineering C. N. U.

Synthesis Tools & Component Libraries • If the synthesizer fails to achieve the time requirements, then the code and/or the architecture must be modified appropriately. • Libraries: significantly impact the performance and the design time. – If tailored library components are available(ALU, FIFO, Register file, etc), the VHDL code takes a more structural approach with component instantiations. 60 EDA Lab. Dept. of Computer Engineering C. N. U.

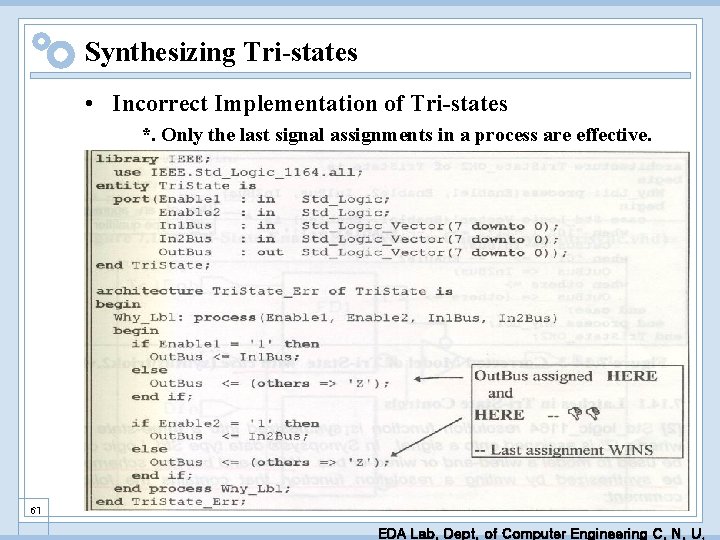

Synthesizing Tri-states • Incorrect Implementation of Tri-states *. Only the last signal assignments in a process are effective. 61 EDA Lab. Dept. of Computer Engineering C. N. U.

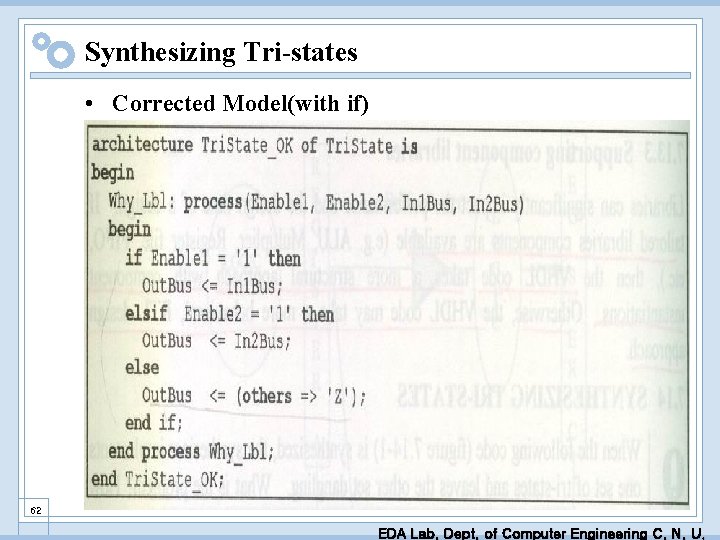

Synthesizing Tri-states • Corrected Model(with if) 62 EDA Lab. Dept. of Computer Engineering C. N. U.

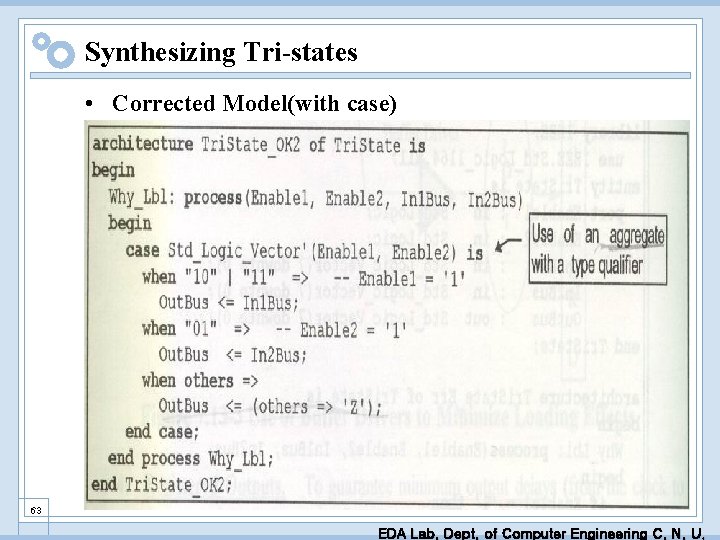

Synthesizing Tri-states • Corrected Model(with case) 63 EDA Lab. Dept. of Computer Engineering C. N. U.

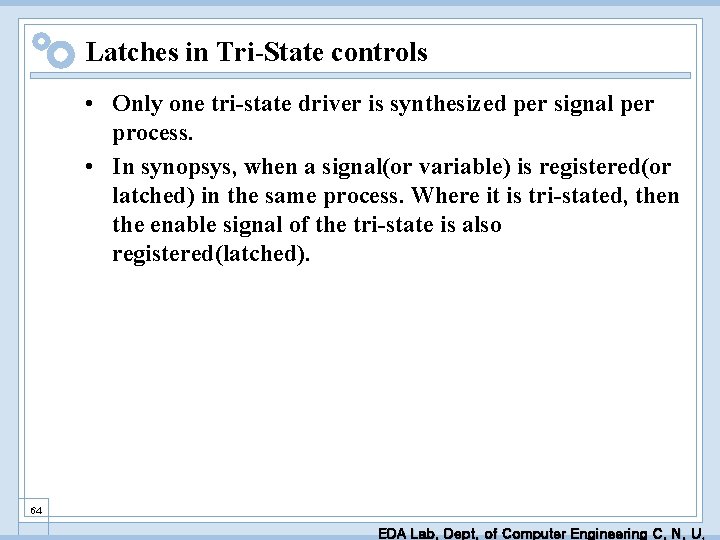

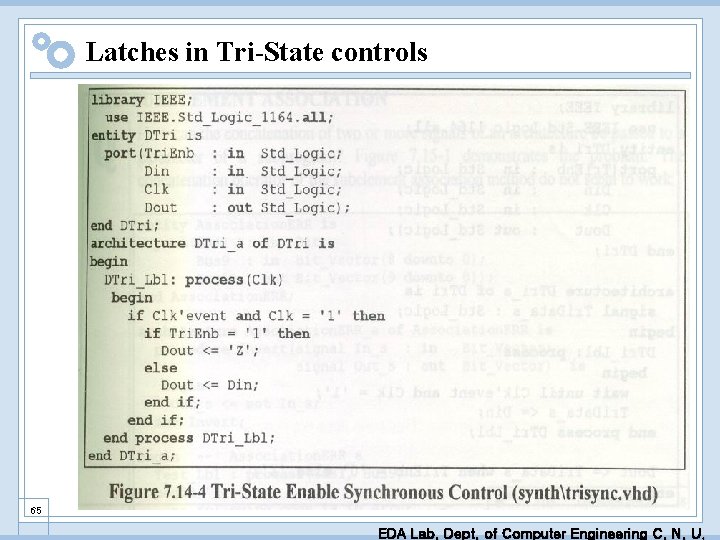

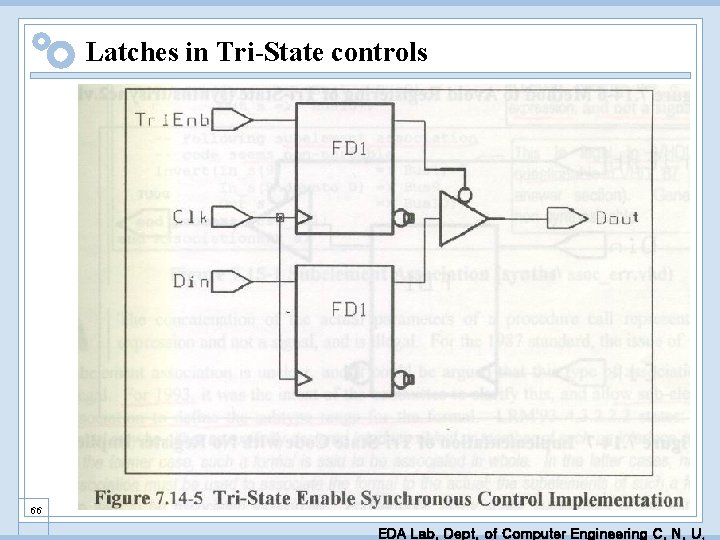

Latches in Tri-State controls • Only one tri-state driver is synthesized per signal per process. • In synopsys, when a signal(or variable) is registered(or latched) in the same process. Where it is tri-stated, then the enable signal of the tri-state is also registered(latched). 64 EDA Lab. Dept. of Computer Engineering C. N. U.

Latches in Tri-State controls 65 EDA Lab. Dept. of Computer Engineering C. N. U.

Latches in Tri-State controls 66 EDA Lab. Dept. of Computer Engineering C. N. U.

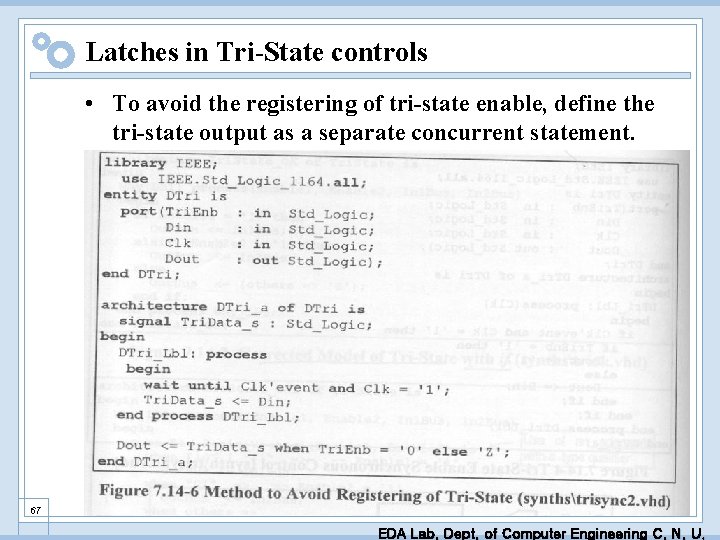

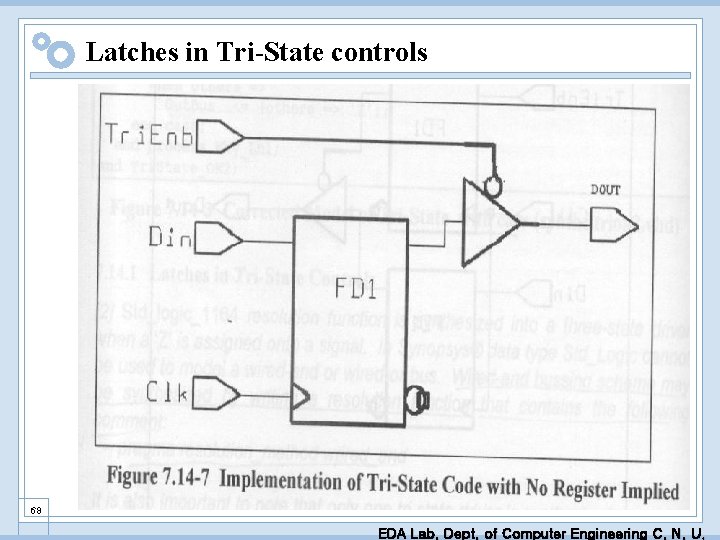

Latches in Tri-State controls • To avoid the registering of tri-state enable, define the tri-state output as a separate concurrent statement. 67 EDA Lab. Dept. of Computer Engineering C. N. U.

Latches in Tri-State controls 68 EDA Lab. Dept. of Computer Engineering C. N. U.

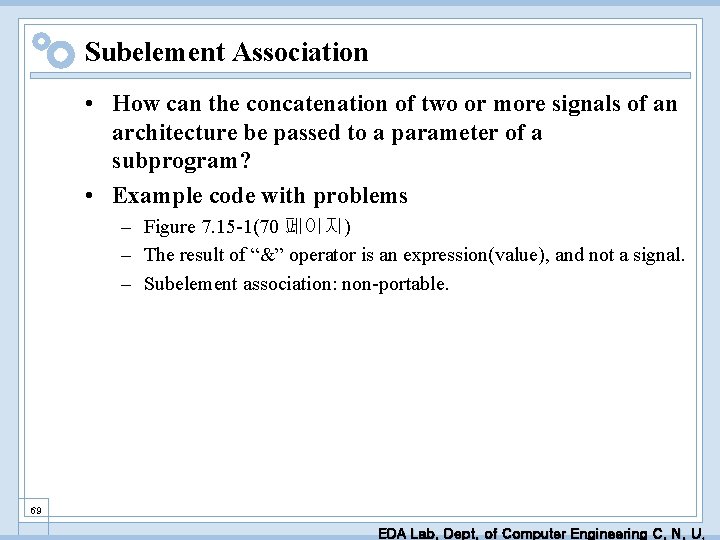

Subelement Association • How can the concatenation of two or more signals of an architecture be passed to a parameter of a subprogram? • Example code with problems – Figure 7. 15 -1(70 페이지) – The result of “&” operator is an expression(value), and not a signal. – Subelement association: non-portable. 69 EDA Lab. Dept. of Computer Engineering C. N. U.

Subelement Association 70 EDA Lab. Dept. of Computer Engineering C. N. U.

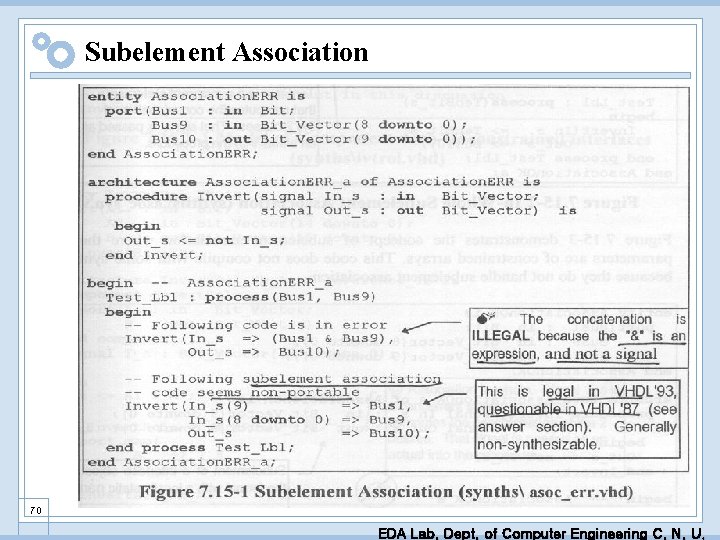

Subelement Association • “In-whole Subelement Association”(using a temporary signal that computes “&”) 71 EDA Lab. Dept. of Computer Engineering C. N. U.

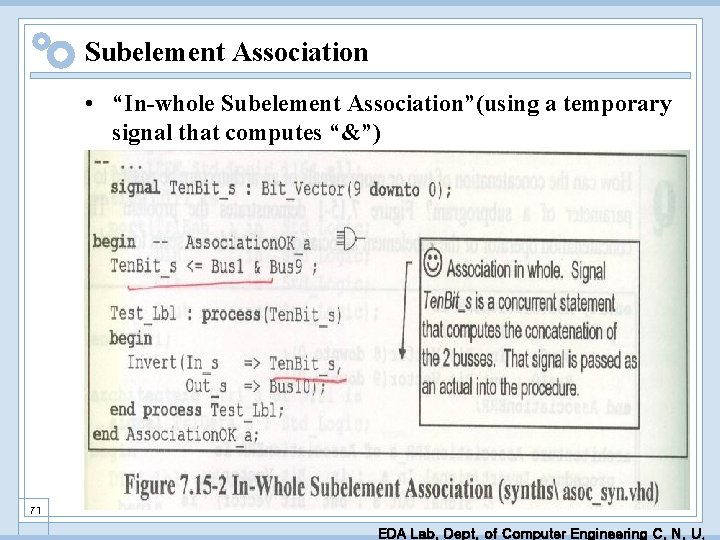

Subelement Association • Subelement Association: agree with VHDL’ 93, but some synthesizers do not handle 72 EDA Lab. Dept. of Computer Engineering C. N. U.

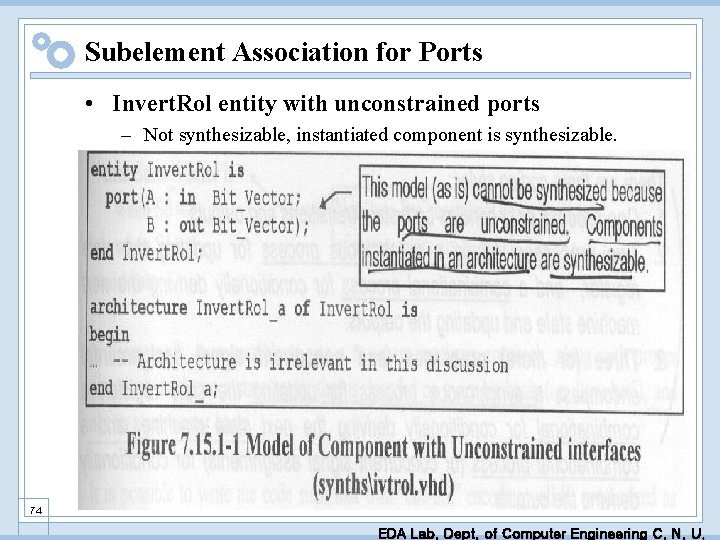

Subelement Association for Ports • The rules for port associations are the same as the ones described above. • The port association “In-whole” is the most portable and synthesizable. 73 EDA Lab. Dept. of Computer Engineering C. N. U.

Subelement Association for Ports • Invert. Rol entity with unconstrained ports – Not synthesizable, instantiated component is synthesizable. 74 EDA Lab. Dept. of Computer Engineering C. N. U.

Finite State Machine • Moore Machine, Mealy Machine • Coding styles – One process only handles both state transitions and outputs. – Two processes include a synchronous process for updating the state register, and a combinational process for conditionally deriving the next machine state and updating the outputs. – Three (or more) processes (and concurrent signal assignments) encompass a synchronous process for updating the state register, a combinational for conditionally deriving the next state machine, and a combinational process (or concurrent signal assignments) for conditionally deriving the outputs. 75 EDA Lab. Dept. of Computer Engineering C. N. U.

One-Hot Encoding(state encoding) • One-hot encoding: each bit represents a state. – Constant S 0 : Std_Logic_Vector (3 downto 0) : = “ 0001”; Constant S 1 : Std_Logic_Vector (3 downto 0) : = “ 0010”; Constant S 2 : Std_Logic_Vector (3 downto 0) : = “ 0100”; Constant S 3 : Std_Logic_Vector (3 downto 0) : = “ 1000”; • A “case” is used for the state transitions. – The entire state vector is decoded (not one-hot encoding) 76 EDA Lab. Dept. of Computer Engineering C. N. U.

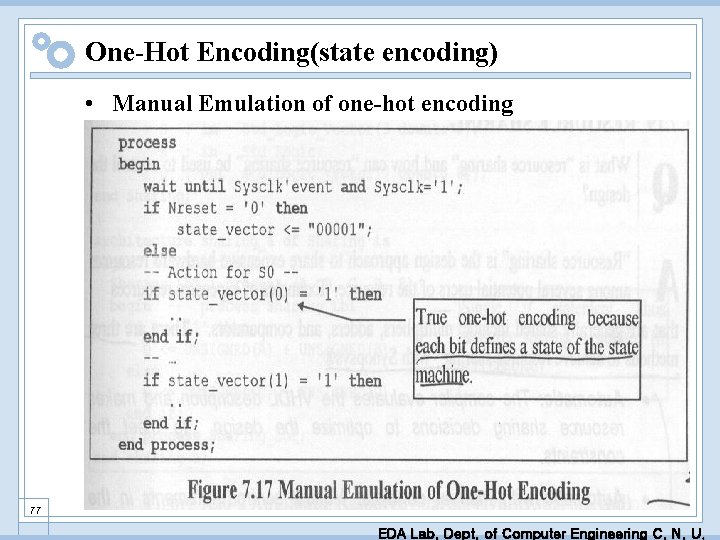

One-Hot Encoding(state encoding) • Manual Emulation of one-hot encoding 77 EDA Lab. Dept. of Computer Engineering C. N. U.

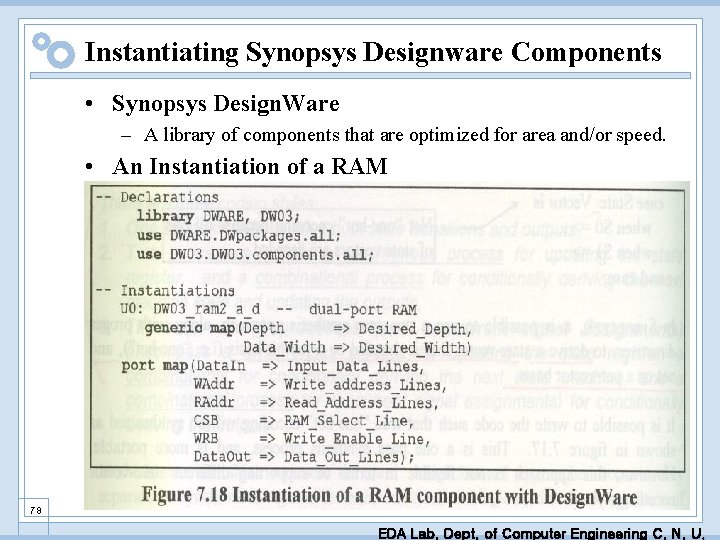

Instantiating Synopsys Designware Components • Synopsys Design. Ware – A library of components that are optimized for area and/or speed. • An Instantiation of a RAM 78 EDA Lab. Dept. of Computer Engineering C. N. U.

Resource Sharing • • The design approach to share expensive hardware resources among several uses of the resource. Three Methods to achieve resource sharing 1. Automatic: compile optimizes the design to meet the constraints. 2. Automatic with manual controls: manual control statement – used to assign operations to resources explicitly. 3. Manual 79 EDA Lab. Dept. of Computer Engineering C. N. U.

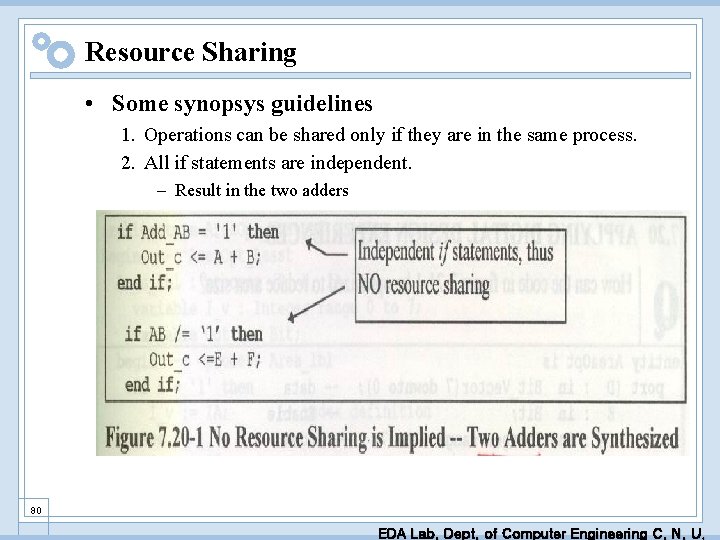

Resource Sharing • Some synopsys guidelines 1. Operations can be shared only if they are in the same process. 2. All if statements are independent. – Result in the two adders 80 EDA Lab. Dept. of Computer Engineering C. N. U.

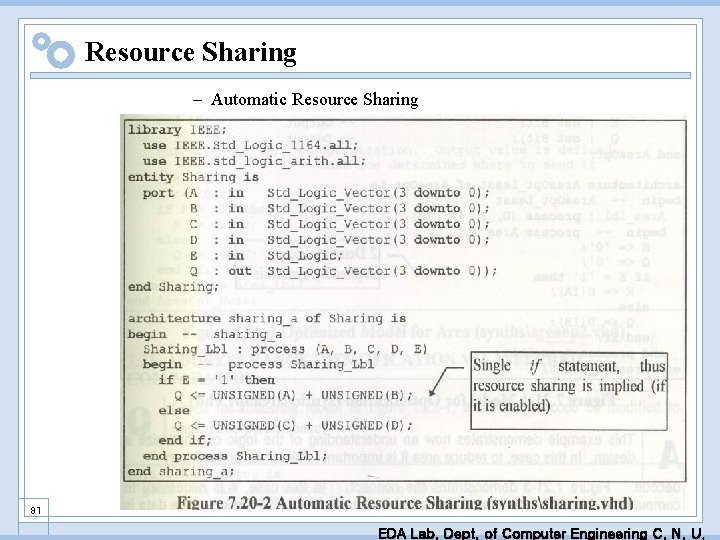

Resource Sharing – Automatic Resource Sharing 81 EDA Lab. Dept. of Computer Engineering C. N. U.

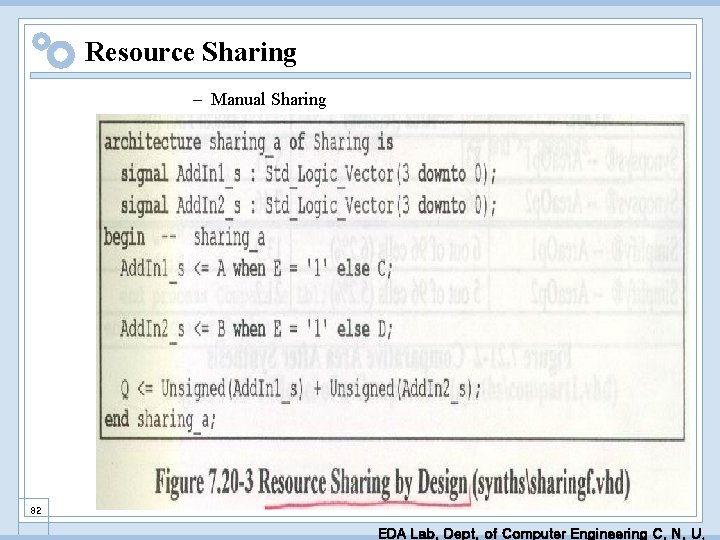

Resource Sharing – Manual Sharing 82 EDA Lab. Dept. of Computer Engineering C. N. U.

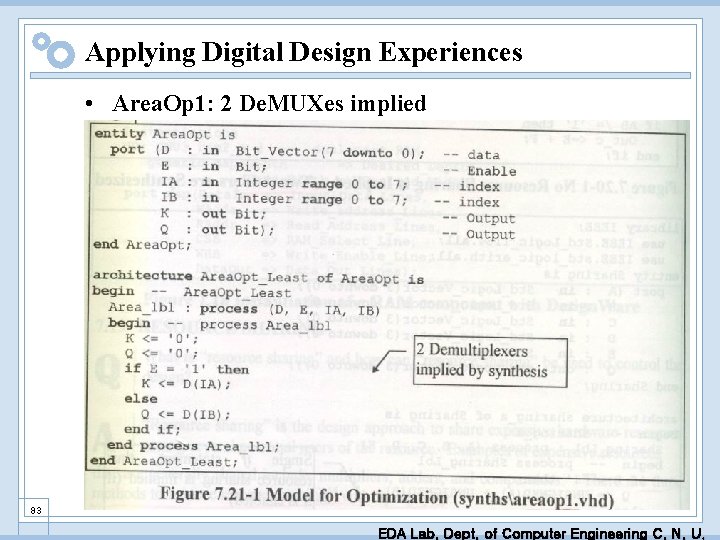

Applying Digital Design Experiences • Area. Op 1: 2 De. MUXes implied 83 EDA Lab. Dept. of Computer Engineering C. N. U.

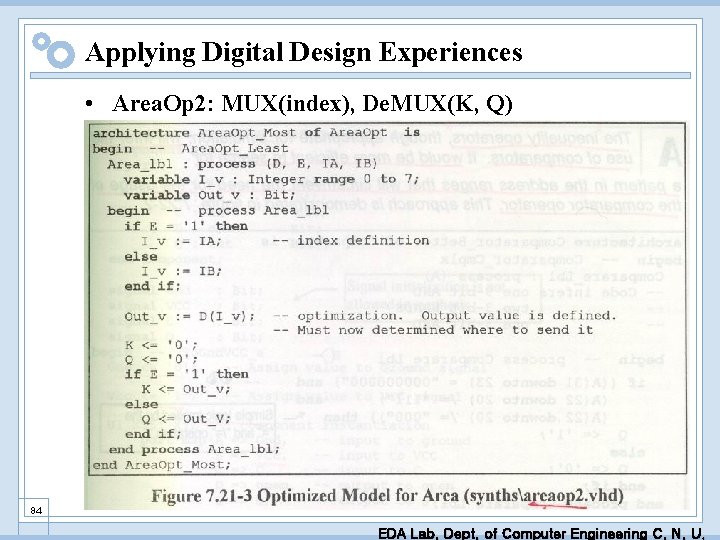

Applying Digital Design Experiences • Area. Op 2: MUX(index), De. MUX(K, Q) 84 EDA Lab. Dept. of Computer Engineering C. N. U.

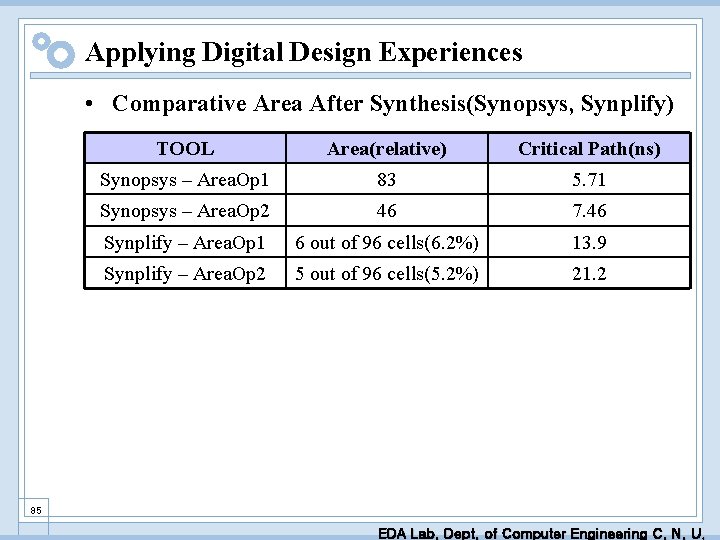

Applying Digital Design Experiences • Comparative Area After Synthesis(Synopsys, Synplify) TOOL Area(relative) Critical Path(ns) Synopsys – Area. Op 1 83 5. 71 Synopsys – Area. Op 2 46 7. 46 Synplify – Area. Op 1 6 out of 96 cells(6. 2%) 13. 9 Synplify – Area. Op 2 5 out of 96 cells(5. 2%) 21. 2 85 EDA Lab. Dept. of Computer Engineering C. N. U.

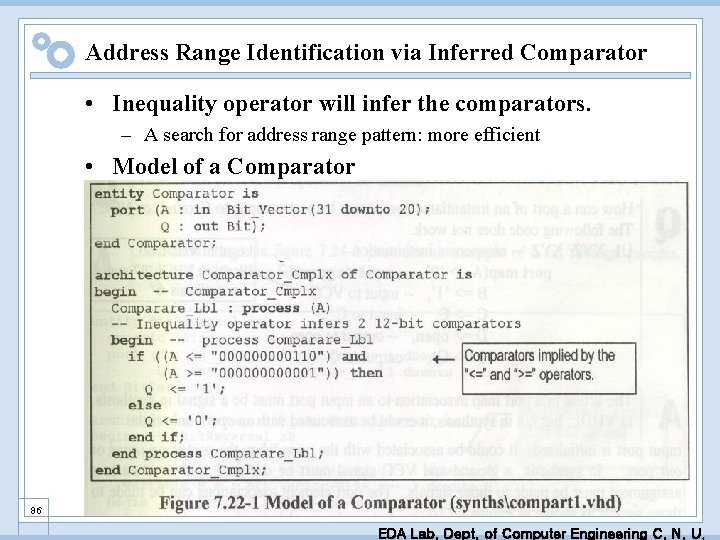

Address Range Identification via Inferred Comparator • Inequality operator will infer the comparators. – A search for address range pattern: more efficient • Model of a Comparator 86 EDA Lab. Dept. of Computer Engineering C. N. U.

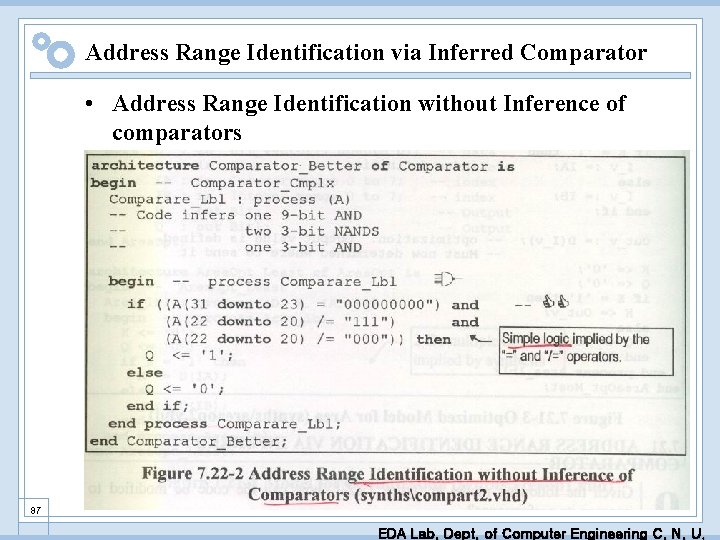

Address Range Identification via Inferred Comparator • Address Range Identification without Inference of comparators 87 EDA Lab. Dept. of Computer Engineering C. N. U.

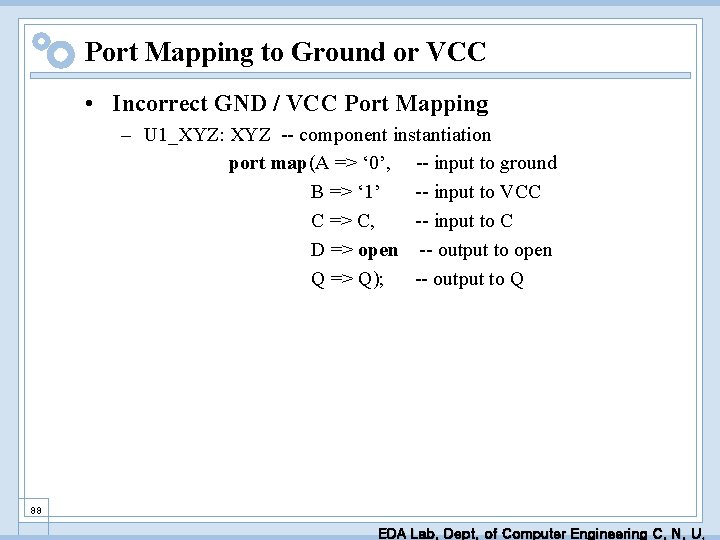

Port Mapping to Ground or VCC • Incorrect GND / VCC Port Mapping – U 1_XYZ: XYZ -- component instantiation port map(A => ‘ 0’, -- input to ground B => ‘ 1’ -- input to VCC C => C, -- input to C D => open -- output to open Q => Q); -- output to Q 88 EDA Lab. Dept. of Computer Engineering C. N. U.

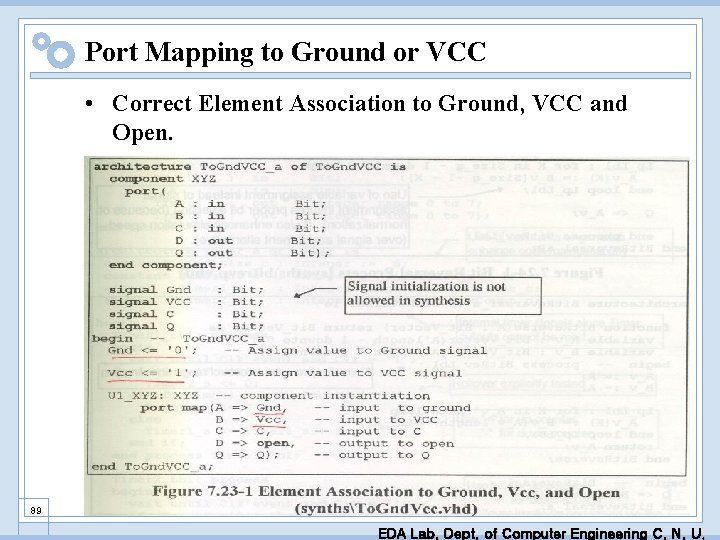

Port Mapping to Ground or VCC • Correct Element Association to Ground, VCC and Open. 89 EDA Lab. Dept. of Computer Engineering C. N. U.

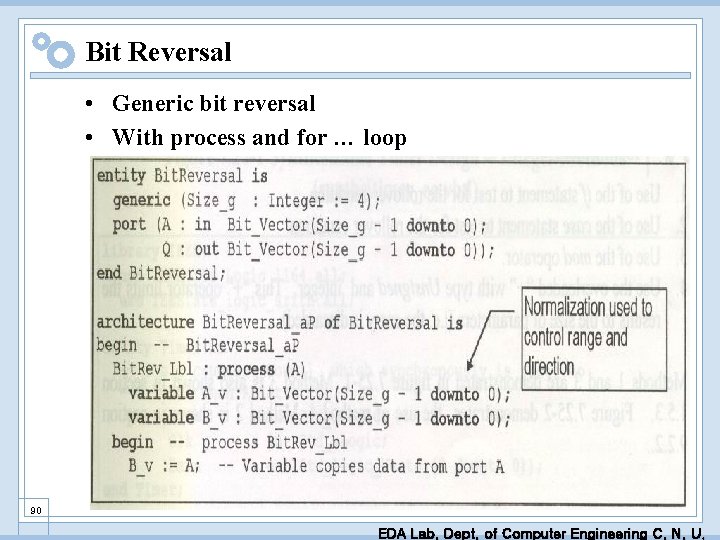

Bit Reversal • Generic bit reversal • With process and for … loop 90 EDA Lab. Dept. of Computer Engineering C. N. U.

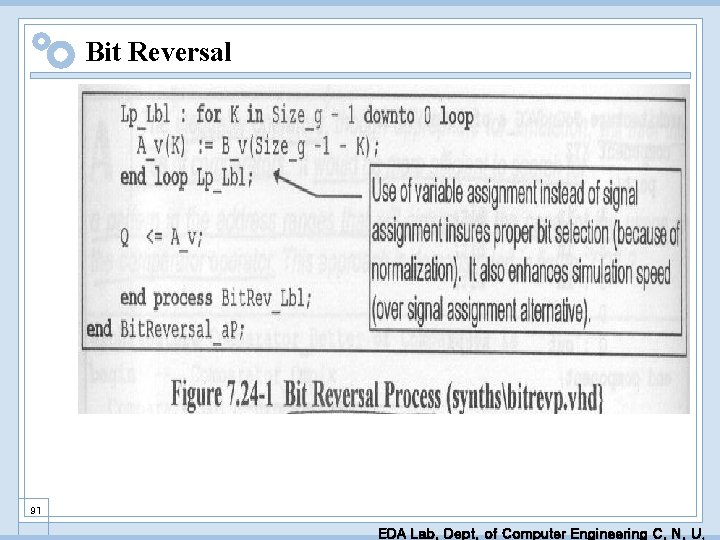

Bit Reversal 91 EDA Lab. Dept. of Computer Engineering C. N. U.

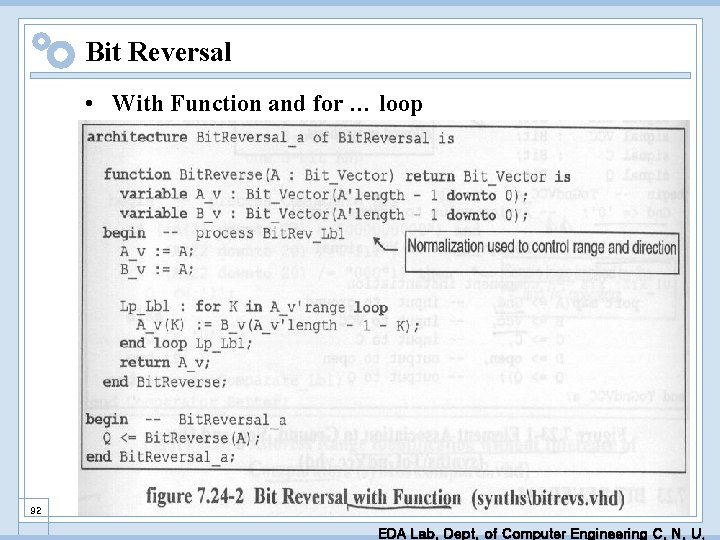

Bit Reversal • With Function and for … loop 92 EDA Lab. Dept. of Computer Engineering C. N. U.

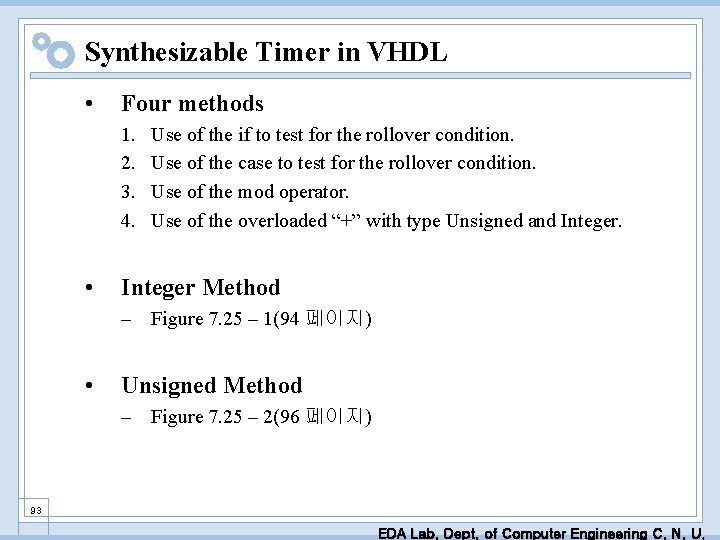

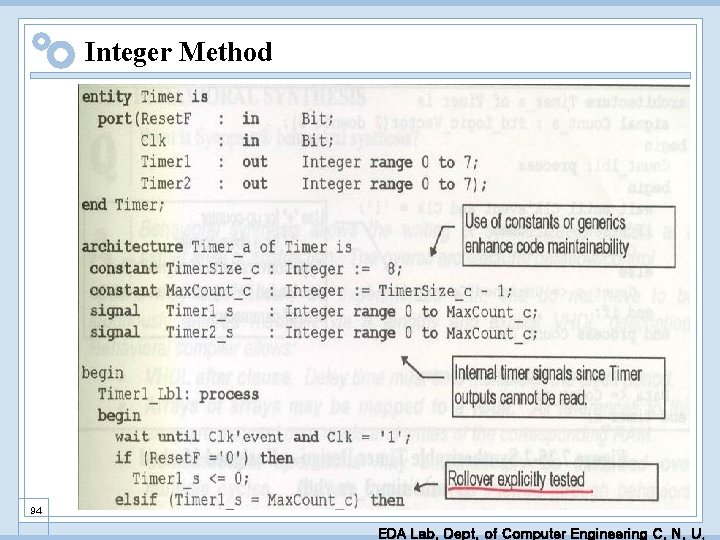

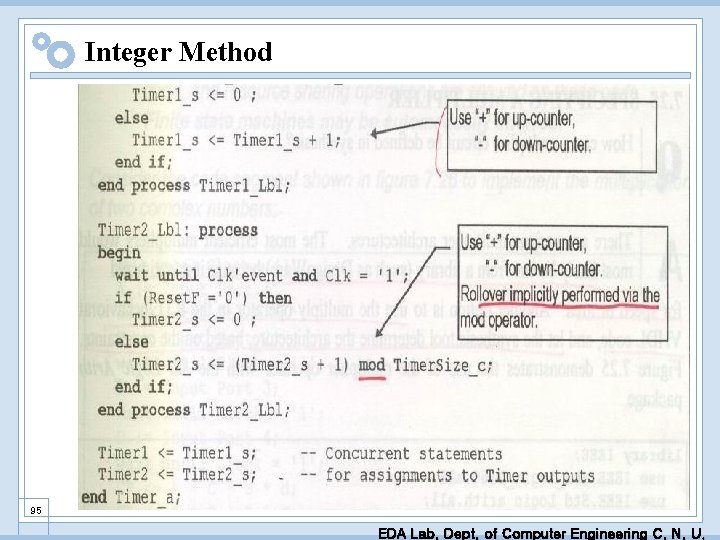

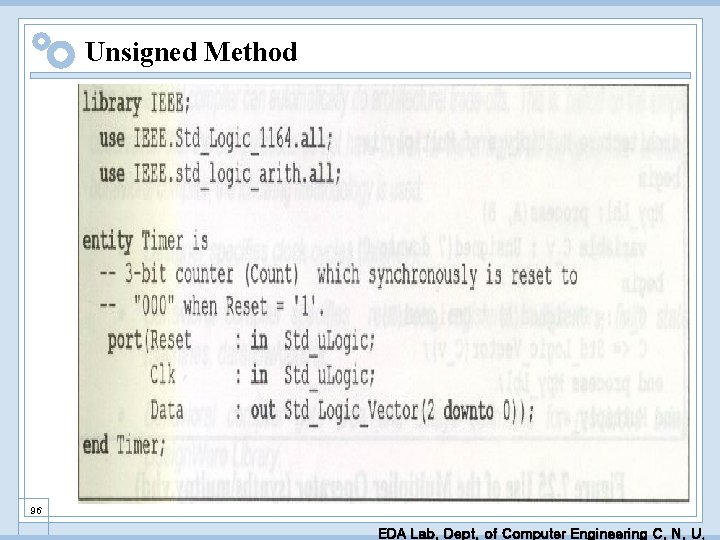

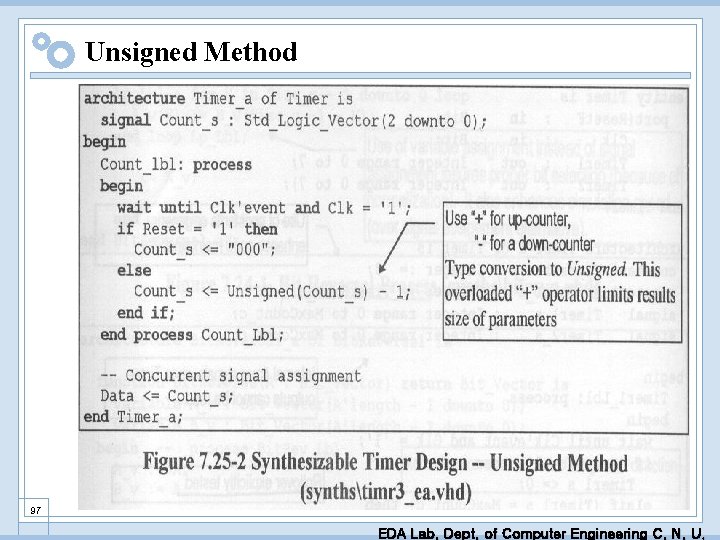

Synthesizable Timer in VHDL • Four methods 1. 2. 3. 4. • Use of the if to test for the rollover condition. Use of the case to test for the rollover condition. Use of the mod operator. Use of the overloaded “+” with type Unsigned and Integer Method – Figure 7. 25 – 1(94 페이지) • Unsigned Method – Figure 7. 25 – 2(96 페이지) 93 EDA Lab. Dept. of Computer Engineering C. N. U.

Integer Method 94 EDA Lab. Dept. of Computer Engineering C. N. U.

Integer Method 95 EDA Lab. Dept. of Computer Engineering C. N. U.

Unsigned Method 96 EDA Lab. Dept. of Computer Engineering C. N. U.

Unsigned Method 97 EDA Lab. Dept. of Computer Engineering C. N. U.

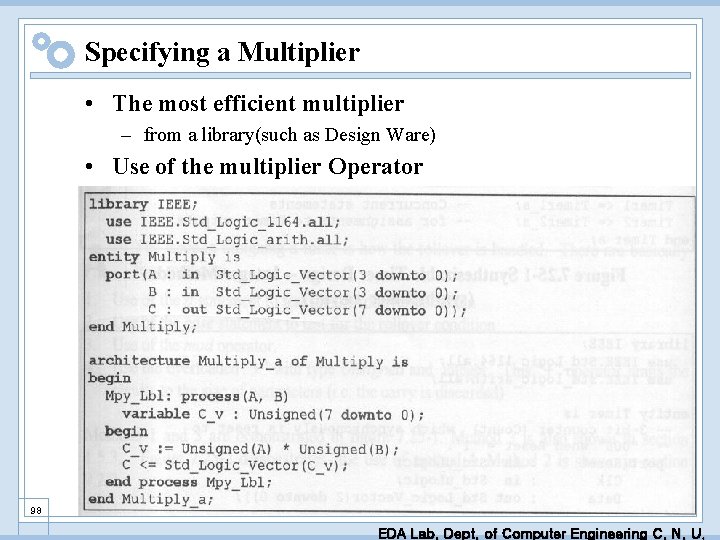

Specifying a Multiplier • The most efficient multiplier – from a library(such as Design Ware) • Use of the multiplier Operator 98 EDA Lab. Dept. of Computer Engineering C. N. U.

Behavioral Synthesis • Behavioral compiler allows – VHDL after clause – delay time must be a multiple of the clock period. – Arrays of arrays may be mapped to a RAM. – Combinational operations may automatically be extended over multiple cycles. Resource sharing operations are performed automatically. – Finite State Machine may be automatically inferred. – Process with multiple “wait” statements. 99 EDA Lab. Dept. of Computer Engineering C. N. U.

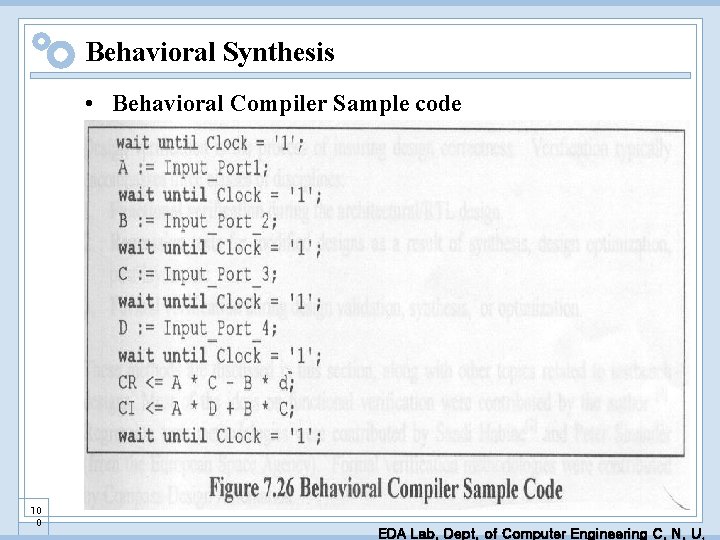

Behavioral Synthesis • Behavioral Compiler Sample code 10 0 EDA Lab. Dept. of Computer Engineering C. N. U.

Behavioral Synthesis • • BC automatically do architectural trade-offs. Methodolog 1. Designer specifies clock cycles(latency). 2. BC specifies resources, registers, MUXes, FSMs, data flow/control. 3. BC gets area and delays estimates for resources using Design. Ware Library. 10 1 EDA Lab. Dept. of Computer Engineering C. N. U.

- Slides: 101