Synopsys 1 Synopsys Tool jdragontrut chungbuk ac kr

Synopsys교육 1 Synopsys Tool 교육 정 용 군 (전자공학과 대학원) jdragon@trut. chungbuk. ac. kr 대상 : VLSI 설계 연구회 1, 2, 3 학년 기간 : 99. 1. 11 ~ 99. 1. 13

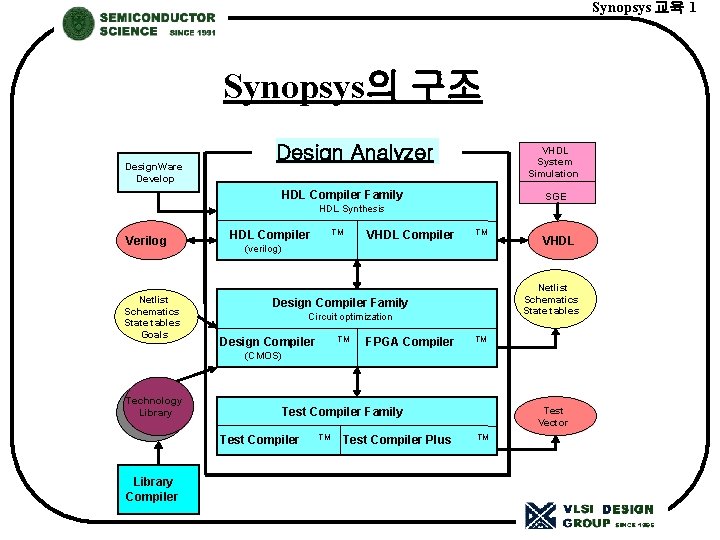

Synopsys 교육 1 Synopsys의 구조 Design. Ware Develop Design Analyzer VHDL System Simulation HDL Compiler Family SGE HDL Synthesis Verilog Netlist Schematics State tables Goals TM HDL Compiler VHDL Compiler TM (verilog) Netlist Schematics State tables Design Compiler Family Circuit optimization TM Design Compiler FPGA Compiler VHDL TM (CMOS) Technology Library Test Compiler Family Test Compiler Library Compiler TM Test Compiler Plus Test Vector TM

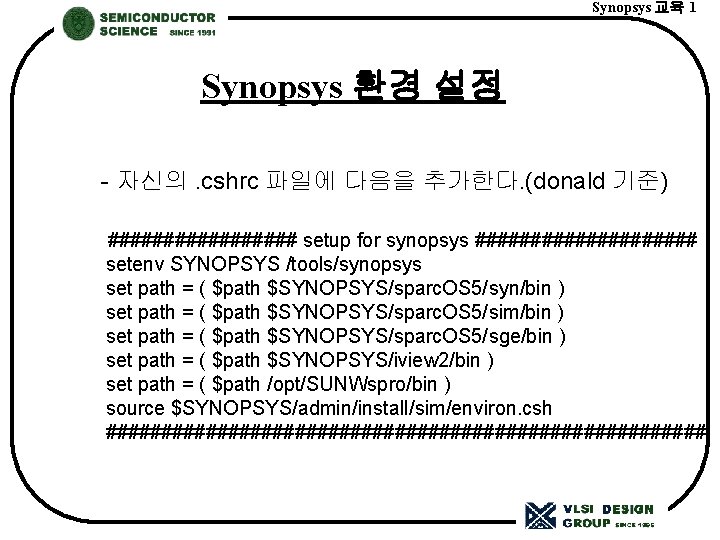

Synopsys 교육 1 Synopsys 환경 설정 - 자신의. cshrc 파일에 다음을 추가한다. (donald 기준) ######### setup for synopsys ########## setenv SYNOPSYS /tools/synopsys set path = ( $path $SYNOPSYS/sparc. OS 5/syn/bin ) set path = ( $path $SYNOPSYS/sparc. OS 5/sim/bin ) set path = ( $path $SYNOPSYS/sparc. OS 5/sge/bin ) set path = ( $path $SYNOPSYS/iview 2/bin ) set path = ( $path /opt/SUNWspro/bin ) source $SYNOPSYS/admin/install/sim/environ. csh ###########################

Synopsys 교육 1 VHDL System Simulator sge vhdlan gvan vhdlsim vhdldbx : : : Simulation Graphical Environment VHDL analyzer Graphical VHDL analyzer VHDL simulator VHDL debugger Synthesis with VHDL => Design Analyzer

![Synopsys 교육 1 VHDL System Simulator 1. SGE 시작 Ex : [donald: home/grad/dragon]sge & Synopsys 교육 1 VHDL System Simulator 1. SGE 시작 Ex : [donald: home/grad/dragon]sge &](http://slidetodoc.com/presentation_image_h/0d84839b937bb17248e21183de07eb82/image-5.jpg)

Synopsys 교육 1 VHDL System Simulator 1. SGE 시작 Ex : [donald: home/grad/dragon]sge &

Synopsys 교육 1 2. Drawing circuits (Schematic editor)

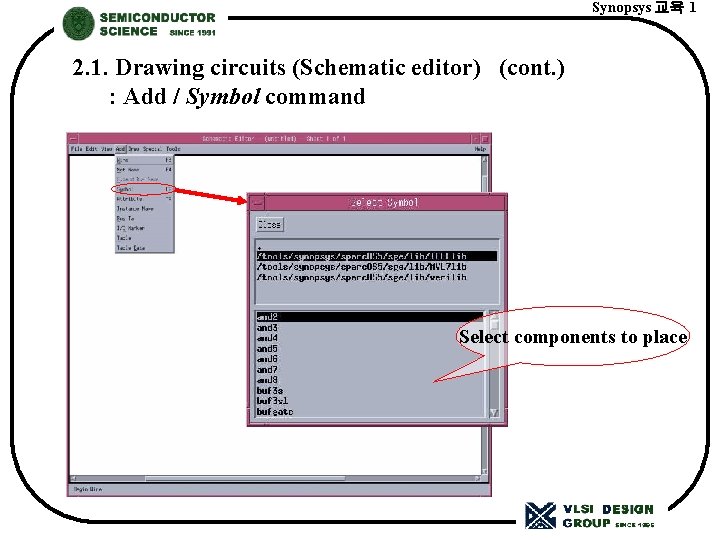

Synopsys 교육 1 2. 1. Drawing circuits (Schematic editor) (cont. ) : Add / Symbol command Select components to place

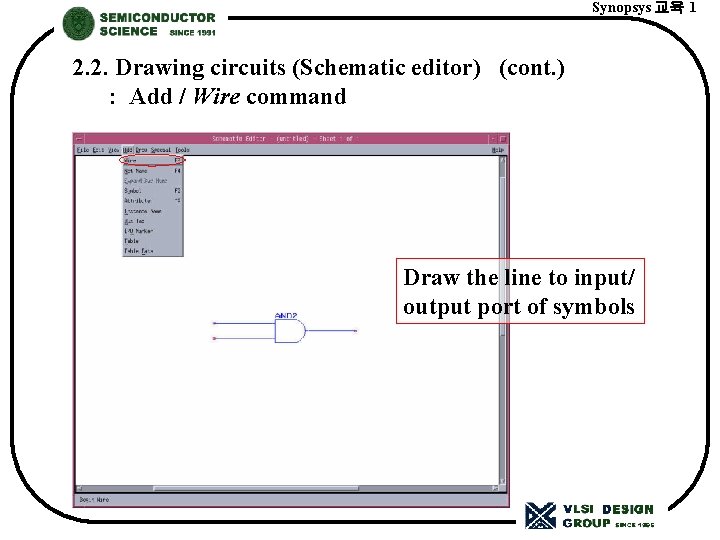

Synopsys 교육 1 2. 2. Drawing circuits (Schematic editor) (cont. ) : Add / Wire command Draw the line to input/ output port of symbols

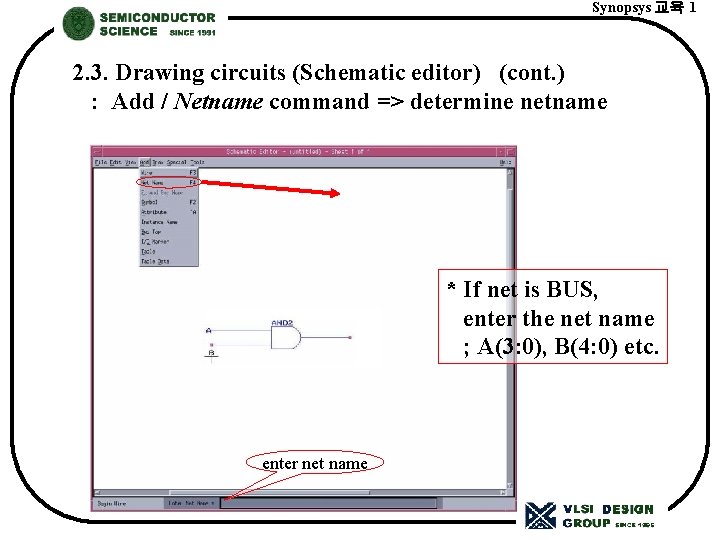

Synopsys 교육 1 2. 3. Drawing circuits (Schematic editor) (cont. ) : Add / Netname command => determine netname * If net is BUS, enter the net name ; A(3: 0), B(4: 0) etc. enter net name

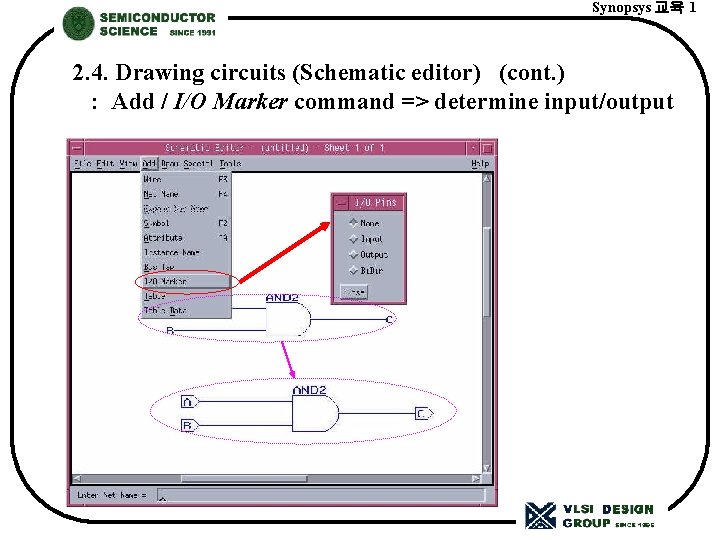

Synopsys 교육 1 2. 4. Drawing circuits (Schematic editor) (cont. ) : Add / I/O Marker command => determine input/output

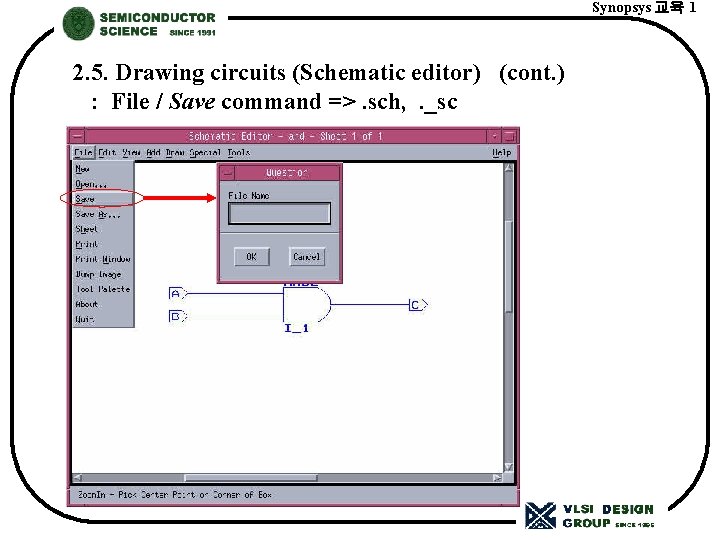

Synopsys 교육 1 2. 5. Drawing circuits (Schematic editor) (cont. ) : File / Save command =>. sch, . _sc

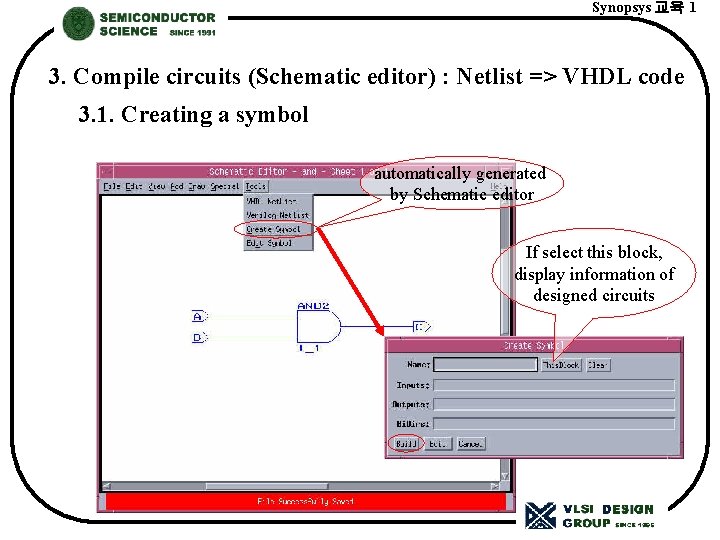

Synopsys 교육 1 3. Compile circuits (Schematic editor) : Netlist => VHDL code 3. 1. Creating a symbol automatically generated by Schematic editor If select this block, display information of designed circuits

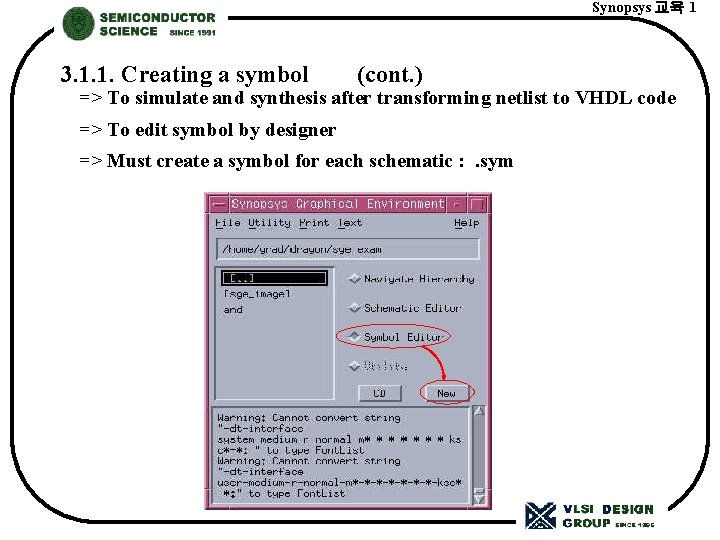

Synopsys 교육 1 3. 1. 1. Creating a symbol (cont. ) => To simulate and synthesis after transforming netlist to VHDL code => To edit symbol by designer => Must create a symbol for each schematic : . sym

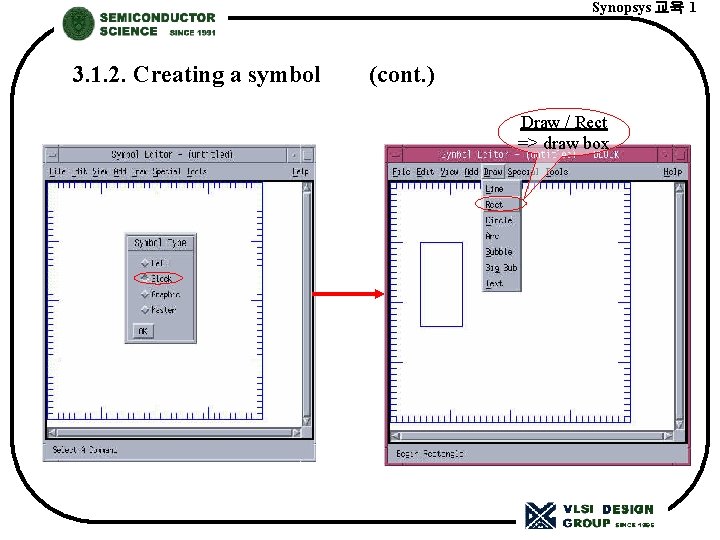

Synopsys 교육 1 3. 1. 2. Creating a symbol (cont. ) Draw / Rect => draw box

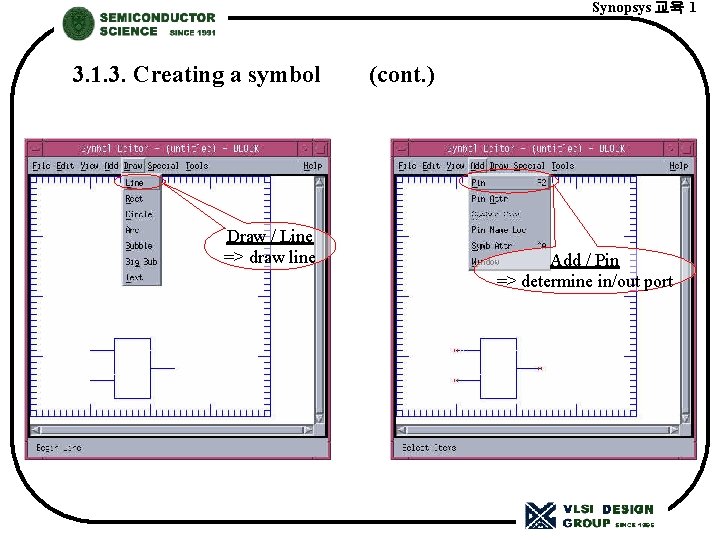

Synopsys 교육 1 3. 1. 3. Creating a symbol Draw / Line => draw line (cont. ) Add / Pin => determine in/out port

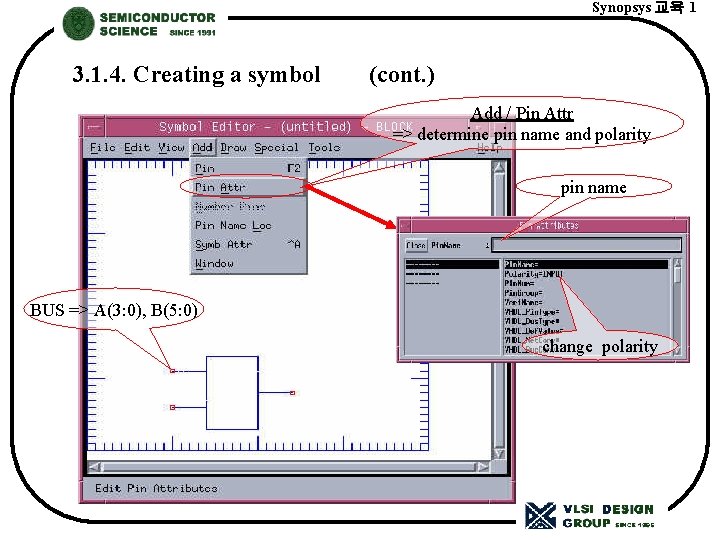

Synopsys 교육 1 3. 1. 4. Creating a symbol (cont. ) Add / Pin Attr => determine pin name and polarity pin name BUS => A(3: 0), B(5: 0) change polarity

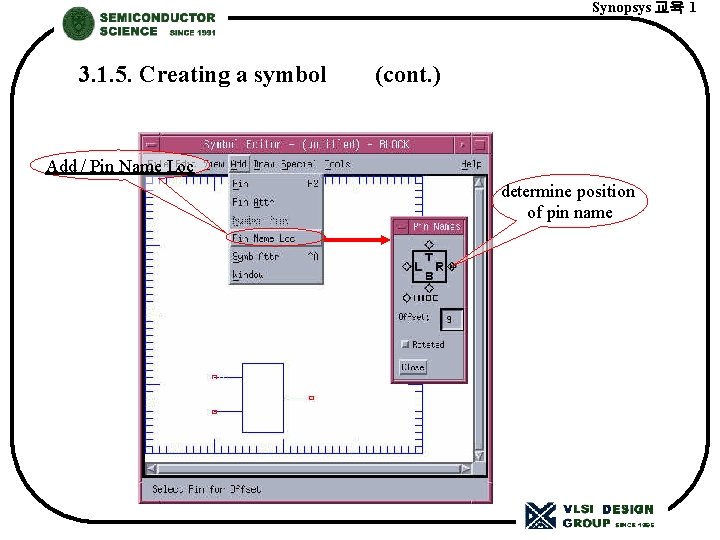

Synopsys 교육 1 3. 1. 5. Creating a symbol (cont. ) Add / Pin Name Loc determine position of pin name

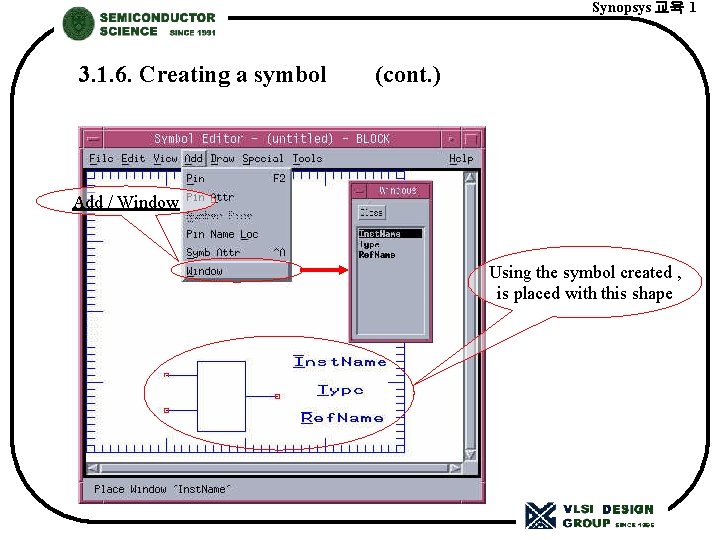

Synopsys 교육 1 3. 1. 6. Creating a symbol (cont. ) Add / Window Using the symbol created , is placed with this shape

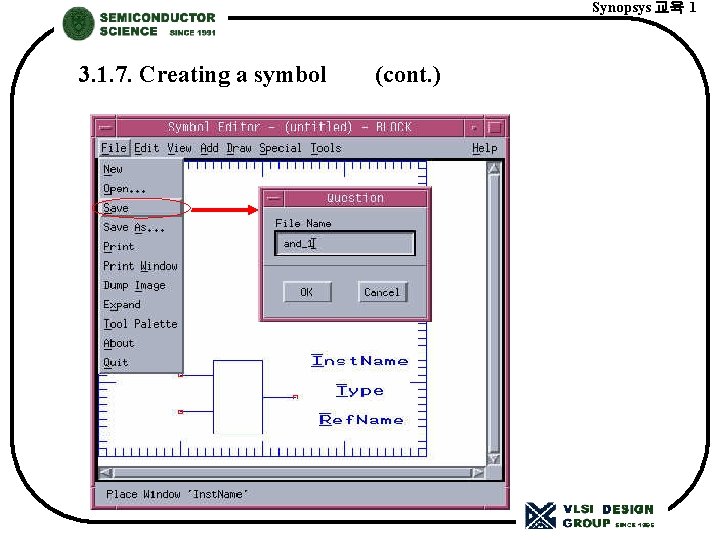

Synopsys 교육 1 3. 1. 7. Creating a symbol (cont. )

Synopsys 교육 1 3. 2. Generate VHDL code vi editor Netlist => VHDL code

Synopsys 교육 1 4. Simulation => It is the most useful method using test bench. 4. 1 Test Bench Generation 1) automatic generation by SGE 2) code test bench for yourself

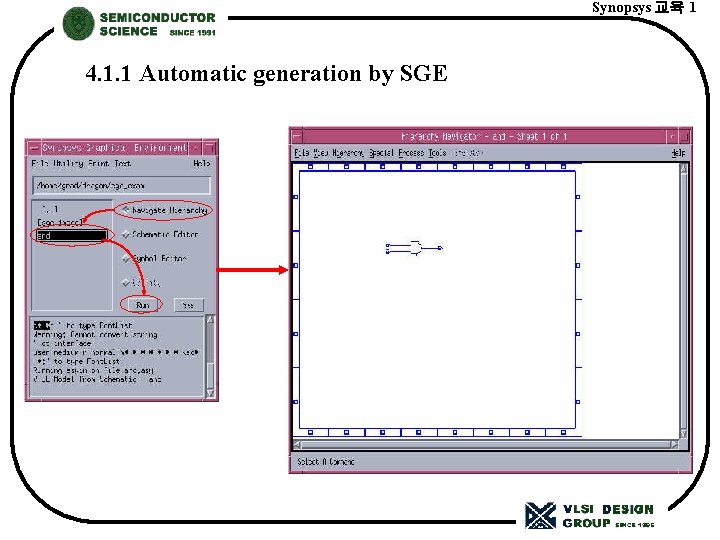

Synopsys 교육 1 4. 1. 1 Automatic generation by SGE

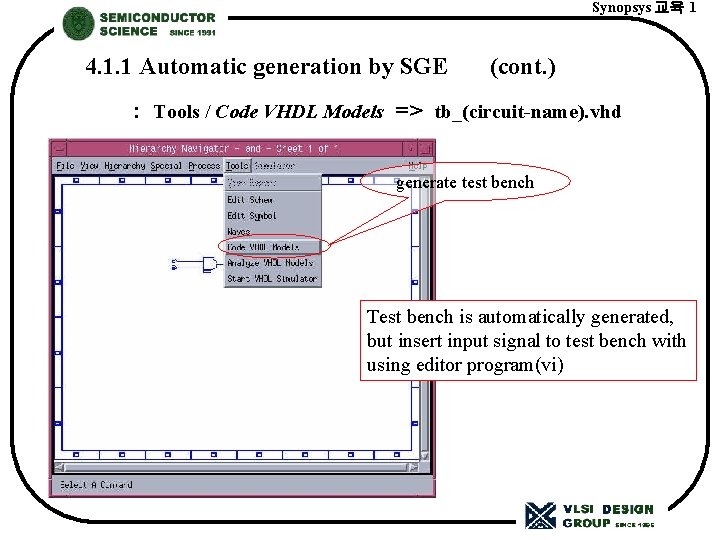

Synopsys 교육 1 4. 1. 1 Automatic generation by SGE (cont. ) : Tools / Code VHDL Models => tb_(circuit-name). vhd generate test bench Test bench is automatically generated, but insert input signal to test bench with using editor program(vi)

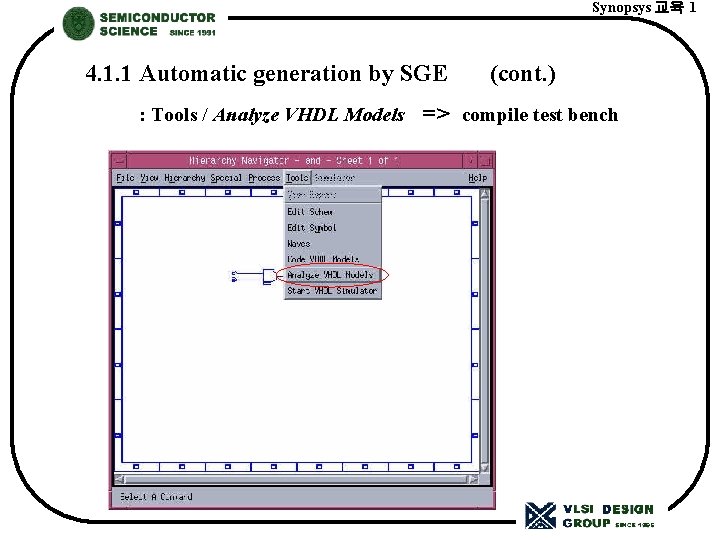

Synopsys 교육 1 4. 1. 1 Automatic generation by SGE : Tools / Analyze VHDL Models (cont. ) => compile test bench

Synopsys 교육 1 4. 1. 1 Automatic generation by SGE (cont. ) : Tools / Start VHDL Simulator => compile test bench VHDL debugger (vhdldbx) WAVE

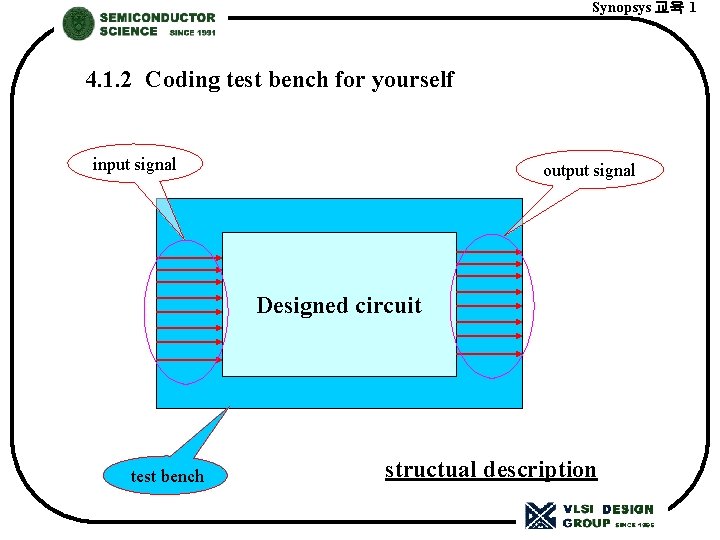

Synopsys 교육 1 4. 1. 2 Coding test bench for yourself input signal output signal Designed circuit test bench structual description

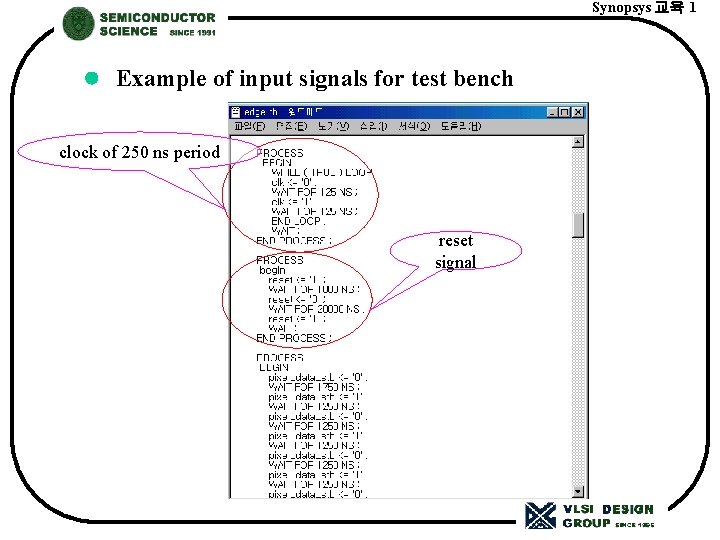

Synopsys 교육 1 Example of input signals for test bench clock of 250 ns period reset signal

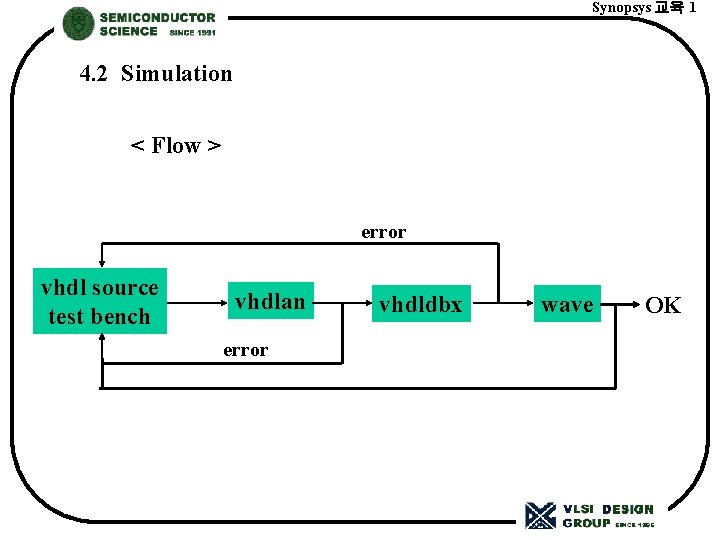

Synopsys 교육 1 4. 2 Simulation < Flow > error vhdl source test bench vhdlan error vhdldbx wave OK

![Synopsys 교육 1 4. 2. 1 vhdlan (shell mode) usage : vhdlan [option] (vhdl Synopsys 교육 1 4. 2. 1 vhdlan (shell mode) usage : vhdlan [option] (vhdl](http://slidetodoc.com/presentation_image_h/0d84839b937bb17248e21183de07eb82/image-29.jpg)

Synopsys 교육 1 4. 2. 1 vhdlan (shell mode) usage : vhdlan [option] (vhdl source, test bench) [option] -l : read vhdl file and generate *. lis file having error message -c : generate object code compiled -v : display information of analyzer Ex : vhdlan -l -c test. vhd cf) graphic mode : gvan

![Synopsys 교육 1 4. 2. 2 vhdldbx ( ex : [donald: home/grad/dragon/WORK]vhdldbx & ) Synopsys 교육 1 4. 2. 2 vhdldbx ( ex : [donald: home/grad/dragon/WORK]vhdldbx & )](http://slidetodoc.com/presentation_image_h/0d84839b937bb17248e21183de07eb82/image-30.jpg)

Synopsys 교육 1 4. 2. 2 vhdldbx ( ex : [donald: home/grad/dragon/WORK]vhdldbx & ) select configuration edit *. log file : have information in/out port being displayed in wave window ex) vi test. log trace clk trace a[0]. . 1. include *. log 2. run 25000

![Synopsys 교육 1 4. 2. 3 wave ( ex : [donald: home/grad/dragon/WORK]waves &) waveform Synopsys 교육 1 4. 2. 3 wave ( ex : [donald: home/grad/dragon/WORK]waves &) waveform](http://slidetodoc.com/presentation_image_h/0d84839b937bb17248e21183de07eb82/image-31.jpg)

Synopsys 교육 1 4. 2. 3 wave ( ex : [donald: home/grad/dragon/WORK]waves &) waveform file *. ow

![Synopsys 교육 1 4. 2. 3 wave ( ex : [donald: home/grad/dragon/WORK]waves &) (cont. Synopsys 교육 1 4. 2. 3 wave ( ex : [donald: home/grad/dragon/WORK]waves &) (cont.](http://slidetodoc.com/presentation_image_h/0d84839b937bb17248e21183de07eb82/image-32.jpg)

Synopsys 교육 1 4. 2. 3 wave ( ex : [donald: home/grad/dragon/WORK]waves &) (cont. )

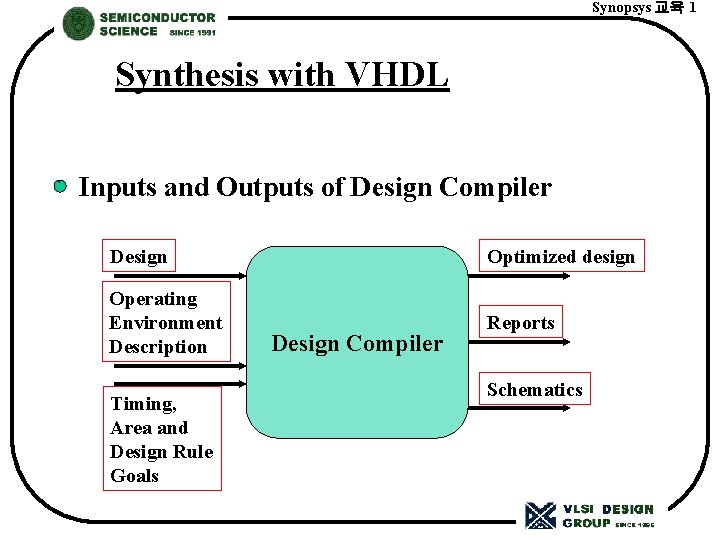

Synopsys 교육 1 Synthesis with VHDL ` Inputs and Outputs of Design Compiler Design Optimized design Operating Environment Description Reports Timing, Area and Design Rule Goals Design Compiler Schematics

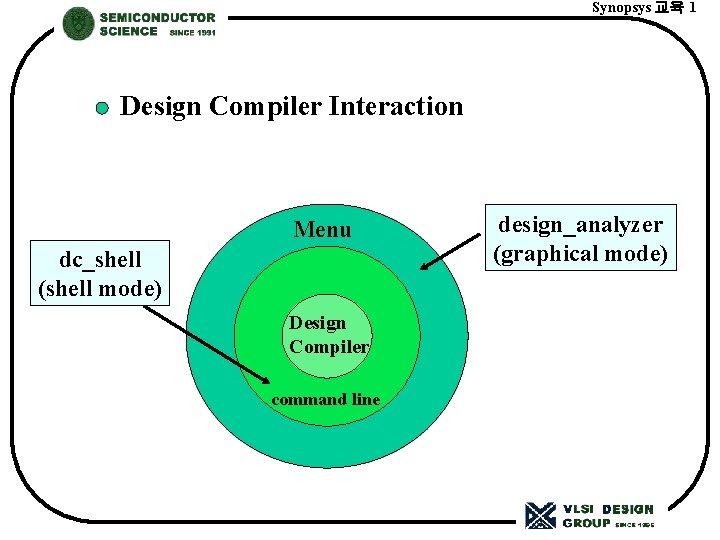

Synopsys 교육 1 Design Compiler Interaction Menu dc_shell (shell mode) Design Compiler command line design_analyzer (graphical mode)

![Synopsys 교육 1 Design analyzer 실행 Ex : [donald: home/grad/dragon]design_analyzer & Synopsys 교육 1 Design analyzer 실행 Ex : [donald: home/grad/dragon]design_analyzer &](http://slidetodoc.com/presentation_image_h/0d84839b937bb17248e21183de07eb82/image-35.jpg)

Synopsys 교육 1 Design analyzer 실행 Ex : [donald: home/grad/dragon]design_analyzer &

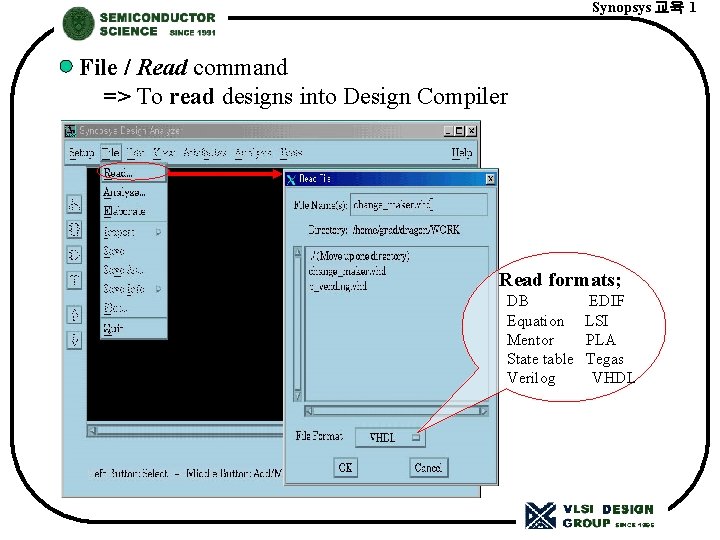

Synopsys 교육 1 File / Read command => To read designs into Design Compiler Read formats; DB Equation Mentor State table Verilog EDIF LSI PLA Tegas VHDL

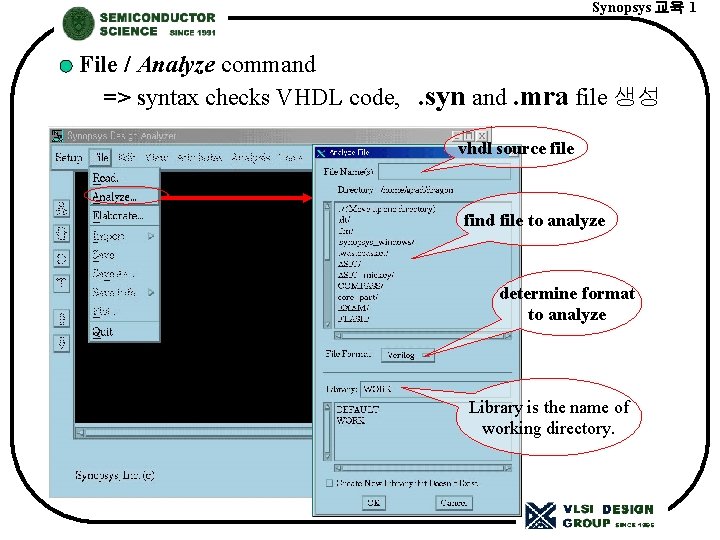

Synopsys 교육 1 File / Analyze command => syntax checks VHDL code, . syn and. mra file 생성 vhdl source file find file to analyze determine format to analyze Library is the name of working directory.

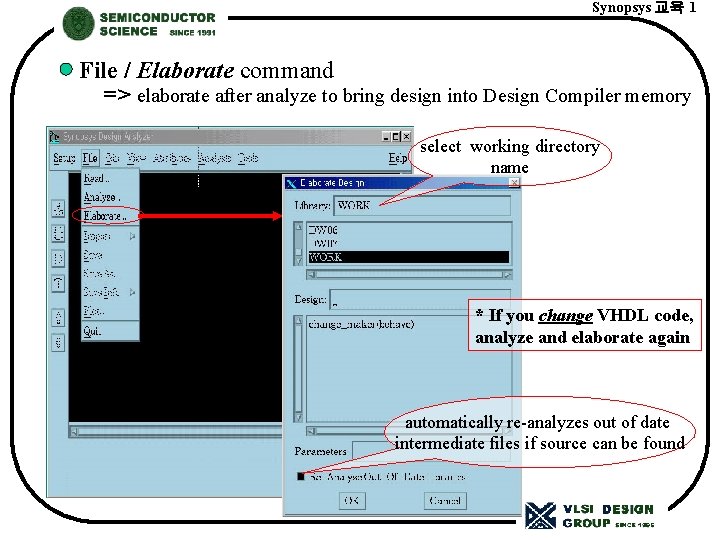

Synopsys 교육 1 File / Elaborate command => elaborate after analyze to bring design into Design Compiler memory select working directory name * If you change VHDL code, analyze and elaborate again automatically re-analyzes out of date intermediate files if source can be found

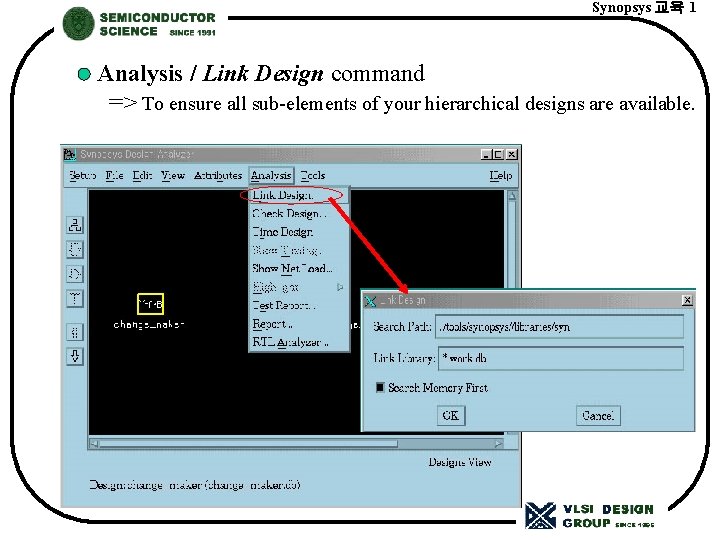

Synopsys 교육 1 Analysis / Link Design command => To ensure all sub-elements of your hierarchical designs are available.

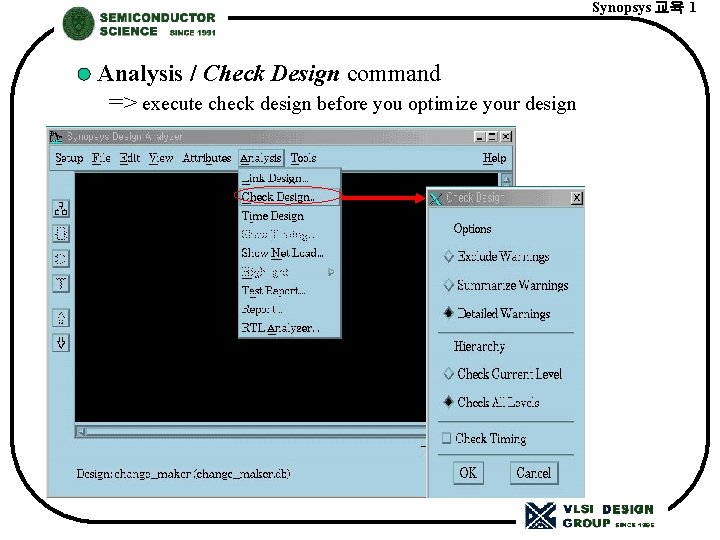

Synopsys 교육 1 Analysis / Check Design command => execute check design before you optimize your design

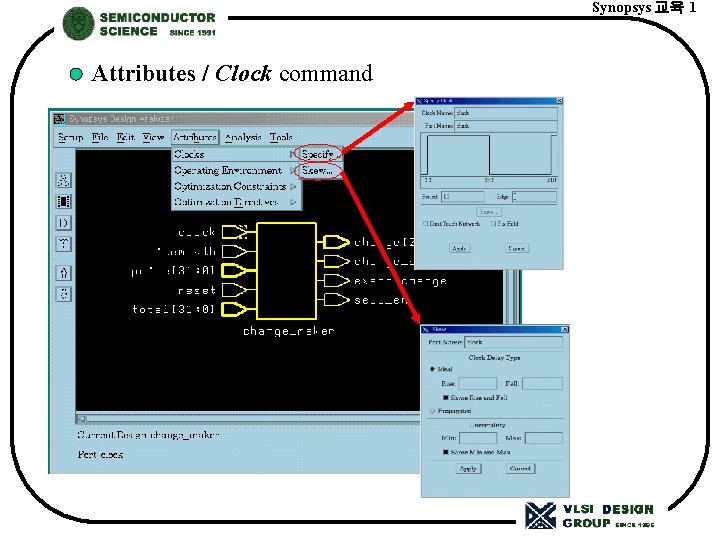

Synopsys 교육 1 Attributes / Clock command

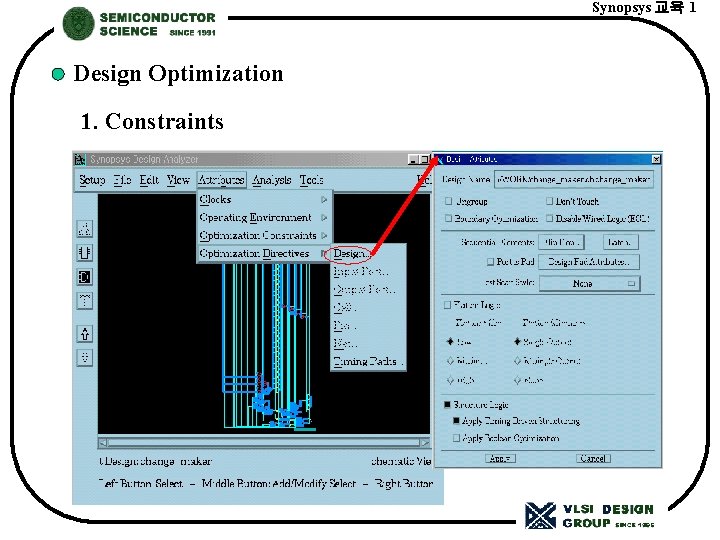

Synopsys 교육 1 Design Optimization 1. Constraints

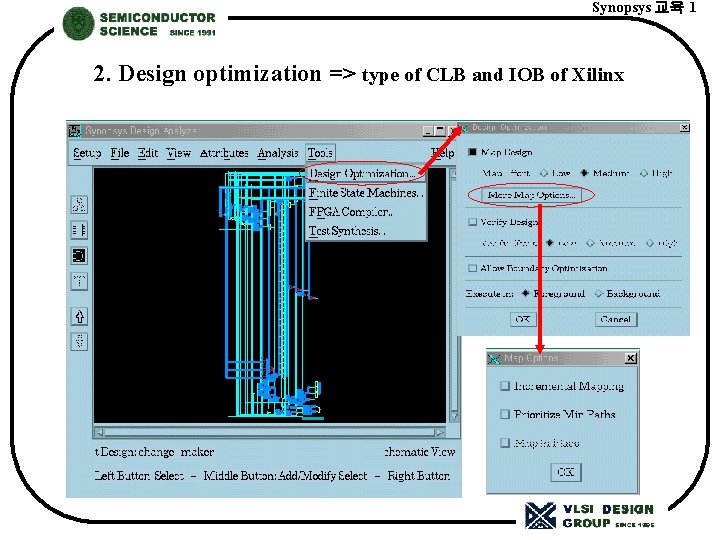

Synopsys 교육 1 2. Design optimization => type of CLB and IOB of Xilinx

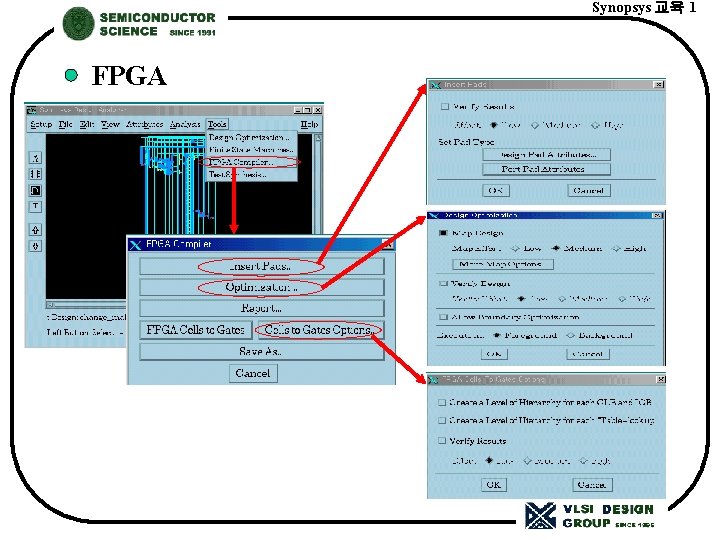

Synopsys 교육 1 FPGA

- Slides: 44