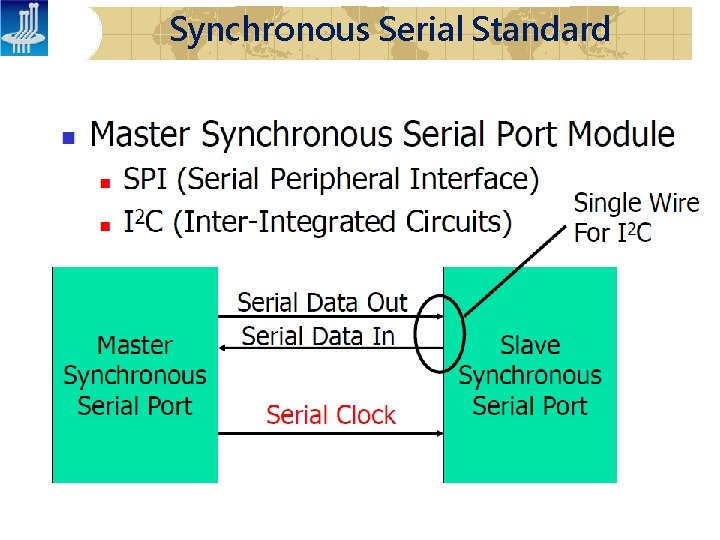

Synchronous Serial Standard Asynchronous Serial Standard Universal SynchronousAsynchronous

- Slides: 27

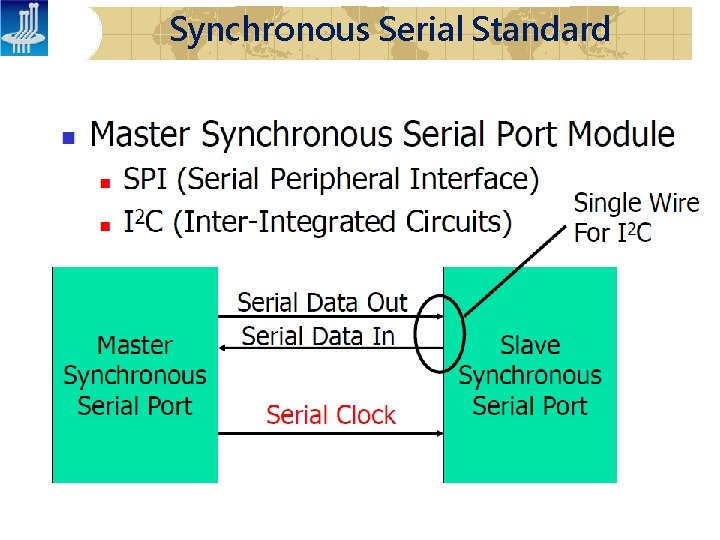

Synchronous Serial Standard

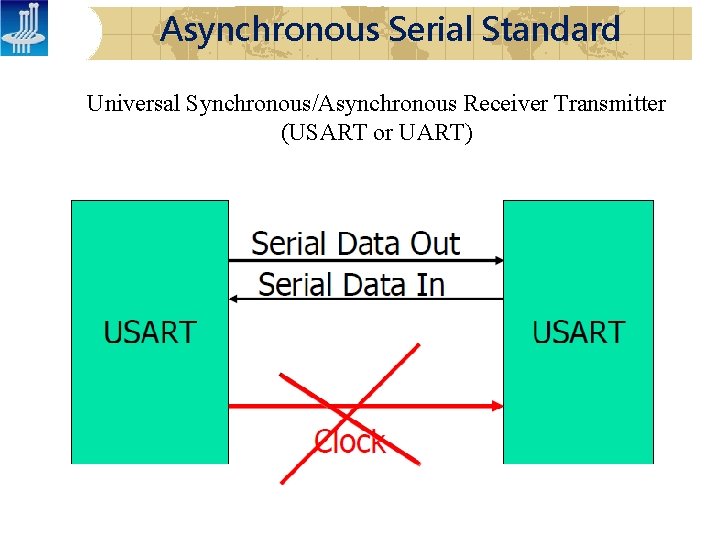

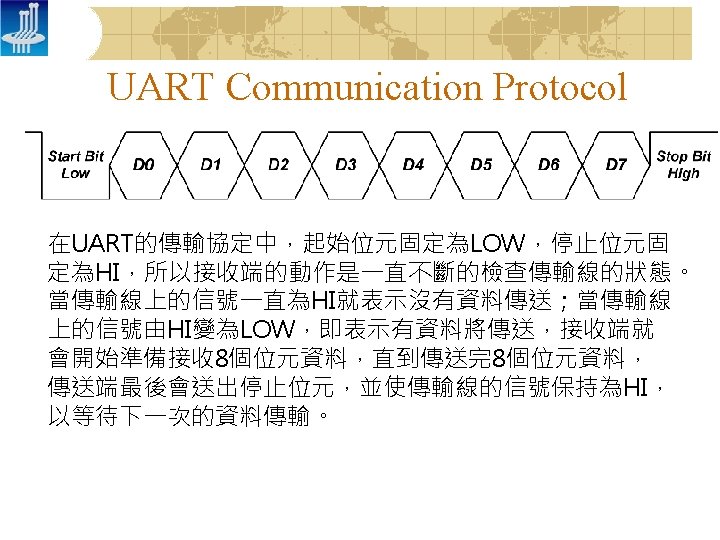

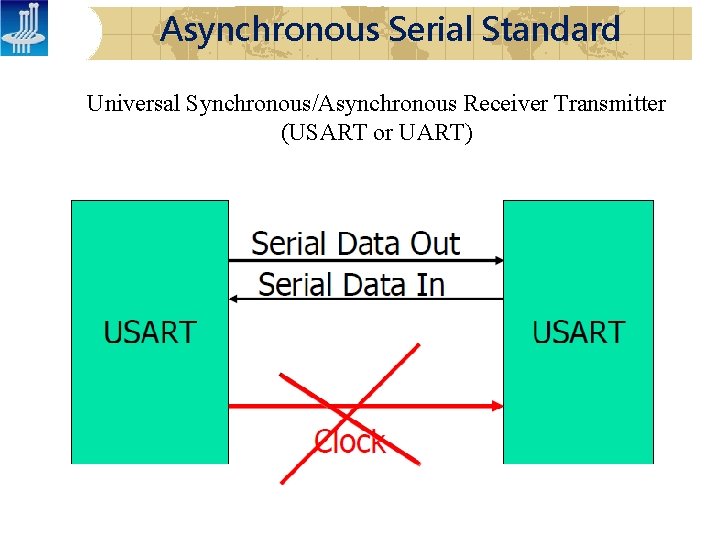

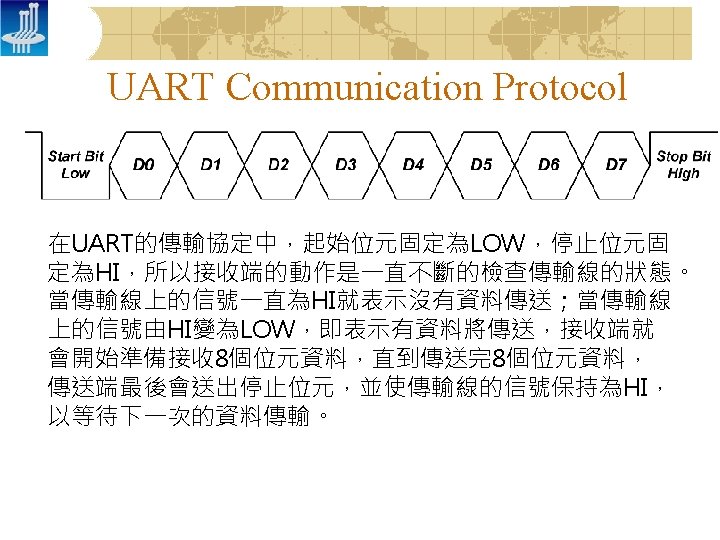

Asynchronous Serial Standard Universal Synchronous/Asynchronous Receiver Transmitter (USART or UART)

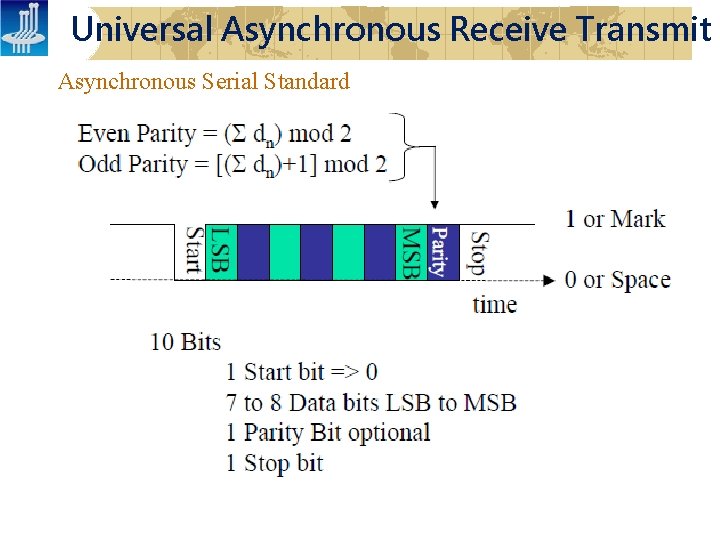

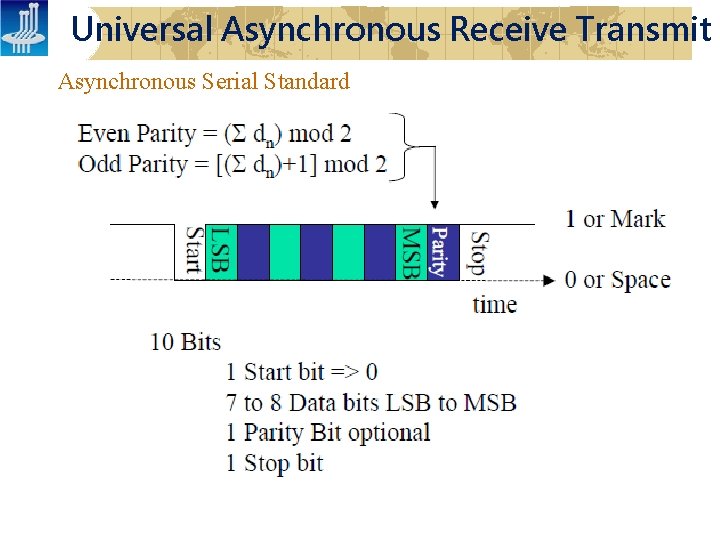

Universal Asynchronous Receive Transmit Asynchronous Serial Standard

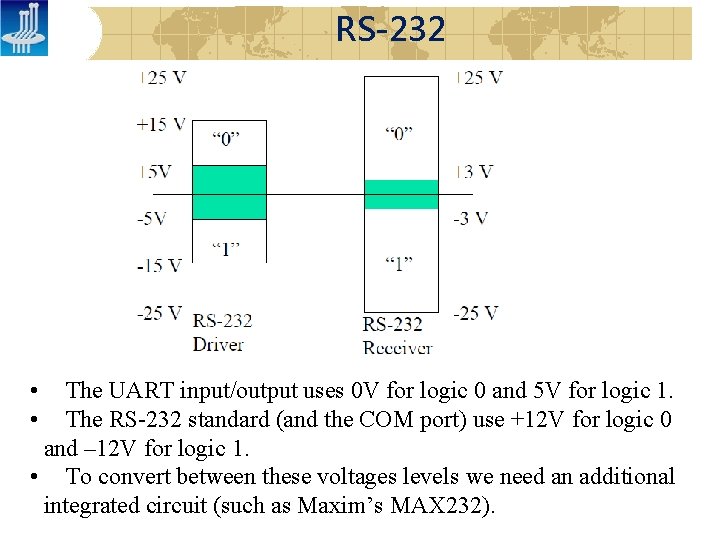

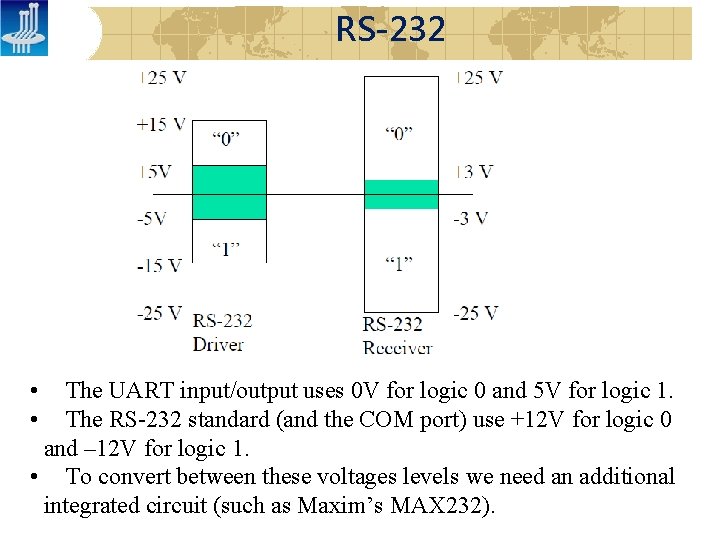

RS-232 • • The UART input/output uses 0 V for logic 0 and 5 V for logic 1. The RS-232 standard (and the COM port) use +12 V for logic 0 and – 12 V for logic 1. • To convert between these voltages levels we need an additional integrated circuit (such as Maxim’s MAX 232).

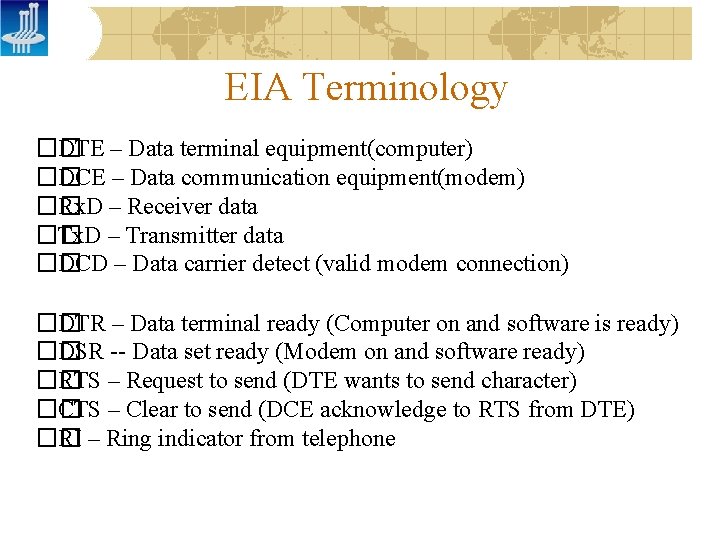

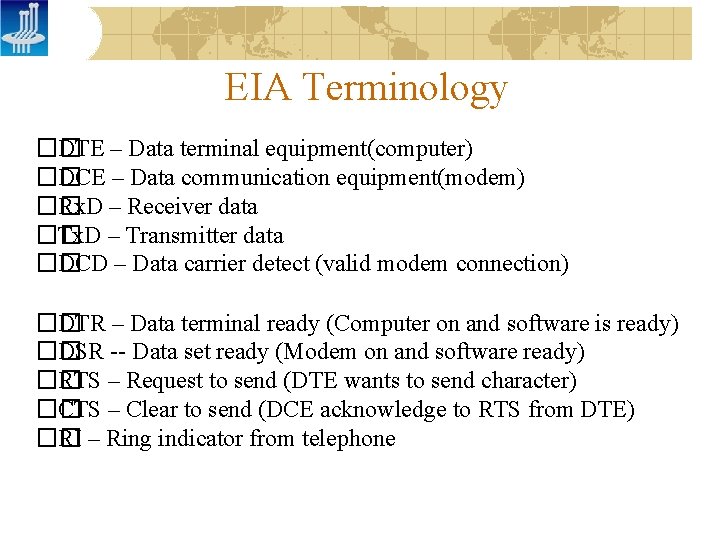

EIA Terminology �� DTE – Data terminal equipment(computer) �� DCE – Data communication equipment(modem) �� Rx. D – Receiver data �� Tx. D – Transmitter data �� DCD – Data carrier detect (valid modem connection) �� DTR – Data terminal ready (Computer on and software is ready) �� DSR -- Data set ready (Modem on and software ready) �� RTS – Request to send (DTE wants to send character) �� CTS – Clear to send (DCE acknowledge to RTS from DTE) �� RI – Ring indicator from telephone

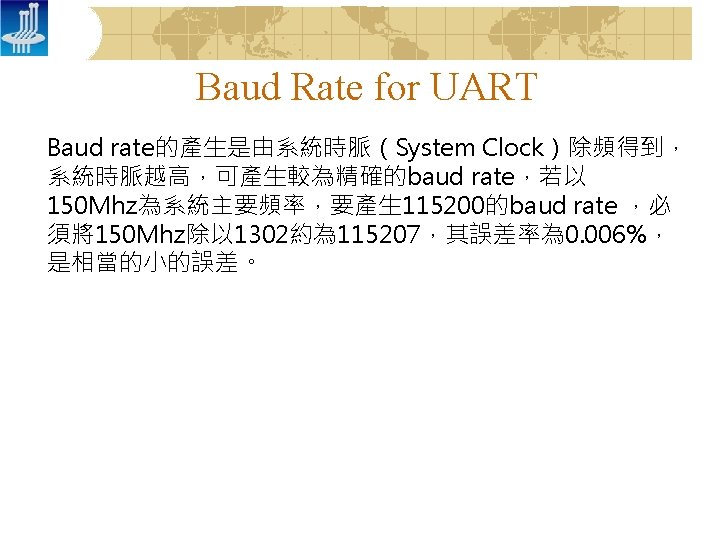

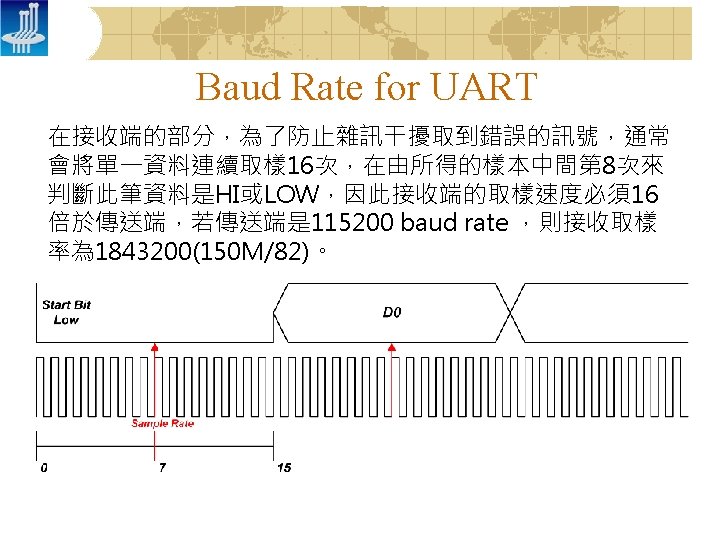

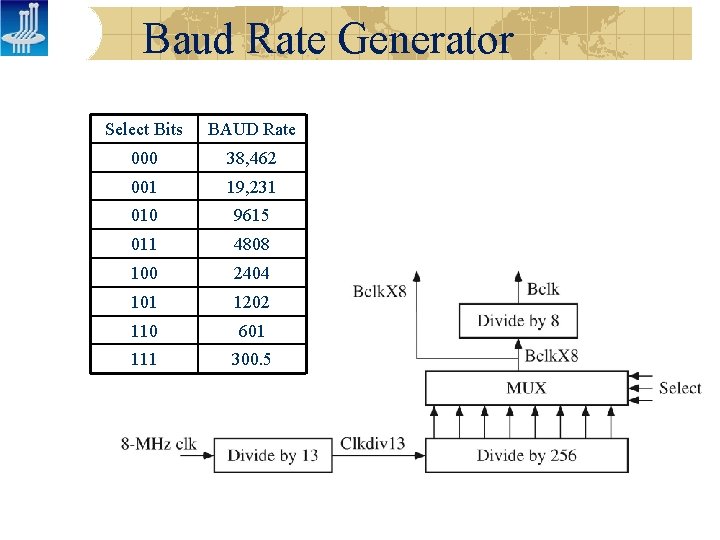

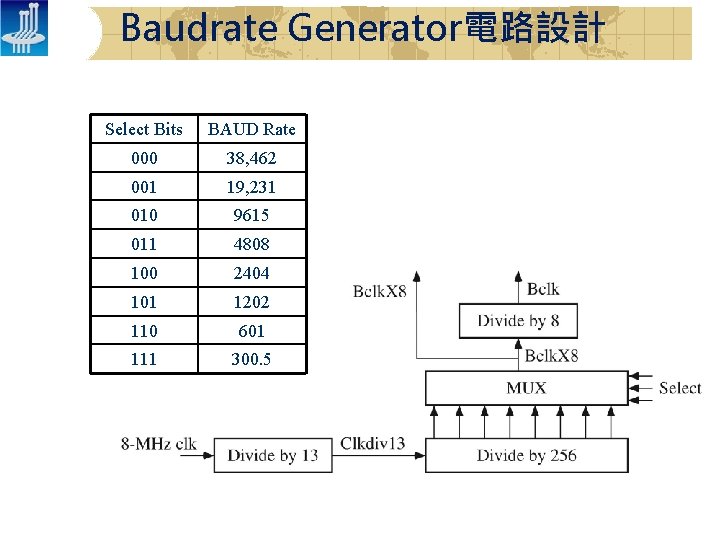

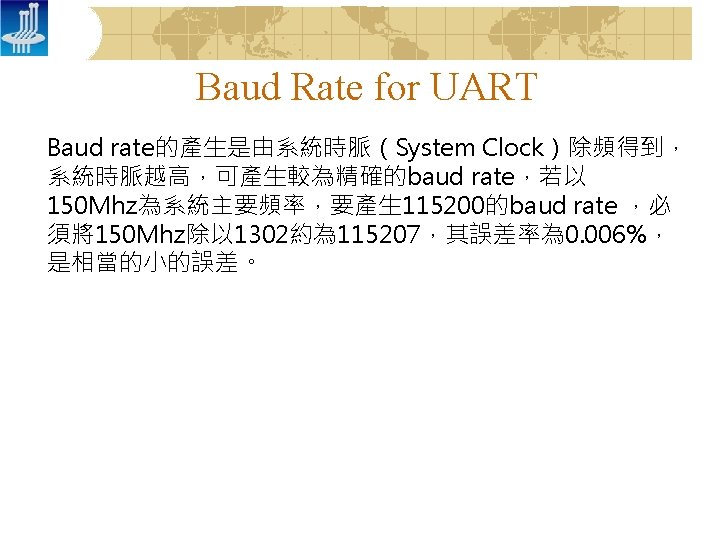

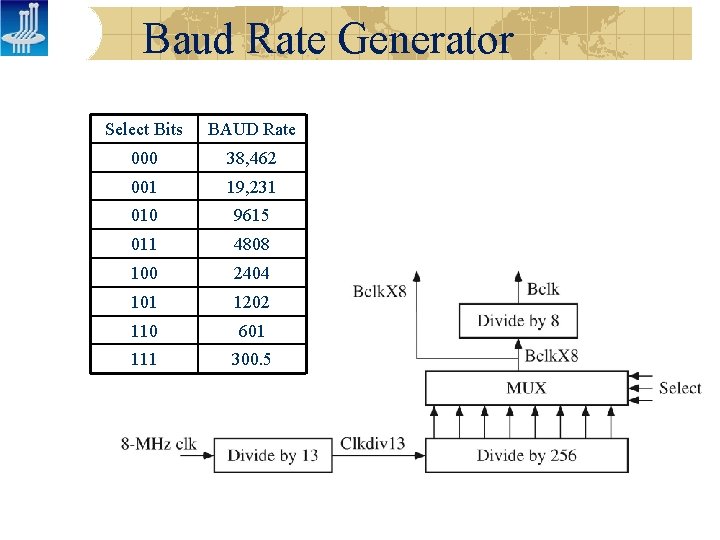

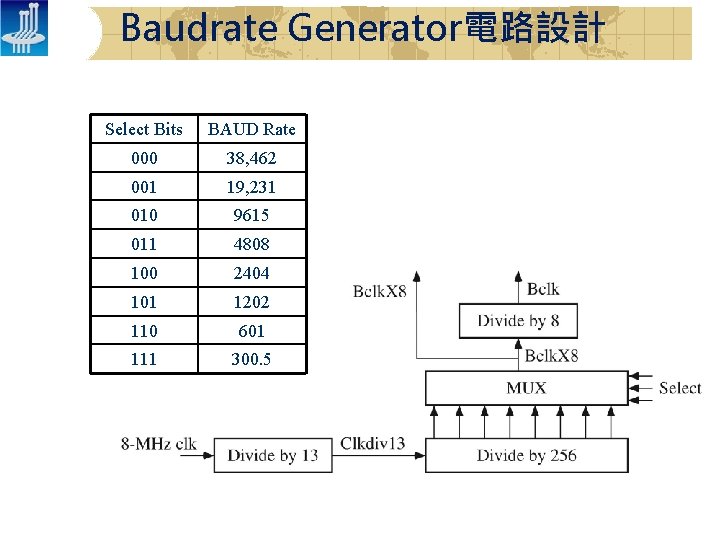

Baud Rate Generator Select Bits BAUD Rate 000 38, 462 001 19, 231 010 9615 011 4808 100 2404 101 1202 110 601 111 300. 5

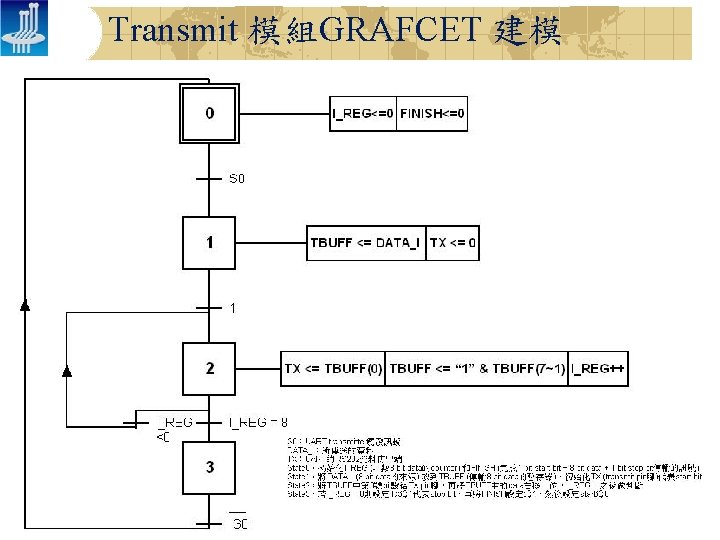

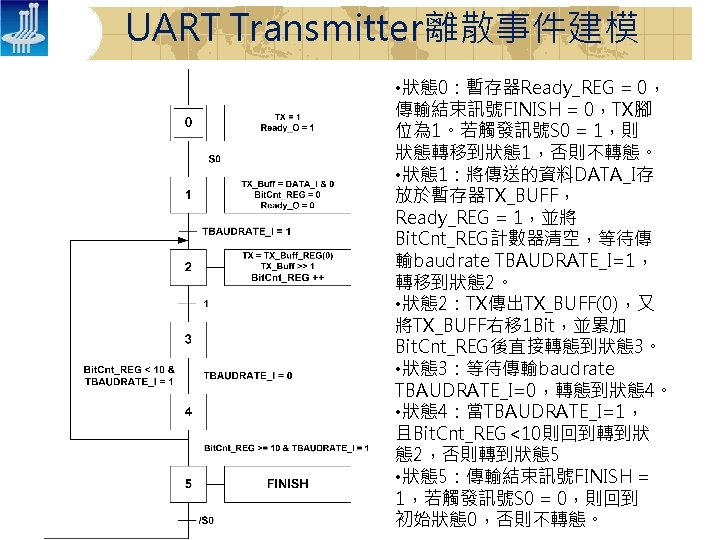

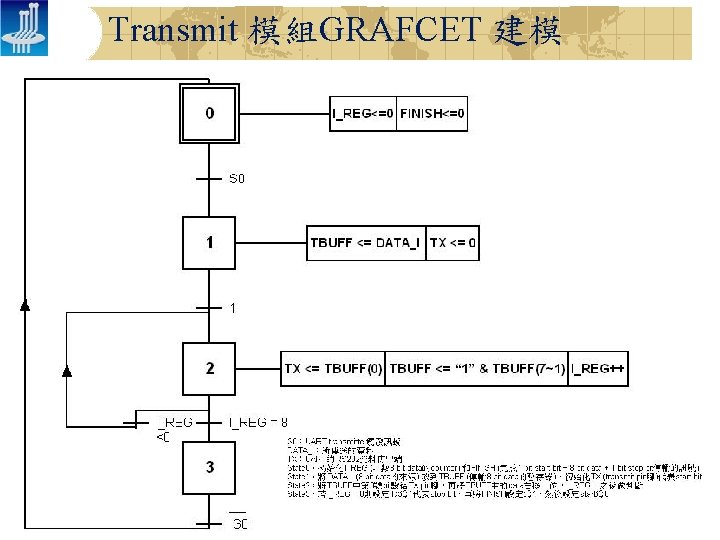

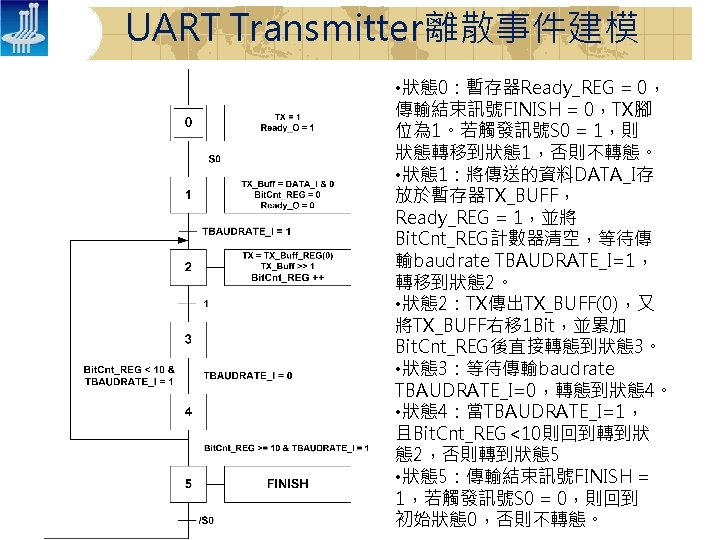

Transmit 模組GRAFCET 建模

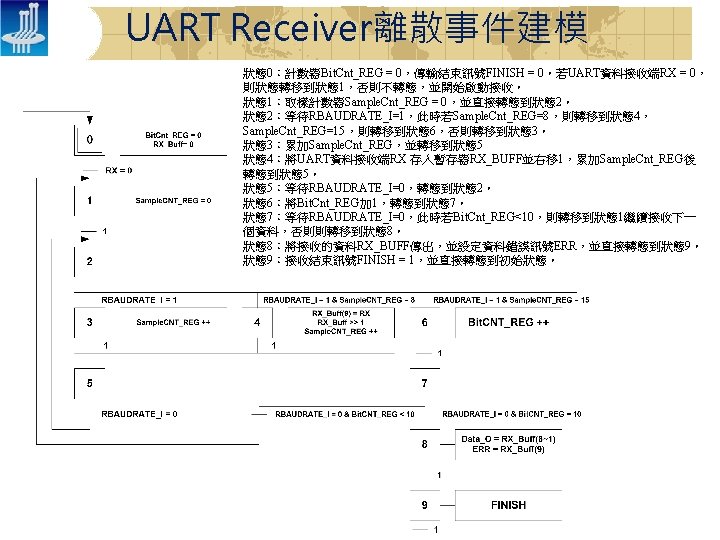

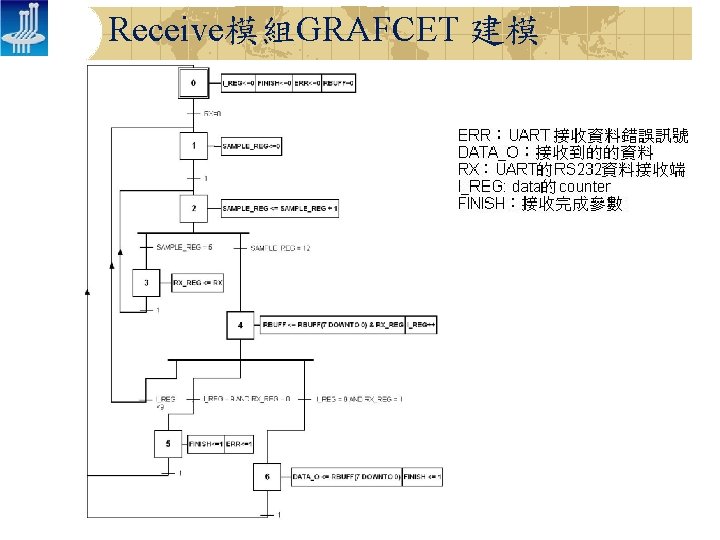

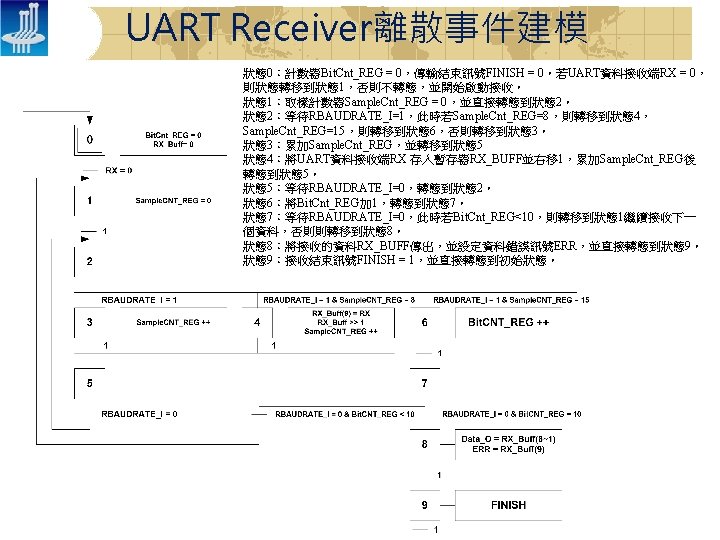

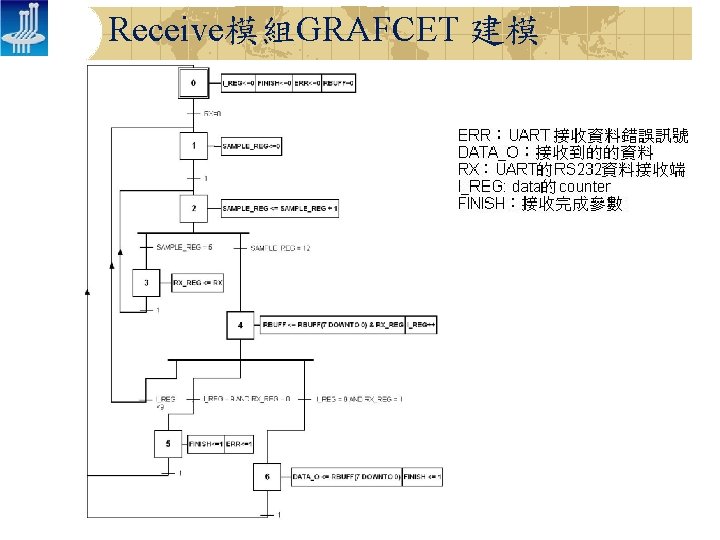

Receive模組GRAFCET 建模

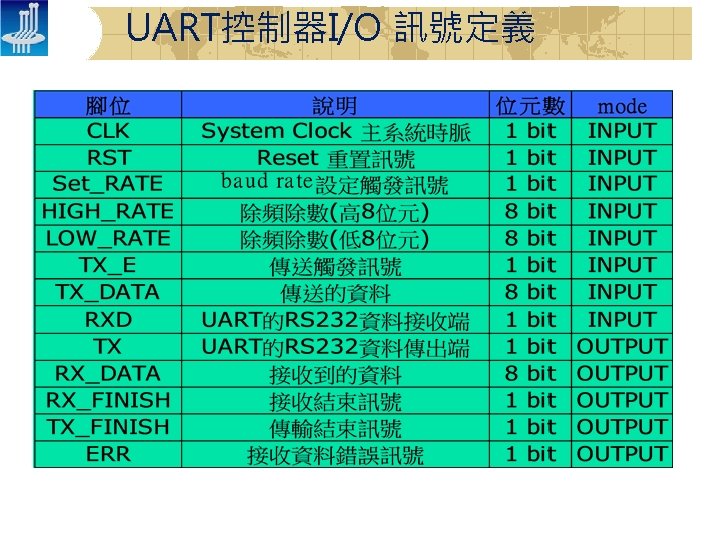

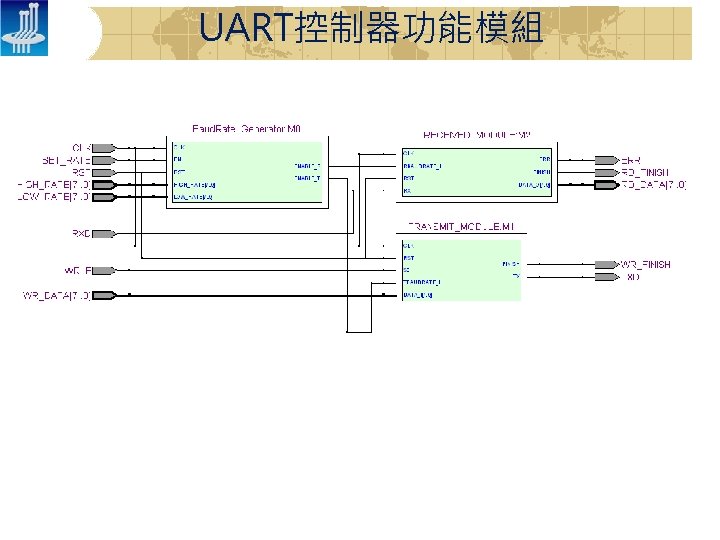

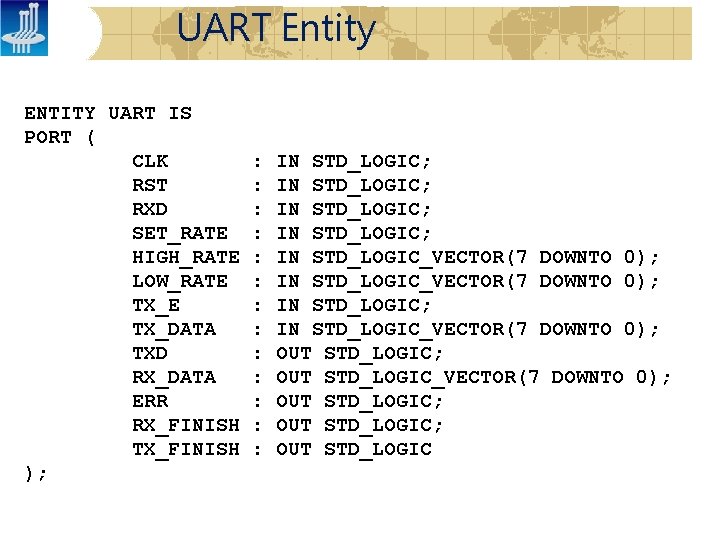

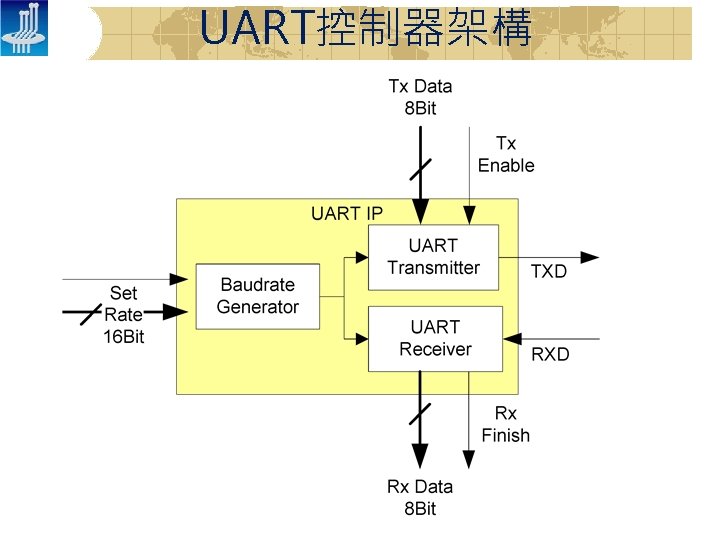

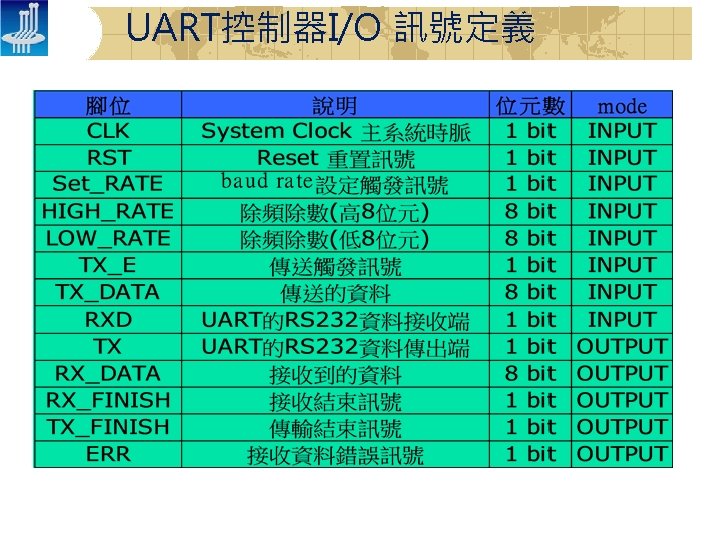

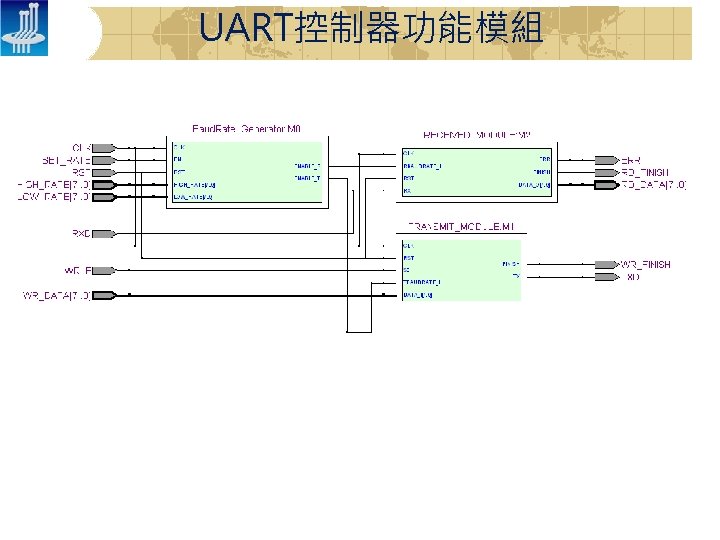

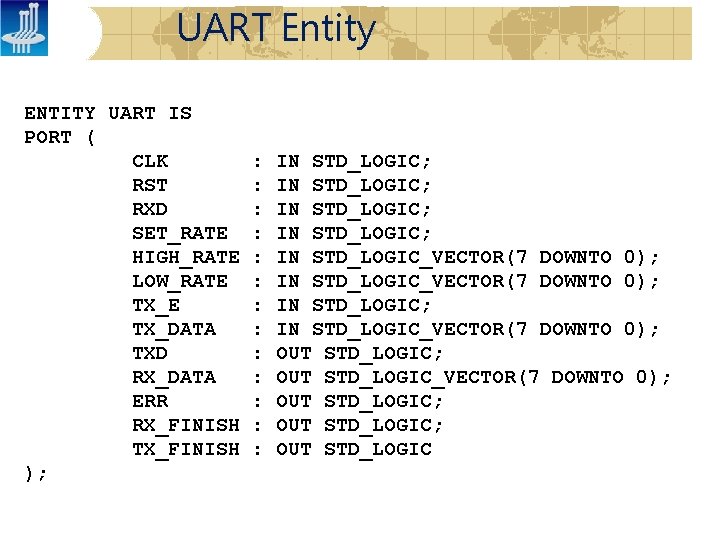

UART Entity ENTITY UART IS PORT ( CLK RST RXD SET_RATE HIGH_RATE LOW_RATE TX_DATA TXD RX_DATA ERR RX_FINISH TX_FINISH ); : : : : IN STD_LOGIC; IN STD_LOGIC_VECTOR(7 DOWNTO 0); IN STD_LOGIC; IN STD_LOGIC_VECTOR(7 DOWNTO 0); OUT STD_LOGIC; OUT STD_LOGIC

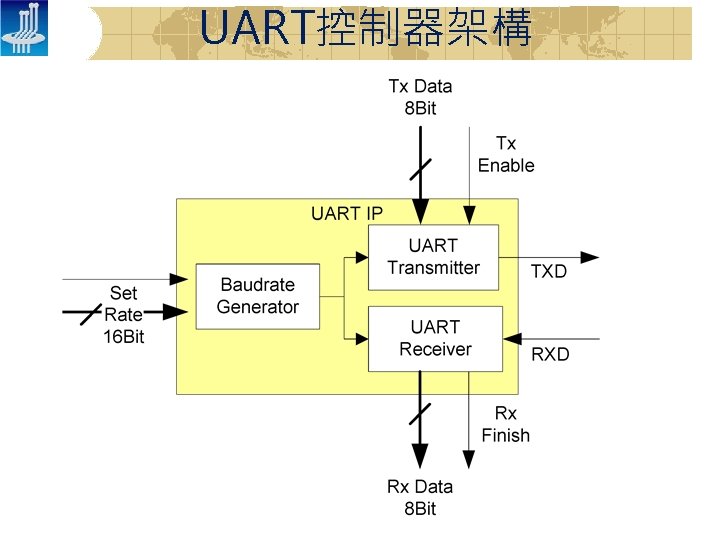

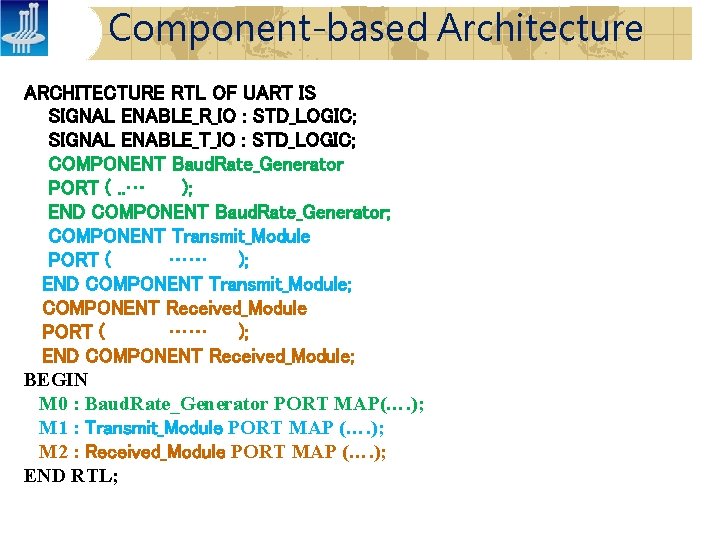

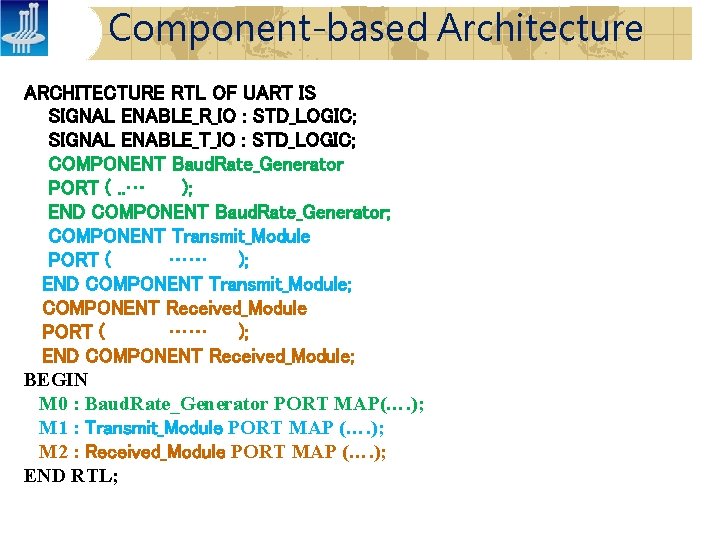

Component-based Architecture ARCHITECTURE RTL OF UART IS SIGNAL ENABLE_R_IO : STD_LOGIC; SIGNAL ENABLE_T_IO : STD_LOGIC; COMPONENT Baud. Rate_Generator PORT (. . … ); END COMPONENT Baud. Rate_Generator; COMPONENT Transmit_Module PORT ( …… ); END COMPONENT Transmit_Module; COMPONENT Received_Module PORT ( …… ); END COMPONENT Received_Module; BEGIN M 0 : Baud. Rate_Generator PORT MAP(…. ); M 1 : Transmit_Module PORT MAP (…. ); M 2 : Received_Module PORT MAP (…. ); END RTL;

Baudrate Generator電路設計 Select Bits BAUD Rate 000 38, 462 001 19, 231 010 9615 011 4808 100 2404 101 1202 110 601 111 300. 5

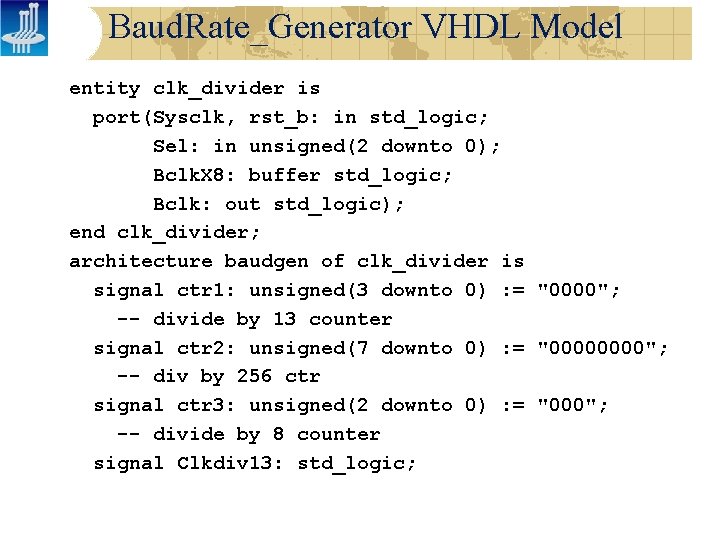

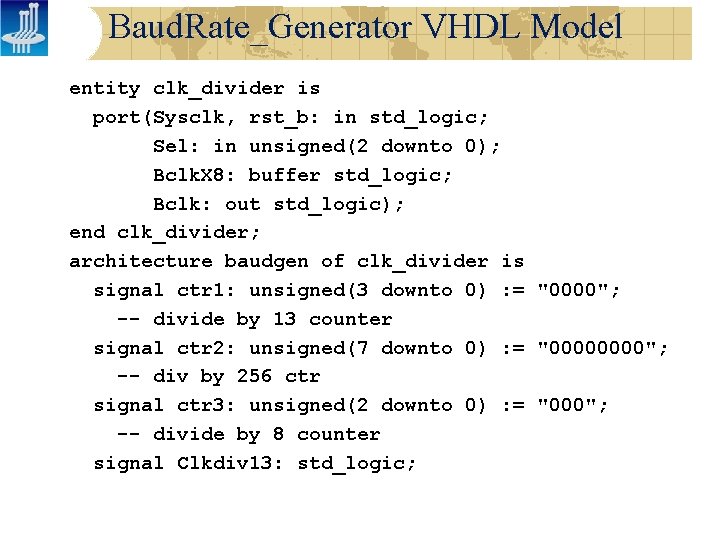

Baud. Rate_Generator VHDL Model entity clk_divider is port(Sysclk, rst_b: in std_logic; Sel: in unsigned(2 downto 0); Bclk. X 8: buffer std_logic; Bclk: out std_logic); end clk_divider; architecture baudgen of clk_divider is signal ctr 1: unsigned(3 downto 0) : = "0000"; -- divide by 13 counter signal ctr 2: unsigned(7 downto 0) : = "0000"; -- div by 256 ctr signal ctr 3: unsigned(2 downto 0) : = "000"; -- divide by 8 counter signal Clkdiv 13: std_logic;

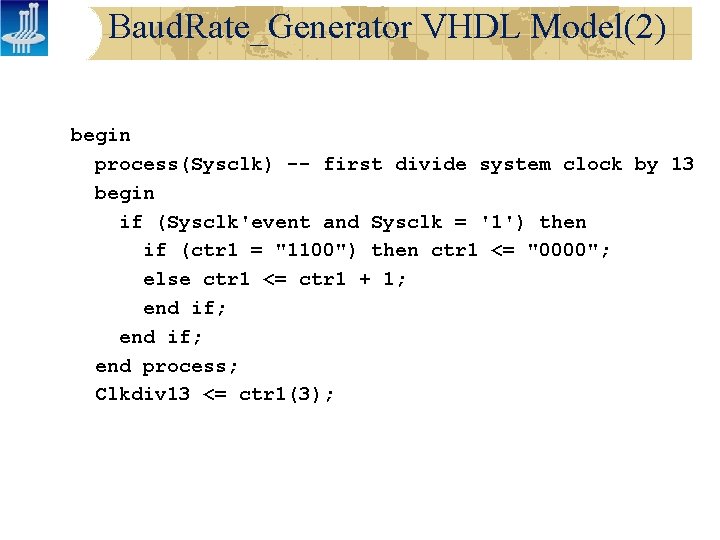

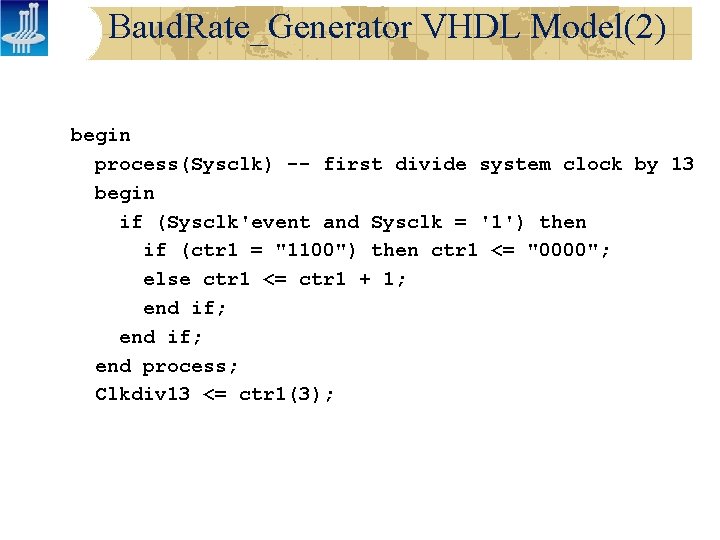

Baud. Rate_Generator VHDL Model(2) begin process(Sysclk) -- first divide system clock by 13 begin if (Sysclk'event and Sysclk = '1') then if (ctr 1 = "1100") then ctr 1 <= "0000"; else ctr 1 <= ctr 1 + 1; end if; end process; Clkdiv 13 <= ctr 1(3);

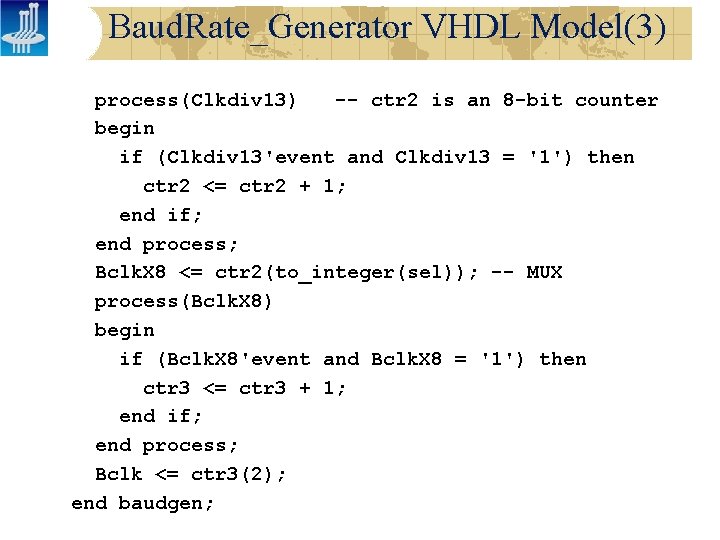

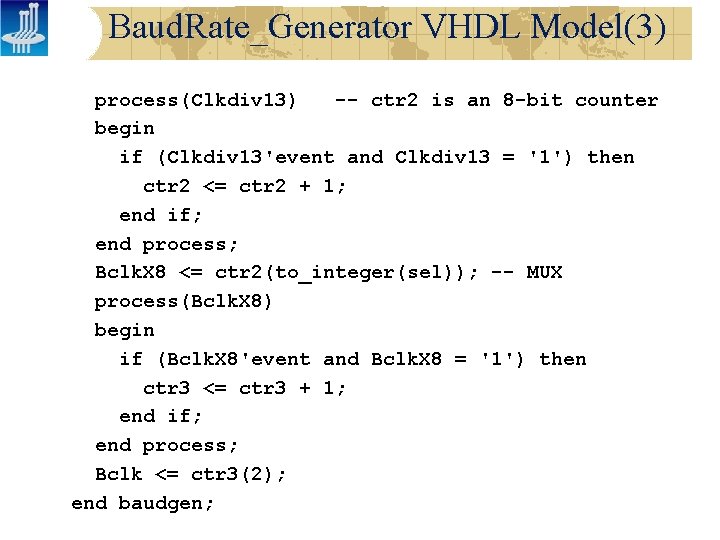

Baud. Rate_Generator VHDL Model(3) process(Clkdiv 13) -- ctr 2 is an 8 -bit counter begin if (Clkdiv 13'event and Clkdiv 13 = '1') then ctr 2 <= ctr 2 + 1; end if; end process; Bclk. X 8 <= ctr 2(to_integer(sel)); -- MUX process(Bclk. X 8) begin if (Bclk. X 8'event and Bclk. X 8 = '1') then ctr 3 <= ctr 3 + 1; end if; end process; Bclk <= ctr 3(2); end baudgen;

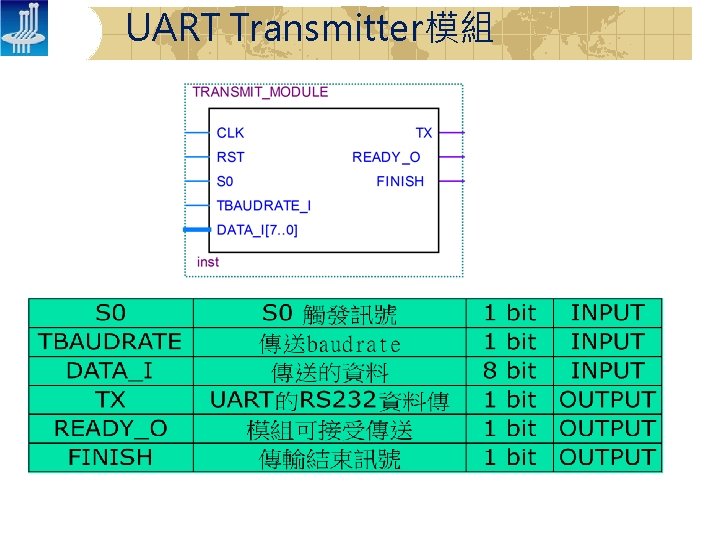

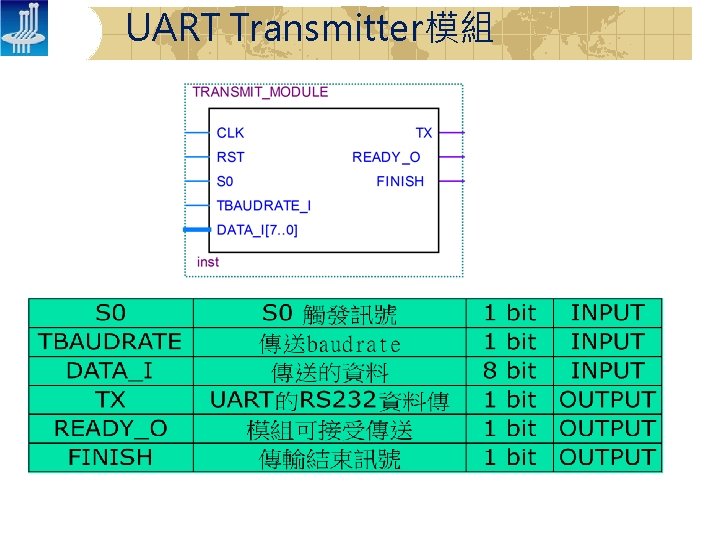

UART Transmitter模組

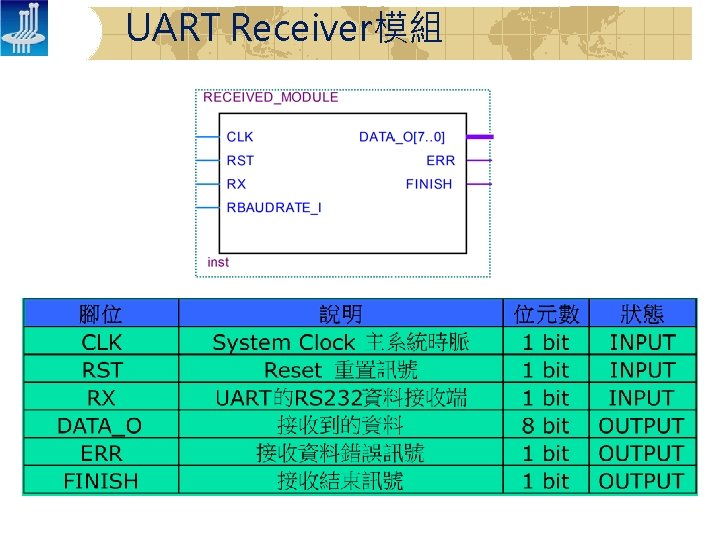

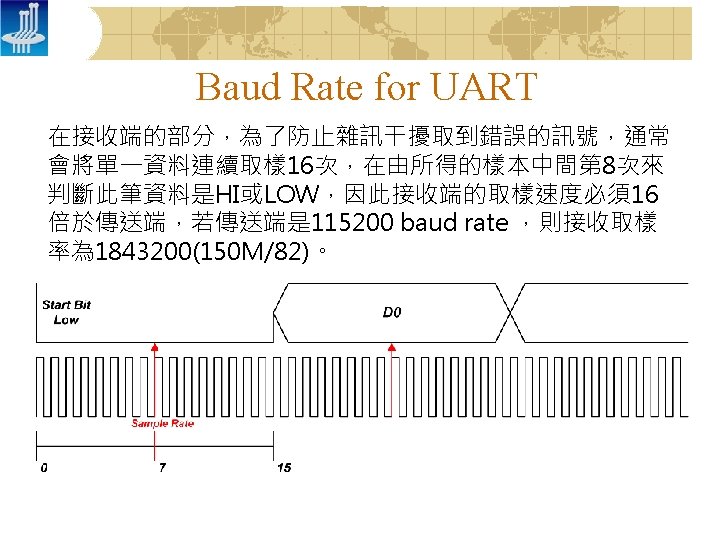

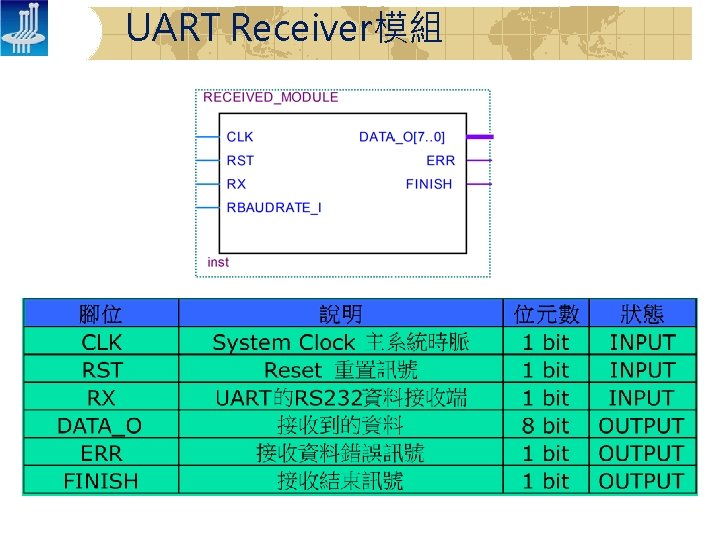

UART Receiver模組