Synchronizer failure and Metastability Bistable element January 31

Synchronizer failure and Metastability

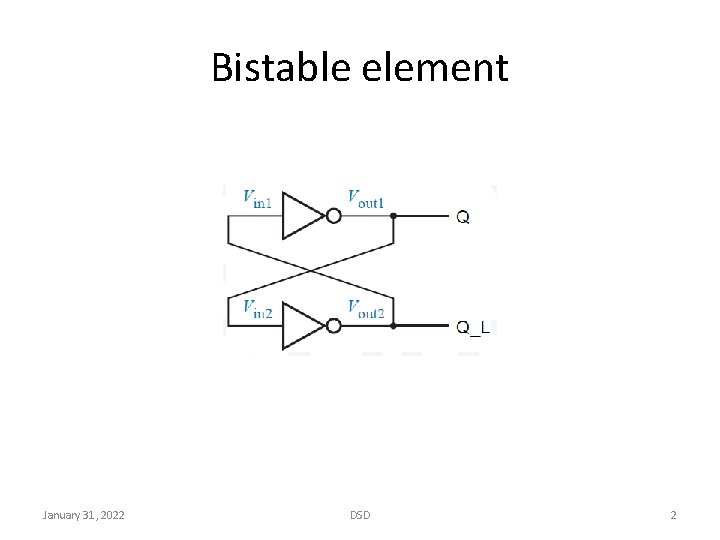

Bistable element January 31, 2022 DSD 2

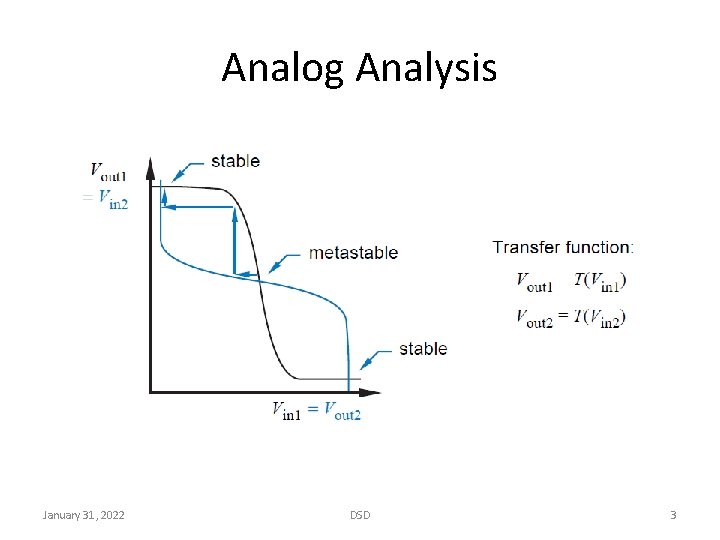

Analog Analysis January 31, 2022 DSD 3

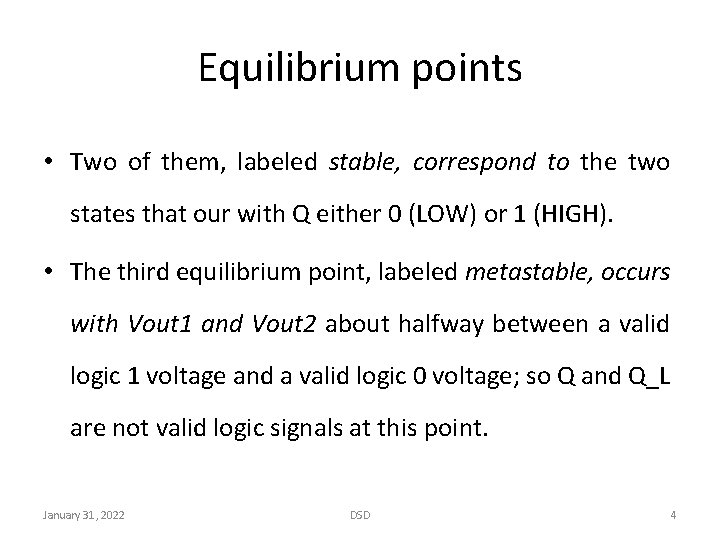

Equilibrium points • Two of them, labeled stable, correspond to the two states that our with Q either 0 (LOW) or 1 (HIGH). • The third equilibrium point, labeled metastable, occurs with Vout 1 and Vout 2 about halfway between a valid logic 1 voltage and a valid logic 0 voltage; so Q and Q_L are not valid logic signals at this point. January 31, 2022 DSD 4

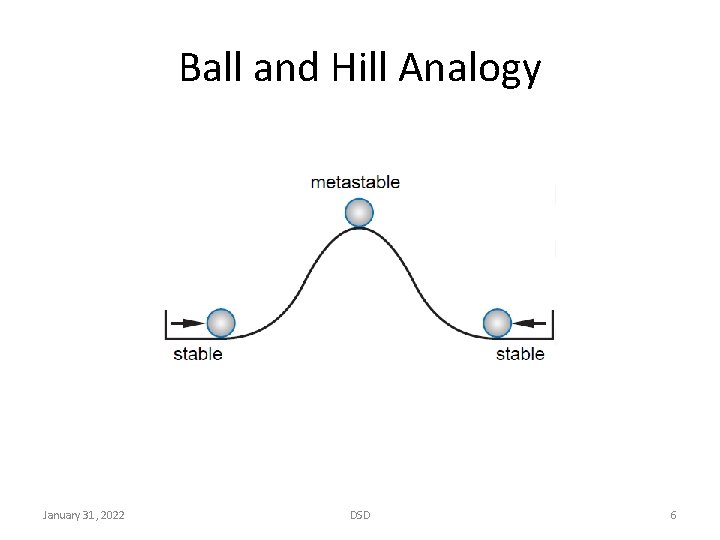

Metastable state • It is not truly stable, because random noise will tend to drive a circuit that is operating at the metastable point toward one of the stable operating points. January 31, 2022 DSD 5

Ball and Hill Analogy January 31, 2022 DSD 6

Asynchronous inputs • Asynchronous input signals that are not synchronized with the system clock. • Usual asynchronous inputs: Interrupts , Status flags (to signal that a resource has become available) etc. January 31, 2022 DSD 7

Asynchronous inputs • Such inputs normally change slowly compared to the system clock frequency, and need not be recognized at a particular clock tick. • If a transition is missed at one clock tick, it can always be detected at the next one. January 31, 2022 DSD 8

Asynchronous inputs • Ignoring the problem of metastability, it is easy to build a synchronizer, a circuit that samples an asynchronous input and produces an output that meets the setup and hold times required in a synchronous system. January 31, 2022 DSD 9

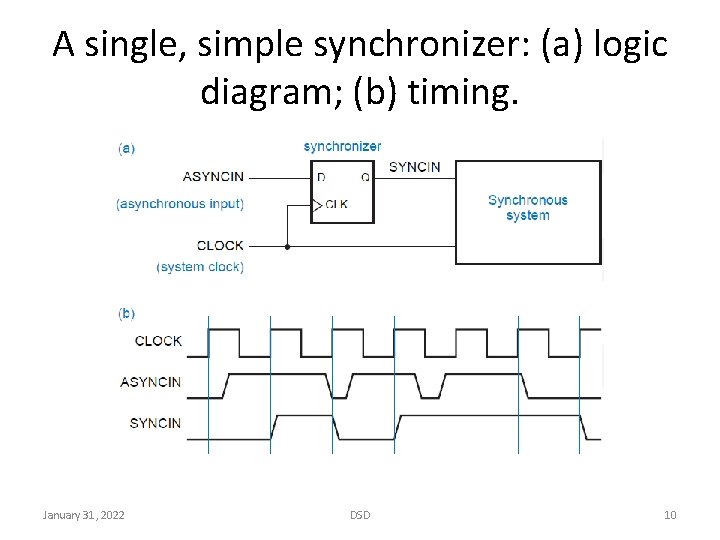

A single, simple synchronizer: (a) logic diagram; (b) timing. January 31, 2022 DSD 10

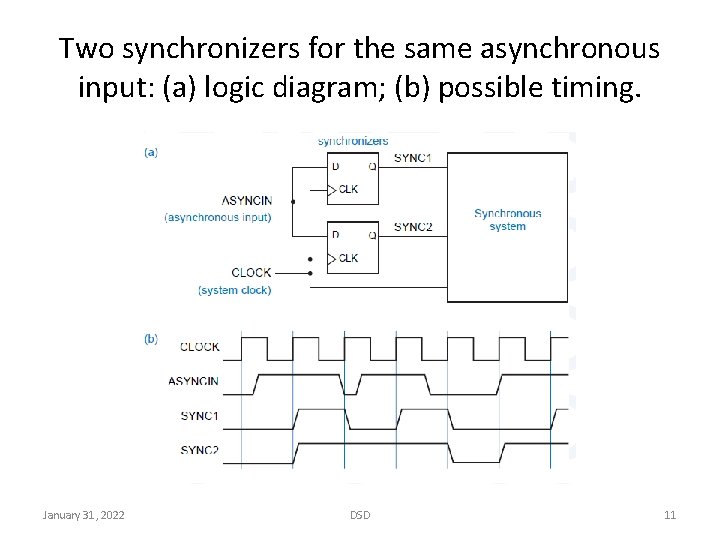

Two synchronizers for the same asynchronous input: (a) logic diagram; (b) possible timing. January 31, 2022 DSD 11

An asynchronous input driving two synchronizers through combinational logic January 31, 2022 DSD 12

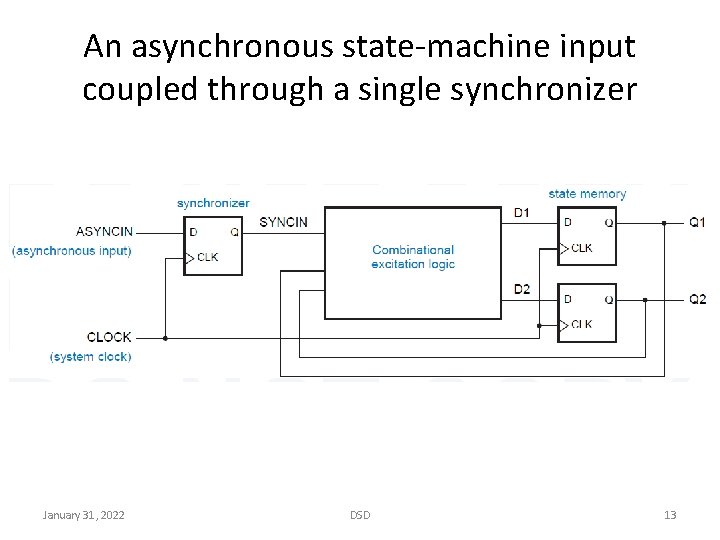

An asynchronous state-machine input coupled through a single synchronizer January 31, 2022 DSD 13

Synchronizer failure • Synchronizer failure is said to occur if a system uses a synchronizer output while the output is still in the metastable state. January 31, 2022 DSD 14

Synchronizer failure • The way to avoid synchronizer failure is to ensure that the system waits “long enough” before using a synchronizer’s output, “long enough” so that the mean time between synchronizer failures is several orders of magnitude longer than the designer’s expected length of employment. January 31, 2022 DSD 15

There are two ways to get a flip-flop out of the metastable state: 1. Force the flip-flop into a valid logic state using input signals that meet the published specifications for minimum pulse width, setup time, and so on. 2. Wait “long enough, ” so the flip-flop comes out of metastability on its own. January 31, 2022 DSD 16

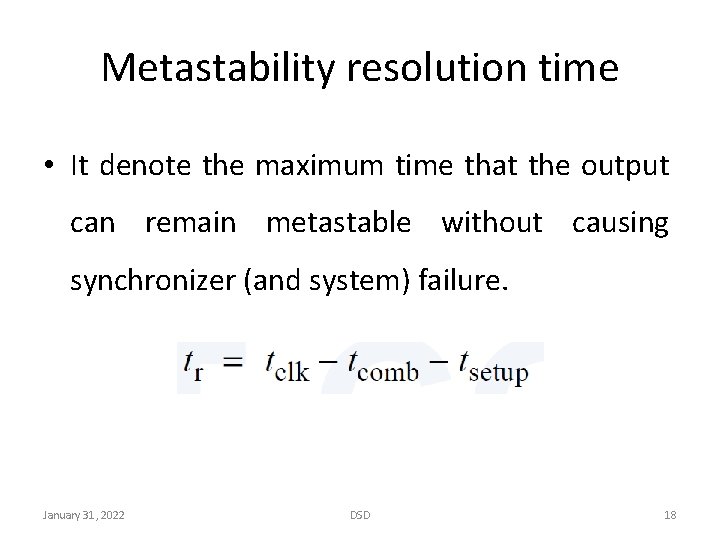

Metastability resolution time • If the setup and hold times of a D flip-flop are met, the flip-flop output settles to a new value within time tpd after the clock edge. • If they are violated, the flip-flop output may be metastable for an arbitrary length of time. January 31, 2022 DSD 17

Metastability resolution time • It denote the maximum time that the output can remain metastable without causing synchronizer (and system) failure. January 31, 2022 DSD 18

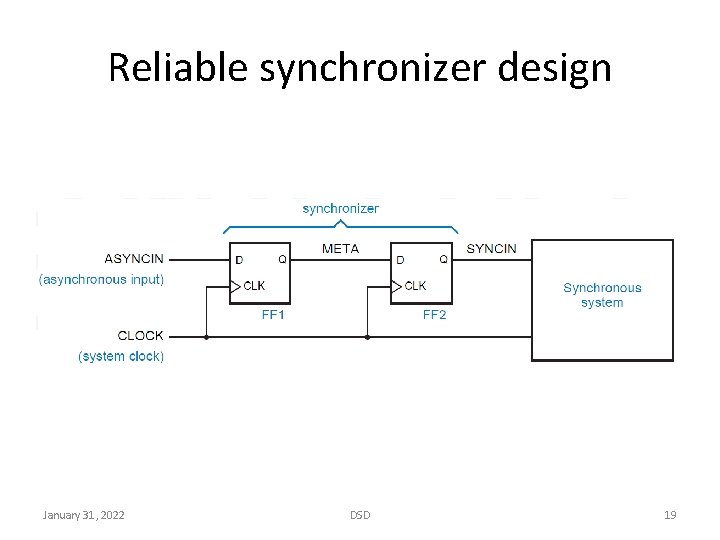

Reliable synchronizer design January 31, 2022 DSD 19

Thank You January 31, 2022 DSD 20

- Slides: 20