SYEN 3330 Digital Systems Chapter 7 Part 2

- Slides: 33

SYEN 3330 Digital Systems Chapter 7 – Part 2 SYEN 3330 Digital Systems Jung H. Kim 1

Counters SYEN 3330 Digital Systems 2

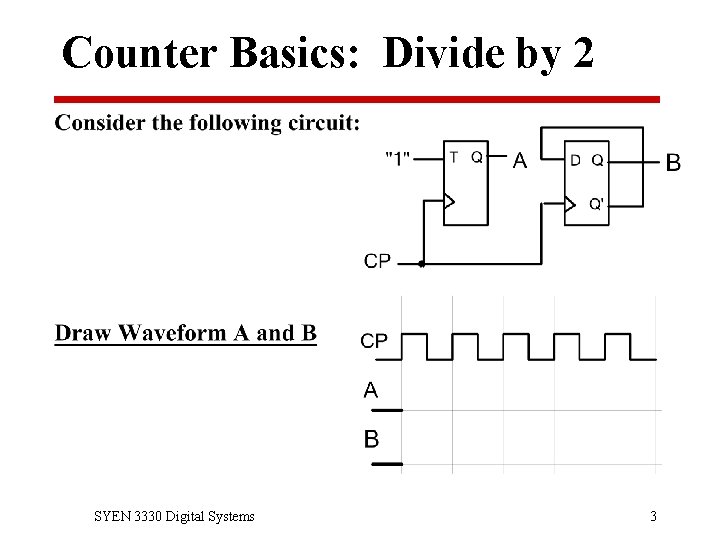

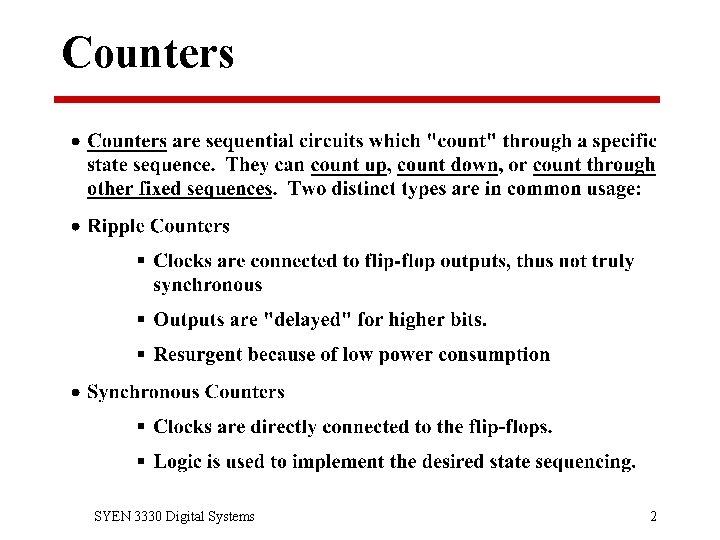

Counter Basics: Divide by 2 SYEN 3330 Digital Systems 3

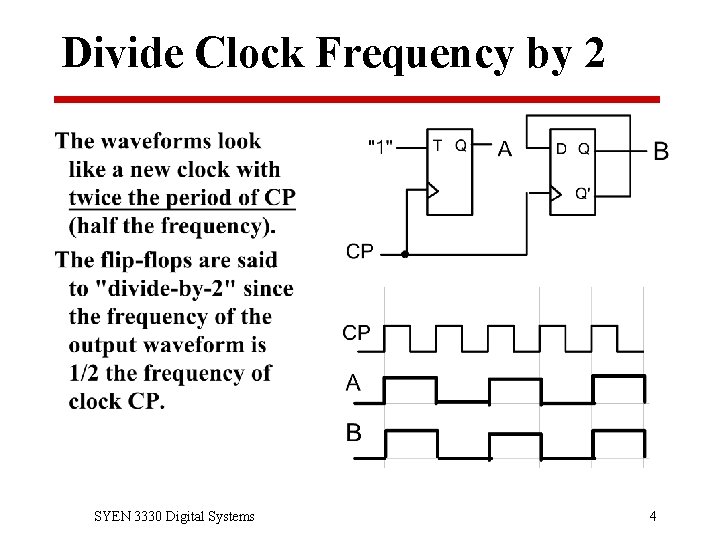

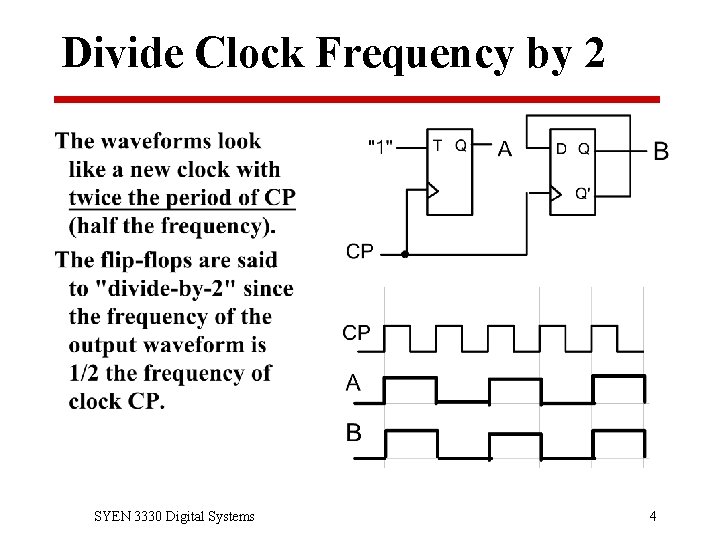

Divide Clock Frequency by 2 SYEN 3330 Digital Systems 4

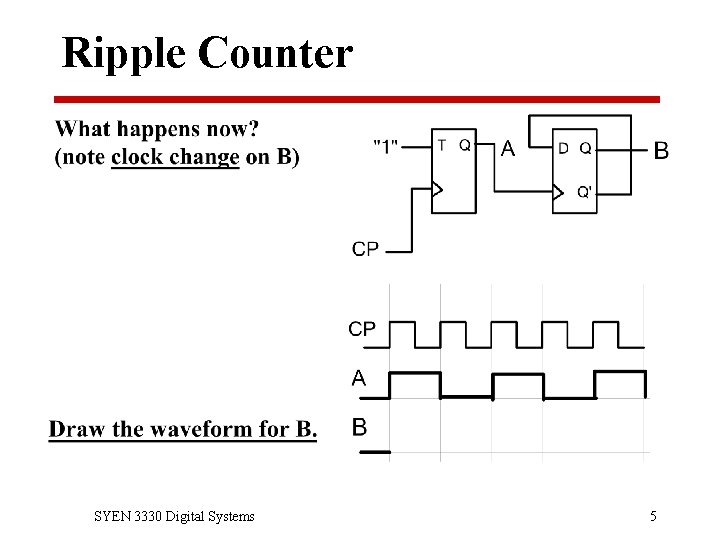

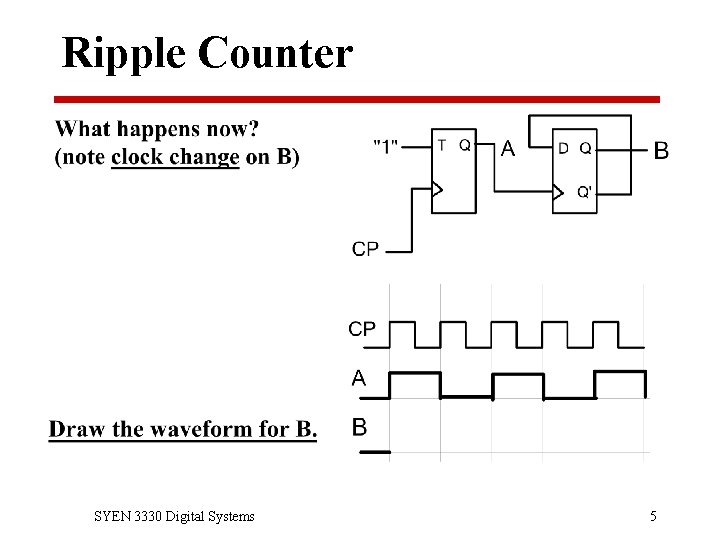

Ripple Counter SYEN 3330 Digital Systems 5

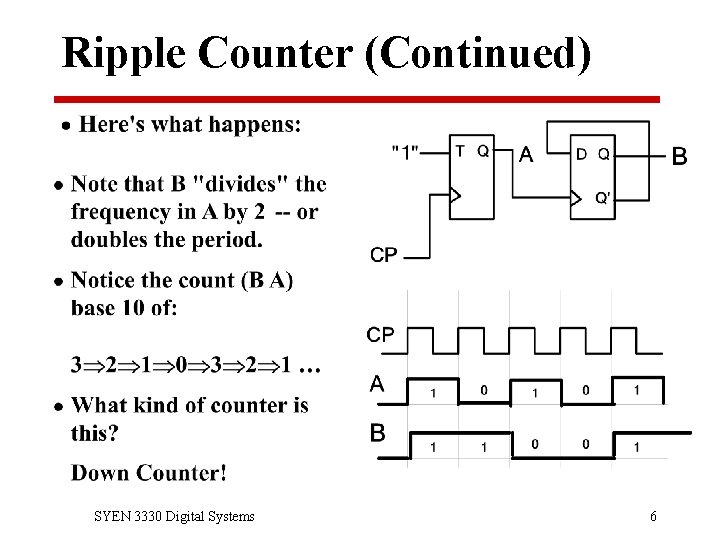

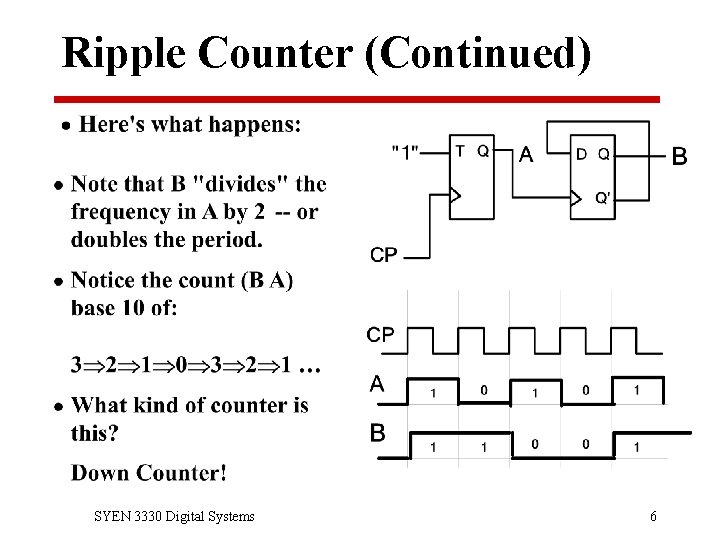

Ripple Counter (Continued) SYEN 3330 Digital Systems 6

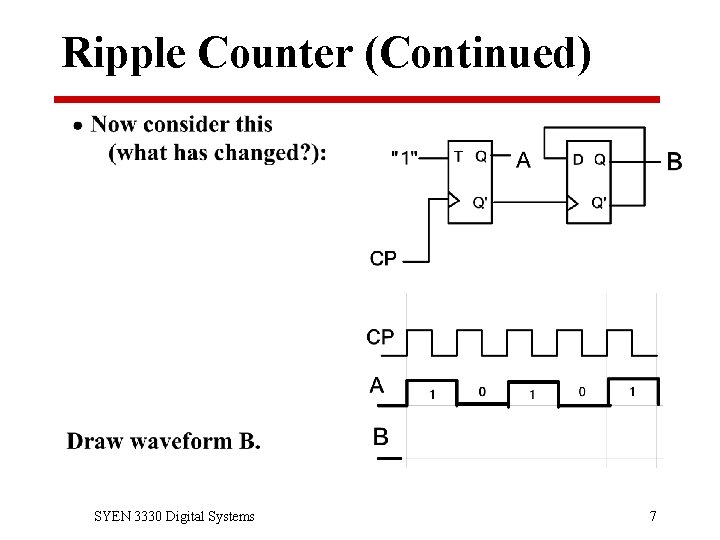

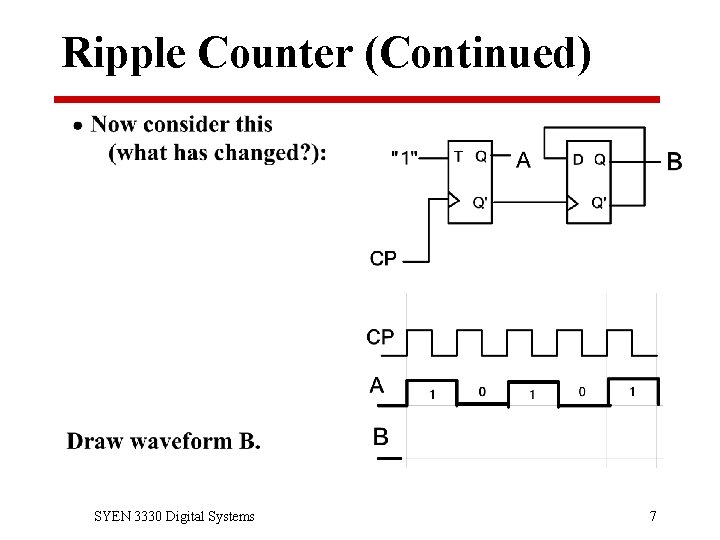

Ripple Counter (Continued) SYEN 3330 Digital Systems 7

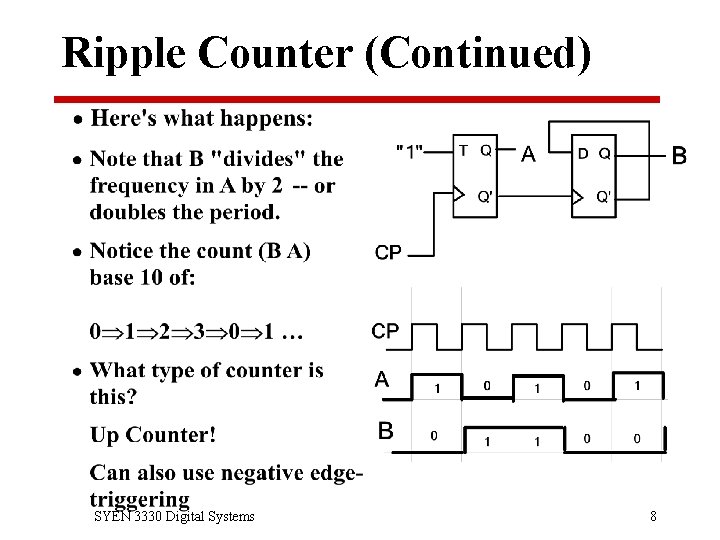

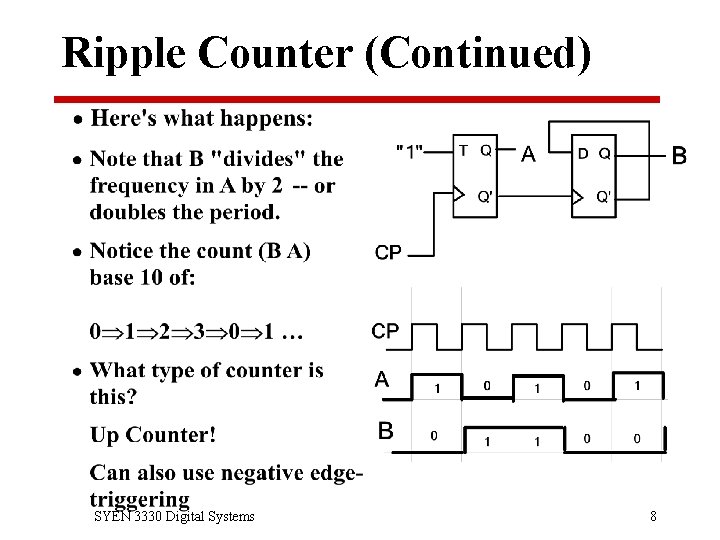

Ripple Counter (Continued) SYEN 3330 Digital Systems 8

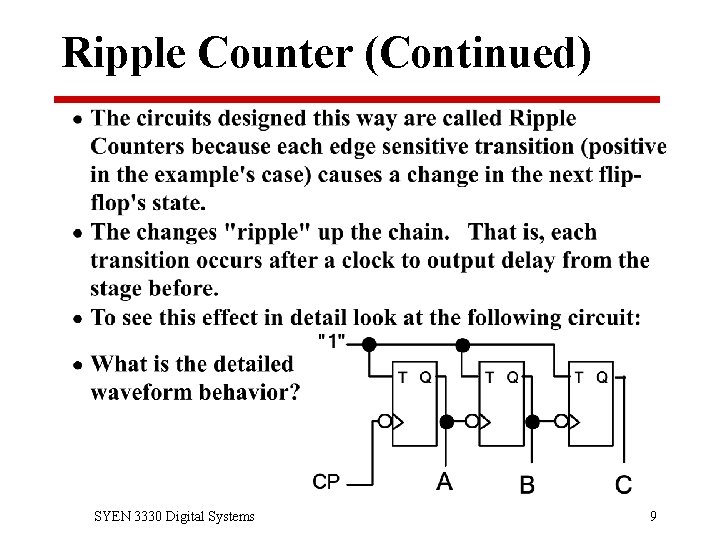

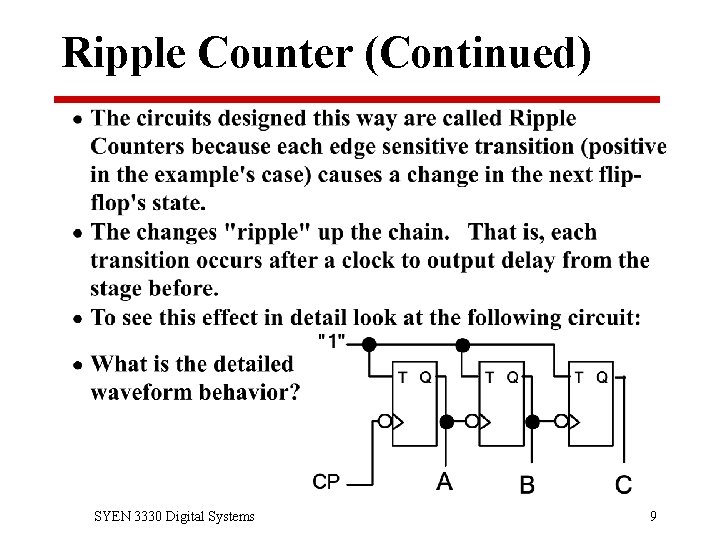

Ripple Counter (Continued) SYEN 3330 Digital Systems 9

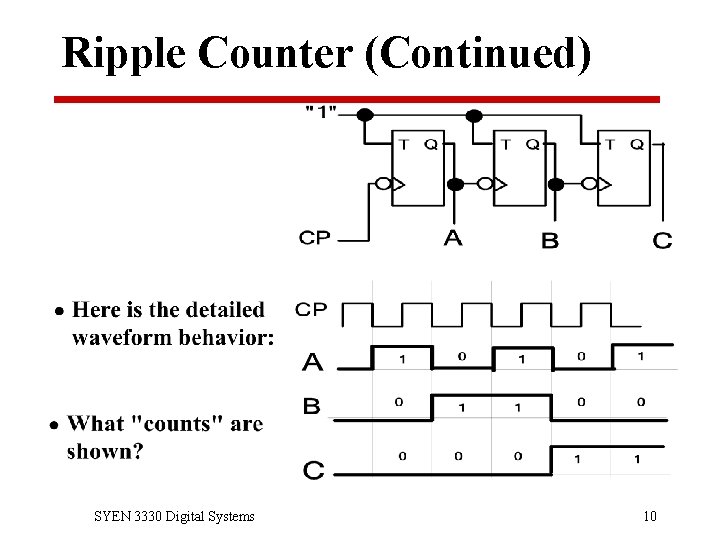

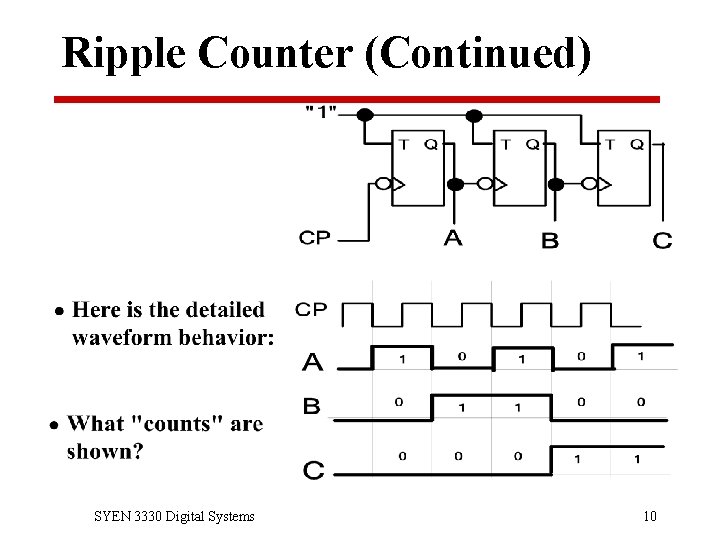

Ripple Counter (Continued) SYEN 3330 Digital Systems 10

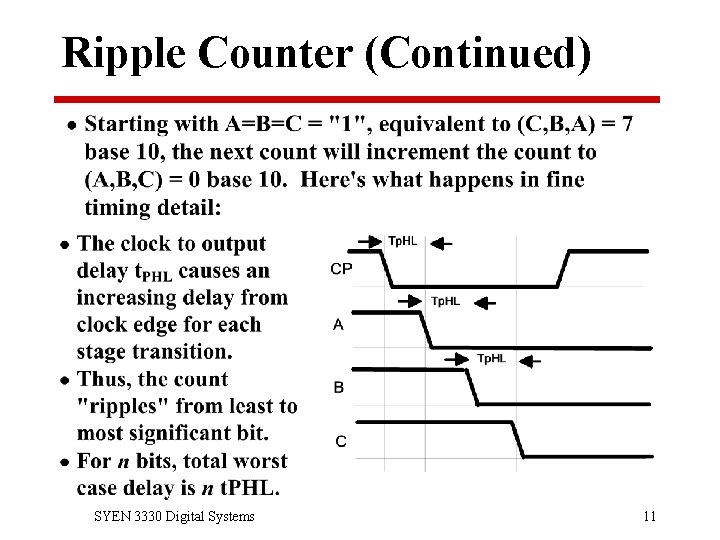

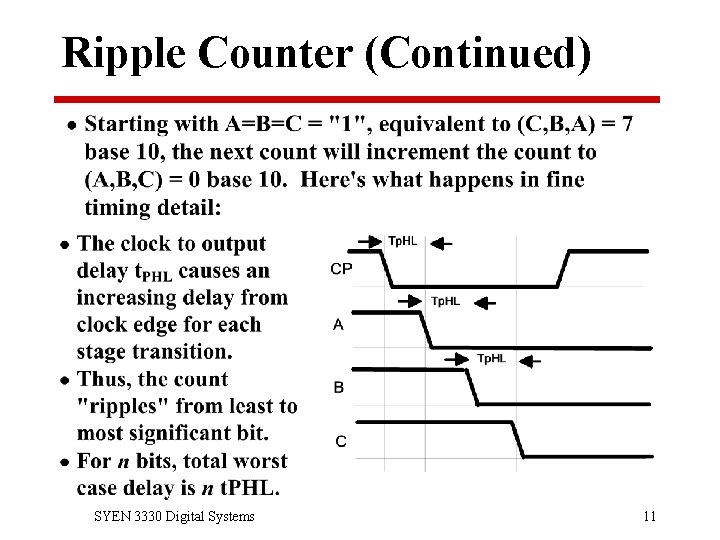

Ripple Counter (Continued) SYEN 3330 Digital Systems 11

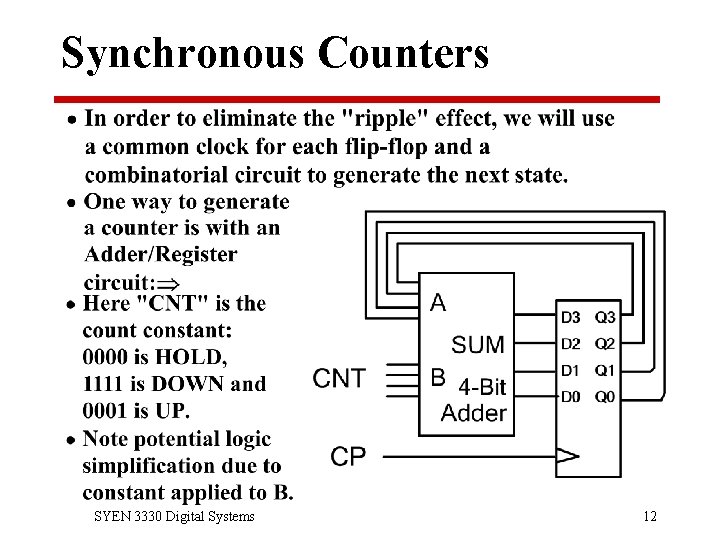

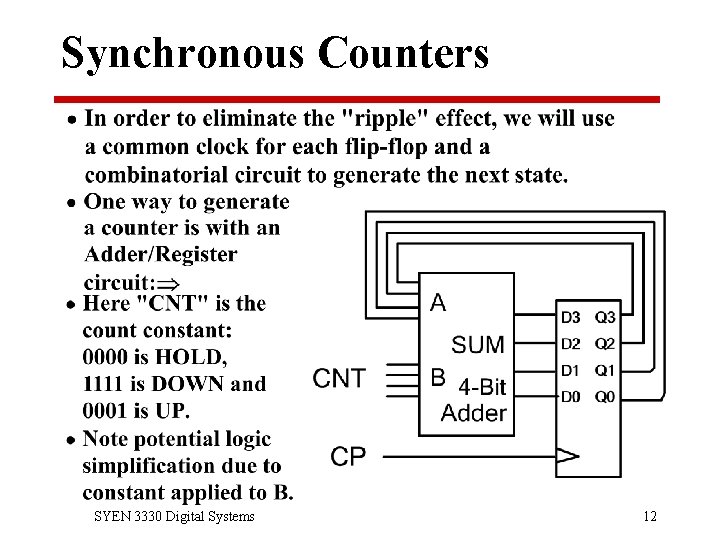

Synchronous Counters SYEN 3330 Digital Systems 12

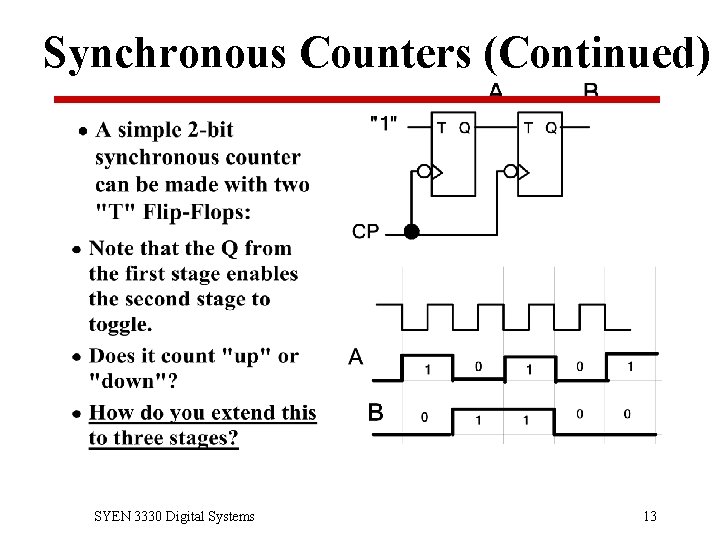

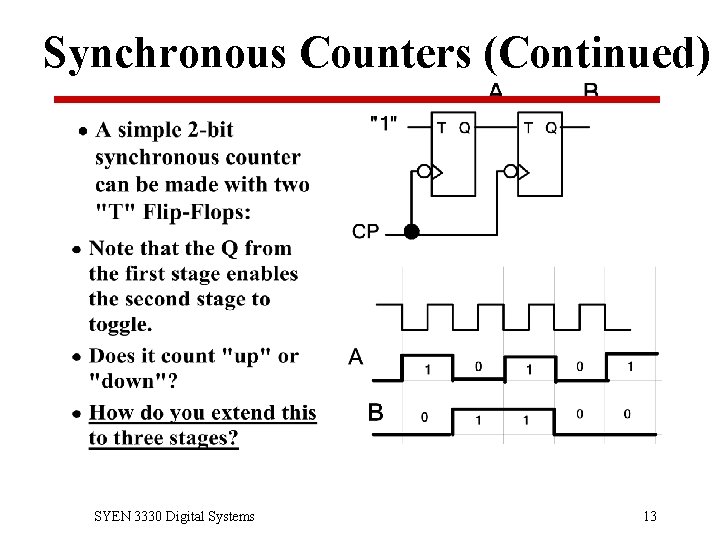

Synchronous Counters (Continued) SYEN 3330 Digital Systems 13

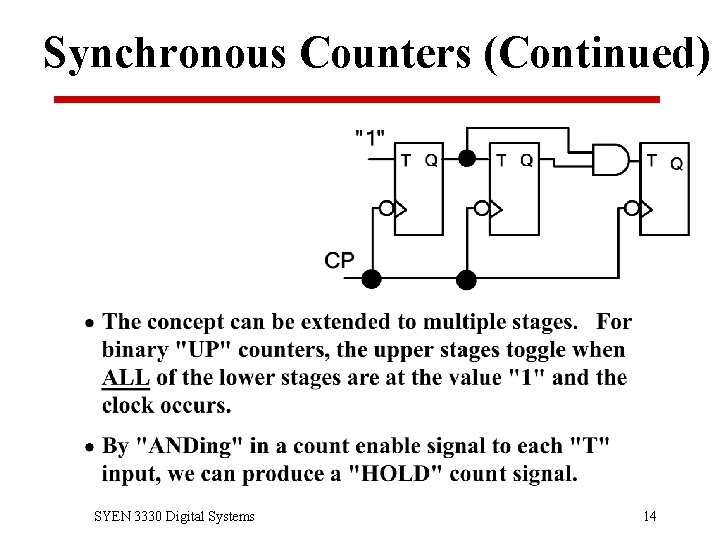

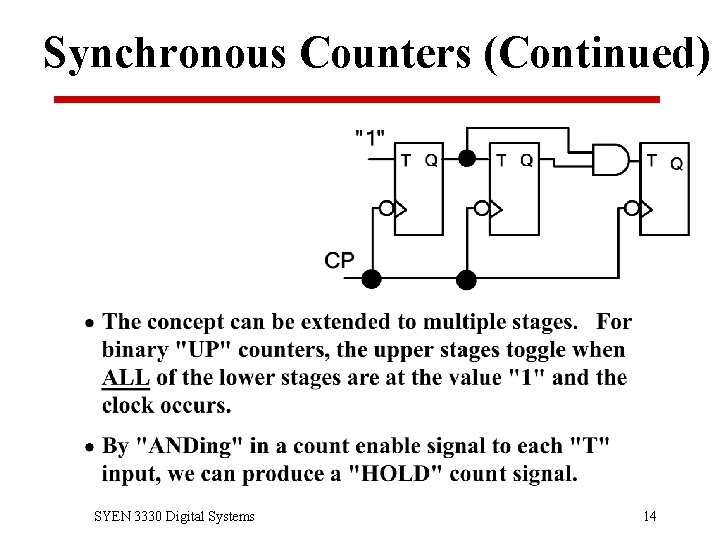

Synchronous Counters (Continued) SYEN 3330 Digital Systems 14

Synchronous Counters – Serial Gating • When a two-input AND gate is used for each stage of the counter with a “ripplelike” carry, this is referred to as serial gating. • As the size of the counter increases the delay through the combinational logic increases roughly in proportion to n, the number of stages. SYEN 3330 Digital Systems 15

Synchronous Counters – Parallel Gating • When a multiple-input ( >2) AND gates are used for each stage of the counter with logic dedicated to each stage or to a group of stages, this is referred to as parallel gating. It resembles carry lookahead in an adder. • As the size of the counter increases the delay through the combinational logic increases roughly in proportion to n/m, the number of stages/the group size. SYEN 3330 Digital Systems 16

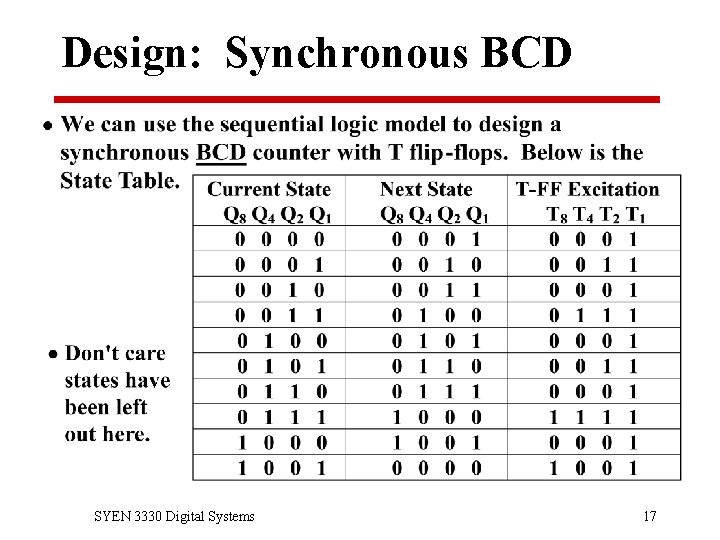

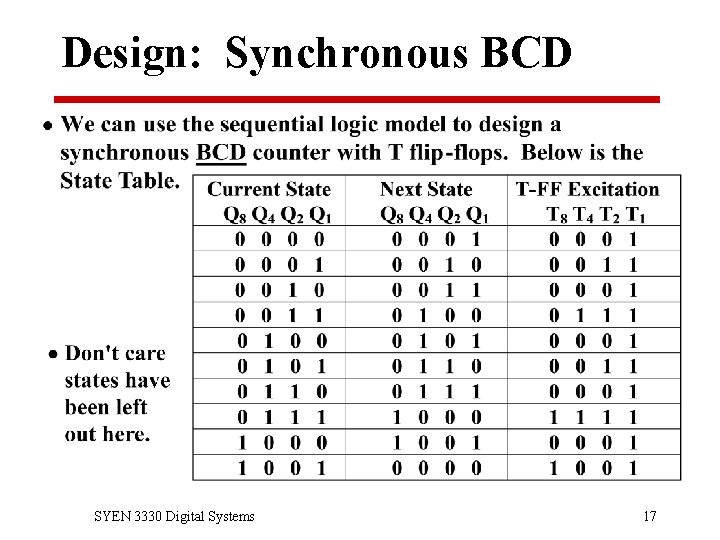

Design: Synchronous BCD SYEN 3330 Digital Systems 17

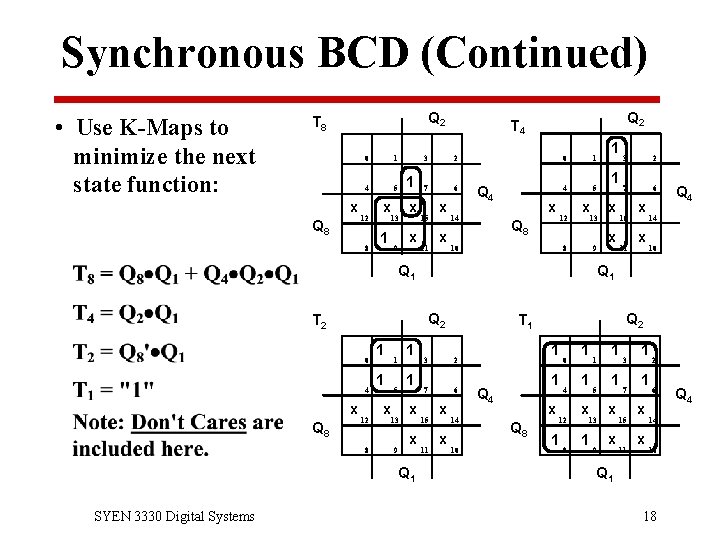

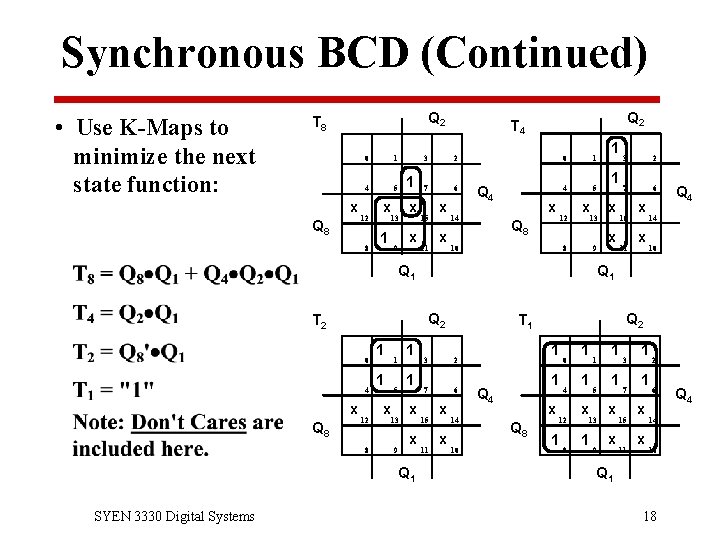

Synchronous BCD (Continued) • Use K-Maps to minimize the next state function: Q 2 T 8 x Q 8 0 1 4 5 12 8 x 13 1 9 1 x x 3 2 7 6 15 11 x x Q 2 T 4 Q 4 14 x Q 8 0 1 4 5 12 10 x 13 8 9 Q 1 0 4 x Q 8 12 8 1 1 1 5 x 13 9 1 1 x x Q 1 SYEN 3330 Digital Systems 1 x x 3 2 7 6 15 11 x x Q 4 14 10 Q 1 Q 2 T 2 1 3 2 7 6 15 11 x x Q 2 T 1 14 10 1 1 Q 4 x Q 8 0 4 12 1 8 1 1 1 5 x 13 1 9 1 1 x x 3 7 15 11 1 1 x x 2 6 14 10 Q 1 18 Q 4

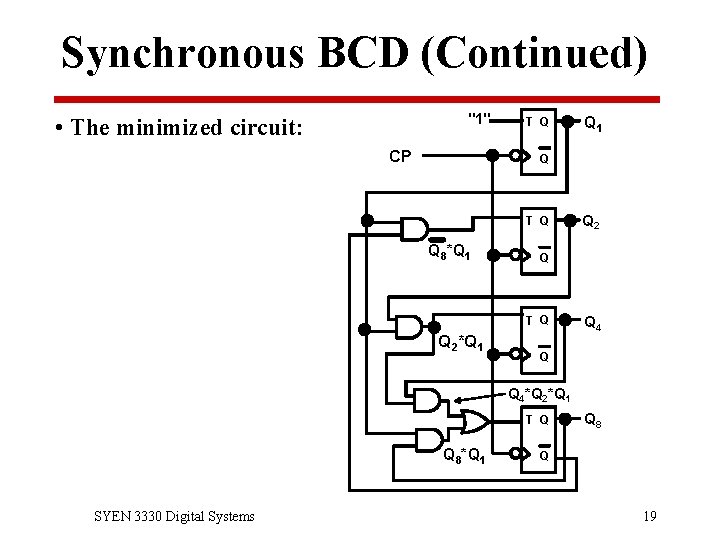

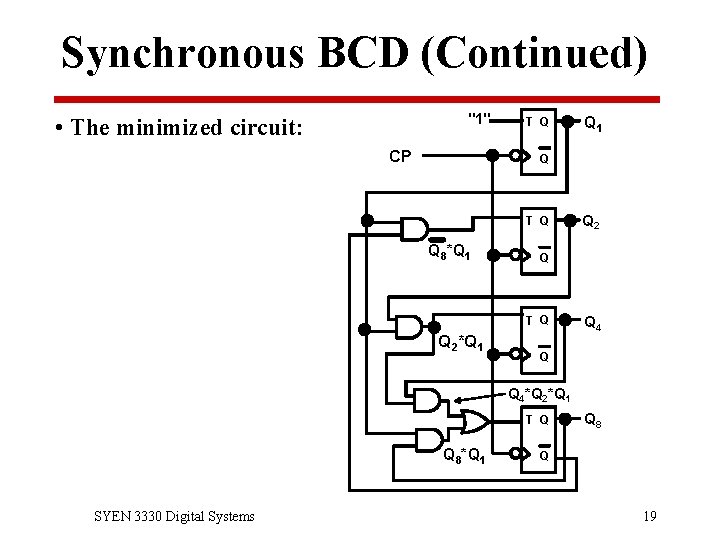

Synchronous BCD (Continued) "1" • The minimized circuit: CP T Q Q 1 Q T Q Q 8*Q 1 Q T Q Q 2*Q 1 Q 2 Q 4 Q Q 4*Q 2*Q 1 T Q Q 8*Q 1 SYEN 3330 Digital Systems Q 8 Q 19

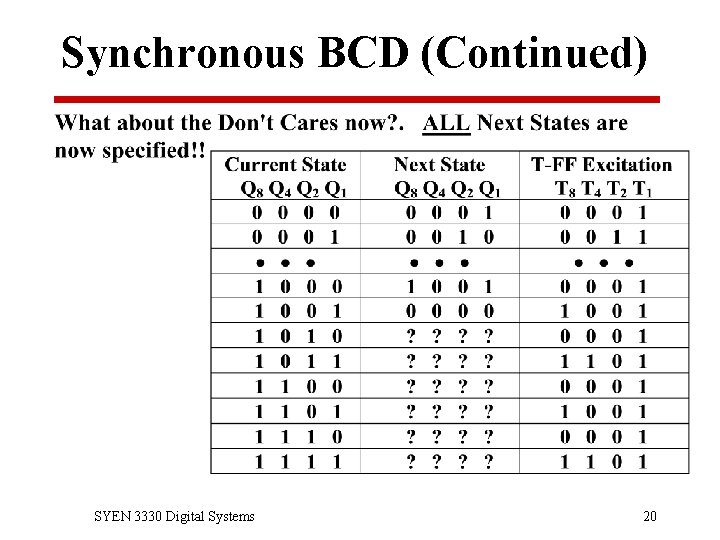

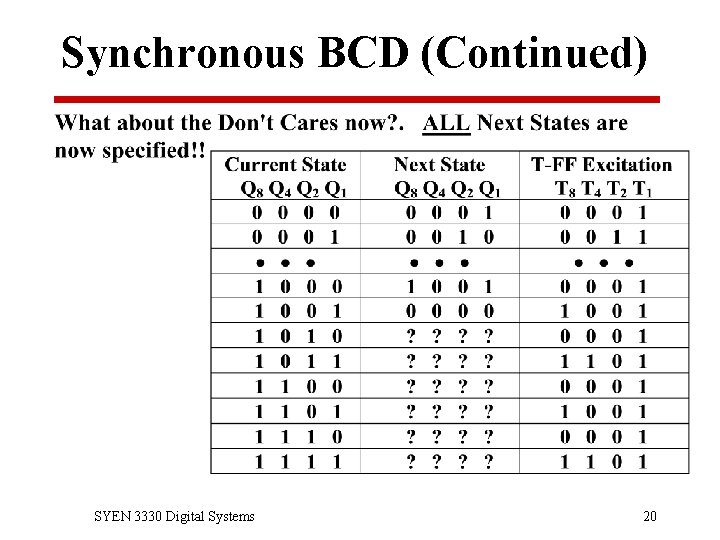

Synchronous BCD (Continued) SYEN 3330 Digital Systems 20

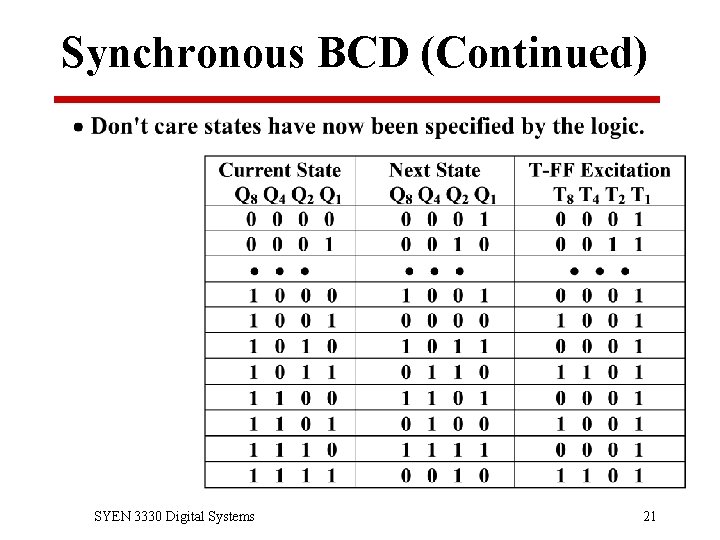

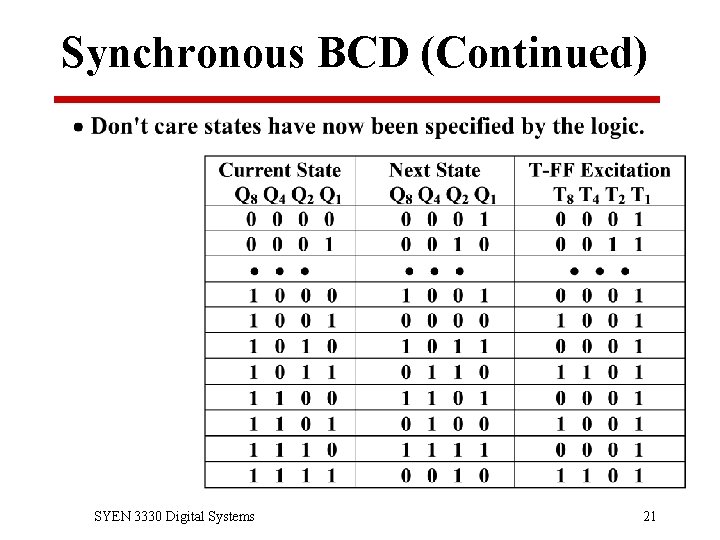

Synchronous BCD (Continued) SYEN 3330 Digital Systems 21

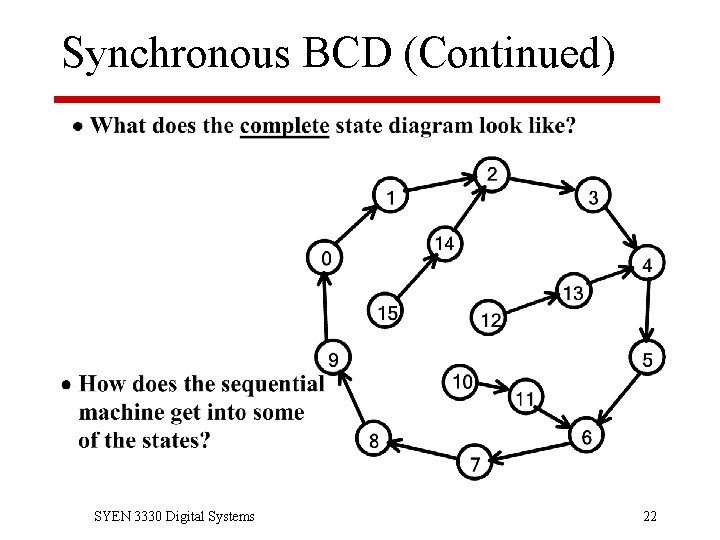

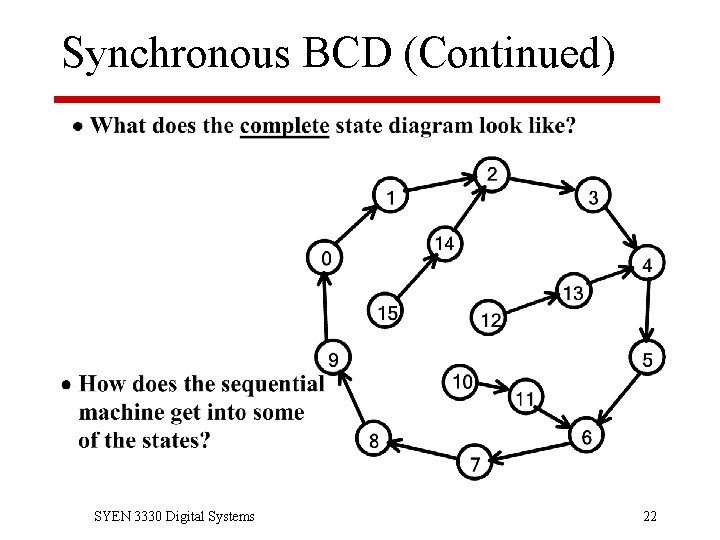

Synchronous BCD (Continued) SYEN 3330 Digital Systems 22

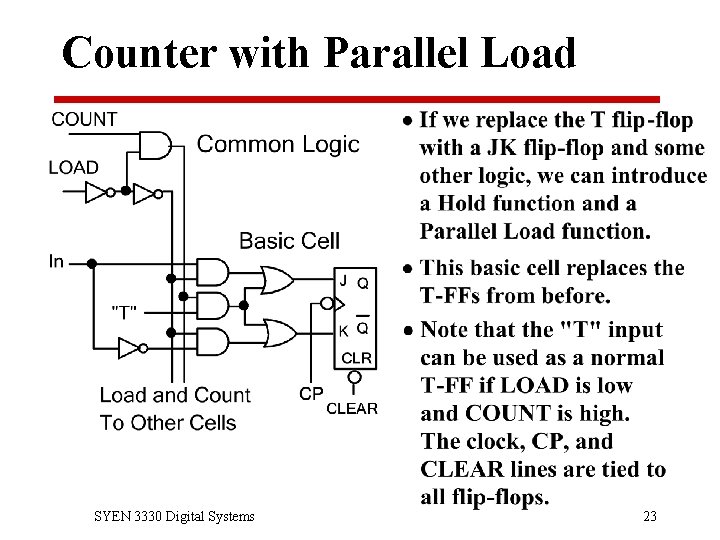

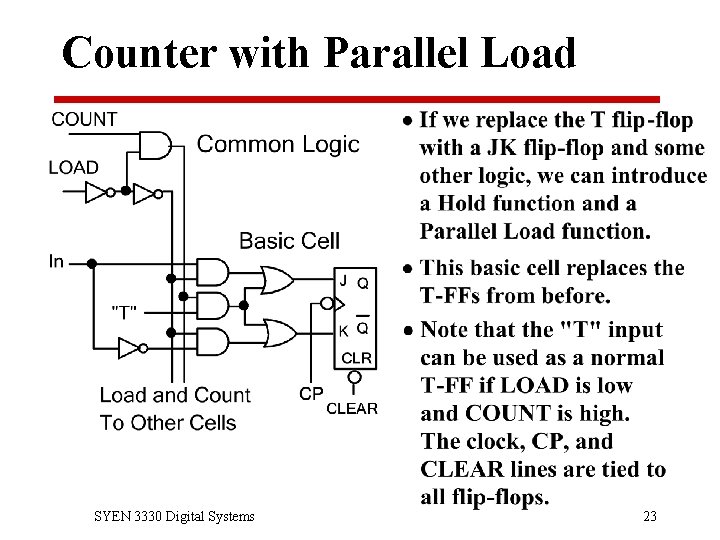

Counter with Parallel Load SYEN 3330 Digital Systems 23

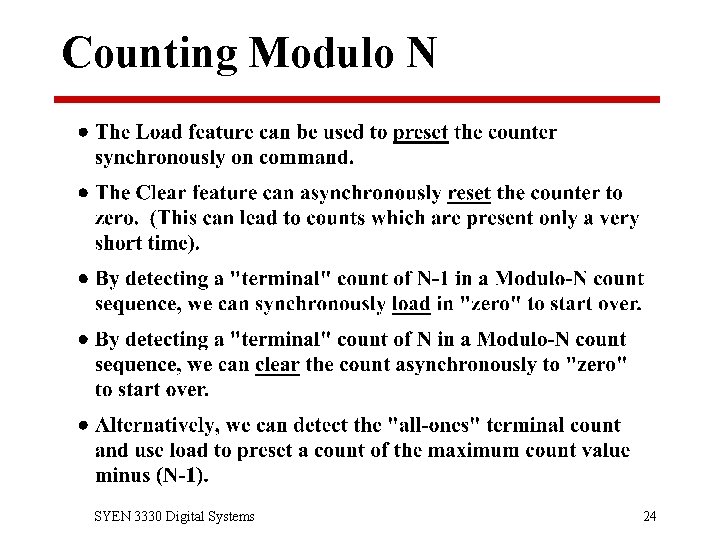

Counting Modulo N SYEN 3330 Digital Systems 24

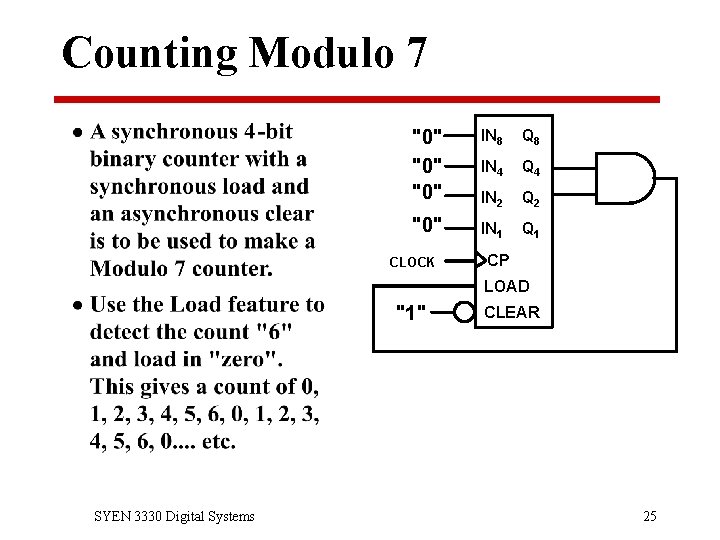

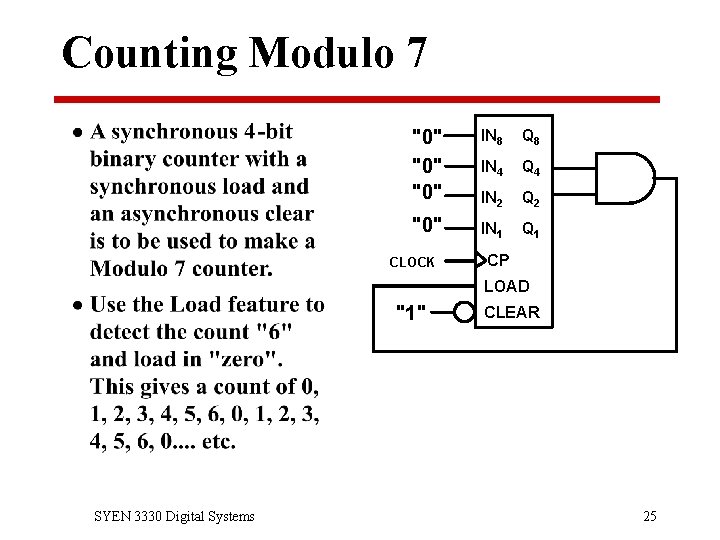

Counting Modulo 7 "0" "0" IN 8 Q 8 IN 4 Q 4 IN 2 Q 2 "0" IN 1 Q 1 CLOCK CP LOAD "1" SYEN 3330 Digital Systems CLEAR 25

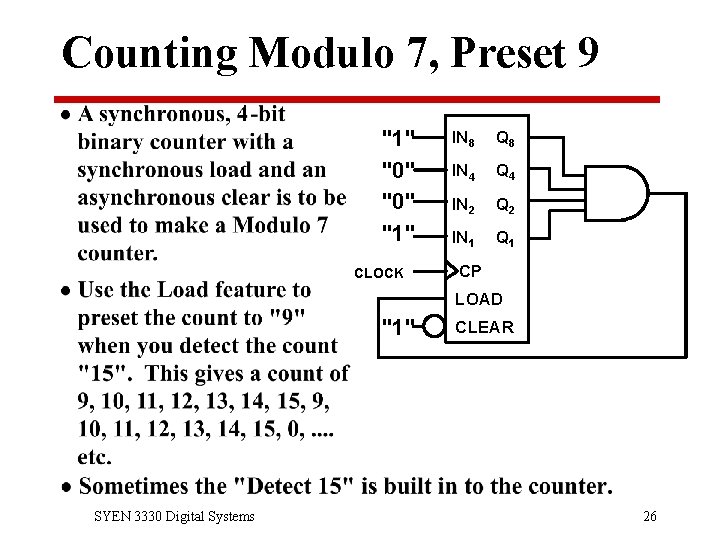

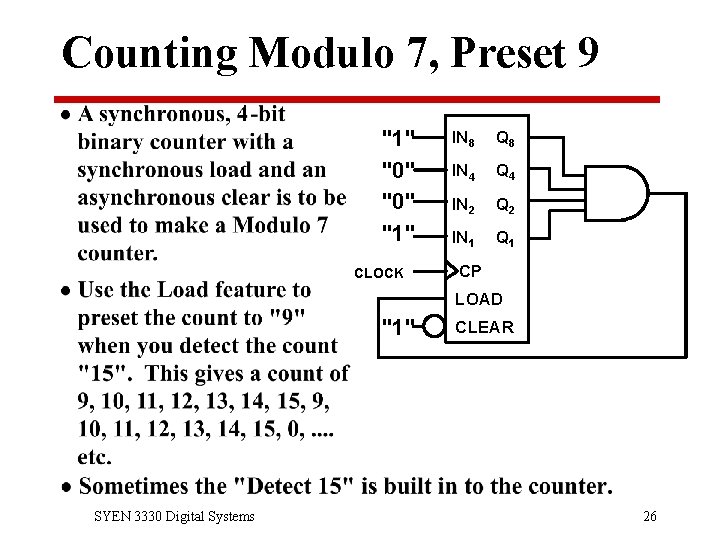

Counting Modulo 7, Preset 9 "1" "0" "1" CLOCK IN 8 Q 8 IN 4 Q 4 IN 2 Q 2 IN 1 Q 1 CP LOAD "1" SYEN 3330 Digital Systems CLEAR 26

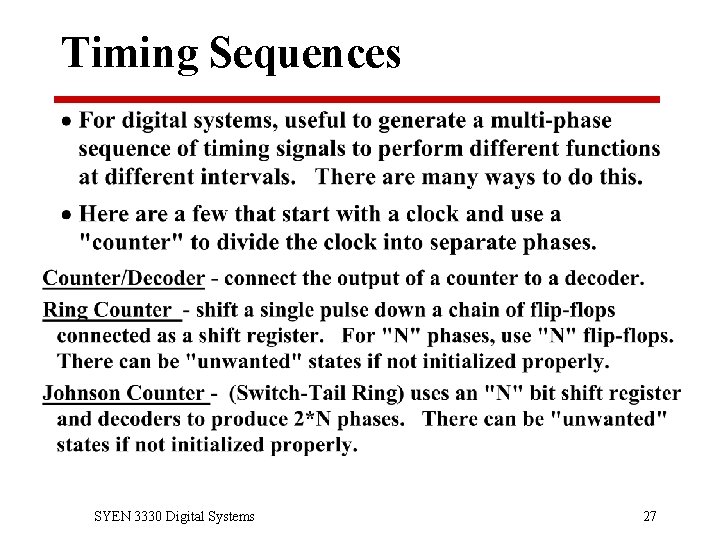

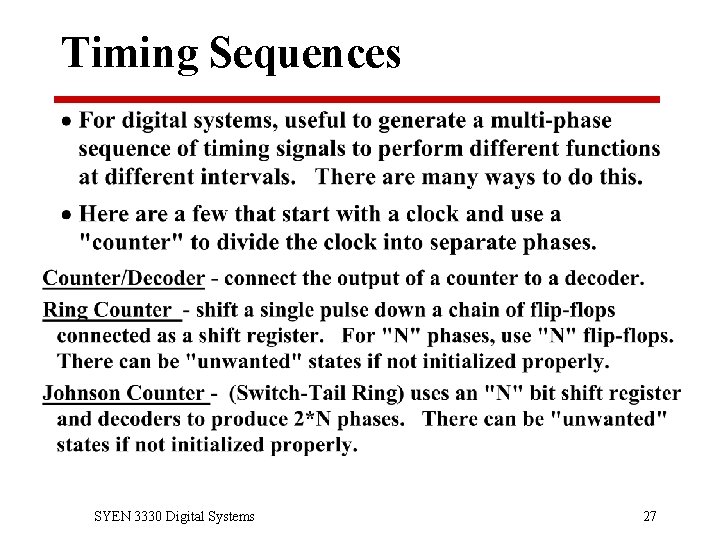

Timing Sequences SYEN 3330 Digital Systems 27

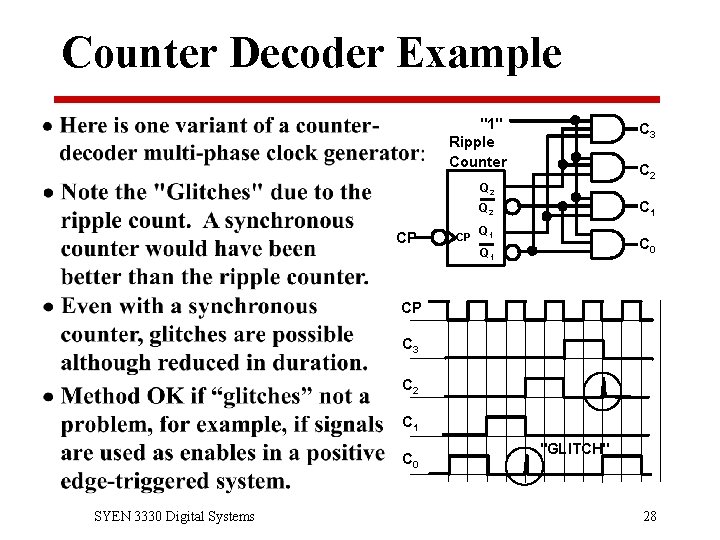

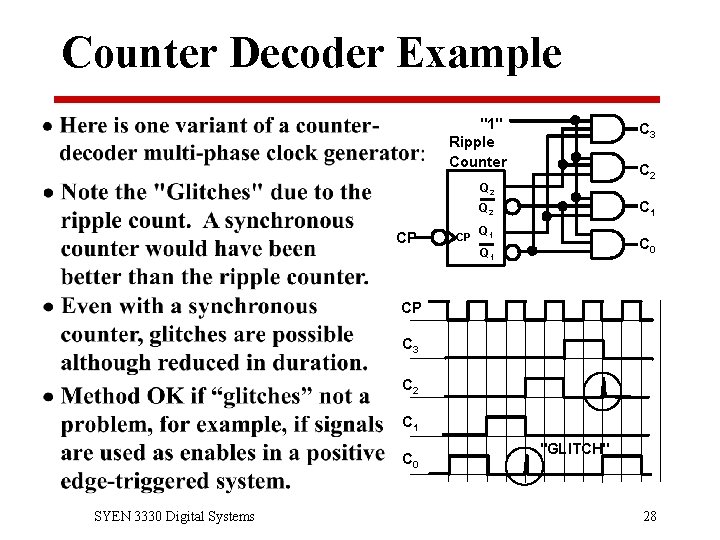

Counter Decoder Example "1" Ripple Counter C 3 C 2 Q 2 C 1 Q 2 CP CP Q 1 C 0 Q 1 CP C 3 C 2 C 1 C 0 SYEN 3330 Digital Systems "GLITCH" 28

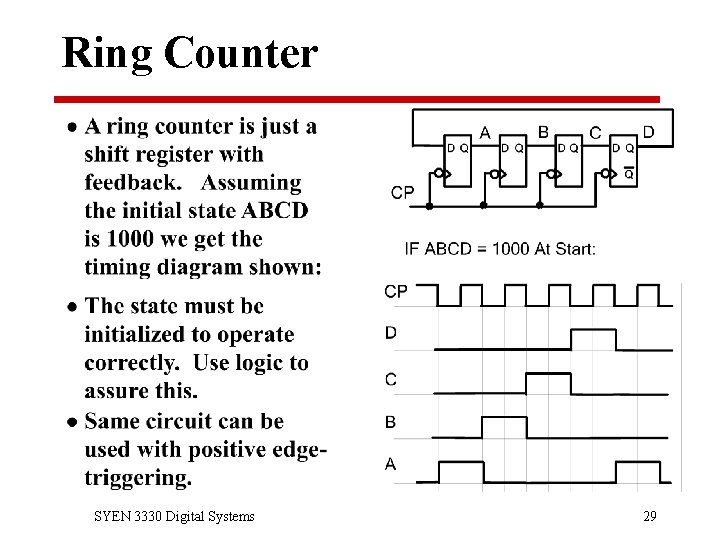

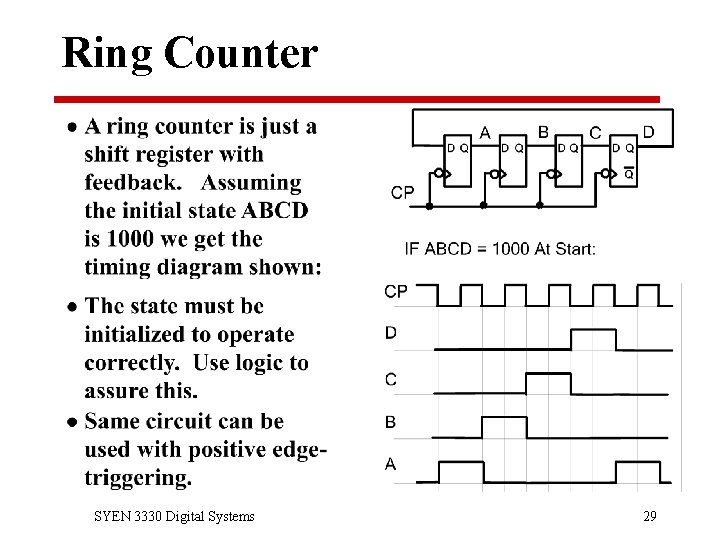

Ring Counter SYEN 3330 Digital Systems 29

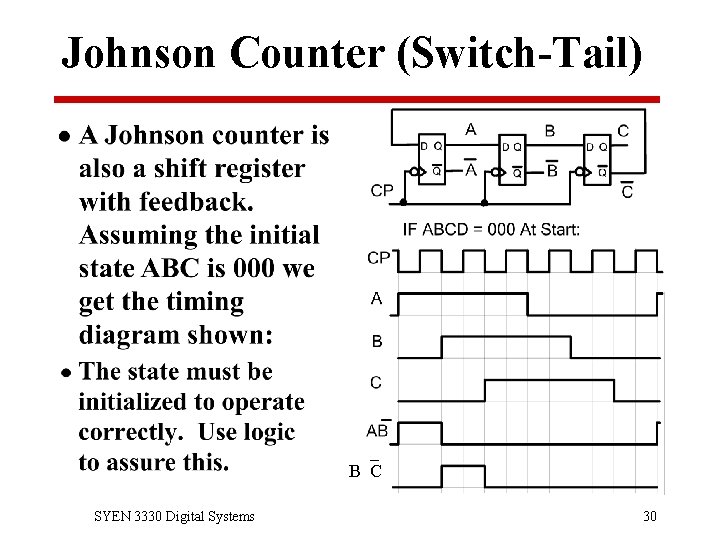

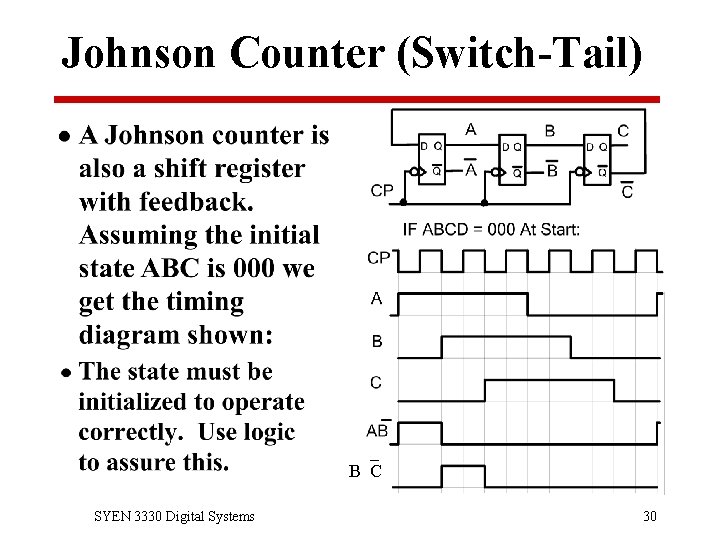

Johnson Counter (Switch-Tail) B C SYEN 3330 Digital Systems 30

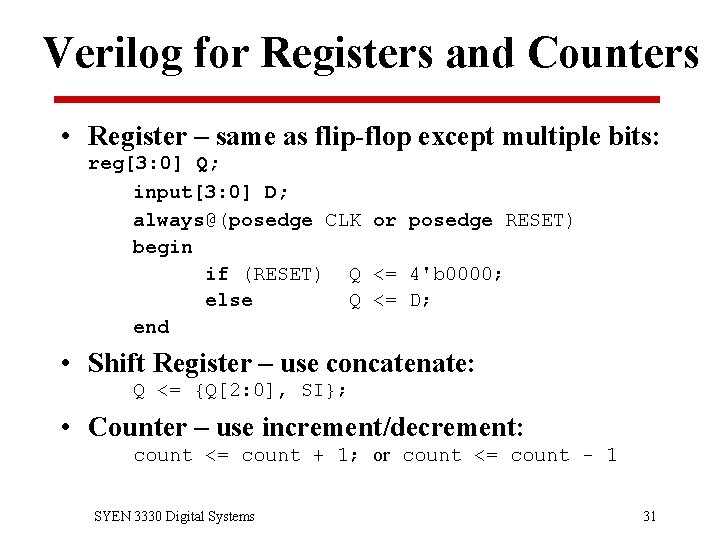

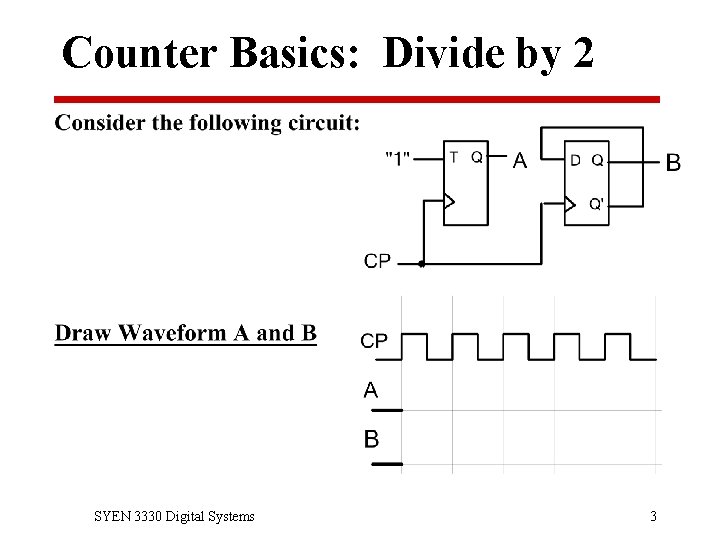

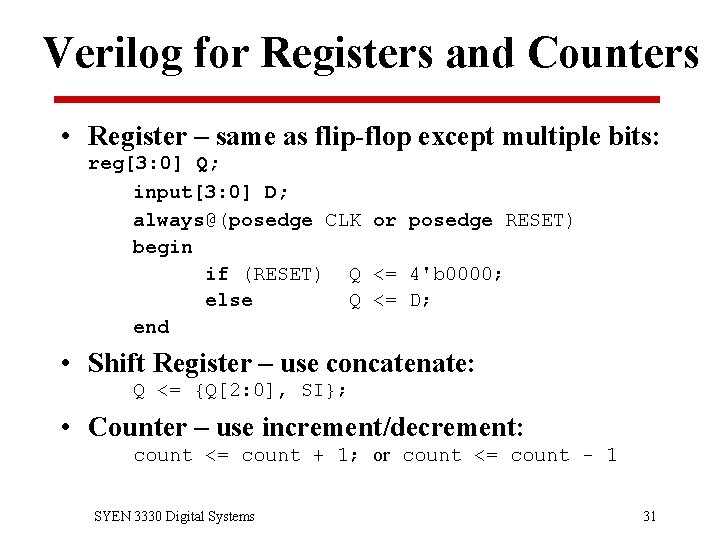

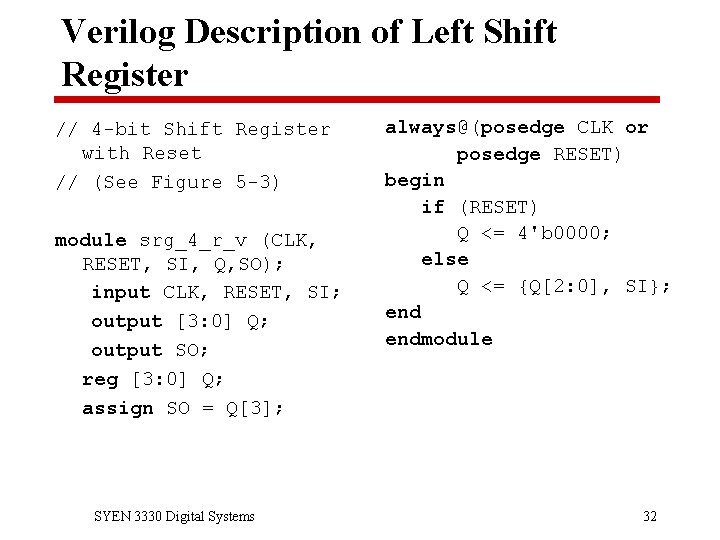

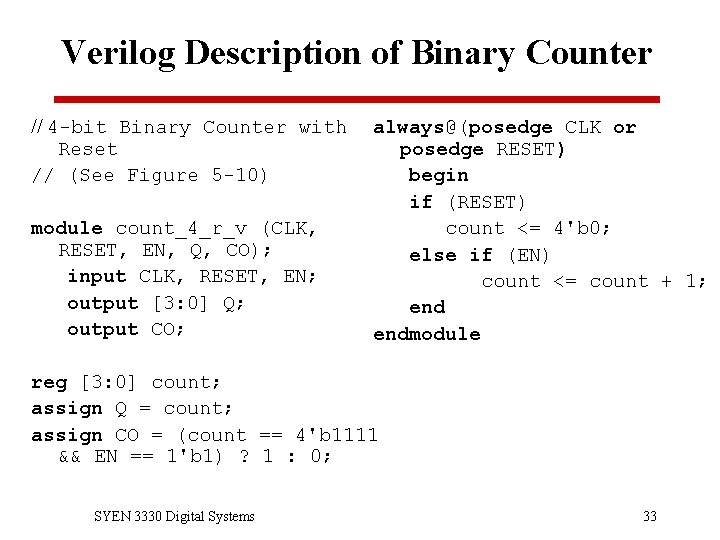

Verilog for Registers and Counters • Register – same as flip-flop except multiple bits: reg[3: 0] Q; input[3: 0] D; always@(posedge CLK or posedge RESET) begin if (RESET) Q <= 4'b 0000; else Q <= D; end • Shift Register – use concatenate: Q <= {Q[2: 0], SI}; • Counter – use increment/decrement: count <= count + 1; or count <= count - 1 SYEN 3330 Digital Systems 31

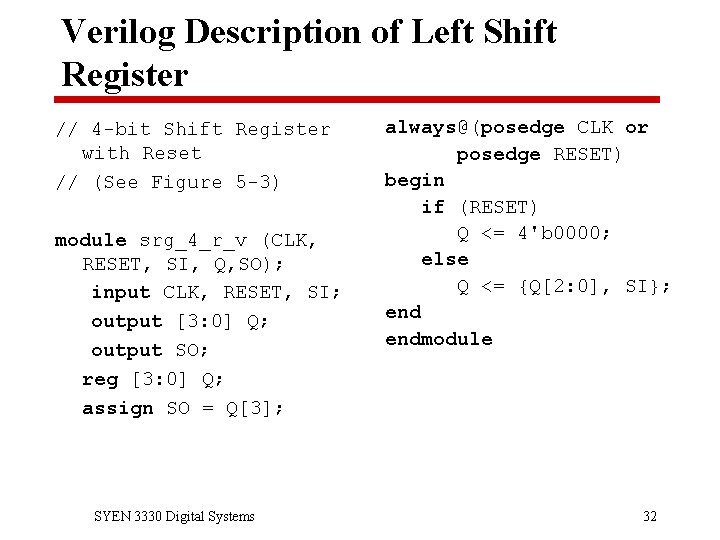

Verilog Description of Left Shift Register // 4 -bit Shift Register with Reset // (See Figure 5 -3) module srg_4_r_v (CLK, RESET, SI, Q, SO); input CLK, RESET, SI; output [3: 0] Q; output SO; reg [3: 0] Q; assign SO = Q[3]; SYEN 3330 Digital Systems always@(posedge CLK or posedge RESET) begin if (RESET) Q <= 4'b 0000; else Q <= {Q[2: 0], SI}; endmodule 32

Verilog Description of Binary Counter // 4 -bit Binary Counter with Reset // (See Figure 5 -10) module count_4_r_v (CLK, RESET, EN, Q, CO); input CLK, RESET, EN; output [3: 0] Q; output CO; always@(posedge CLK or posedge RESET) begin if (RESET) count <= 4'b 0; else if (EN) count <= count + 1; endmodule reg [3: 0] count; assign Q = count; assign CO = (count == 4'b 1111 && EN == 1'b 1) ? 1 : 0; SYEN 3330 Digital Systems 33