Switched Capacitor Blocks Alex Doboli Ph D Department

Switched Capacitor Blocks Alex Doboli, Ph. D. Department of Electrical and Computer Engineering State University of New York at Stony Brook Email: adoboli@ece. sunysb. edu ©Alex Doboli 2006

Overview of the Chapter • Introduction to SC circuits • Programmable SC blocks in PSo. C • SC principle: controlled movement of charge • Electrical nonidealities: circuit nonidealities, non-zero switch resistance, channel charge injection, clock feedthrough • Basic SC blocks: gain amplifier, programmable gain amplifier, comparator, integrator, differentiator • PSo. C’s programmable SC blocks: – Type C and Type D SC blocks – Programming (registers) ©Alex Doboli 2006

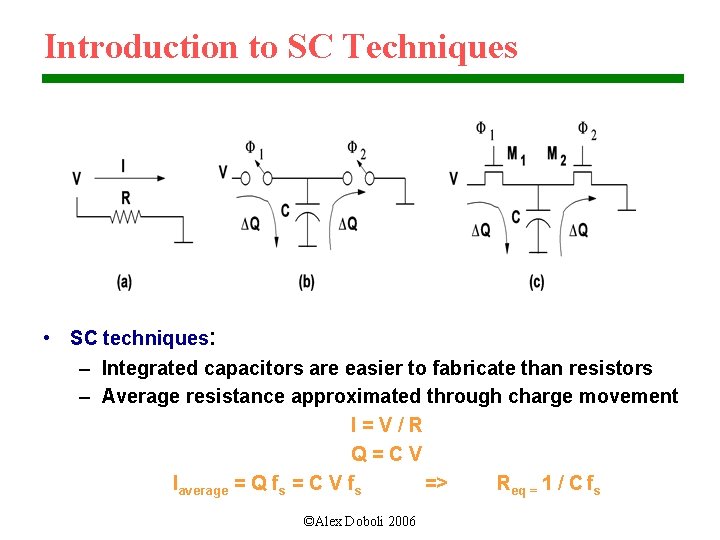

Introduction to SC Techniques • SC techniques: – Integrated capacitors are easier to fabricate than resistors – Average resistance approximated through charge movement I=V/R Q=CV Iaverage = Q fs = C V fs => Req = 1 / C fs ©Alex Doboli 2006

Introduction to SC Techniques • Constraints: – – Switches Ф 1 and Ф 2 can never be closed at the same time Switch Ф 1 must have time to open before switch Ф 2 closes Switch Ф 2 must have time to open before switch Ф 1 closes Frequency fs must allow enough time for the circuits to fully charge and discharge ©Alex Doboli 2006

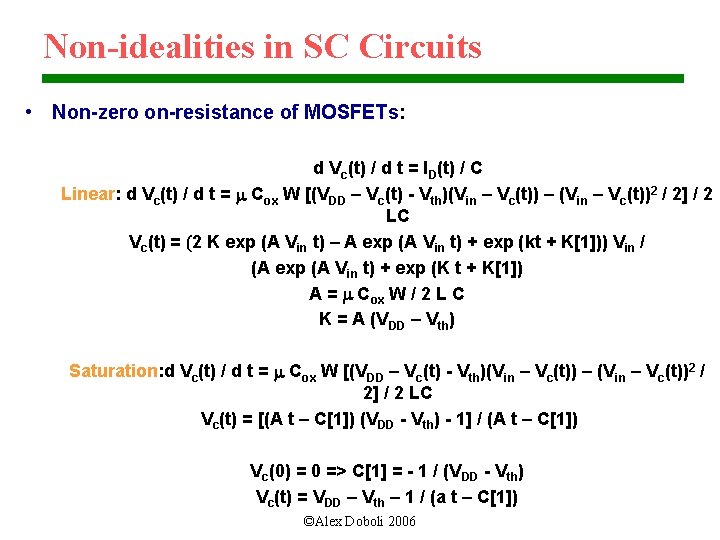

Non-idealities in SC Circuits • Non-zero on-resistance of MOSFETs: d Vc(t) / d t = ID(t) / C Linear: d Vc(t) / d t = m Cox W [(VDD – Vc(t) - Vth)(Vin – Vc(t)) – (Vin – Vc(t))2 / 2] / 2 LC Vc(t) = (2 K exp (A Vin t) – A exp (A Vin t) + exp (kt + K[1])) Vin / (A exp (A Vin t) + exp (K t + K[1]) A = m Cox W / 2 L C K = A (VDD – Vth) Saturation: d Vc(t) / d t = m Cox W [(VDD – Vc(t) - Vth)(Vin – Vc(t)) – (Vin – Vc(t))2 / 2] / 2 LC Vc(t) = [(A t – C[1]) (VDD - Vth) - 1] / (A t – C[1]) Vc(0) = 0 => C[1] = - 1 / (VDD - Vth) Vc(t) = VDD – Vth – 1 / (a t – C[1]) ©Alex Doboli 2006

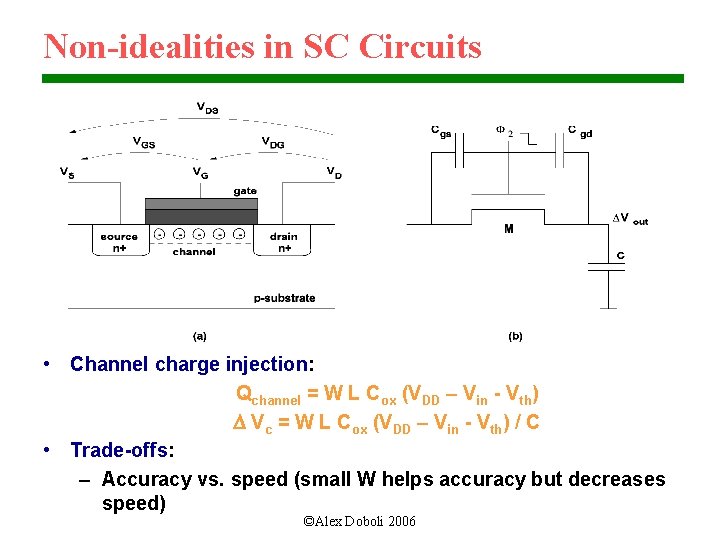

Non-idealities in SC Circuits • Channel charge injection: Qchannel = W L Cox (VDD – Vin - Vth) D Vc = W L Cox (VDD – Vin - Vth) / C • Trade-offs: – Accuracy vs. speed (small W helps accuracy but decreases speed) ©Alex Doboli 2006

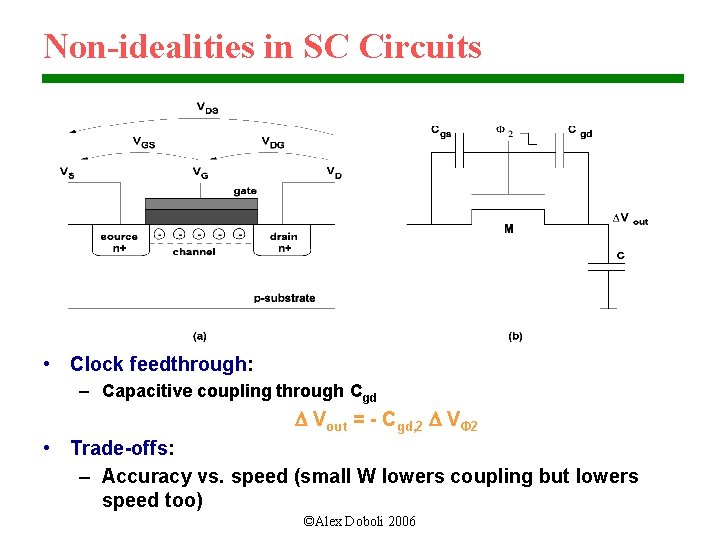

Non-idealities in SC Circuits • Clock feedthrough: – Capacitive coupling through Cgd D Vout = - Cgd, 2 D VΦ 2 • Trade-offs: – Accuracy vs. speed (small W lowers coupling but lowers speed too) ©Alex Doboli 2006

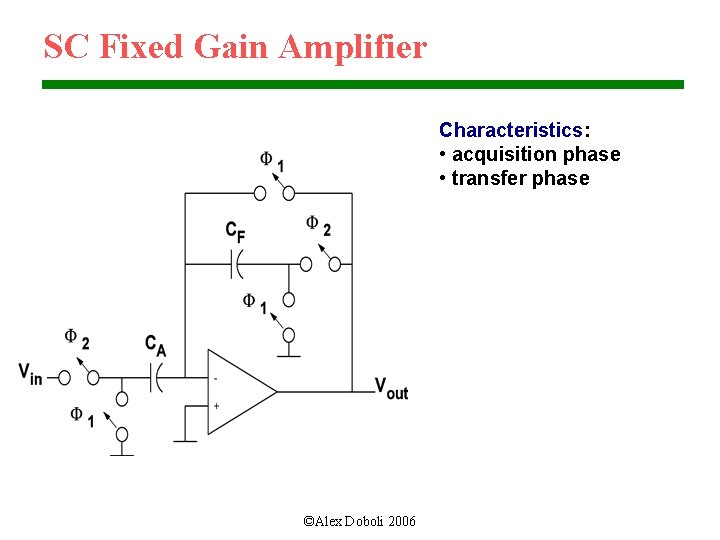

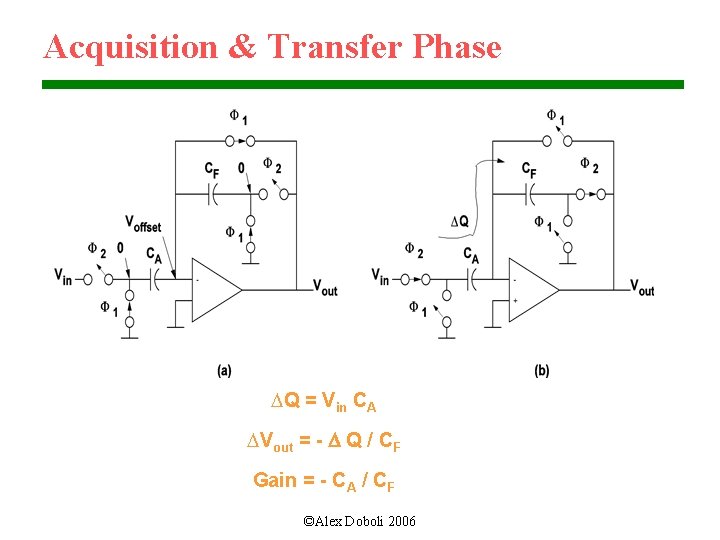

SC Fixed Gain Amplifier Characteristics: • acquisition phase • transfer phase ©Alex Doboli 2006

Acquisition & Transfer Phase DQ = Vin CA DVout = - D Q / CF Gain = - CA / CF ©Alex Doboli 2006

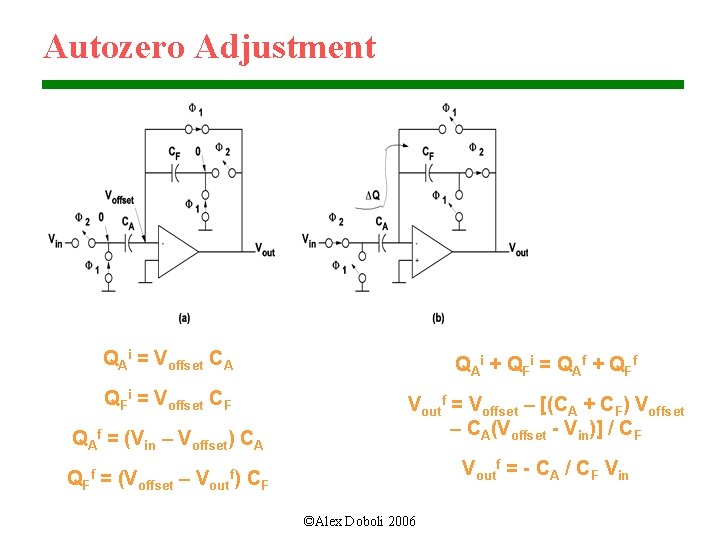

Autozero Adjustment QAi = Voffset CA QAi + QFi = QAf + QFf QFi = Voffset CF Voutf = Voffset – [(CA + CF) Voffset – CA(Voffset - Vin)] / CF QAf = (Vin – Voffset) CA Voutf = - CA / CF Vin QF = (Voffset – Vout CF f f) ©Alex Doboli 2006

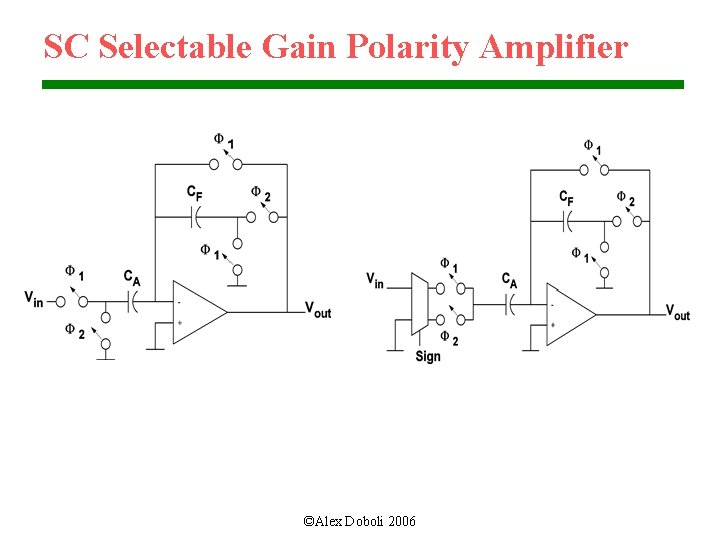

SC Selectable Gain Polarity Amplifier ©Alex Doboli 2006

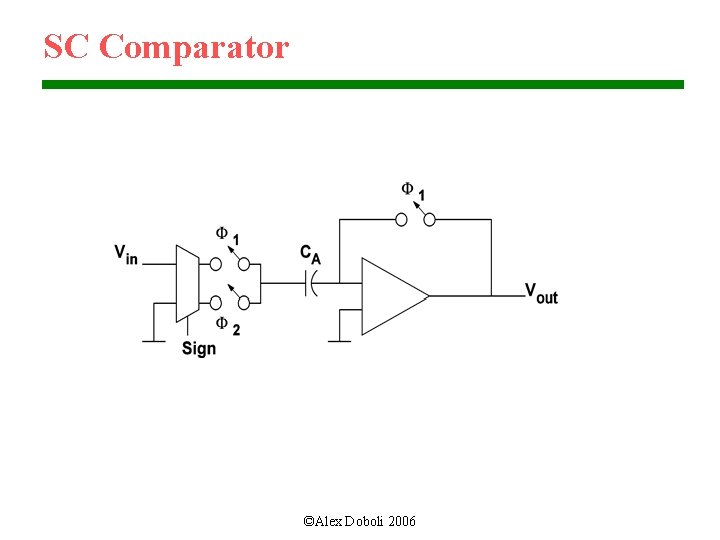

SC Comparator ©Alex Doboli 2006

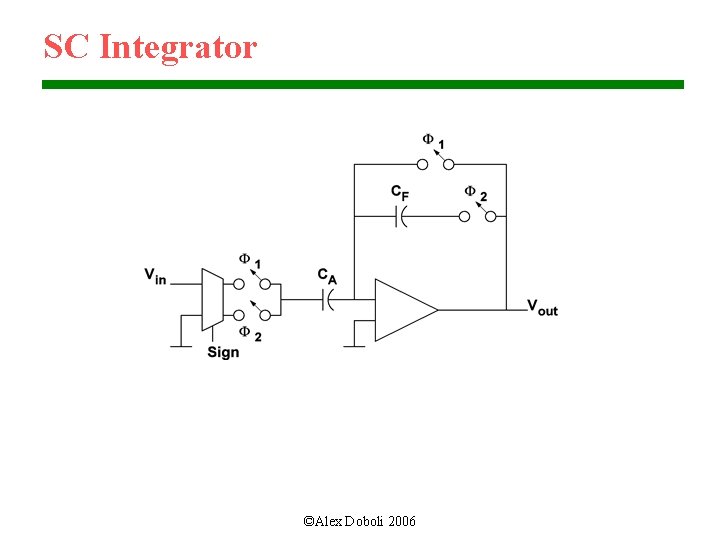

SC Integrator ©Alex Doboli 2006

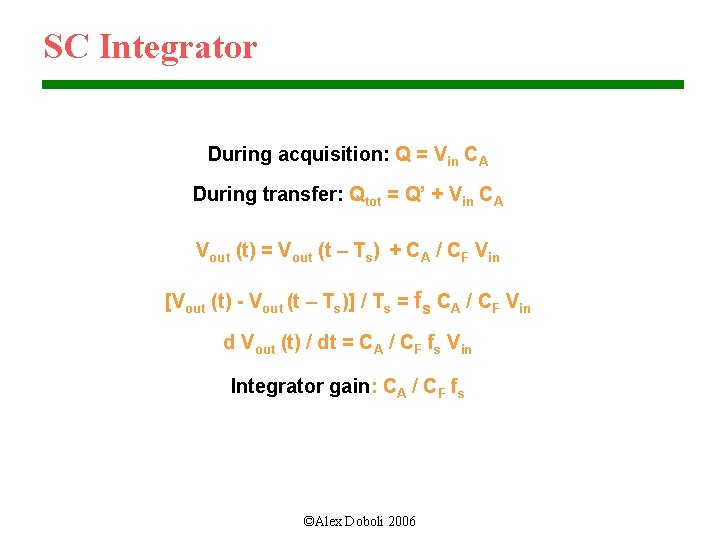

SC Integrator During acquisition: Q = Vin CA During transfer: Qtot = Q’ + Vin CA Vout (t) = Vout (t – Ts) + CA / CF Vin [Vout (t) - Vout (t – Ts)] / Ts = fs CA / CF Vin d Vout (t) / dt = CA / CF fs Vin Integrator gain: CA / CF fs ©Alex Doboli 2006

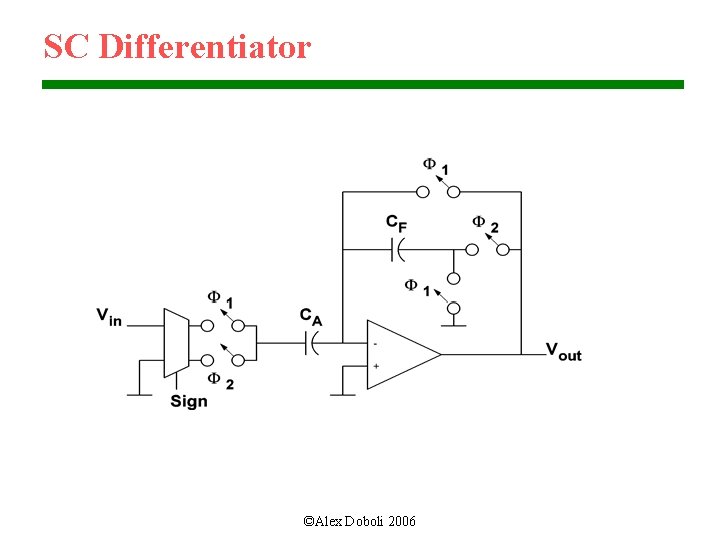

SC Differentiator ©Alex Doboli 2006

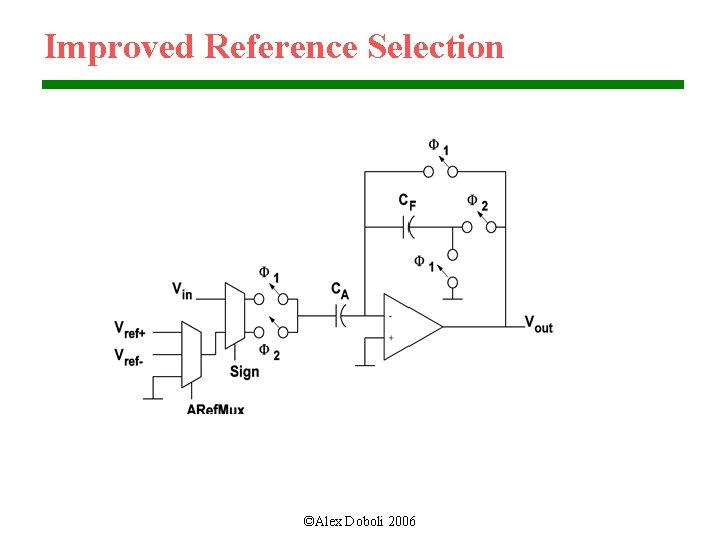

Improved Reference Selection ©Alex Doboli 2006

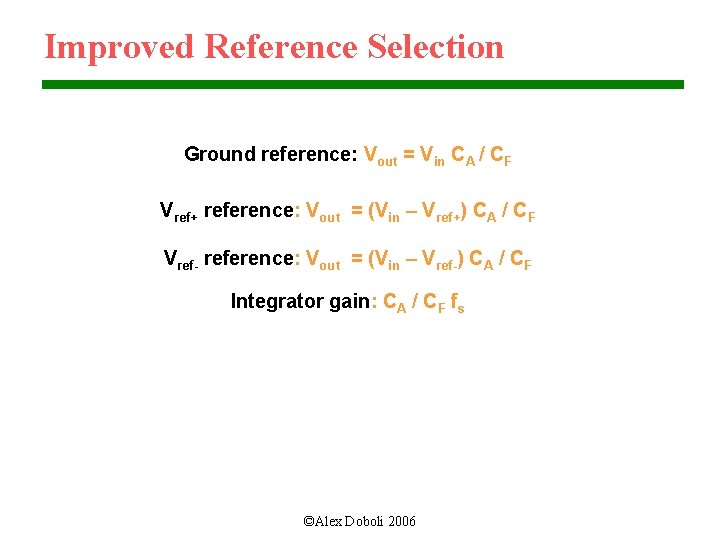

Improved Reference Selection Ground reference: Vout = Vin CA / CF Vref+ reference: Vout = (Vin – Vref+) CA / CF Vref- reference: Vout = (Vin – Vref-) CA / CF Integrator gain: CA / CF fs ©Alex Doboli 2006

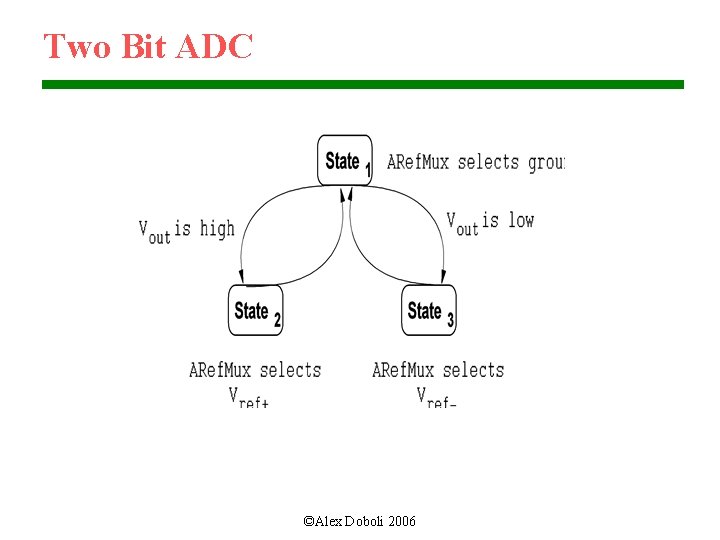

Two Bit ADC ©Alex Doboli 2006

Two Bit ADC 1. 2. 3. 4. Vin > Vref+ Vin < Vref+ and Vin > 0 Vin < 0 and Vin > Vref. Vin < Vref- ©Alex Doboli 2006

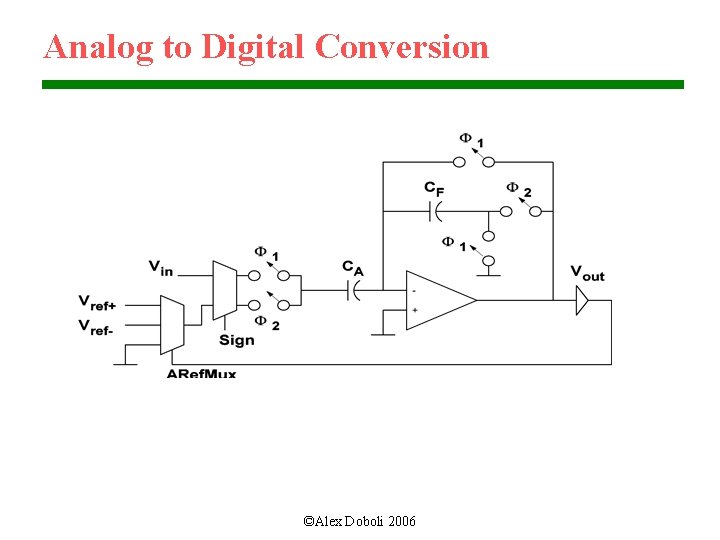

Analog to Digital Conversion ©Alex Doboli 2006

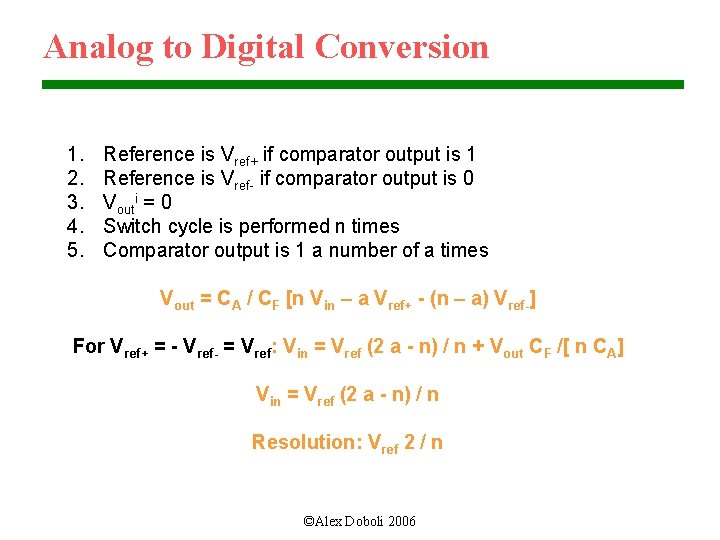

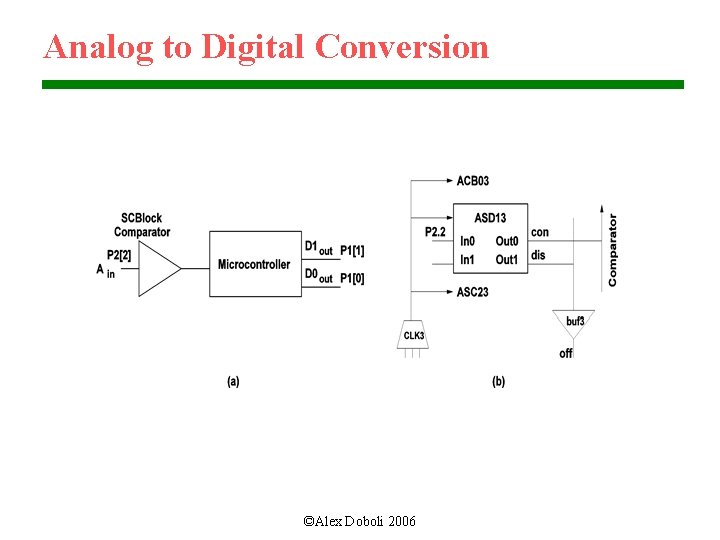

Analog to Digital Conversion 1. 2. 3. 4. 5. Reference is Vref+ if comparator output is 1 Reference is Vref- if comparator output is 0 Vouti = 0 Switch cycle is performed n times Comparator output is 1 a number of a times Vout = CA / CF [n Vin – a Vref+ - (n – a) Vref-] For Vref+ = - Vref- = Vref: Vin = Vref (2 a - n) / n + Vout CF /[ n CA] Vin = Vref (2 a - n) / n Resolution: Vref 2 / n ©Alex Doboli 2006

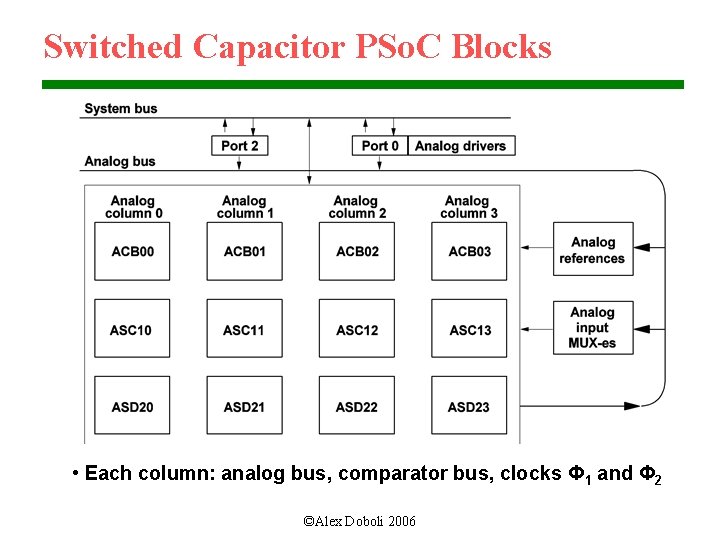

Switched Capacitor PSo. C Blocks • Each column: analog bus, comparator bus, clocks Φ 1 and Φ 2 ©Alex Doboli 2006

PSo. C Type C Block ©Alex Doboli 2006

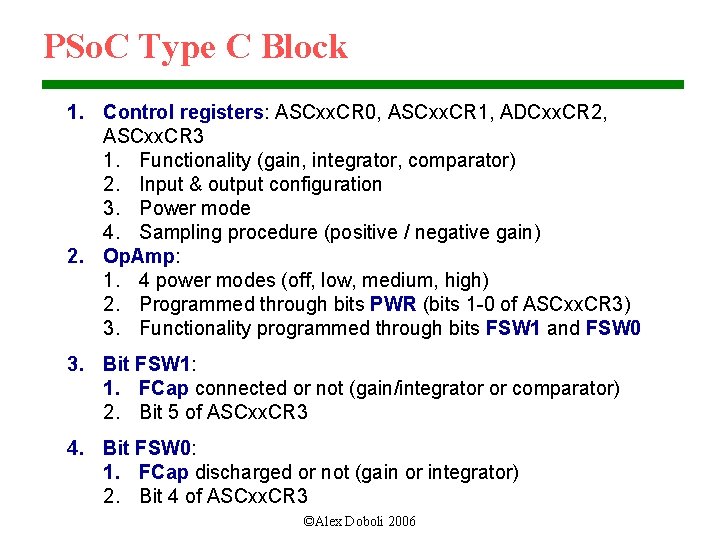

PSo. C Type C Block 1. Control registers: ASCxx. CR 0, ASCxx. CR 1, ADCxx. CR 2, ASCxx. CR 3 1. Functionality (gain, integrator, comparator) 2. Input & output configuration 3. Power mode 4. Sampling procedure (positive / negative gain) 2. Op. Amp: 1. 4 power modes (off, low, medium, high) 2. Programmed through bits PWR (bits 1 -0 of ASCxx. CR 3) 3. Functionality programmed through bits FSW 1 and FSW 0 3. Bit FSW 1: 1. FCap connected or not (gain/integrator or comparator) 2. Bit 5 of ASCxx. CR 3 4. Bit FSW 0: 1. FCap discharged or not (gain or integrator) 2. Bit 4 of ASCxx. CR 3 ©Alex Doboli 2006

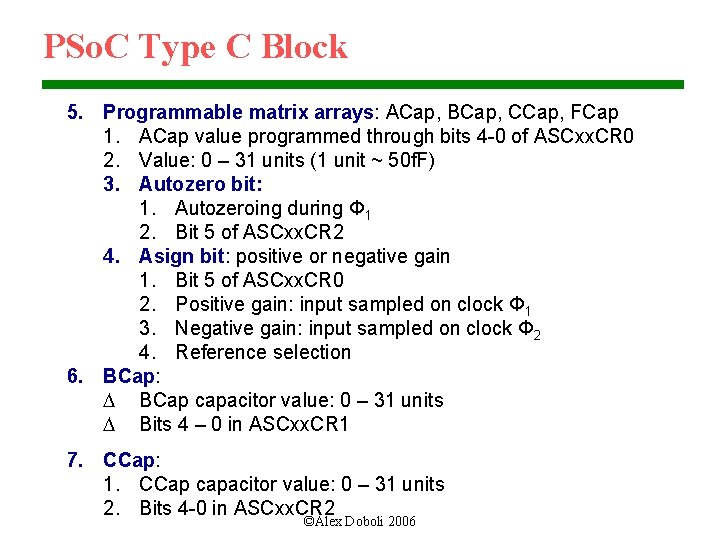

PSo. C Type C Block 5. Programmable matrix arrays: ACap, BCap, CCap, FCap 1. ACap value programmed through bits 4 -0 of ASCxx. CR 0 2. Value: 0 – 31 units (1 unit ~ 50 f. F) 3. Autozero bit: 1. Autozeroing during Φ 1 2. Bit 5 of ASCxx. CR 2 4. Asign bit: positive or negative gain 1. Bit 5 of ASCxx. CR 0 2. Positive gain: input sampled on clock Φ 1 3. Negative gain: input sampled on clock Φ 2 4. Reference selection 6. BCap: D BCap capacitor value: 0 – 31 units D Bits 4 – 0 in ASCxx. CR 1 7. CCap: 1. CCap capacitor value: 0 – 31 units 2. Bits 4 -0 in ASCxx. CR 2 ©Alex Doboli 2006

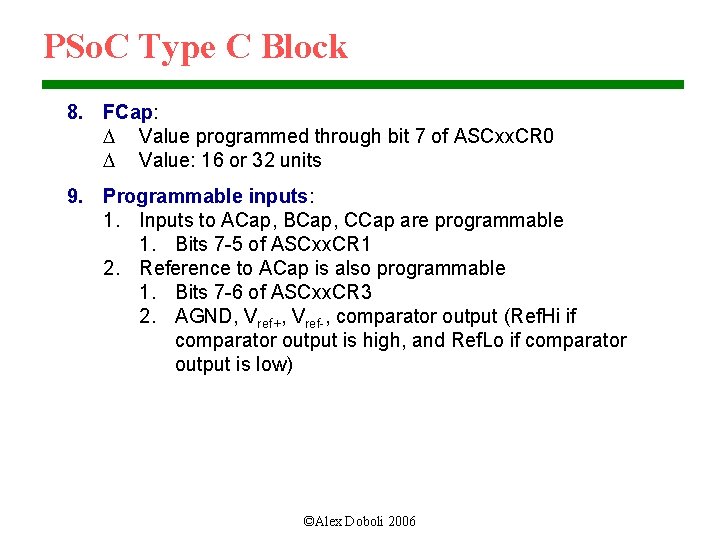

PSo. C Type C Block 8. FCap: D Value programmed through bit 7 of ASCxx. CR 0 D Value: 16 or 32 units 9. Programmable inputs: 1. Inputs to ACap, BCap, CCap are programmable 1. Bits 7 -5 of ASCxx. CR 1 2. Reference to ACap is also programmable 1. Bits 7 -6 of ASCxx. CR 3 2. AGND, Vref+, Vref-, comparator output (Ref. Hi if comparator output is high, and Ref. Lo if comparator output is low) ©Alex Doboli 2006

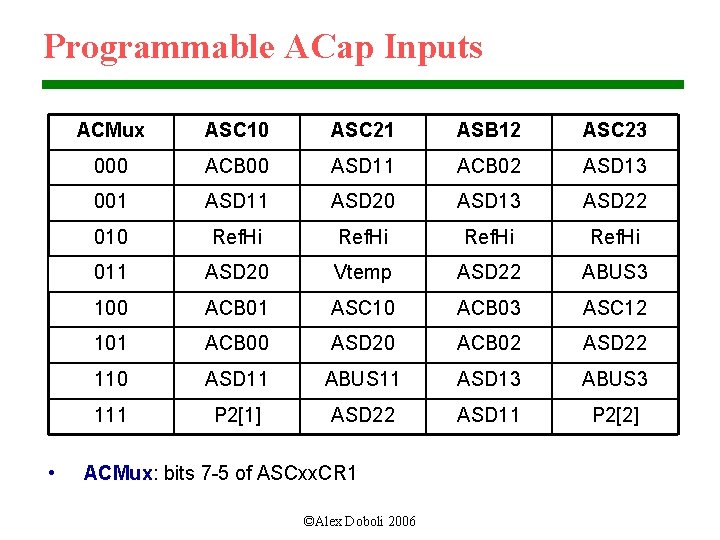

Programmable ACap Inputs • ACMux ASC 10 ASC 21 ASB 12 ASC 23 000 ACB 00 ASD 11 ACB 02 ASD 13 001 ASD 11 ASD 20 ASD 13 ASD 22 010 Ref. Hi 011 ASD 20 Vtemp ASD 22 ABUS 3 100 ACB 01 ASC 10 ACB 03 ASC 12 101 ACB 00 ASD 20 ACB 02 ASD 22 110 ASD 11 ABUS 11 ASD 13 ABUS 3 111 P 2[1] ASD 22 ASD 11 P 2[2] ACMux: bits 7 -5 of ASCxx. CR 1 ©Alex Doboli 2006

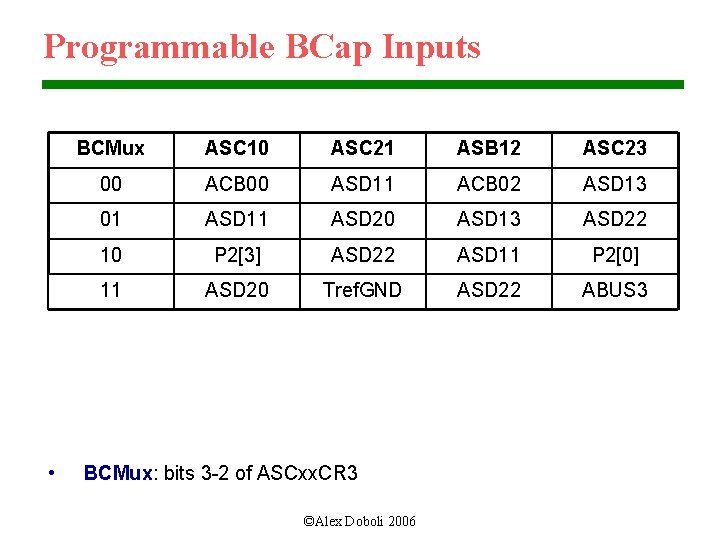

Programmable BCap Inputs • BCMux ASC 10 ASC 21 ASB 12 ASC 23 00 ACB 00 ASD 11 ACB 02 ASD 13 01 ASD 11 ASD 20 ASD 13 ASD 22 10 P 2[3] ASD 22 ASD 11 P 2[0] 11 ASD 20 Tref. GND ASD 22 ABUS 3 BCMux: bits 3 -2 of ASCxx. CR 3 ©Alex Doboli 2006

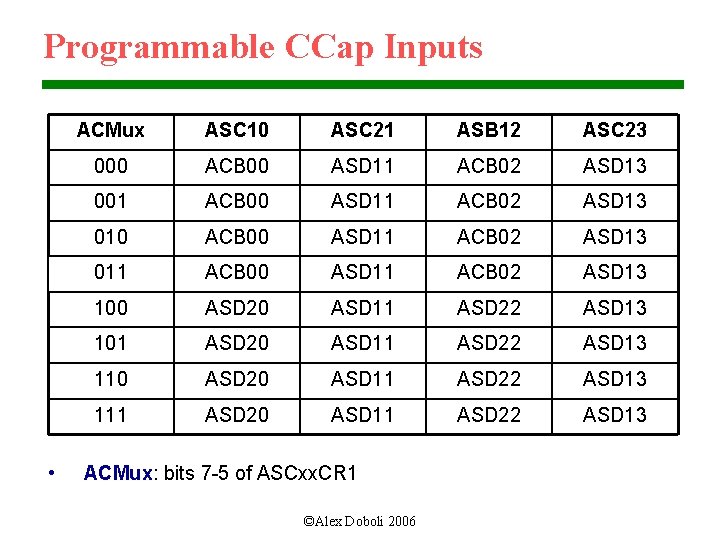

Programmable CCap Inputs • ACMux ASC 10 ASC 21 ASB 12 ASC 23 000 ACB 00 ASD 11 ACB 02 ASD 13 001 ACB 00 ASD 11 ACB 02 ASD 13 010 ACB 00 ASD 11 ACB 02 ASD 13 011 ACB 00 ASD 11 ACB 02 ASD 13 100 ASD 20 ASD 11 ASD 22 ASD 13 101 ASD 20 ASD 11 ASD 22 ASD 13 110 ASD 20 ASD 11 ASD 22 ASD 13 111 ASD 20 ASD 11 ASD 22 ASD 13 ACMux: bits 7 -5 of ASCxx. CR 1 ©Alex Doboli 2006

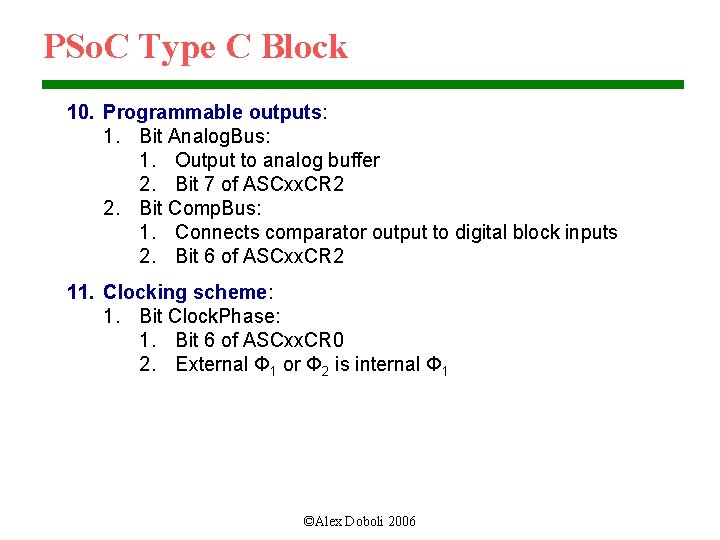

PSo. C Type C Block 10. Programmable outputs: 1. Bit Analog. Bus: 1. Output to analog buffer 2. Bit 7 of ASCxx. CR 2 2. Bit Comp. Bus: 1. Connects comparator output to digital block inputs 2. Bit 6 of ASCxx. CR 2 11. Clocking scheme: 1. Bit Clock. Phase: 1. Bit 6 of ASCxx. CR 0 2. External Φ 1 or Φ 2 is internal Φ 1 ©Alex Doboli 2006

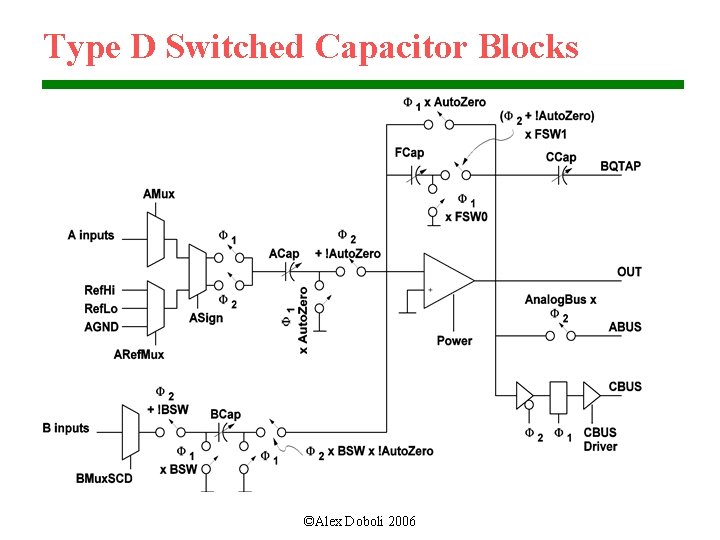

Type D Switched Capacitor Blocks ©Alex Doboli 2006

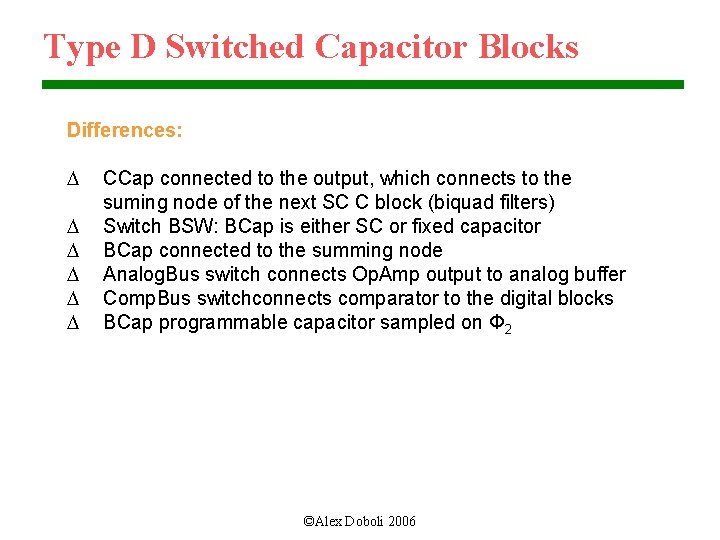

Type D Switched Capacitor Blocks Differences: D D D CCap connected to the output, which connects to the suming node of the next SC C block (biquad filters) Switch BSW: BCap is either SC or fixed capacitor BCap connected to the summing node Analog. Bus switch connects Op. Amp output to analog buffer Comp. Bus switchconnects comparator to the digital blocks BCap programmable capacitor sampled on Φ 2 ©Alex Doboli 2006

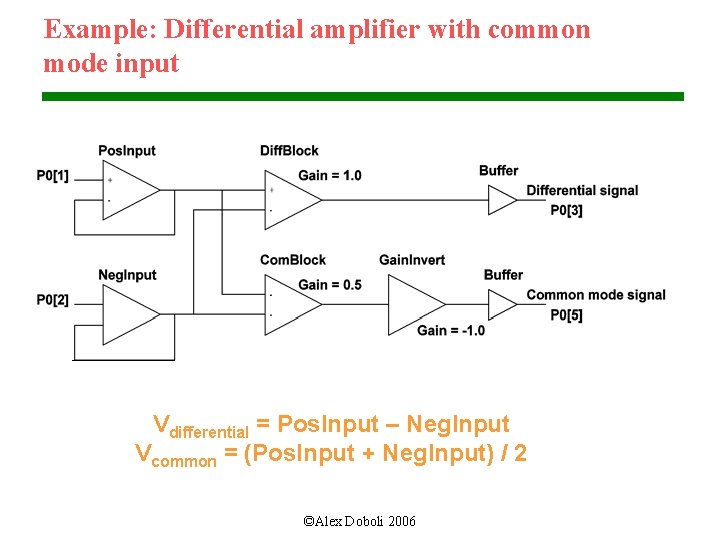

Example: Differential amplifier with common mode input Vdifferential = Pos. Input – Neg. Input Vcommon = (Pos. Input + Neg. Input) / 2 ©Alex Doboli 2006

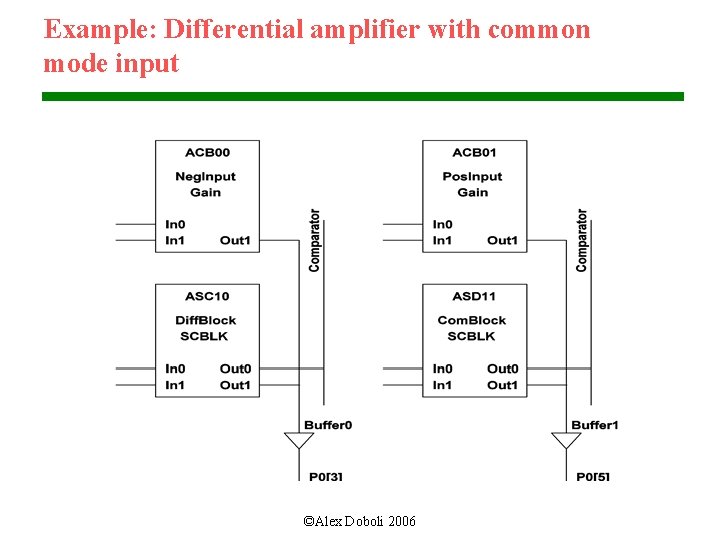

Example: Differential amplifier with common mode input ©Alex Doboli 2006

Analog to Digital Conversion ©Alex Doboli 2006

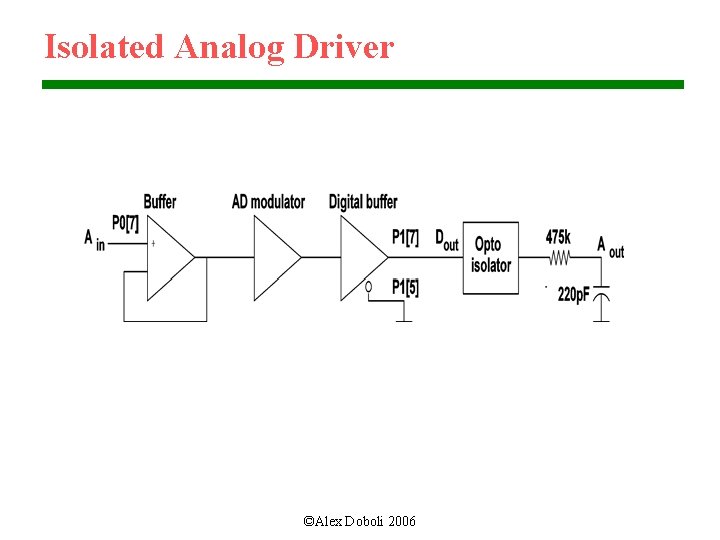

Isolated Analog Driver ©Alex Doboli 2006

- Slides: 36