SWG Competitive Project Office Introduction to IBMs System

SWG Competitive Project Office Introduction to IBM’s System z Hardware Architecture

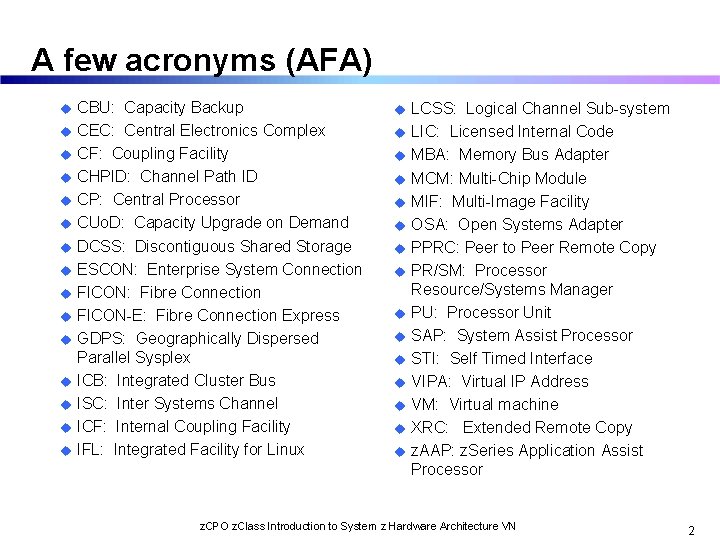

A few acronyms (AFA) u u u u CBU: Capacity Backup CEC: Central Electronics Complex CF: Coupling Facility CHPID: Channel Path ID CP: Central Processor CUo. D: Capacity Upgrade on Demand DCSS: Discontiguous Shared Storage ESCON: Enterprise System Connection FICON: Fibre Connection FICON-E: Fibre Connection Express GDPS: Geographically Dispersed Parallel Sysplex ICB: Integrated Cluster Bus ISC: Inter Systems Channel ICF: Internal Coupling Facility IFL: Integrated Facility for Linux u u u u LCSS: Logical Channel Sub-system LIC: Licensed Internal Code MBA: Memory Bus Adapter MCM: Multi-Chip Module MIF: Multi-Image Facility OSA: Open Systems Adapter PPRC: Peer to Peer Remote Copy PR/SM: Processor Resource/Systems Manager PU: Processor Unit SAP: System Assist Processor STI: Self Timed Interface VIPA: Virtual IP Address VM: Virtual machine XRC: Extended Remote Copy z. AAP: z. Series Application Assist Processor z. CPO z. Class Introduction to System z Hardware Architecture VN 2

Key Terminology (a challenge) z. CPO z. Class Introduction to System z Hardware Architecture VN 4

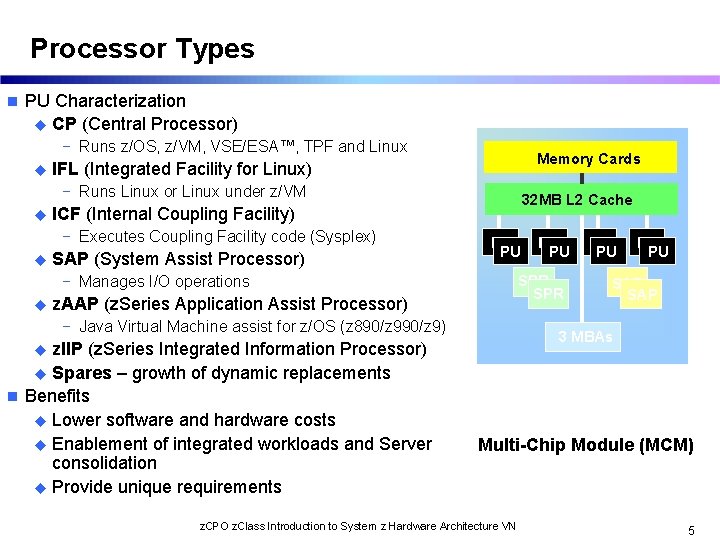

Processor Types n PU Characterization u CP (Central Processor) − Runs z/OS, z/VM, VSE/ESA™, TPF and Linux u Memory Cards IFL (Integrated Facility for Linux) − Runs Linux or Linux under z/VM u ICF (Internal Coupling Facility) − Executes Coupling Facility code (Sysplex) u 32 MB L 2 Cache SAP (System Assist Processor) PU PU − Manages I/O operations u SPR z. AAP (z. Series Application Assist Processor) − Java Virtual Machine assist for z/OS (z 890/z 9) z. IIP (z. Series Integrated Information Processor) u Spares – growth of dynamic replacements n Benefits u Lower software and hardware costs u Enablement of integrated workloads and Server consolidation u Provide unique requirements PU PU PU SAP 3 MBAs u Multi-Chip Module (MCM) z. CPO z. Class Introduction to System z Hardware Architecture VN 5

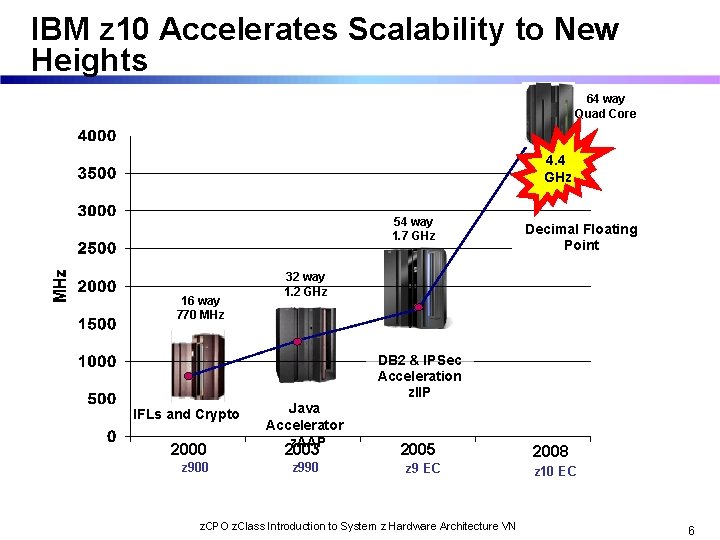

IBM z 10 Accelerates Scalability to New Heights 64 way Quad Core 4. 4 GHz 54 way 1. 7 GHz 16 way 770 MHz Decimal Floating Point 32 way 1. 2 GHz DB 2 & IPSec Acceleration z. IIP IFLs and Crypto 2000 z 900 Java Accelerator z. AAP 2003 z 990 2005 z 9 EC z. CPO z. Class Introduction to System z Hardware Architecture VN 2008 z 10 EC 6

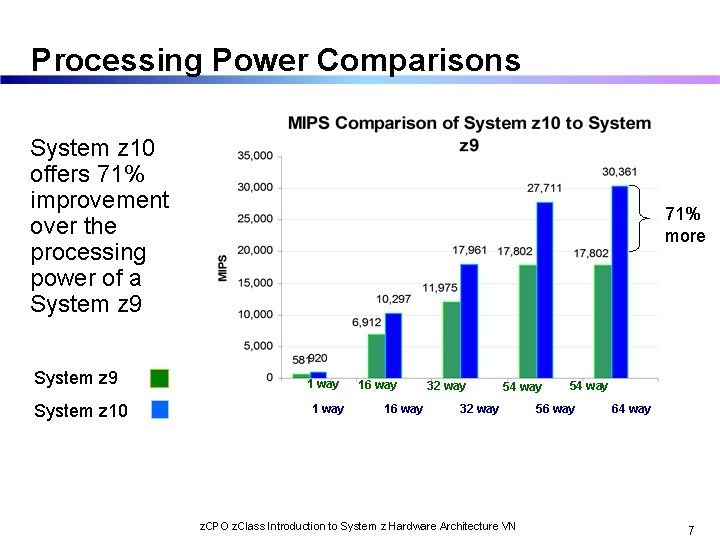

Processing Power Comparisons System z 10 offers 71% improvement over the processing power of a System z 9 System z 10 71% more 1 way 16 way 32 way 54 way 32 way z. CPO z. Class Introduction to System z Hardware Architecture VN 54 way 56 way 64 way 7

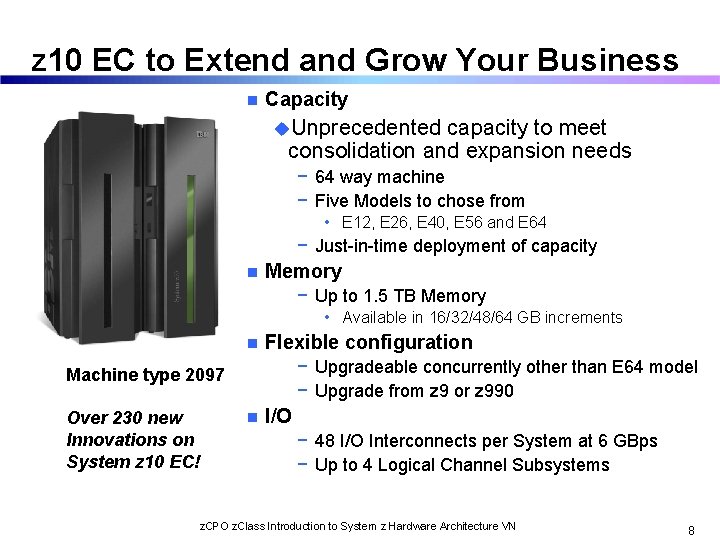

z 10 EC to Extend and Grow Your Business n Capacity u. Unprecedented capacity to meet consolidation and expansion needs − 64 way machine − Five Models to chose from • E 12, E 26, E 40, E 56 and E 64 − Just-in-time deployment of capacity n Memory − Up to 1. 5 TB Memory • Available in 16/32/48/64 GB increments n Flexible configuration − Upgradeable concurrently other than E 64 model − Upgrade from z 9 or z 990 Machine type 2097 Over 230 new Innovations on System z 10 EC! n I/O − 48 I/O Interconnects per System at 6 GBps − Up to 4 Logical Channel Subsystems z. CPO z. Class Introduction to System z Hardware Architecture VN 8

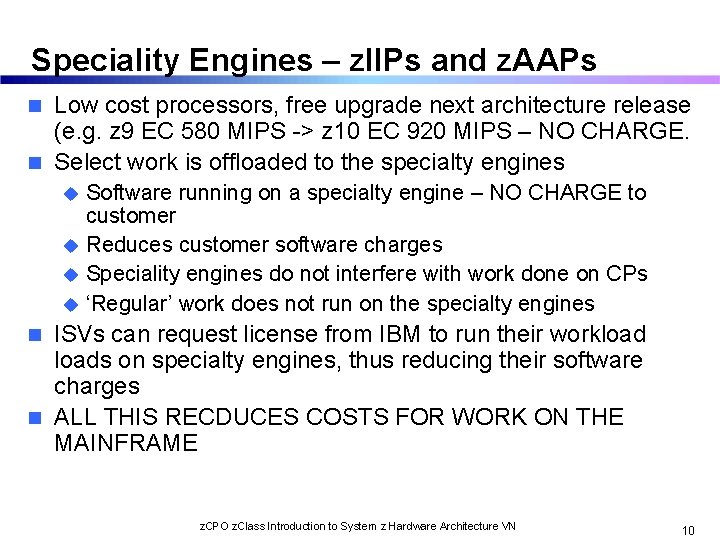

Speciality Engines – z. IIPs and z. AAPs Low cost processors, free upgrade next architecture release (e. g. z 9 EC 580 MIPS -> z 10 EC 920 MIPS – NO CHARGE. n Select work is offloaded to the specialty engines n Software running on a specialty engine – NO CHARGE to customer u Reduces customer software charges u Speciality engines do not interfere with work done on CPs u ‘Regular’ work does not run on the specialty engines u ISVs can request license from IBM to run their workloads on specialty engines, thus reducing their software charges n ALL THIS RECDUCES COSTS FOR WORK ON THE MAINFRAME n z. CPO z. Class Introduction to System z Hardware Architecture VN 10

z. AAPs – not just for Java Anymore! More new application technology exploiters, more new benefits n z. AAP designed to help implement new application technologies on System z™ u Java™ was the first exploiter u z/OS XML System Services − Introduced with z/OS V 1. 9 and rolled back to V 1. 8 and V 1. 7. − DB 2 9 and Enterprise Cobol V 4. 1 are the first exploiters. u New function on z 10 EC may benefit Java performance − New z 10 processor chip design and more available server memory plus (in 2 Q 08) support for new decimal floating point on z 10 EC by Java Big. Decimal * u PLUS z. AAP price is same for z 10 EC as z 9 EC and we offer no charge MES upgrades when moving to new technology z. CPO z. Class Introduction to System z Hardware Architecture VN 11

z. IIPs –Not Just for DB 2 Anymore! n z. IIPs can help to integrate data across the enterprise u n Centralized data serving u n z. IIP is enabled for XML parsing, first to exploit this is inserting and saving DB 2 9 XML data over DRDA® (Distributed Remote Data. Base Architecture) Remote mirror u n z. IIP becomes an IPSec encryption engine helpful in creating highly secure connections in an enterprise Serving XML data u n First to exploit z. IIP were workloads such as BI, ERP, and CRM applications running on distributed servers with remote connectivity to DB 2® V 8 Network encryption u n Optimizing resources and lowering TCO for eligible data z. IIP becomes a data mirroring engine with z. IIP assisted z/OS Global Mirror function (z. GM, formerly XRC) helpful in reducing server utilization at Disaster Recovery site z/OS V 1. 8+ − (XRC stands for ‘Remote Copy’ for Disaster Recovery) Exploiting of z. IIPs by ISVs u u z. IIPs offer economics to help customers PLUS z. IIP price is same for z 10 EC as z 9 EC and we offer no charge upgrades when moving to new technology z. CPO z. Class Introduction to System z Hardware Architecture VN 12

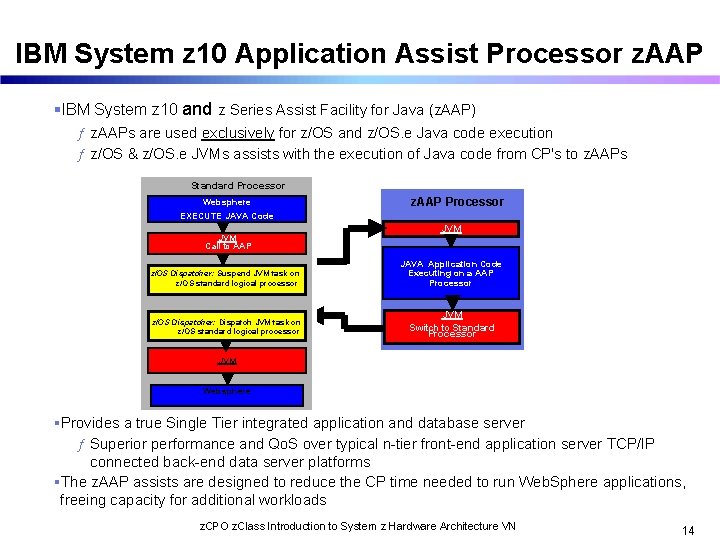

IBM System z 10 Application Assist Processor z. AAP IBM System z 10 and z Series Assist Facility for Java (z. AAP) ƒ z. AAPs are used exclusively for z/OS and z/OS. e Java code execution ƒ z/OS & z/OS. e JVMs assists with the execution of Java code from CP's to z. AAPs Standard Processor Websphere z. AAP Processor EXECUTE JAVA Code JVM Call to AAP JVM z/OS Dispatcher: Suspend JVM task on z/OS standard logical processor JAVA Application Code Executing on a AAP Processor z/OS Dispatcher: Dispatch JVM task on z/OS standard logical processor JVM Switch to Standard Processor JVM Websphere Provides a true Single Tier integrated application and database server ƒ Superior performance and Qo. S over typical n-tier front-end application server TCP/IP connected back-end data server platforms The z. AAP assists are designed to reduce the CP time needed to run Web. Sphere applications, freeing capacity for additional workloads z. CPO z. Class Introduction to System z Hardware Architecture VN 14

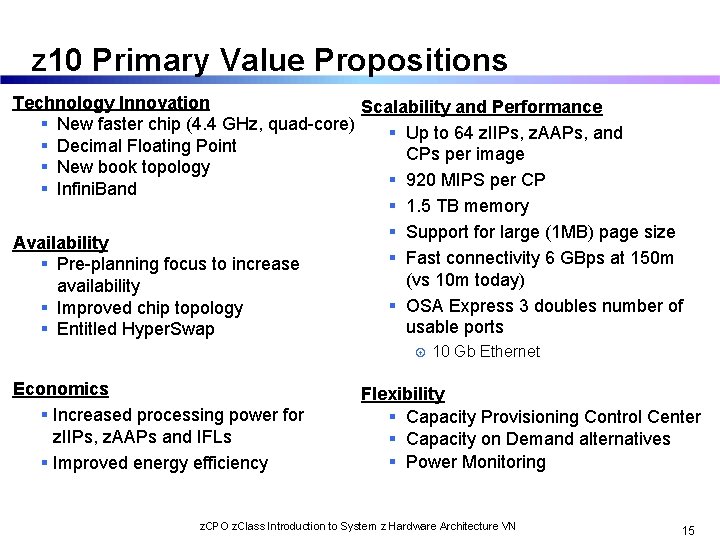

z 10 Primary Value Propositions Technology Innovation Scalability and Performance New faster chip (4. 4 GHz, quad-core) Up to 64 z. IIPs, z. AAPs, and Decimal Floating Point CPs per image New book topology 920 MIPS per CP Infini. Band 1. 5 TB memory Support for large (1 MB) page size Availability Fast connectivity 6 GBps at 150 m Pre-planning focus to increase (vs 10 m today) availability OSA Express 3 doubles number of Improved chip topology usable ports Entitled Hyper. Swap Economics Increased processing power for z. IIPs, z. AAPs and IFLs Improved energy efficiency 10 Gb Ethernet Flexibility Capacity Provisioning Control Center Capacity on Demand alternatives Power Monitoring z. CPO z. Class Introduction to System z Hardware Architecture VN 15

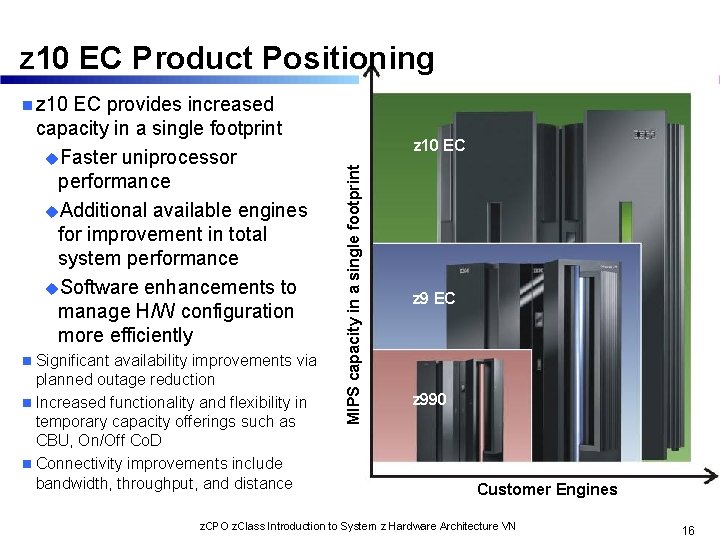

z 10 EC Product Positioning n z 10 n Significant availability improvements via planned outage reduction n Increased functionality and flexibility in temporary capacity offerings such as CBU, On/Off Co. D n Connectivity improvements include bandwidth, throughput, and distance z 10 EC MIPS capacity in a single footprint EC provides increased capacity in a single footprint u. Faster uniprocessor performance u. Additional available engines for improvement in total system performance u. Software enhancements to manage H/W configuration more efficiently z 9 EC z 990 Customer Engines z. CPO z. Class Introduction to System z Hardware Architecture VN 16

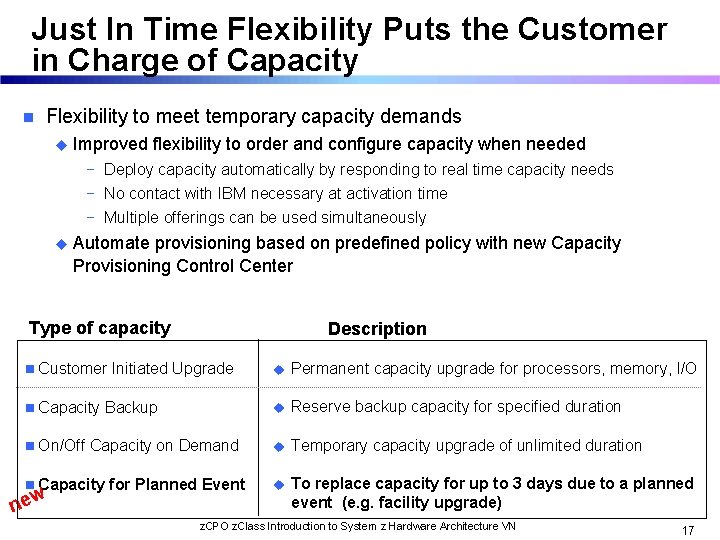

Just In Time Flexibility Puts the Customer in Charge of Capacity n Flexibility to meet temporary capacity demands u Improved flexibility to order and configure capacity when needed − Deploy capacity automatically by responding to real time capacity needs − No contact with IBM necessary at activation time − Multiple offerings can be used simultaneously u Automate provisioning based on predefined policy with new Capacity Provisioning Control Center Type of capacity n Customer n Capacity n On/Off Initiated Upgrade Backup Capacity on Demand n Capacity new Description for Planned Event u Permanent capacity upgrade for processors, memory, I/O u Reserve backup capacity for specified duration u Temporary capacity upgrade of unlimited duration u To replace capacity for up to 3 days due to a planned event (e. g. facility upgrade) z. CPO z. Class Introduction to System z Hardware Architecture VN 17

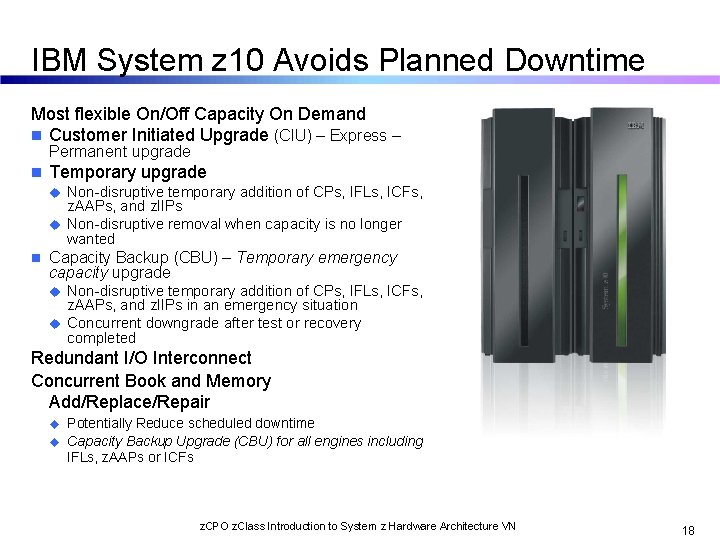

IBM System z 10 Avoids Planned Downtime Most flexible On/Off Capacity On Demand n Customer Initiated Upgrade (CIU) – Express – Permanent upgrade n Temporary upgrade u u n Non-disruptive temporary addition of CPs, IFLs, ICFs, z. AAPs, and z. IIPs Non-disruptive removal when capacity is no longer wanted Capacity Backup (CBU) – Temporary emergency capacity upgrade u u Non-disruptive temporary addition of CPs, IFLs, ICFs, z. AAPs, and z. IIPs in an emergency situation Concurrent downgrade after test or recovery completed Redundant I/O Interconnect Concurrent Book and Memory Add/Replace/Repair u u Potentially Reduce scheduled downtime Capacity Backup Upgrade (CBU) for all engines including IFLs, z. AAPs or ICFs z. CPO z. Class Introduction to System z Hardware Architecture VN 18

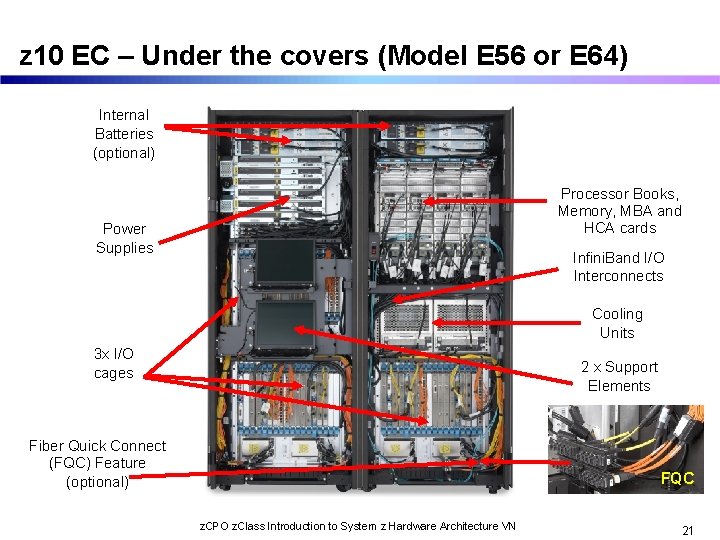

z 10 EC – Under the covers (Model E 56 or E 64) Internal Batteries (optional) Processor Books, Memory, MBA and HCA cards Power Supplies Infini. Band I/O Interconnects Cooling Units 3 x I/O cages 2 x Support Elements Fiber Quick Connect (FQC) Feature (optional) FQC z. CPO z. Class Introduction to System z Hardware Architecture VN 21

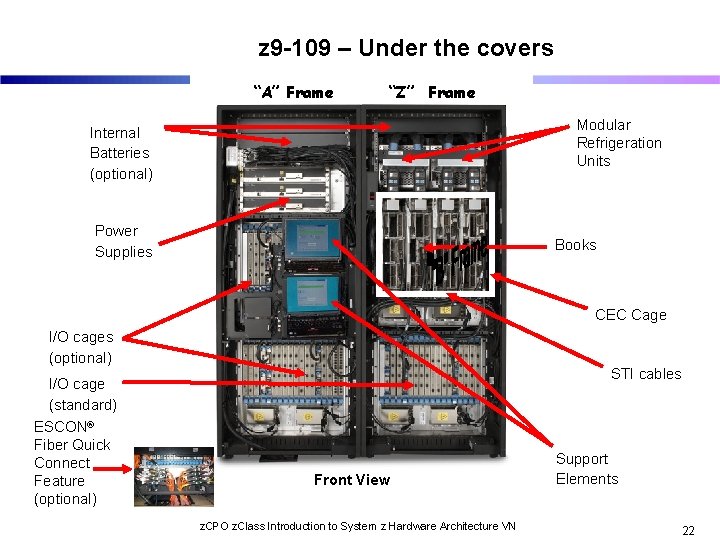

z 9 -109 – Under the covers “A” Frame “Z” Frame Modular Refrigeration Units Internal Batteries (optional) Power Supplies Books CEC Cage I/O cages (optional) STI cables I/O cage (standard) ESCON® Fiber Quick Connect Feature (optional) Front View z. CPO z. Class Introduction to System z Hardware Architecture VN Support Elements 22

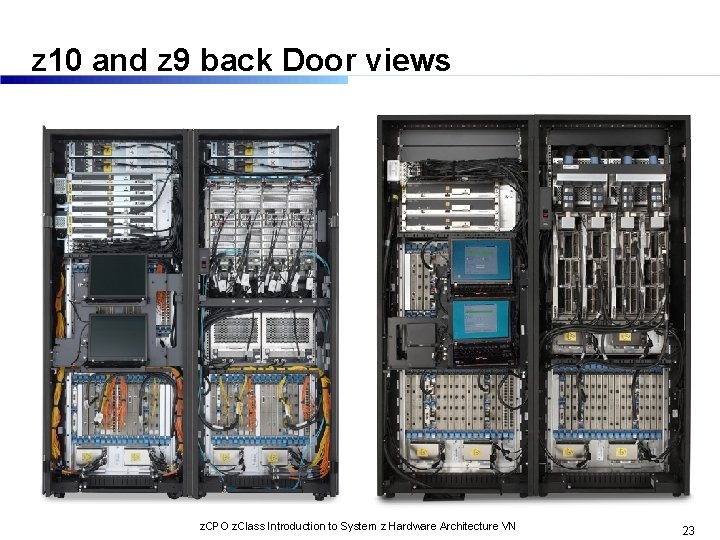

z 10 and z 9 back Door views z. CPO z. Class Introduction to System z Hardware Architecture VN 23

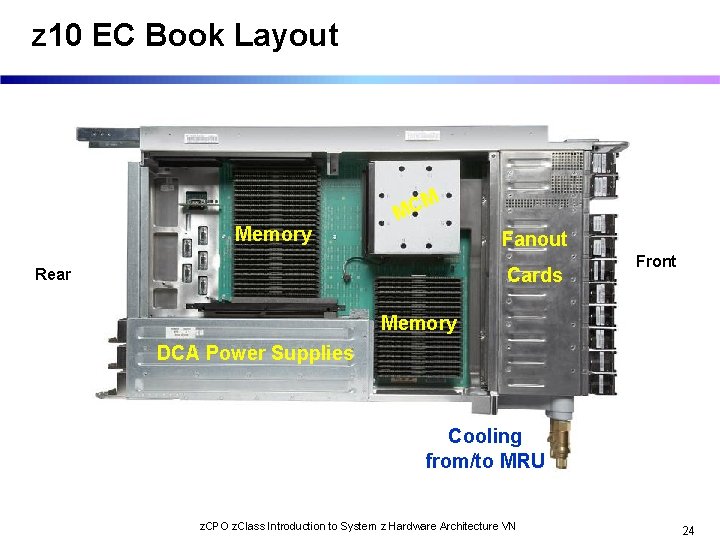

z 10 EC Book Layout Memory M C M Fanout Cards Rear Front Memory DCA Power Supplies Cooling from/to MRU z. CPO z. Class Introduction to System z Hardware Architecture VN 24

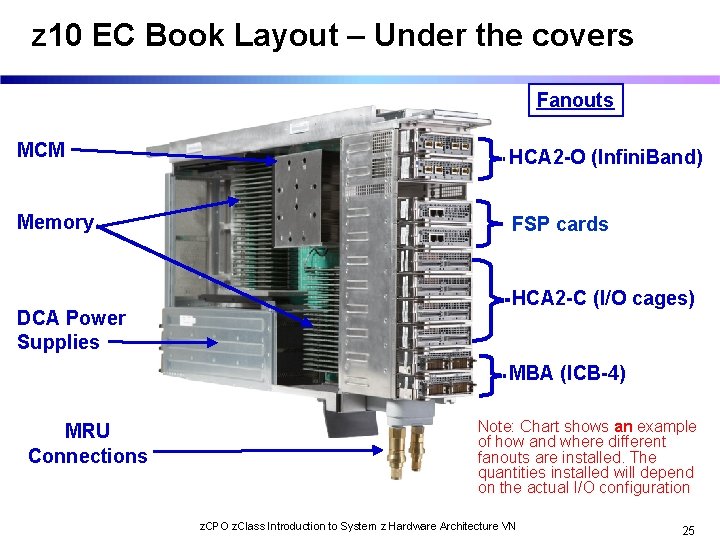

z 10 EC Book Layout – Under the covers Fanouts MCM HCA 2 -O (Infini. Band) Memory FSP cards DCA Power Supplies HCA 2 -C (I/O cages) MBA (ICB-4) MRU Connections Note: Chart shows an example of how and where different fanouts are installed. The quantities installed will depend on the actual I/O configuration z. CPO z. Class Introduction to System z Hardware Architecture VN 25

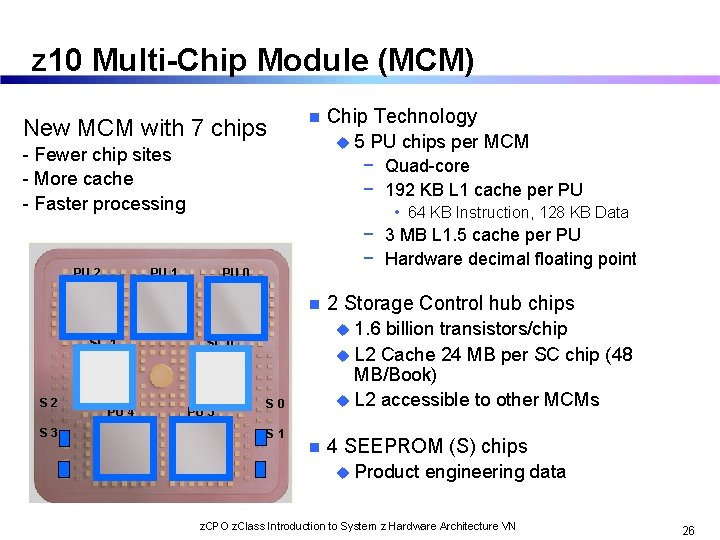

z 10 Multi-Chip Module (MCM) New MCM with 7 chips n u 5 PU chips per MCM − Quad-core − 192 KB L 1 cache per PU - Fewer chip sites - More cache - Faster processing PU 2 • 64 KB Instruction, 128 KB Data PU 1 − 3 MB L 1. 5 cache per PU − Hardware decimal floating point PU 0 n SC 1 S 2 S 3 PU 4 Chip Technology u 1. 6 billion transistors/chip u L 2 Cache 24 MB per SC chip (48 MB/Book) u L 2 accessible to other MCMs SC 0 PU 3 2 Storage Control hub chips S 0 S 1 n 4 SEEPROM (S) chips u Product engineering data z. CPO z. Class Introduction to System z Hardware Architecture VN 26

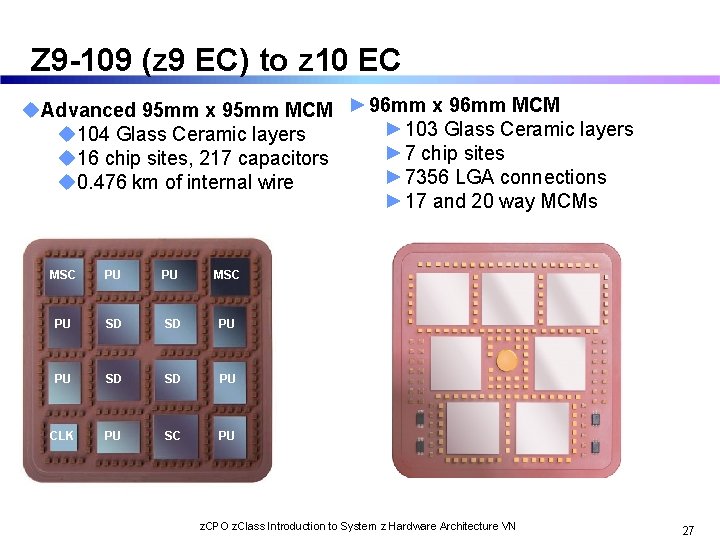

Z 9 -109 (z 9 EC) to z 10 EC u. Advanced 95 mm x 95 mm MCM ► 96 mm x 96 mm MCM ► 103 Glass Ceramic layers u 104 Glass Ceramic layers ► 7 chip sites u 16 chip sites, 217 capacitors ► 7356 LGA connections u 0. 476 km of internal wire ► 17 and 20 way MCMs MSC PU PU MSC PU SD SD PU CLK PU SC PU z. CPO z. Class Introduction to System z Hardware Architecture VN 27

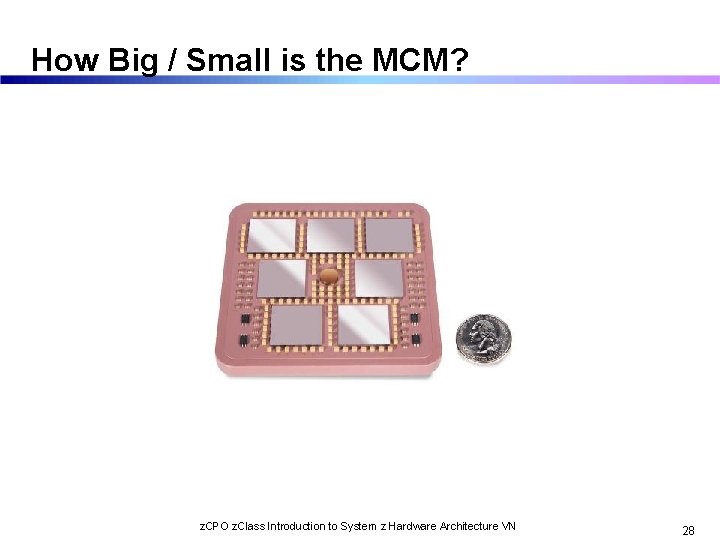

How Big / Small is the MCM? z. CPO z. Class Introduction to System z Hardware Architecture VN 28

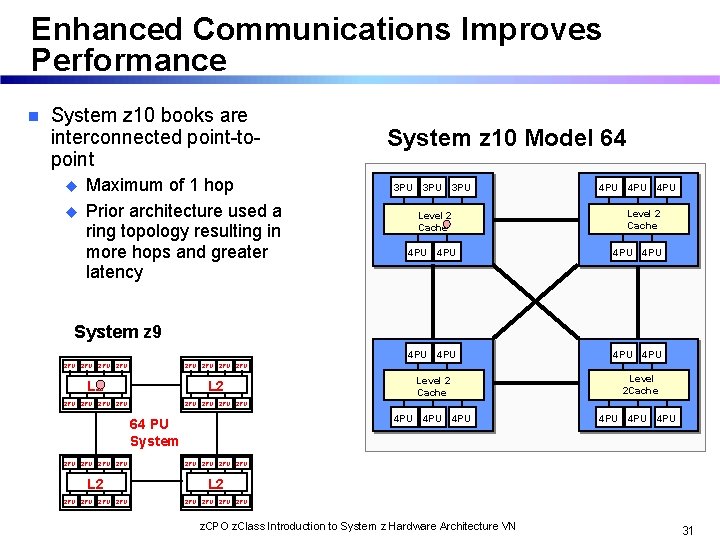

Enhanced Communications Improves Performance n System z 10 books are interconnected point-topoint u u Maximum of 1 hop Prior architecture used a ring topology resulting in more hops and greater latency System z 10 Model 64 3 PU 3 PU Level 2 Cache 4 PU 4 PU 4 PU Level 2 Cache Level 2 Cache 4 PU 4 PU 4 PU System z 9 2 PU 2 PU L 2 2 PU 2 PU 64 PU System 2 PU 2 PU L 2 2 PU 2 PU z. CPO z. Class Introduction to System z Hardware Architecture VN 31

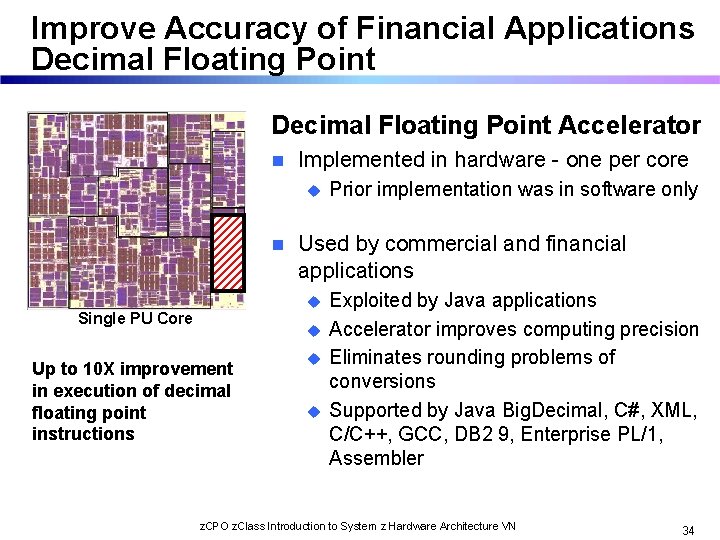

Improve Accuracy of Financial Applications Decimal Floating Point Accelerator n Implemented in hardware - one per core u n Used by commercial and financial applications u Single PU Core u Up to 10 X improvement in execution of decimal floating point instructions Prior implementation was in software only u u Exploited by Java applications Accelerator improves computing precision Eliminates rounding problems of conversions Supported by Java Big. Decimal, C#, XML, C/C++, GCC, DB 2 9, Enterprise PL/1, Assembler z. CPO z. Class Introduction to System z Hardware Architecture VN 34

Improve Performance with New Dispatching and Paging New dispatching algorithms n Hiper. Dispatch improves workload dispatching affinity n u Optimizes dispatching of work to the same physical processor • Access to hardware cache optimized when work is dispatched on the same physical processor • Reduces CPU-to-memory access time • Performance improvement – Reduces queuing delays and resultant latency n Large Page support for performance improvement • • New 1 MB page size versus 4 KB pages Page management more efficient Improves performance by increasing likelihood of buffer hits Designed for long running, memory intensive applications z. CPO z. Class Introduction to System z Hardware Architecture VN 36

z 10 EC Hiper. Dispatch n Hiper. Dispatch u Dispatcher u Vertical – z 10 EC unique function Affinity (DA) - New z/OS Dispatcher CPU Management (VCM) - New PR/SM Support n Hardware cache optimization occurs when a given unit of work is consistently dispatched on the same physical CPU u Up till now software, hardware, and firmware have had pride in the fact of how independent they were from each other u Non-Uniform-Memory-Access has forced a paradigm change u CPUs have different distance-to-memory attributes u Memory accesses can take a number of cycles depending upon cache level / local or remote repository accessed n The entire z 10 EC hardware/firmware/OS stack now tightly collaborates to obtain the hardware’s full potential z. CPO z. Class Introduction to System z Hardware Architecture VN 37

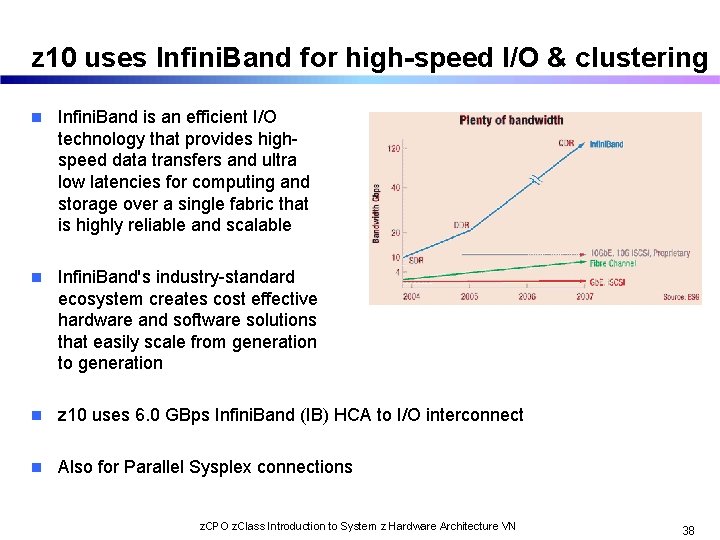

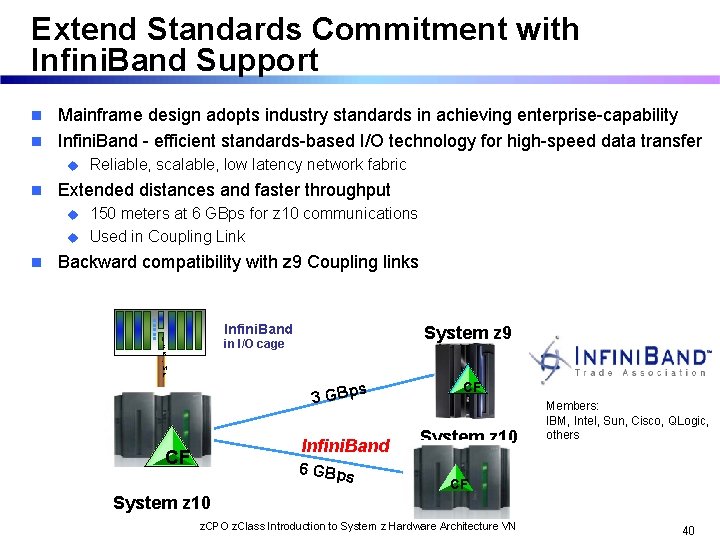

z 10 uses Infini. Band for high-speed I/O & clustering n Infini. Band is an efficient I/O technology that provides highspeed data transfers and ultra low latencies for computing and storage over a single fabric that is highly reliable and scalable n Infini. Band's industry-standard ecosystem creates cost effective hardware and software solutions that easily scale from generation to generation n z 10 uses 6. 0 GBps Infini. Band (IB) HCA to I/O interconnect n Also for Parallel Sysplex connections z. CPO z. Class Introduction to System z Hardware Architecture VN 38

Extend Standards Commitment with Infini. Band Support Mainframe design adopts industry standards in achieving enterprise-capability n Infini. Band - efficient standards-based I/O technology for high-speed data transfer n u n Extended distances and faster throughput u u n Reliable, scalable, low latency network fabric 150 meters at 6 GBps for z 10 communications Used in Coupling Link Backward compatibility with z 9 Coupling links Infini. Band I F B M P System z 9 in I/O cage s 3 GBp Infini. Band CF 6 GBps CF System z 10 Members: IBM, Intel, Sun, Cisco, QLogic, others CF System z 10 z. CPO z. Class Introduction to System z Hardware Architecture VN 40

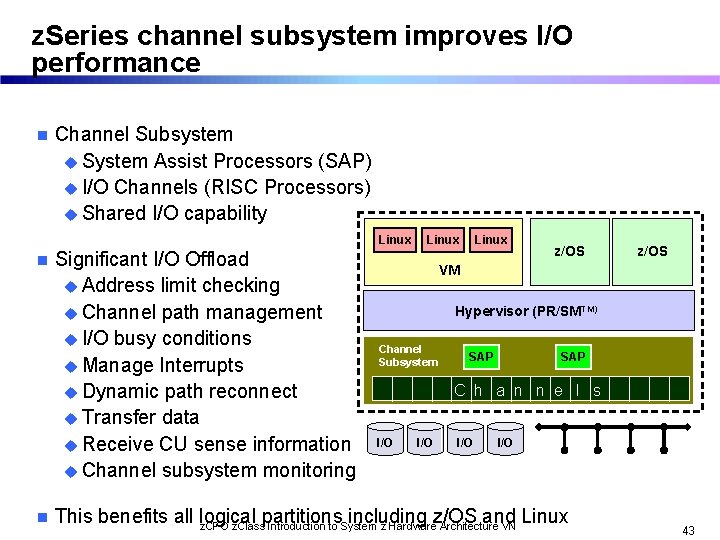

z. Series channel subsystem improves I/O performance n Channel Subsystem u System Assist Processors (SAP) u I/O Channels (RISC Processors) u Shared I/O capability Linux n n Significant I/O Offload u Address limit checking u Channel path management u I/O busy conditions u Manage Interrupts u Dynamic path reconnect u Transfer data u Receive CU sense information u Channel subsystem monitoring Linux z/OS VM Hypervisor (PR/SMTM) Channel Subsystem SAP C h a n n e l s I/O I/O This benefits all logical partitions including z/OS and Linux z. CPO z. Class Introduction to System z Hardware Architecture VN 43

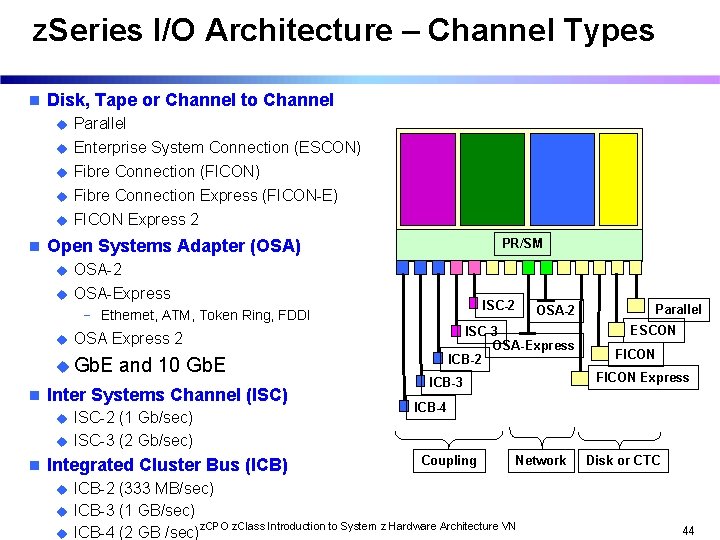

z. Series I/O Architecture – Channel Types n n Disk, Tape or Channel to Channel u Parallel u Enterprise System Connection (ESCON) u Fibre Connection (FICON) u Fibre Connection Express (FICON-E) u FICON Express 2 Open Systems Adapter (OSA) u u PR/SM OSA-2 OSA-Express ISC-2 − Ethernet, ATM, Token Ring, FDDI u n and 10 Gb. E Inter Systems Channel (ISC) u ISC-2 (1 Gb/sec) ISC-3 (2 Gb/sec) Integrated Cluster Bus (ICB) u u u ISC-3 OSA-Express ICB-2 OSA Express 2 u Gb. E OSA-2 Parallel ESCON FICON Express ICB-3 ICB-4 Coupling Network ICB-2 (333 MB/sec) ICB-3 (1 GB/sec) ICB-4 (2 GB /sec)z. CPO z. Class Introduction to System z Hardware Architecture VN Disk or CTC 44

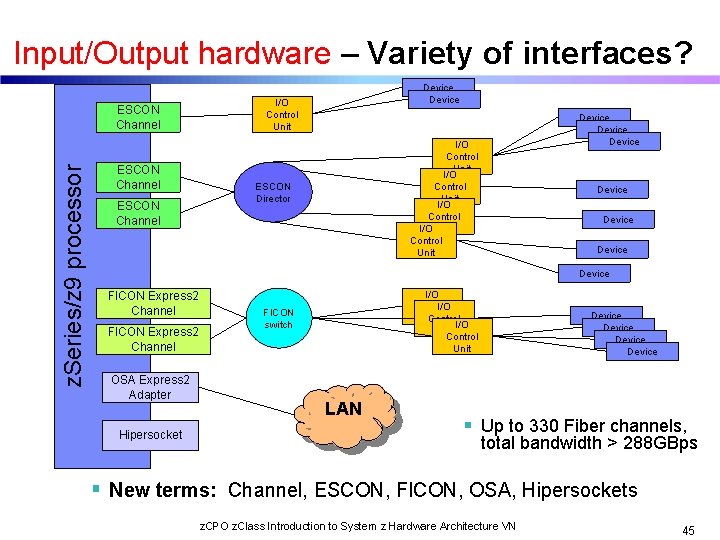

Input/Output hardware – Variety of interfaces? z. Series/z 9 processor ESCON Channel Device I/O Control Unit Device I/O Control Unit I/O Control I/O Unit Control Unit ESCON Director Device FICON Express 2 Channel OSA Express 2 Adapter Hipersocket I/O Control Unit I/O Unit Control Unit FICON switch LAN Device Up to 330 Fiber channels, total bandwidth > 288 GBps New terms: Channel, ESCON, FICON, OSA, Hipersockets z. CPO z. Class Introduction to System z Hardware Architecture VN 45

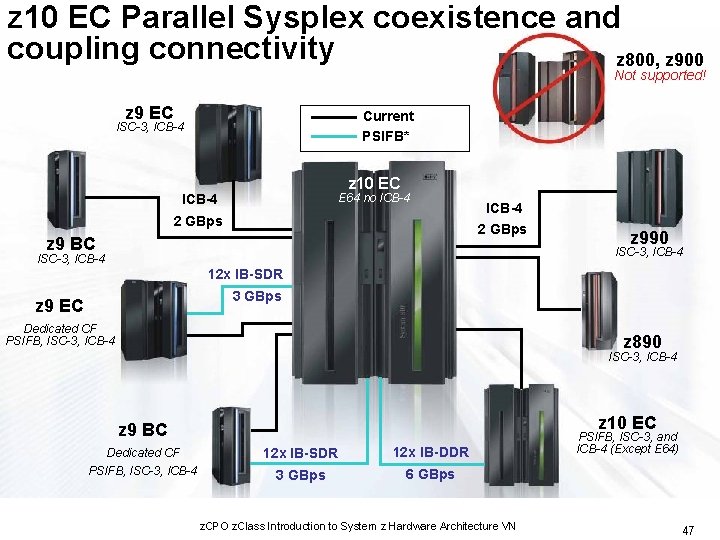

z 10 EC Parallel Sysplex coexistence and coupling connectivity z 800, z 900 Not supported! z 9 EC Current PSIFB* ISC-3, ICB-4 z 10 EC E 64 no ICB-4 2 GBps z 9 BC z 990 ISC-3, ICB-4 12 x IB-SDR 3 GBps z 9 EC Dedicated CF PSIFB, ISC-3, ICB-4 z 890 ISC-3, ICB-4 z 10 EC z 9 BC Dedicated CF 12 x IB-SDR 12 x IB-DDR PSIFB, ISC-3, ICB-4 3 GBps 6 GBps PSIFB, ISC-3, and ICB-4 (Except E 64) * All statements regarding IBM's future direction and intent are subject to change or withdrawal without notice, and represent goals and objectives only. z. CPO z. Class Introduction to System z Hardware Architecture VN 47

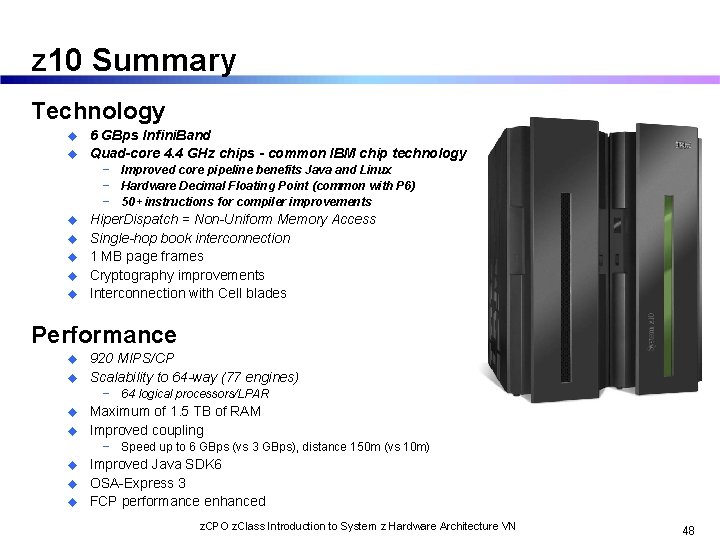

z 10 Summary Technology u u 6 GBps Infini. Band Quad-core 4. 4 GHz chips - common IBM chip technology − Improved core pipeline benefits Java and Linux − Hardware Decimal Floating Point (common with P 6) − 50+ instructions for compiler improvements u u u Hiper. Dispatch = Non-Uniform Memory Access Single-hop book interconnection 1 MB page frames Cryptography improvements Interconnection with Cell blades Performance u u 920 MIPS/CP Scalability to 64 -way (77 engines) − 64 logical processors/LPAR u u Maximum of 1. 5 TB of RAM Improved coupling − Speed up to 6 GBps (vs 3 GBps), distance 150 m (vs 10 m) u u u Improved Java SDK 6 OSA-Express 3 FCP performance enhanced z. CPO z. Class Introduction to System z Hardware Architecture VN 48

Some Processor Math n n n Clocking Cycle Time MIPS / BIPS /FIPS Virtual Storage Bandwidth z. CPO z. Class Introduction to System z Hardware Architecture VN 49

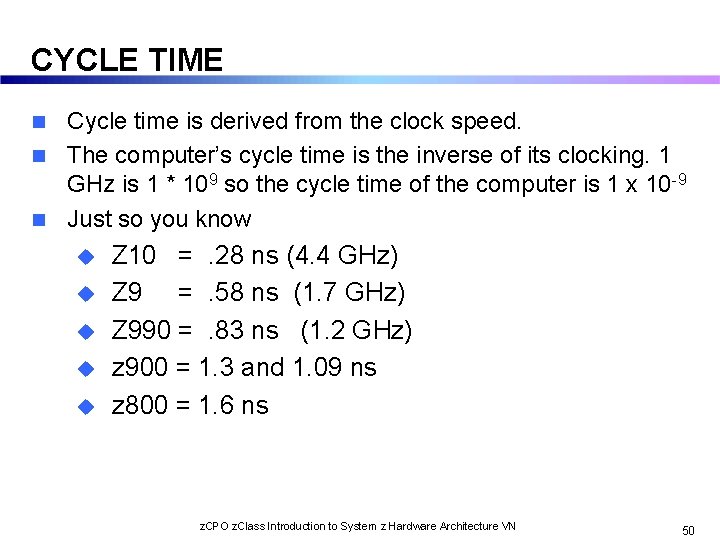

CYCLE TIME Cycle time is derived from the clock speed. n The computer’s cycle time is the inverse of its clocking. 1 GHz is 1 * 109 so the cycle time of the computer is 1 x 10 -9 n Just so you know n u u u Z 10 =. 28 ns (4. 4 GHz) Z 9 =. 58 ns (1. 7 GHz) Z 990 =. 83 ns (1. 2 GHz) z 900 = 1. 3 and 1. 09 ns z 800 = 1. 6 ns z. CPO z. Class Introduction to System z Hardware Architecture VN 50

MIPS – Millions of Instructions Per Second n n MIPs or BIPs are determined by benchmarks where you get instrumentation and can find out the AVERAGE cycles required to execute all the instructions used by the benchmark. You divide the clock speed (not the cycle time) by the average number of cycles / instruction. If the avg is 5 cycles and the GHz is 1. 7 x 109 the MIPs would be 340. u i. e. ((1. 7 x 109)/5) = 340 − The number of cycles per instruction depends on the workload type, e. g. transactions, vs. Batch or numerical intensive u If you have 54 processors, that gives you 18, 360 MIPs (roughly) − i. e. (340 x 54) = 18, 630 n Roughly (for 1 processor) u z 9 EC MIPS = 580 u z 10 EC MIPS = 920 z. CPO z. Class Introduction to System z Hardware Architecture VN 51

MHz to cycle time to MIPs once more n Let’s look at the relationships… n Hz is Hertz or cycles/second. Household current usually runs at 60 Hz or 60 cycles per second Take (for example) a computer that is rated at 400 MHz (at 400, 000 cycles per second). n u n Cycle time = 1/MHz. So the synchronization time (i. e. the cycle time) is 1/(4 x 106) (note 106 is one million). 1/MHz equals 2. 5 x 10 -9 or 2. 5 nano seconds (10 -9 is. 00001 … eight zeros and then the 1) MIPs is Million(s) of Instructions Per Second u u This value will represent the average number of instructions the processor can complete within a second. So MHz/(average number of cycles per instructions)=MIPs. If it is say 4 cycles average per instruction, then 400 MHz/4 equals 100 MIPS (in this example) If we have 6 tightly coupled processors, that would give us 6 * 100 or 600 MIPs That’s why MIPs also known as Meaningless Indicator of Performance… z. CPO z. Class Introduction to System z Hardware Architecture VN 52

Calibration – Cycle Time and Why Caches? n n n Equate 1 nano second (10 -9) to a second Then a millisecond (10 -3) is 1, 000 times slower… “How Much Slower? ”, you ask. That would be a million seconds or 11 days So the processor can run an instruction in a “second” but it will take about 11+ days to get data it needs from a disk to the processor… Houston, We have a Challenge! u ERGO: Cache is Us. z. CPO z. Class Introduction to System z Hardware Architecture VN 53

Calibration – Size of Virtual Storage n n n n Different from Real Storage. . u Virtual address are mapped to real storage u z/OS is a 64 bit operating system u Maximum virtual storage is 16 Exabytes (how big is that? ) If I am a megabyte tall (220), say 6 feet … And I grew to a gigabyte (230), I would be > mile high … really 6, 144 feet If I grew to an exabyte (260), I would be 1, 249, 445, 031 miles high… That would be about 6. 7 round trips to the sun (ours), or 1 round trip to Pluto… (2. 6 billion miles from earth) Multiply that times 16 to get the full 64 bit effect u I. E. 18, 446, 744, 073, 551, 616 So we have a lot of virtual storage… z 10 has 1. 5 TB of REAL storage 1, 649, 267, 441, 664 …. Exabytes are too much for my brain to handle … z. CPO z. Class Introduction to System z Hardware Architecture VN 54

Calibration – Bandwidth… If we equate a byte to a table spoon of beer, then the bandwidth of the z 9 is equivalent to 48 million kegs per second… n Bottoms up! n Of course this is not totally accurate, the z 9 bandwidth is a computed number… n u #STIs * STI bandwidth z. CPO z. Class Introduction to System z Hardware Architecture VN 55

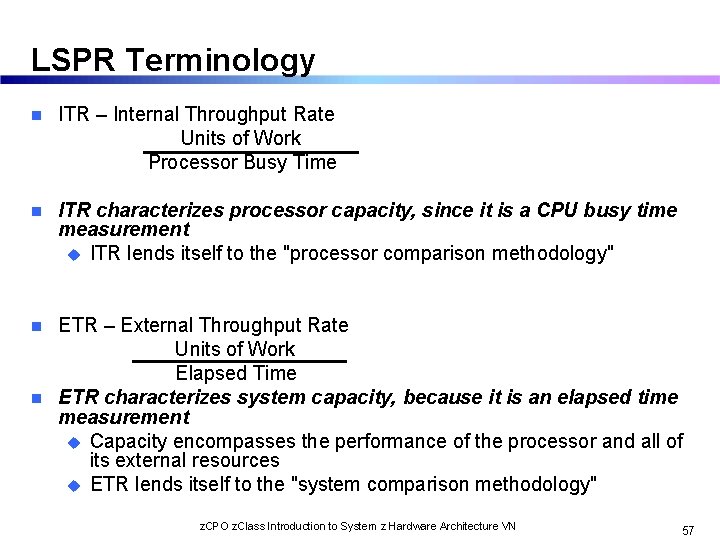

LSPR Terminology n ITR – Internal Throughput Rate Units of Work Processor Busy Time n ITR characterizes processor capacity, since it is a CPU busy time measurement u ITR lends itself to the "processor comparison methodology" ETR – External Throughput Rate Units of Work Elapsed Time n ETR characterizes system capacity, because it is an elapsed time measurement u Capacity encompasses the performance of the processor and all of its external resources u ETR lends itself to the "system comparison methodology" n z. CPO z. Class Introduction to System z Hardware Architecture VN 57

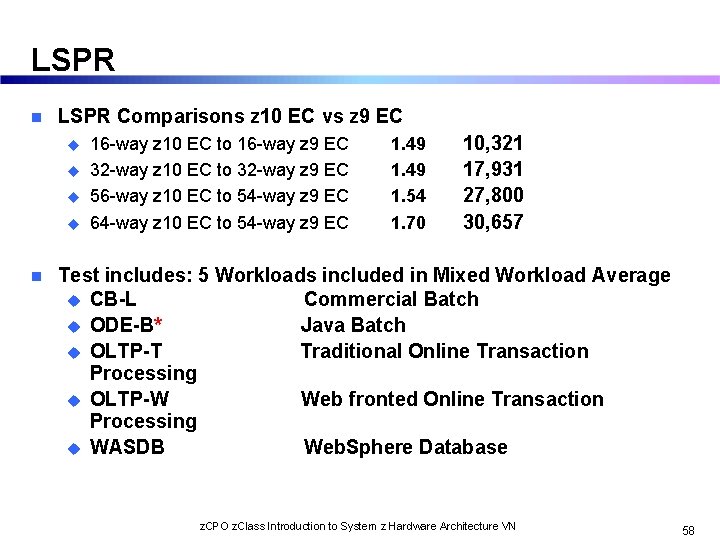

LSPR n LSPR Comparisons z 10 EC vs z 9 EC u u n 16 -way z 10 EC to 16 -way z 9 EC 32 -way z 10 EC to 32 -way z 9 EC 56 -way z 10 EC to 54 -way z 9 EC 64 -way z 10 EC to 54 -way z 9 EC 1. 49 1. 54 1. 70 10, 321 17, 931 27, 800 30, 657 Test includes: 5 Workloads included in Mixed Workload Average u CB-L Commercial Batch u ODE-B* Java Batch u OLTP-T Traditional Online Transaction Processing u OLTP-W Web fronted Online Transaction Processing u WASDB Web. Sphere Database z. CPO z. Class Introduction to System z Hardware Architecture VN 58

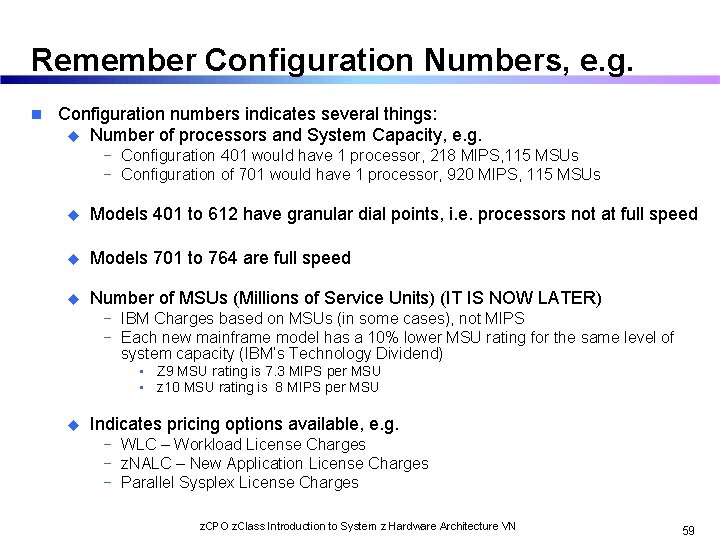

Remember Configuration Numbers, e. g. n Configuration numbers indicates several things: u Number of processors and System Capacity, e. g. − Configuration 401 would have 1 processor, 218 MIPS, 115 MSUs − Configuration of 701 would have 1 processor, 920 MIPS, 115 MSUs u Models 401 to 612 have granular dial points, i. e. processors not at full speed u Models 701 to 764 are full speed u Number of MSUs (Millions of Service Units) (IT IS NOW LATER) − IBM Charges based on MSUs (in some cases), not MIPS − Each new mainframe model has a 10% lower MSU rating for the same level of system capacity (IBM’s Technology Dividend) • Z 9 MSU rating is 7. 3 MIPS per MSU • z 10 MSU rating is 8 MIPS per MSU u Indicates pricing options available, e. g. − WLC – Workload License Charges − z. NALC – New Application License Charges − Parallel Sysplex License Charges z. CPO z. Class Introduction to System z Hardware Architecture VN 59

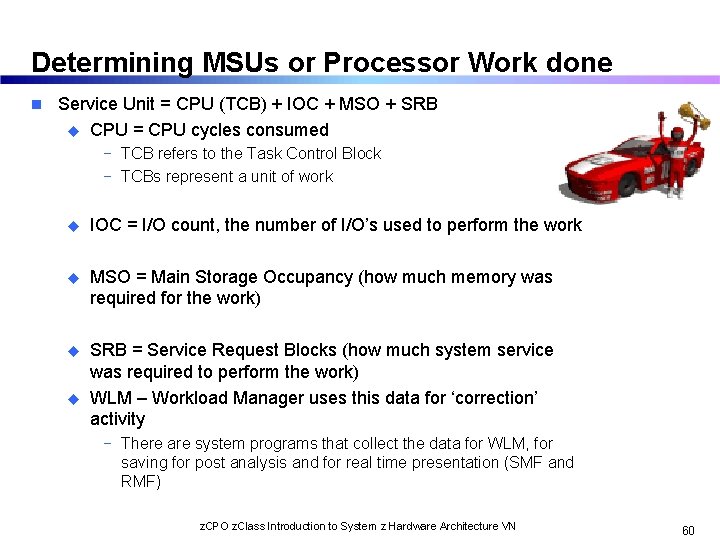

Determining MSUs or Processor Work done n Service Unit = CPU (TCB) + IOC + MSO + SRB u CPU = CPU cycles consumed − TCB refers to the Task Control Block − TCBs represent a unit of work u IOC = I/O count, the number of I/O’s used to perform the work u MSO = Main Storage Occupancy (how much memory was required for the work) u SRB = Service Request Blocks (how much system service was required to perform the work) WLM – Workload Manager uses this data for ‘correction’ activity u − There are system programs that collect the data for WLM, for saving for post analysis and for real time presentation (SMF and RMF) z. CPO z. Class Introduction to System z Hardware Architecture VN 60

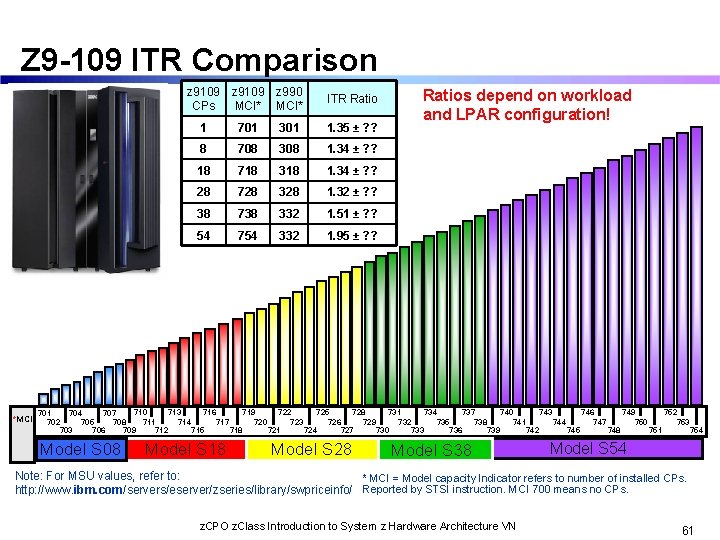

Z 9 -109 ITR Comparison z 9109 z 990 CPs MCI* *MCI ITR Ratio 1 701 301 1. 35 ± ? ? 8 708 308 1. 34 ± ? ? 18 718 318 1. 34 ± ? ? 28 728 328 1. 32 ± ? ? 38 738 332 1. 51 ± ? ? 54 754 332 1. 95 ± ? ? Ratios depend on workload and LPAR configuration! 710 713 716 719 722 725 728 731 734 737 740 743 746 749 752 701 704 707 702 705 708 711 714 717 720 723 726 729 732 735 738 741 744 747 750 753 706 709 712 715 718 721 724 727 730 733 736 739 742 745 748 751 754 Model S 08 Model S 18 Model S 28 Model S 38 Model S 54 Note: For MSU values, refer to: * MCI = Model capacity Indicator refers to number of installed CPs. http: //www. ibm. com/servers/eserver/zseries/library/swpriceinfo/ Reported by STSI instruction. MCI 700 means no CPs. z. CPO z. Class Introduction to System z Hardware Architecture VN 61

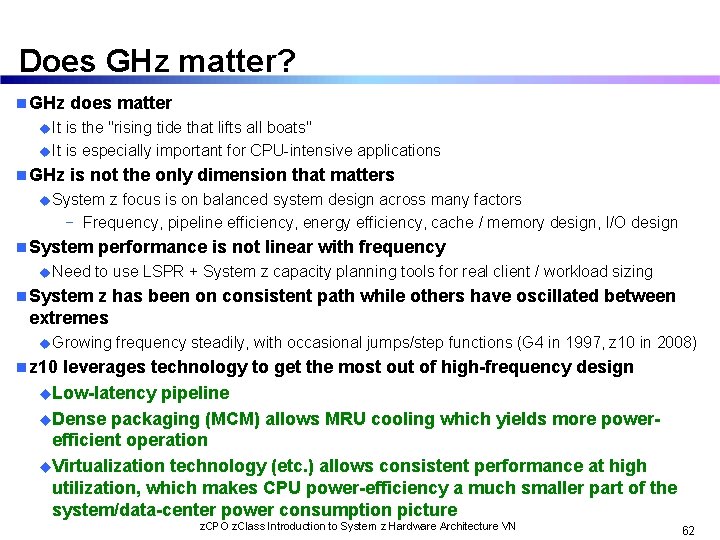

Does GHz matter? n GHz does matter u It is the "rising tide that lifts all boats" u It is especially important for CPU-intensive applications n GHz is not the only dimension that matters u System z focus is on balanced system design across many factors − Frequency, pipeline efficiency, energy efficiency, cache / memory design, I/O design n System u Need performance is not linear with frequency to use LSPR + System z capacity planning tools for real client / workload sizing n System z has been on consistent path while others have oscillated between extremes u Growing frequency steadily, with occasional jumps/step functions (G 4 in 1997, z 10 in 2008) n z 10 leverages technology to get the most out of high-frequency design u. Low-latency pipeline u. Dense packaging (MCM) allows MRU cooling which yields more powerefficient operation u. Virtualization technology (etc. ) allows consistent performance at high utilization, which makes CPU power-efficiency a much smaller part of the system/data-center power consumption picture z. CPO z. Class Introduction to System z Hardware Architecture VN 62

Summary n New super fast quad-core microprocessor at 4. 4 GHz n Innovation Decimal Floating Point u Enhanced enterprise data serving u n Industry-leading performance and availability n Continued cost effectiveness n New flexible configuration enhancements to simplify operations z. CPO z. Class Introduction to System z Hardware Architecture VN 63

- Slides: 48