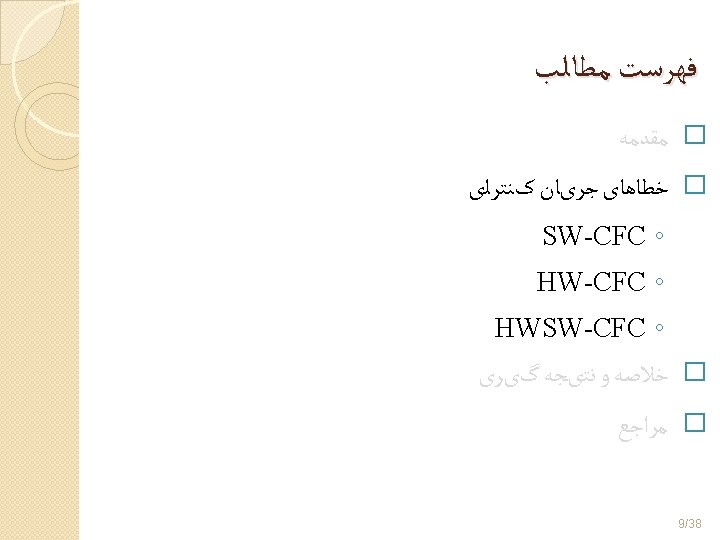

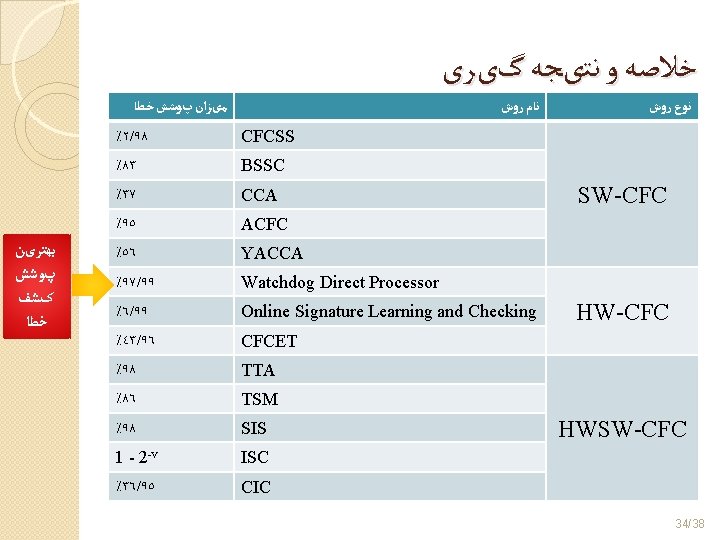

SWCFC CFC by software checking CFCSS Block signature

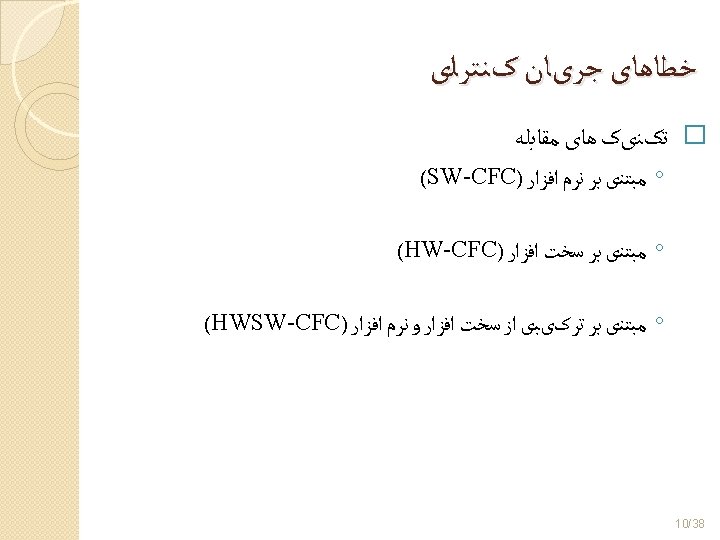

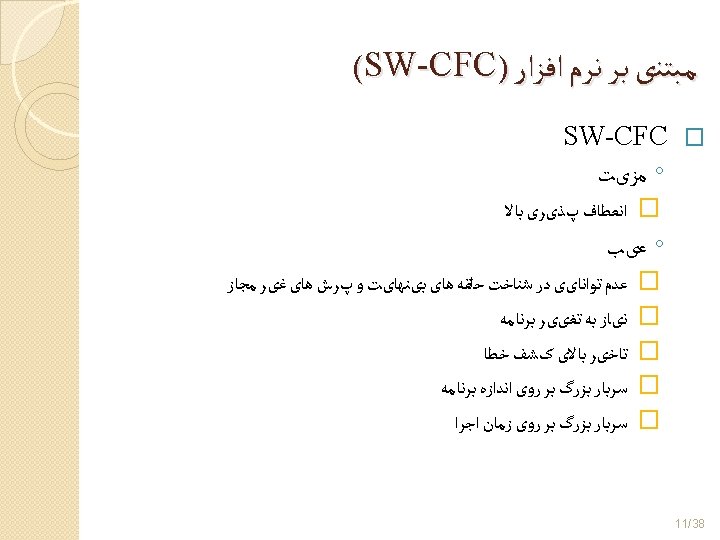

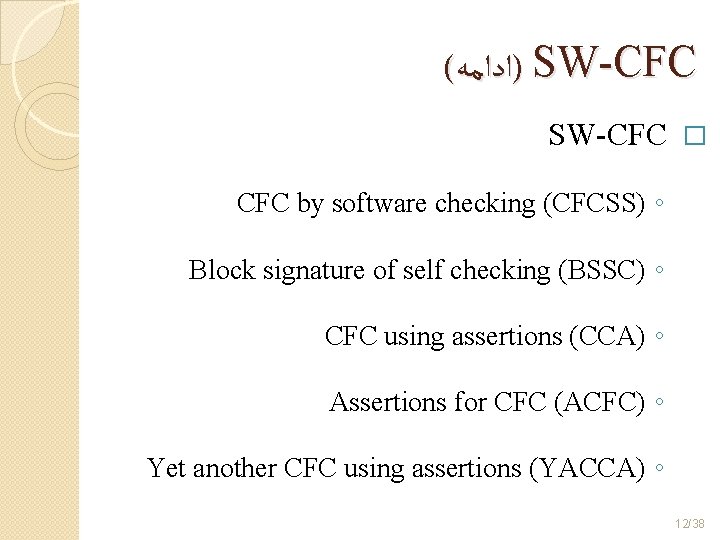

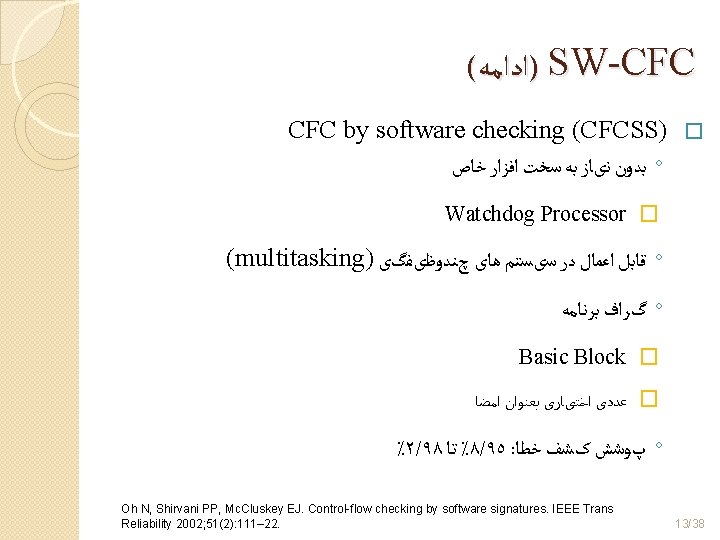

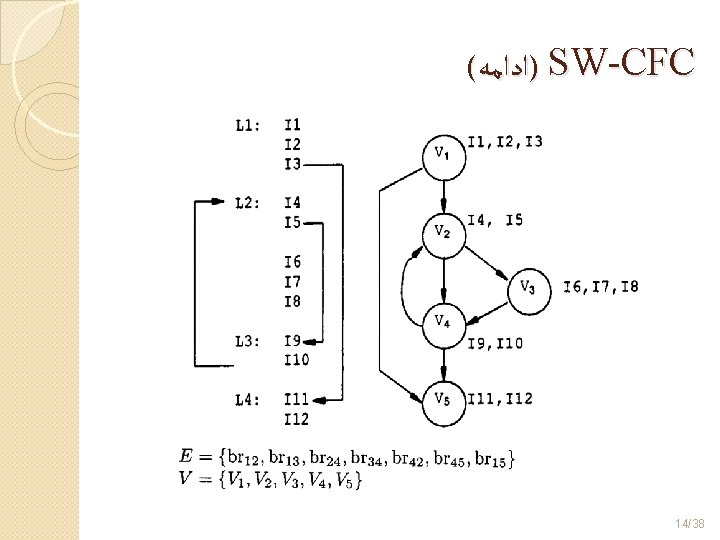

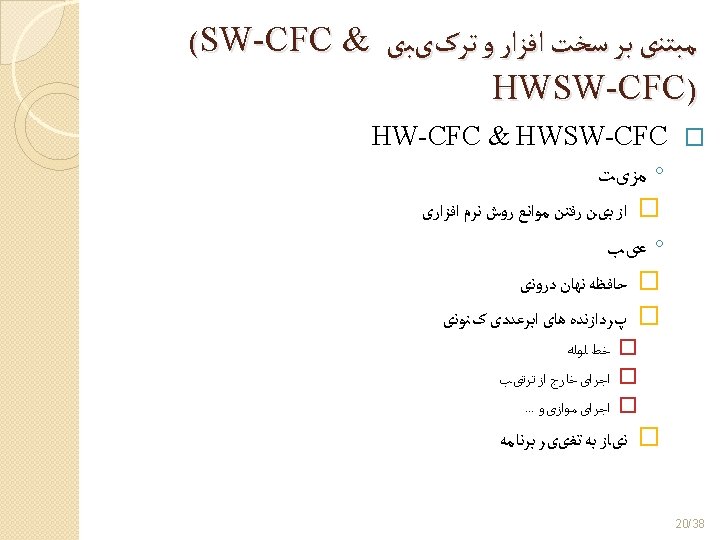

( )ﺍﺩﺍﻣﻪ SW-CFC � CFC by software checking (CFCSS) ◦ Block signature of self checking (BSSC) ◦ CFC using assertions (CCA) ◦ Assertions for CFC (ACFC) ◦ Yet another CFC using assertions (YACCA) ◦ 12/38

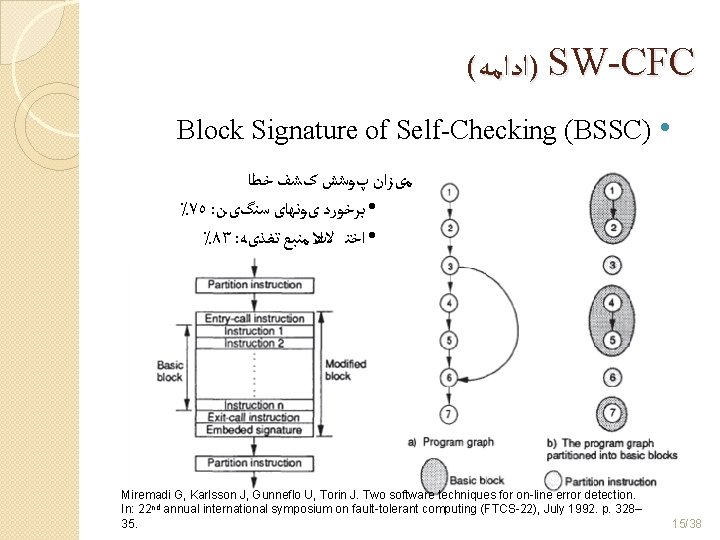

( )ﺍﺩﺍﻣﻪ SW-CFC Block Signature of Self-Checking (BSSC) • ﻣیﺰﺍﻥ پﻮﺷﺶ کﺸﻒ ﺧﻄﺎ ٪٧٥ : • ﺑﺮﺧﻮﺭﺩ یﻮﻧﻬﺎی ﺳﻨگیﻦ ٪٨٣ : ﻻﺕ ﻣﻨﺒﻊ ﺗﻐﺬیﻪ • ﺍﺧﺘ ﻼ Miremadi G, Karlsson J, Gunneflo U, Torin J. Two software techniques for on-line error detection. In: 22 nd annual international symposium on fault-tolerant computing (FTCS-22), July 1992. p. 328– 35. 15/38

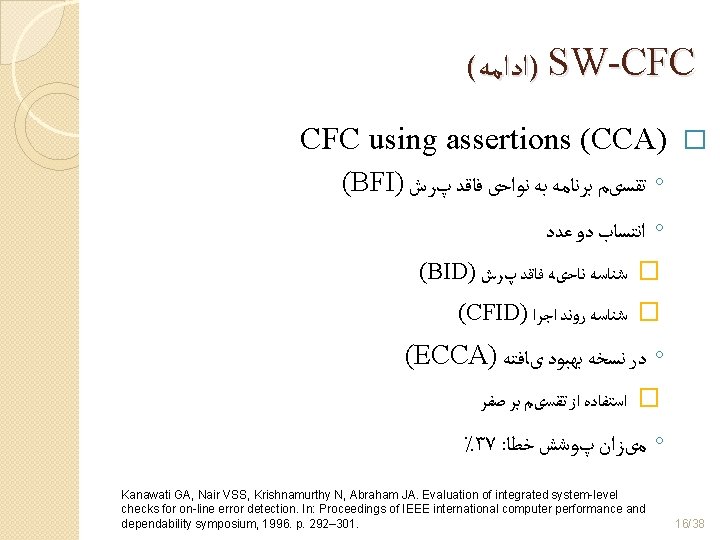

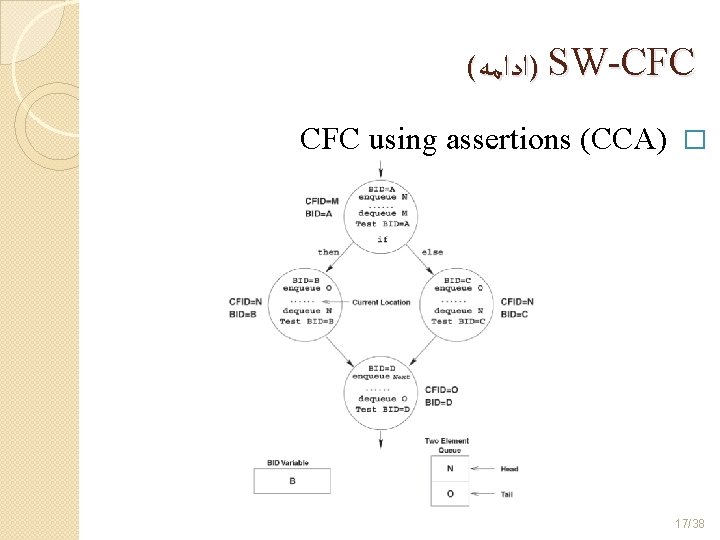

( )ﺍﺩﺍﻣﻪ SW-CFC using assertions (CCA) � (BFI) ◦ ﺗﻘﺴیﻢ ﺑﺮﻧﺎﻣﻪ ﺑﻪ ﻧﻮﺍﺣی ﻓﺎﻗﺪ پﺮﺵ ◦ ﺍﻧﺘﺴﺎﺏ ﺩﻭ ﻋﺪﺩ (BID) � ﺷﻨﺎﺳﻪ ﻧﺎﺣیﻪ ﻓﺎﻗﺪ پﺮﺵ (CFID) � ﺷﻨﺎﺳﻪ ﺭﻭﻧﺪ ﺍﺟﺮﺍ (ECCA) ◦ ﺩﺭ ﻧﺴﺨﻪ ﺑﻬﺒﻮﺩ یﺎﻓﺘﻪ � ﺍﺳﺘﻔﺎﺩﻩ ﺍﺯ ﺗﻘﺴیﻢ ﺑﺮ ﺻﻔﺮ ٪٣٧ : ◦ ﻣیﺰﺍﻥ پﻮﺷﺶ ﺧﻄﺎ Kanawati GA, Nair VSS, Krishnamurthy N, Abraham JA. Evaluation of integrated system-level checks for on-line error detection. In: Proceedings of IEEE international computer performance and dependability symposium, 1996. p. 292– 301. 16/38

( )ﺍﺩﺍﻣﻪ SW-CFC using assertions (CCA) � 17/38

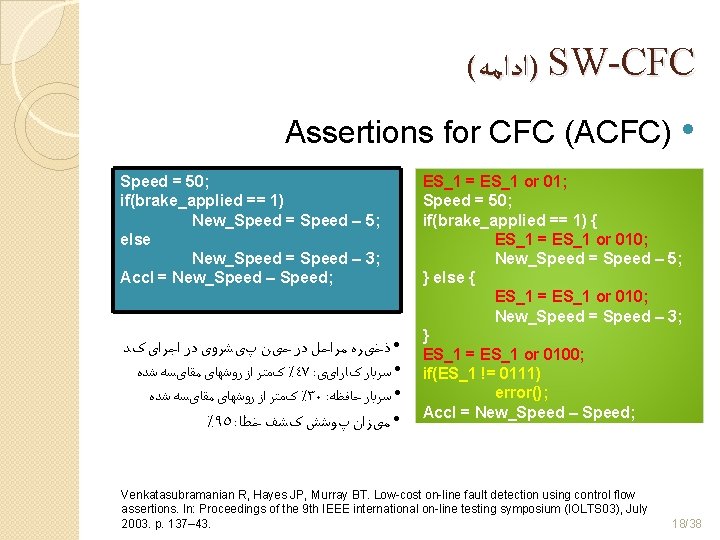

( )ﺍﺩﺍﻣﻪ SW-CFC Assertions for CFC (ACFC) • Speed = 50; if(brake_applied == 1) New_Speed = Speed – 5; else New_Speed = Speed – 3; Accl = New_Speed – Speed; • ﺫﺧیﺮﻩ ﻣﺮﺍﺣﻞ ﺩﺭ ﺣیﻦ پیﺸﺮﻭی ﺩﺭ ﺍﺟﺮﺍی کﺪ کﻤﺘﺮ ﺍﺯ ﺭﻭﺷﻬﺎی ﻣﻘﺎیﺴﻪ ﺷﺪﻩ ٪٤٧ : • ﺳﺮﺑﺎﺭ کﺎﺭﺍیی کﻤﺘﺮ ﺍﺯ ﺭﻭﺷﻬﺎی ﻣﻘﺎیﺴﻪ ﺷﺪﻩ ٪٣٠ : • ﺳﺮﺑﺎﺭ ﺣﺎﻓﻈﻪ ٪٩٥ : • ﻣیﺰﺍﻥ پﻮﺷﺶ کﺸﻒ ﺧﻄﺎ ES_1 = ES_1 or 01; Speed = 50; if(brake_applied == 1) { ES_1 = ES_1 or 010; New_Speed = Speed – 5; } else { ES_1 = ES_1 or 010; New_Speed = Speed – 3; } ES_1 = ES_1 or 0100; if(ES_1 != 0111) error(); Accl = New_Speed – Speed; Venkatasubramanian R, Hayes JP, Murray BT. Low-cost on-line fault detection using control flow assertions. In: Proceedings of the 9 th IEEE international on-line testing symposium (IOLTS 03), July 2003. p. 137– 43. 18/38

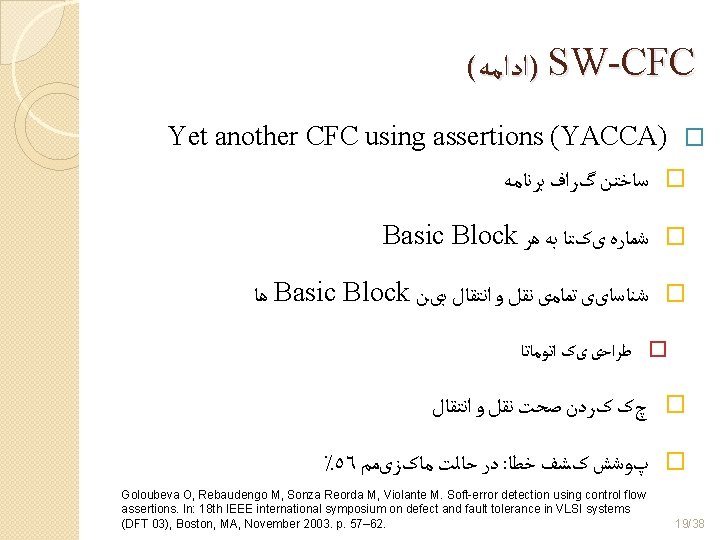

( )ﺍﺩﺍﻣﻪ SW-CFC Yet another CFC using assertions (YACCA) � � ﺳﺎﺧﺘﻦ گﺮﺍﻑ ﺑﺮﻧﺎﻣﻪ Basic Block � ﺷﻤﺎﺭﻩ یکﺘﺎ ﺑﻪ ﻫﺮ ﻫﺎ Basic Block � ﺷﻨﺎﺳﺎیی ﺗﻤﺎﻣی ﻧﻘﻞ ﻭ ﺍﻧﺘﻘﺎﻝ ﺑیﻦ � ﻃﺮﺍﺣی یک ﺍﺗﻮﻣﺎﺗﺎ � چک کﺮﺩﻥ ﺻﺤﺖ ﻧﻘﻞ ﻭ ﺍﻧﺘﻘﺎﻝ ٪٥٦ ﺩﺭ ﺣﺎﻟﺖ ﻣﺎکﺰیﻤﻢ : � پﻮﺷﺶ کﺸﻒ ﺧﻄﺎ Goloubeva O, Rebaudengo M, Sonza Reorda M, Violante M. Soft-error detection using control flow assertions. In: 18 th IEEE international symposium on defect and fault tolerance in VLSI systems (DFT 03), Boston, MA, November 2003. p. 57– 62. 19/38

( )ﺍﺩﺍﻣﻪ HW-CFC � Watchdog Direct Processor ◦ Online Signature Learning and Checking ◦ CFC by Execution Tracing (CFCET) ◦ 21/38

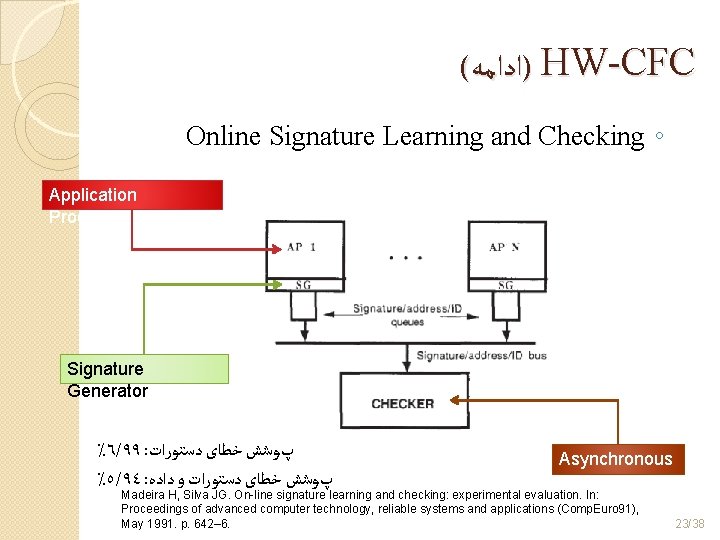

( )ﺍﺩﺍﻣﻪ HW-CFC Online Signature Learning and Checking ◦ Application Processor Signature Generator ٪٦/٩٩ : پﻮﺷﺶ ﺧﻄﺎی ﺩﺳﺘﻮﺭﺍﺕ ٪٥/٩٤ : پﻮﺷﺶ ﺧﻄﺎی ﺩﺳﺘﻮﺭﺍﺕ ﻭ ﺩﺍﺩﻩ Asynchronous Madeira H, Silva JG. On-line signature learning and checking: experimental evaluation. In: Proceedings of advanced computer technology, reliable systems and applications (Comp. Euro 91), May 1991. p. 642– 6. 23/38

( )ﺍﺩﺍﻣﻪ HW-CFC by Execution Tracing (CFCET) � ◦ گﺮﺍﻑ پﺮﺵ ﺑﺮﻧﺎﻣﻪ � ﻣﻘﺎیﺴﻪ ﺑﺎ گﺮﺍﻑ ﻣﺮﺟﻊ پﺮﺷﻬﺎ ◦ ﺳﺮﺑﺎﺭ ﺑﺮﻧﺎﻣﻪ ﺻﻔﺮ ◦ پﺎیپﻼیﻦ ﻭ ﺣﺎﻓﻈﻪ ﻧﻬﺎﻥ ٪٤٣/٩٦ : ◦ پﻮﺷﺶ ﺧﻄﺎ ﺗﻘﺮیﺒ ﺻﻔﺮ : ◦ ﺗﺎﺧیﺮ کﺸﻒ ﺧﻄﺎ Rajabzadeh A, Miremadi G. CFCET: A hardware-based control flow checking technique in COTS processors using execution tracing, Microelectronics Reliability 46 (2006), 2006, pp. 959 -972. 24/38

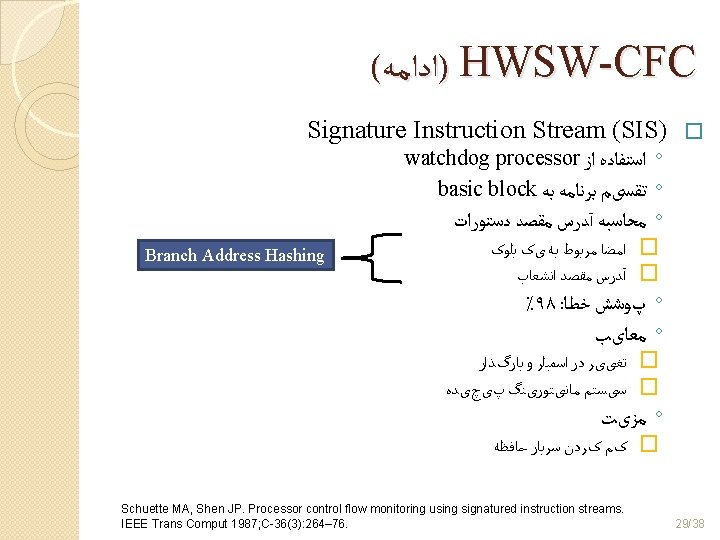

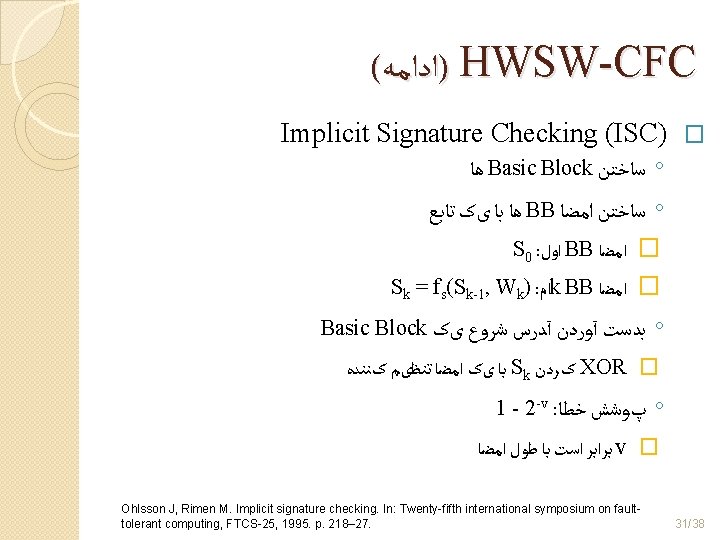

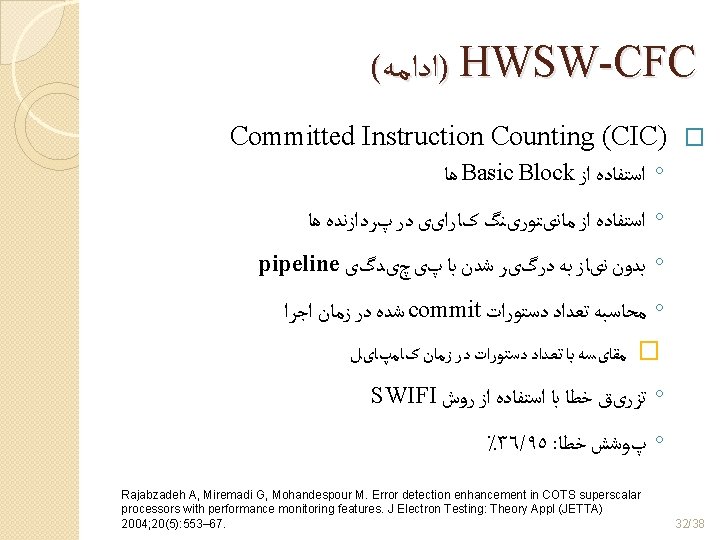

( )ﺍﺩﺍﻣﻪ HWSW-CFC � Time-Address Checking (TTA) ◦ Time Signature Monitoring (TSM) ◦ Signature Instruction Stream (SIS) ◦ Implicit Signature Checking (ISC) ◦ Committed Instruction Counting (CIC) ◦ 25/38

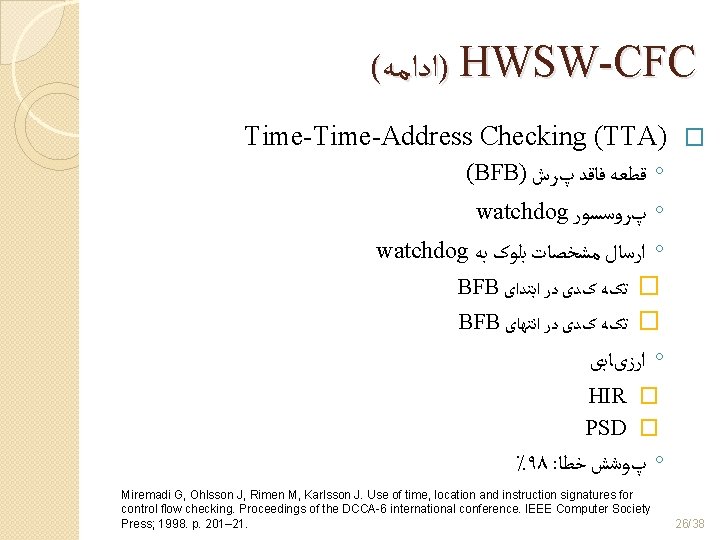

( )ﺍﺩﺍﻣﻪ HWSW-CFC Time-Address Checking (TTA) � (BFB) ◦ ﻗﻄﻌﻪ ﻓﺎﻗﺪ پﺮﺵ watchdog ◦ پﺮﻭﺳﺴﻮﺭ watchdog ◦ ﺍﺭﺳﺎﻝ ﻣﺸﺨﺼﺎﺕ ﺑﻠﻮک ﺑﻪ BFB � ﺗکﻪ کﺪی ﺩﺭ ﺍﺑﺘﺪﺍی BFB � ﺗکﻪ کﺪی ﺩﺭ ﺍﻧﺘﻬﺎی ◦ ﺍﺭﺯیﺎﺑی HIR � PSD � ٪٩٨ : ◦ پﻮﺷﺶ ﺧﻄﺎ Miremadi G, Ohlsson J, Rimen M, Karlsson J. Use of time, location and instruction signatures for control flow checking. Proceedings of the DCCA-6 international conference. IEEE Computer Society Press; 1998. p. 201– 21. 26/38

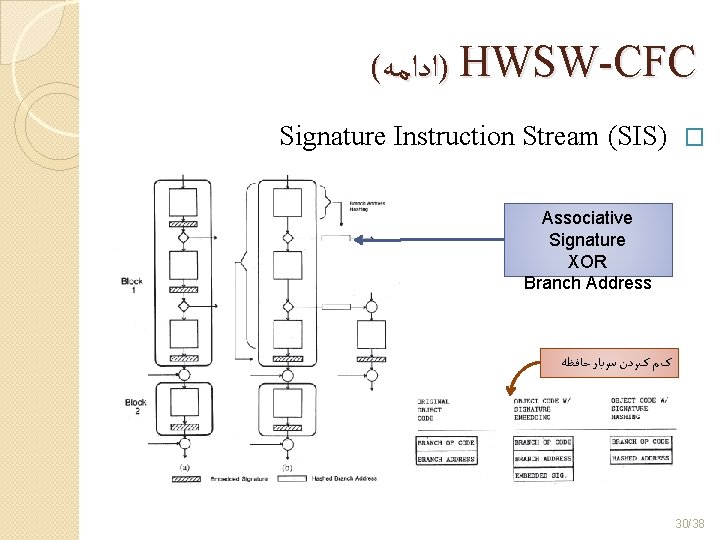

( )ﺍﺩﺍﻣﻪ HWSW-CFC Signature Instruction Stream (SIS) � Associative Signature XOR Branch Address کﻢ کﺮﺩﻥ ﺳﺮﺑﺎﺭ ﺣﺎﻓﻈﻪ 30/38

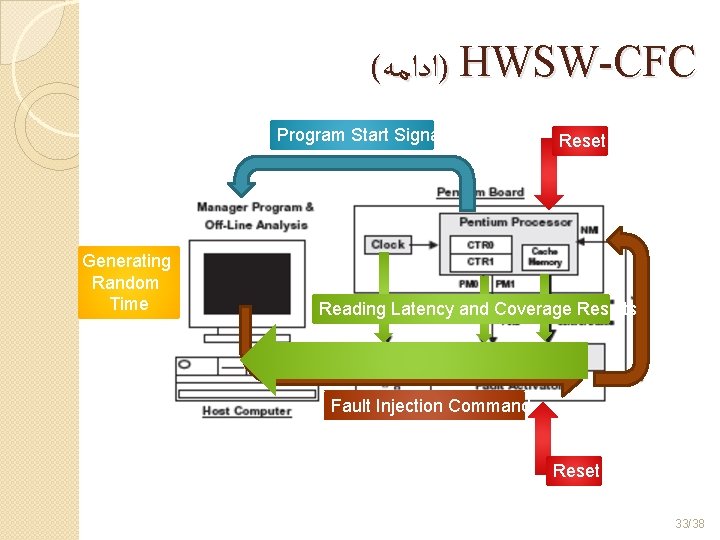

( )ﺍﺩﺍﻣﻪ HWSW-CFC Program Start Signal Generating Random Time Reset Reading Latency and Coverage Results Fault Injection Command Reset 33/38

![ﻣﺮﺍﺟﻊ � [1] Oh N, Shirvani PP, Mc. Cluskey EJ. Control-flow checking by ﻣﺮﺍﺟﻊ � [1] Oh N, Shirvani PP, Mc. Cluskey EJ. Control-flow checking by](http://slidetodoc.com/presentation_image_h2/6aa939351c8049e3dbc8e490cdf6fca1/image-35.jpg)

ﻣﺮﺍﺟﻊ � [1] Oh N, Shirvani PP, Mc. Cluskey EJ. Control-flow checking by software signatures. IEEE Trans Reliability 2002; 51(2): 111– 22. � [2] Miremadi G, Karlsson J, Gunneflo U, Torin J. Two software techniques for on-line error detection. In: 22 nd annual international symposium on fault -tolerant computing (FTCS-22), July 1992. p. 328– 35. � [3] Kanawati GA, Nair VSS, Krishnamurthy N, Abraham JA. Evaluation of integrated system-level checks for on-line error detection. In: Proceedings of IEEE international computer performance and dependability symposium, 1996. p. 292– 301. � [4] Alkhalifa Z, Nair VSS, Krishnamurthy N, Abraham JA. Design and evaluation of system-level checks for on-line control flow error detection. IEEE Trans Parallel Distrib Syst 1999; 10(6): 627– 41. � [5] Alkhalifa Z, Nair VSS. Design of a portable control-flow checking technique. In: Proceedings of the high-assurance systems engineering workshop, August 1997. p. 120– 3. 35/38

![ﻣﺮﺍﺟﻊ � [6] Venkatasubramanian R, Hayes JP, Murray BT. Low-cost on-line fault detection ﻣﺮﺍﺟﻊ � [6] Venkatasubramanian R, Hayes JP, Murray BT. Low-cost on-line fault detection](http://slidetodoc.com/presentation_image_h2/6aa939351c8049e3dbc8e490cdf6fca1/image-36.jpg)

ﻣﺮﺍﺟﻊ � [6] Venkatasubramanian R, Hayes JP, Murray BT. Low-cost on-line fault detection using control flow assertions. In: Proceedings of the 9 th IEEE international on-line testing symposium (IOLTS 03), July 2003. p. 137– 43. � [7] Goloubeva O, Rebaudengo M, Sonza Reorda M, Violante M. Soft-error detection using control flow assertions. In: 18 th IEEE international symposium on defect and fault tolerance in VLSI systems (DFT 03), Boston, MA, November 2003. p. 57– 62. � [8] Michel T, Leveugle R, Saucier G. A new approach to control flow checking without program modification. In: 21 st international symposium on fault-tolerant computing, 1991. p. 334– 41. � [9] Madeira H, Silva JG. On-line signature learning and checking: experimental evaluation. In: Proceedings of advanced computer technology, reliable systems and applications (Comp. Euro 91), May 1991. p. 642– 6. � [10] Rajabzadeh A, Miremadi G. CFCET: A hardware-based control flow checking technique in COTS processors using execution tracing, Microelectronics Reliability 46 (2006), 2006, pp. 959 -972. 36/38

![ﻣﺮﺍﺟﻊ [11] Miremadi G, Ohlsson J, Rimen M, Karlsson J. Use of time, ﻣﺮﺍﺟﻊ [11] Miremadi G, Ohlsson J, Rimen M, Karlsson J. Use of time,](http://slidetodoc.com/presentation_image_h2/6aa939351c8049e3dbc8e490cdf6fca1/image-37.jpg)

ﻣﺮﺍﺟﻊ [11] Miremadi G, Ohlsson J, Rimen M, Karlsson J. Use of time, location and instruction signatures for control flow checking. Proceedings of the DCCA-6 international conference. IEEE Computer Society Press; 1998. p. 201– 21. � [12] Madeira H, Rela M, Furtado P, Silva JG. Time behavior monitoring as an error detection mechanism. In: 3 rd IFIP working conference on dependable computing for critical applications (DCCA-3), September 1992. p. 121– 32. � [13] Schuette MA, Shen JP. Processor control flow monitoring using signatured instruction streams. IEEE Trans Comput 1987; C 36(3): 264– 76. � [14] Ohlsson J, Rimen M. Implicit signature checking. In: Twentyfifth international symposium on fault-tolerant computing, FTCS 25, 1995. p. 218– 27. � [15] Rajabzadeh A, Miremadi G, Mohandespour M. Error detection enhancement in COTS superscalar processors with performance monitoring features. J Electron Testing: Theory Appl (JETTA) 2004; 20(5): 553– 67. � 37/38

Thank you for your patience !!!

- Slides: 38