Swami Keshvanand Institute of Technology Management Gramothan Jaipur

- Slides: 83

Swami Keshvanand Institute of Technology, Management & Gramothan, Jaipur B. Tech. V Semester ECE B Subject: 5 EC 4 -04 Digital Signal Processing Topic : 3. Discrete Fourier Transform Dr. Monika Mathur Associate Professor, ECE Department. SKIT, Jaipur

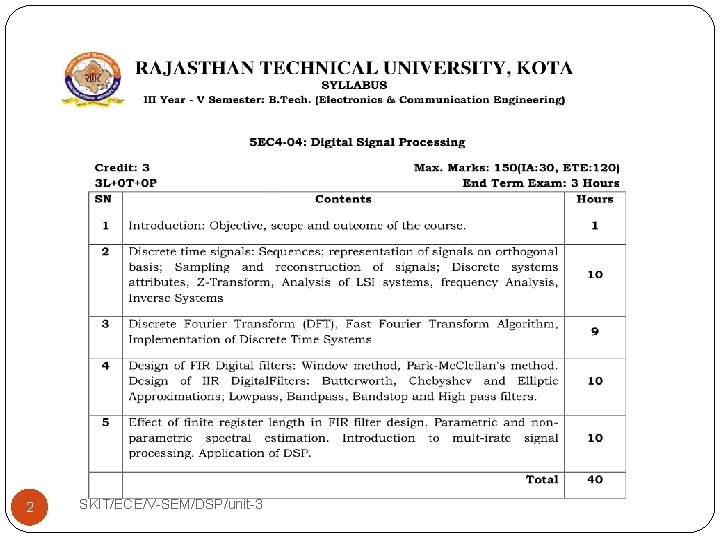

2 SKIT/ECE/V-SEM/DSP/unit-3

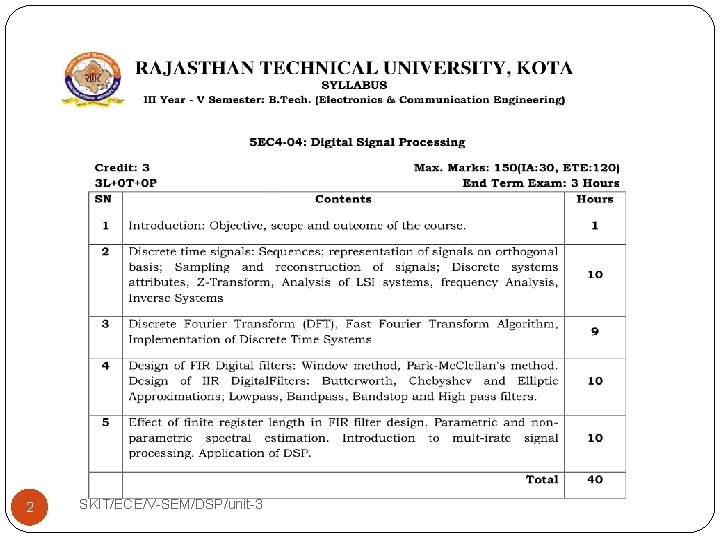

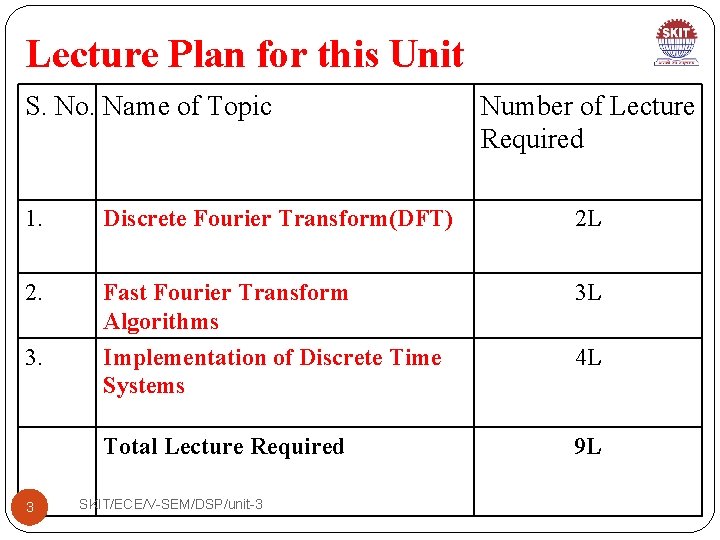

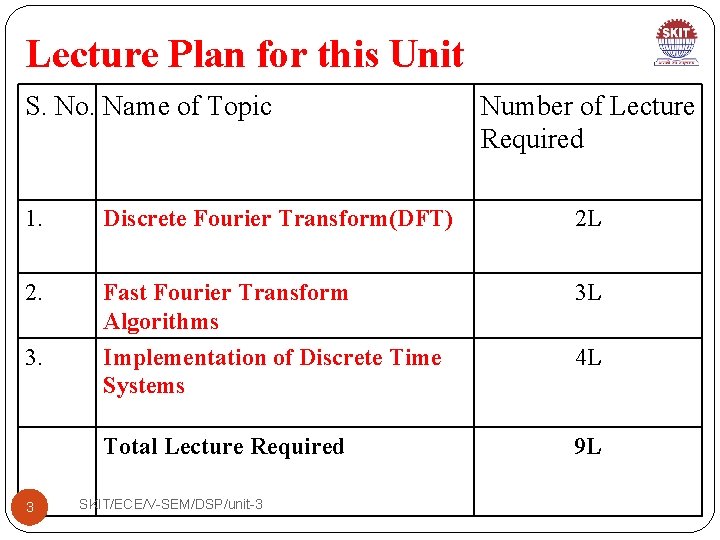

Lecture Plan for this Unit S. No. Name of Topic Number of Lecture Required 1. Discrete Fourier Transform(DFT) 2 L 2. Fast Fourier Transform Algorithms Implementation of Discrete Time Systems 3 L Total Lecture Required 9 L 3. 3 SKIT/ECE/V-SEM/DSP/unit-3 4 L

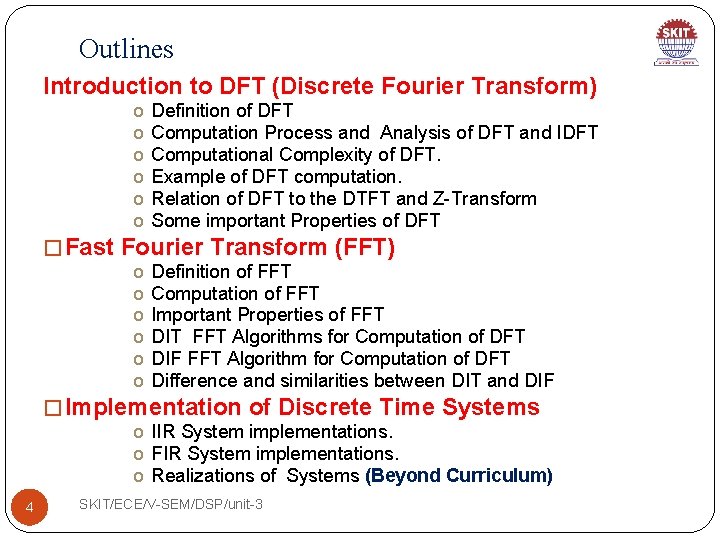

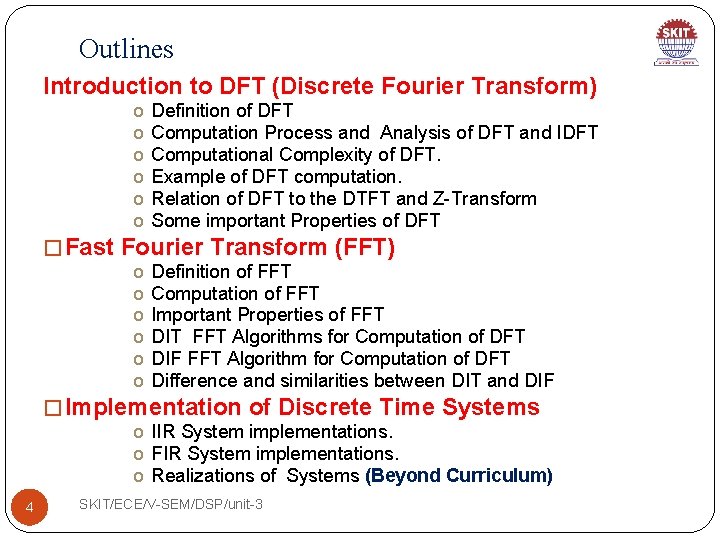

Outlines Introduction to DFT (Discrete Fourier Transform) o o o Definition of DFT Computation Process and Analysis of DFT and IDFT Computational Complexity of DFT. Example of DFT computation. Relation of DFT to the DTFT and Z-Transform Some important Properties of DFT � Fast Fourier Transform (FFT) o o o Definition of FFT Computation of FFT Important Properties of FFT DIT FFT Algorithms for Computation of DFT DIF FFT Algorithm for Computation of DFT Difference and similarities between DIT and DIF � Implementation of Discrete Time Systems o IIR System implementations. o FIR System implementations. o Realizations of Systems (Beyond Curriculum) 4 SKIT/ECE/V-SEM/DSP/unit-3

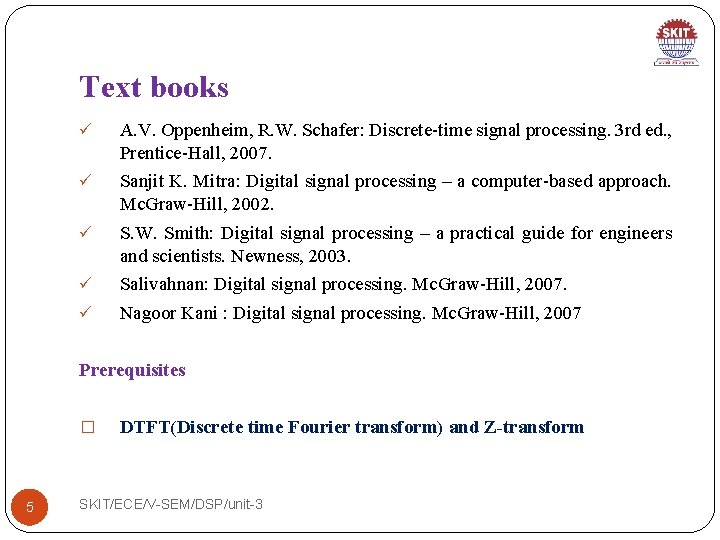

Text books ü A. V. Oppenheim, R. W. Schafer: Discrete-time signal processing. 3 rd ed. , Prentice-Hall, 2007. ü Sanjit K. Mitra: Digital signal processing – a computer-based approach. Mc. Graw-Hill, 2002. ü S. W. Smith: Digital signal processing – a practical guide for engineers and scientists. Newness, 2003. ü Salivahnan: Digital signal processing. Mc. Graw-Hill, 2007. ü Nagoor Kani : Digital signal processing. Mc. Graw-Hill, 2007 Prerequisites � 5 DTFT(Discrete time Fourier transform) and Z-transform SKIT/ECE/V-SEM/DSP/unit-3

Lecture No. - 3 -1 �Discrete Fourier Transform(DFT) 6 SKIT/ECE/V-SEM/DSP/unit-3

Introduction to DFT (Discrete Fourier Transform) �The discrete Fourier transform or DFT is the transform that deals with a finite discrete-time signal and a finite or discrete number of frequencies. � To Understand the DFT first we recall DTFT and ZTransform and From that find the need of DFT. �DTFT (Discrete Time Fourier Transform) is the frequency domain representation of Absolutely summable sequences. �Z- Transform is the generalized frequency domain representation of arbitrary sequences. 7 SKIT/ECE/V-SEM/DSP/unit-3

Contd…. . �These two transforms have the common features: �The transform is defined for infinite Length sequences. �They are function of continuous variables ( ω and z) �We can say that these both are not numerically computable transforms. �DFT overcomes these two problems as it is a transform for finite length sequences and numerically computed transform. So suitable for computer implementations. 8 SKIT/ECE/V-SEM/DSP/unit-3

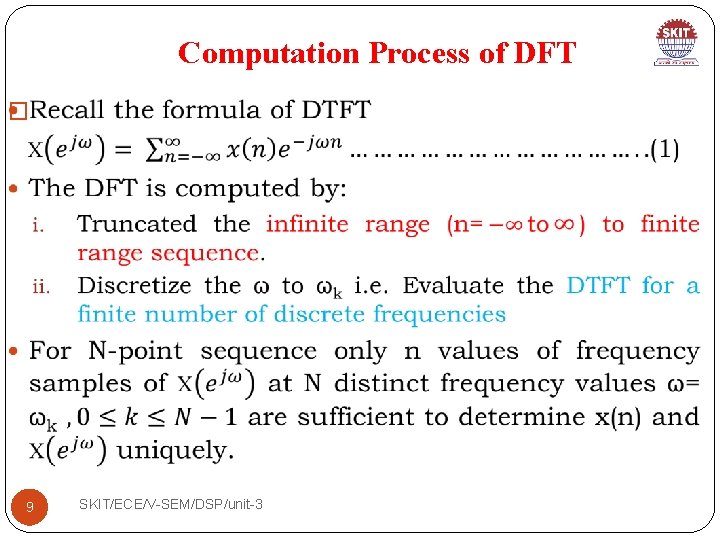

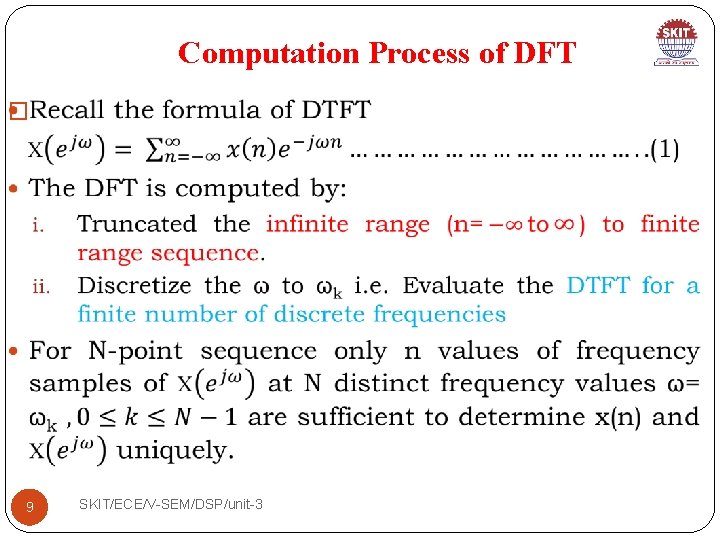

Computation Process of DFT � 9 SKIT/ECE/V-SEM/DSP/unit-3

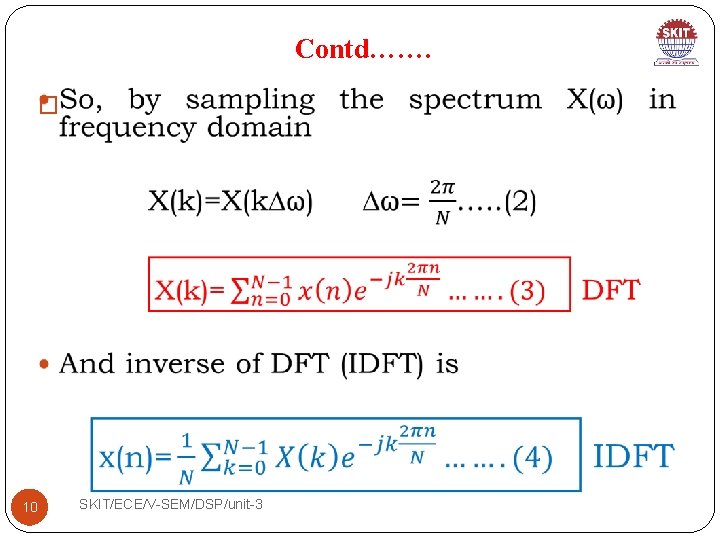

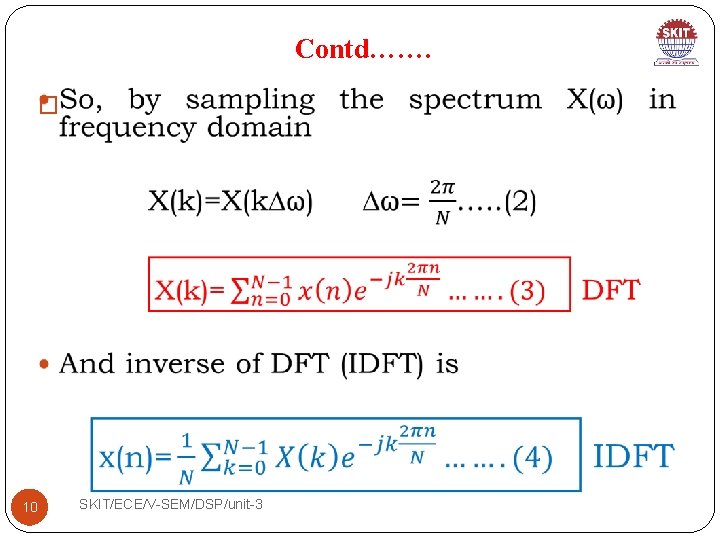

Contd……. � 10 SKIT/ECE/V-SEM/DSP/unit-3

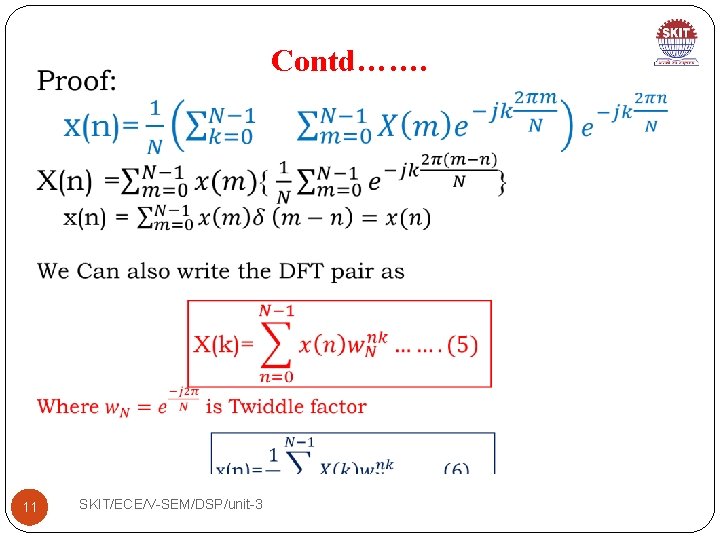

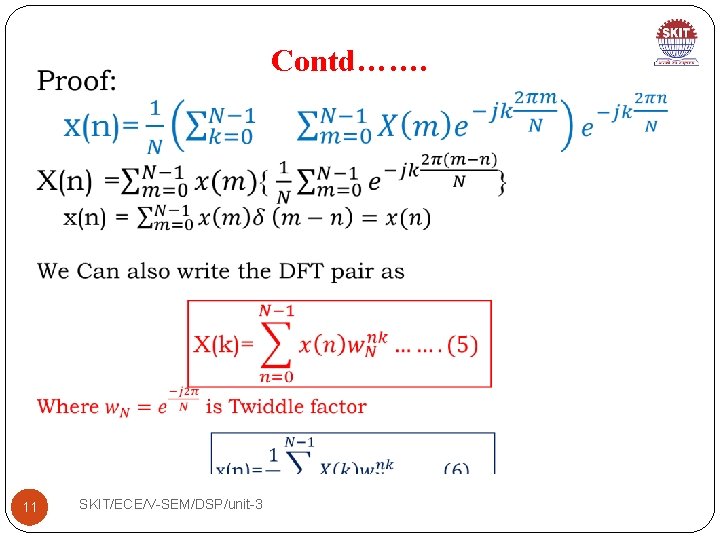

Contd……. 11 SKIT/ECE/V-SEM/DSP/unit-3

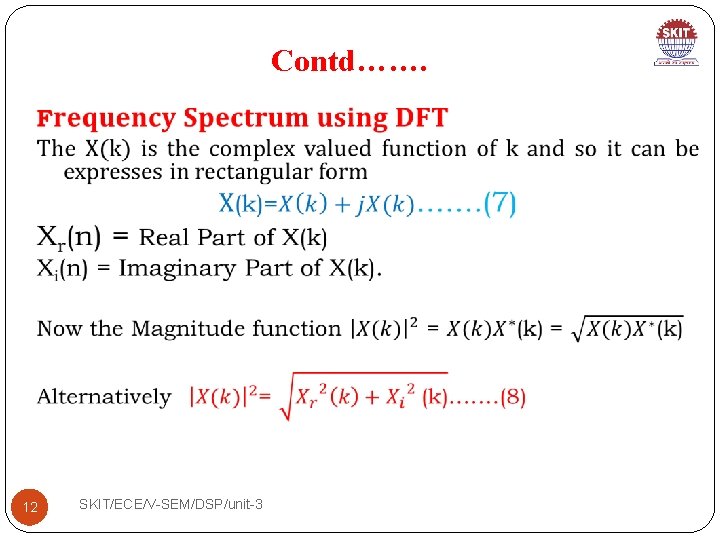

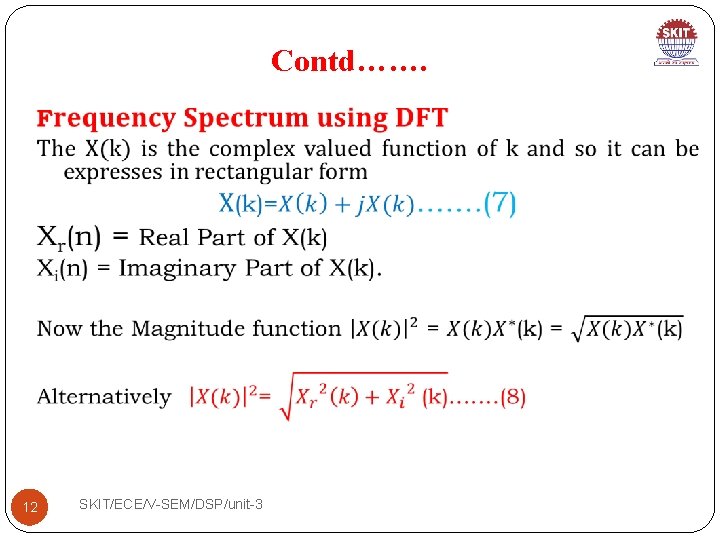

Contd……. 12 SKIT/ECE/V-SEM/DSP/unit-3

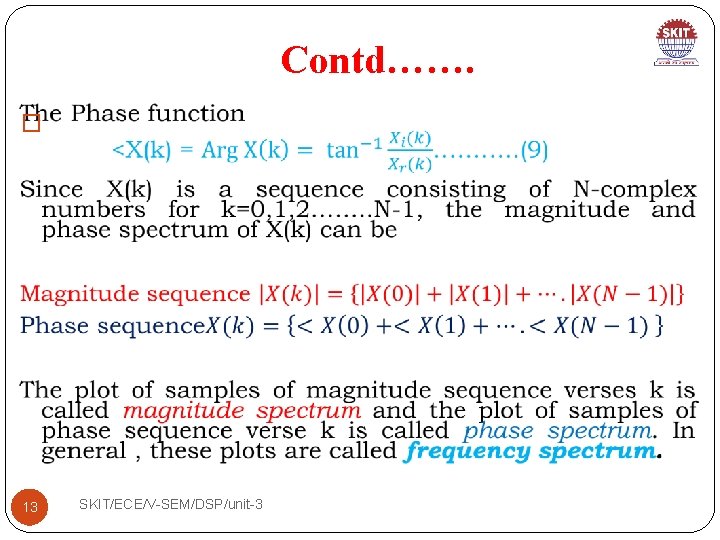

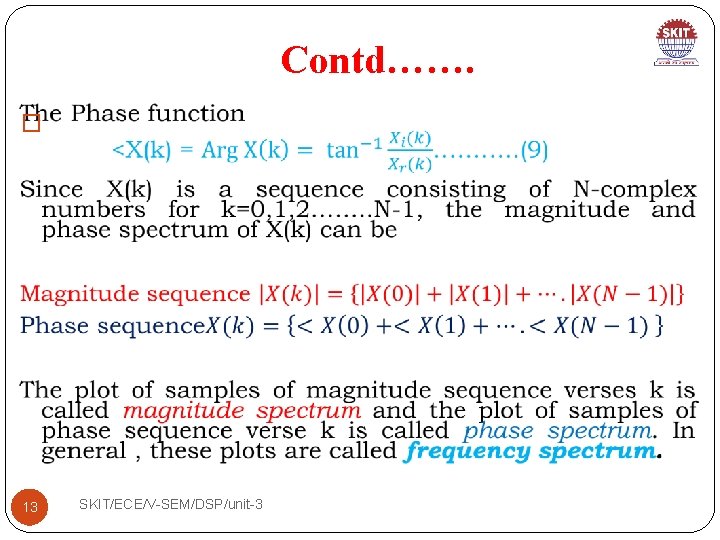

Contd……. � 13 SKIT/ECE/V-SEM/DSP/unit-3

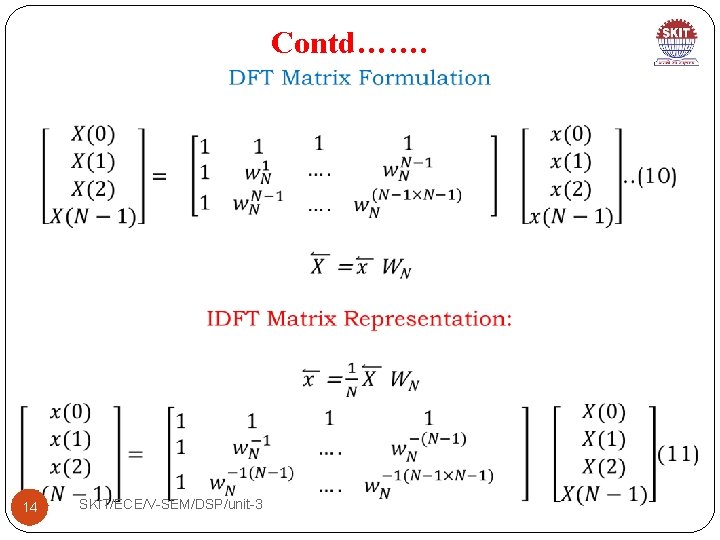

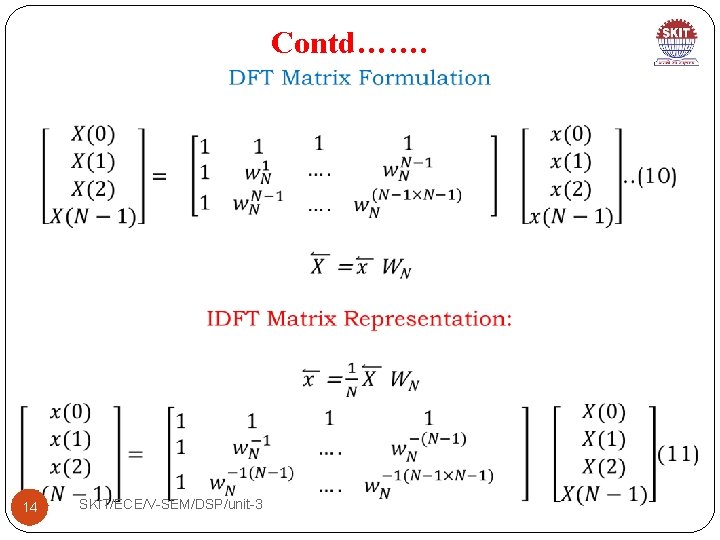

Contd……. 14 SKIT/ECE/V-SEM/DSP/unit-3

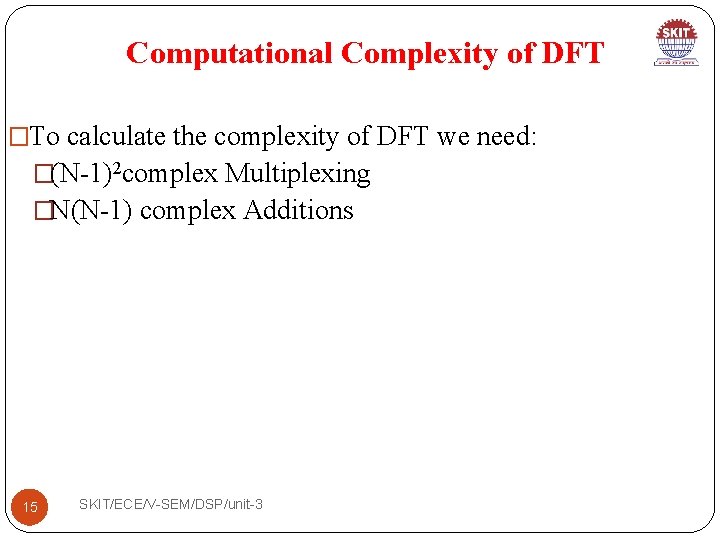

Computational Complexity of DFT �To calculate the complexity of DFT we need: �(N-1)2 complex Multiplexing �N(N-1) complex Additions 15 SKIT/ECE/V-SEM/DSP/unit-3

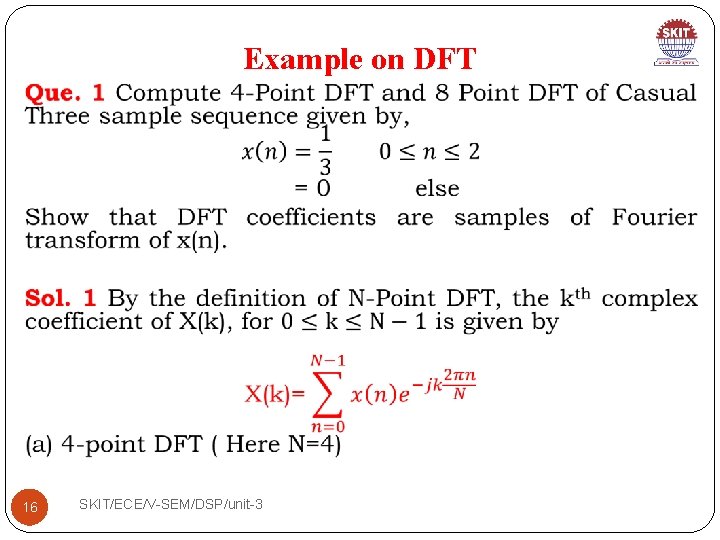

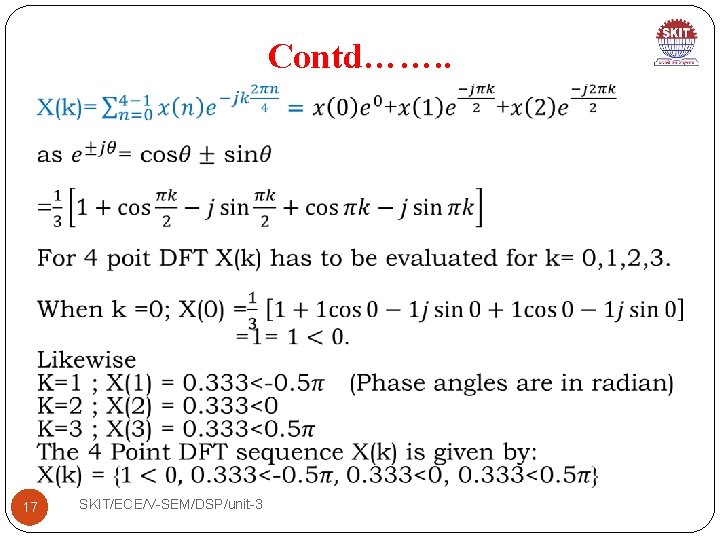

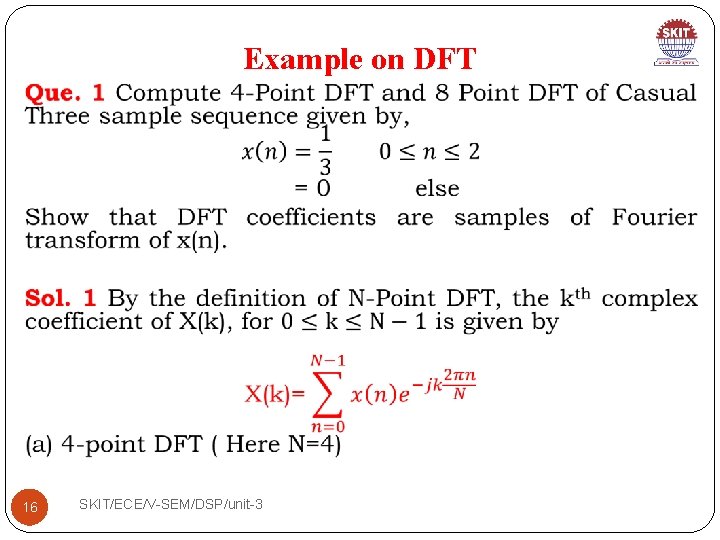

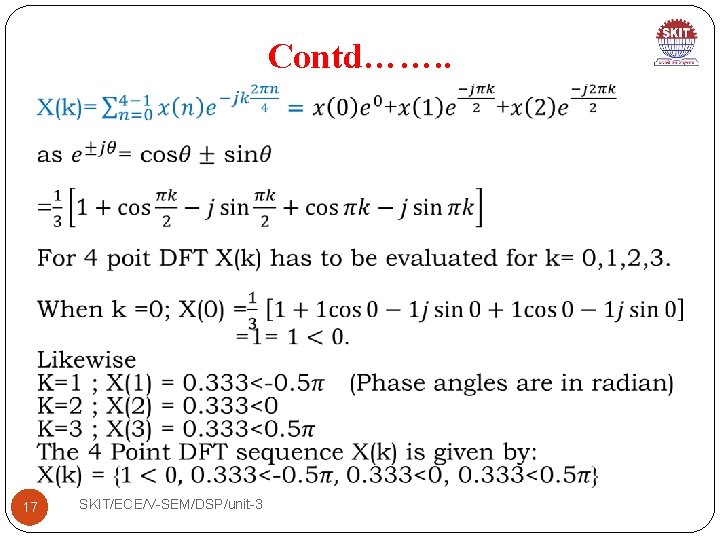

Example on DFT 16 SKIT/ECE/V-SEM/DSP/unit-3

Contd……. . 17 SKIT/ECE/V-SEM/DSP/unit-3

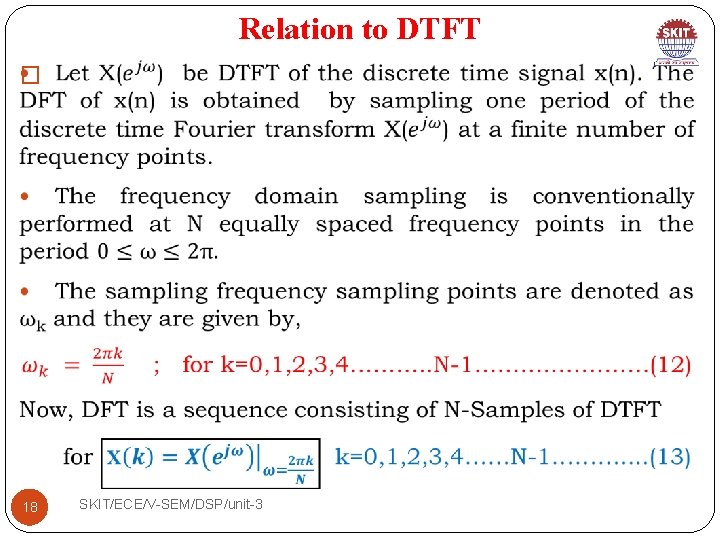

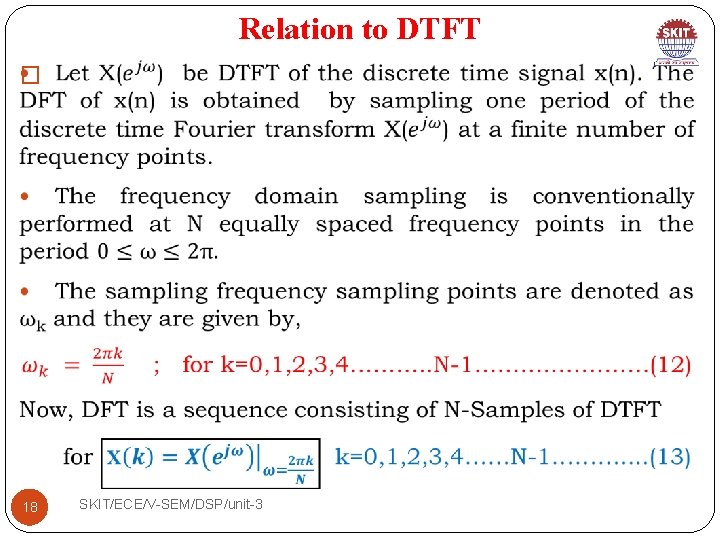

Relation to DTFT � 18 SKIT/ECE/V-SEM/DSP/unit-3

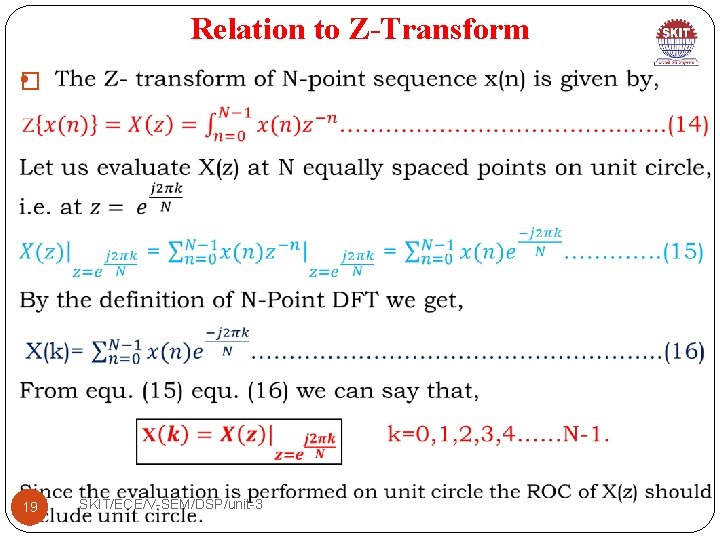

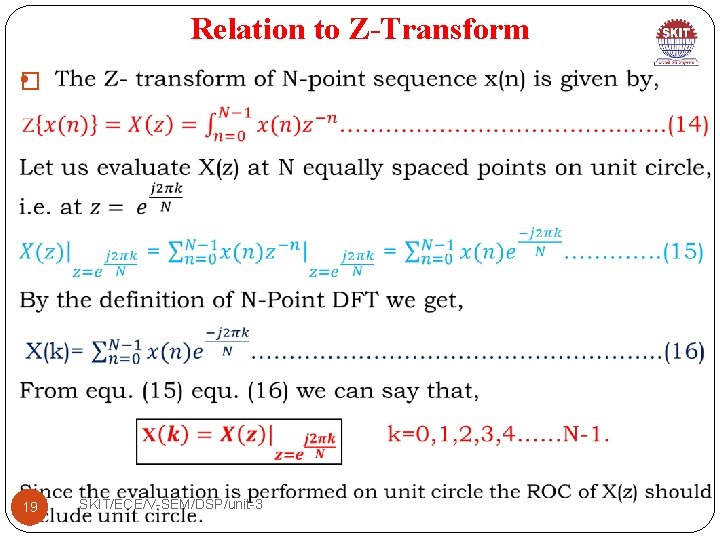

Relation to Z-Transform � 19 SKIT/ECE/V-SEM/DSP/unit-3

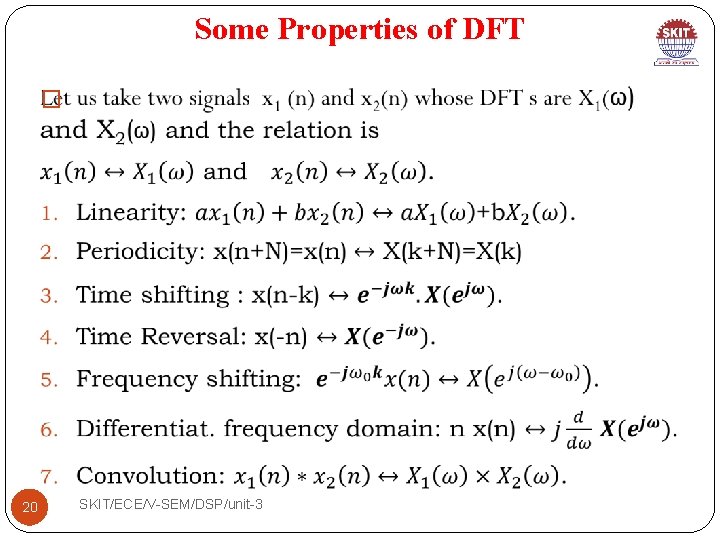

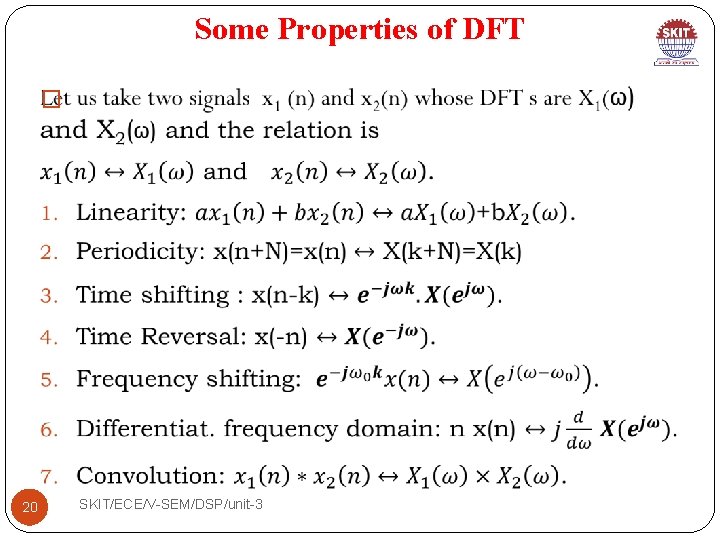

Some Properties of DFT � 20 SKIT/ECE/V-SEM/DSP/unit-3

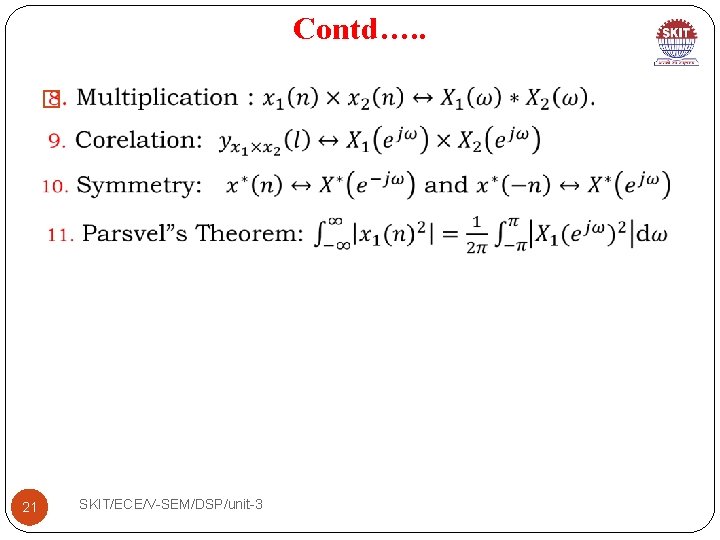

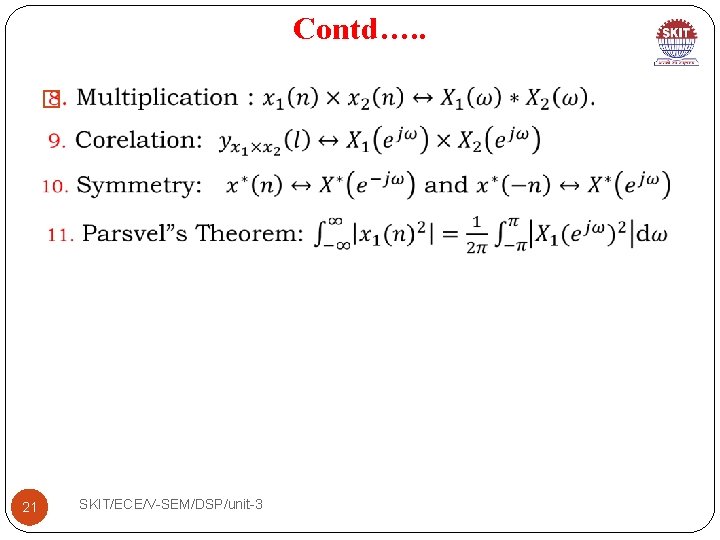

Contd…. . � 21 SKIT/ECE/V-SEM/DSP/unit-3

Lecture No. - 3 -2 �Tutorial on the DFT 22 SKIT/ECE/V-SEM/DSP/unit-3

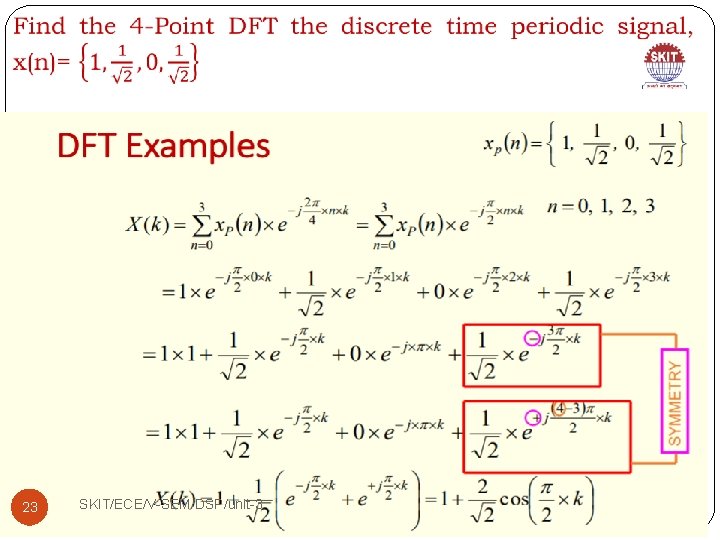

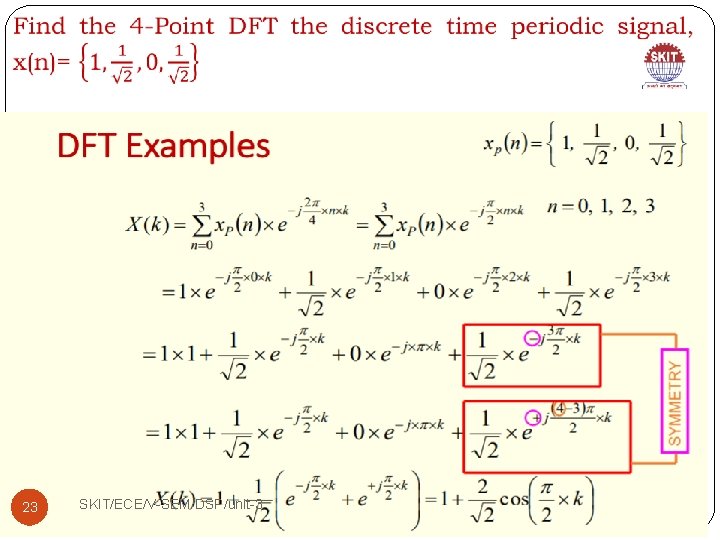

23 SKIT/ECE/V-SEM/DSP/unit-3

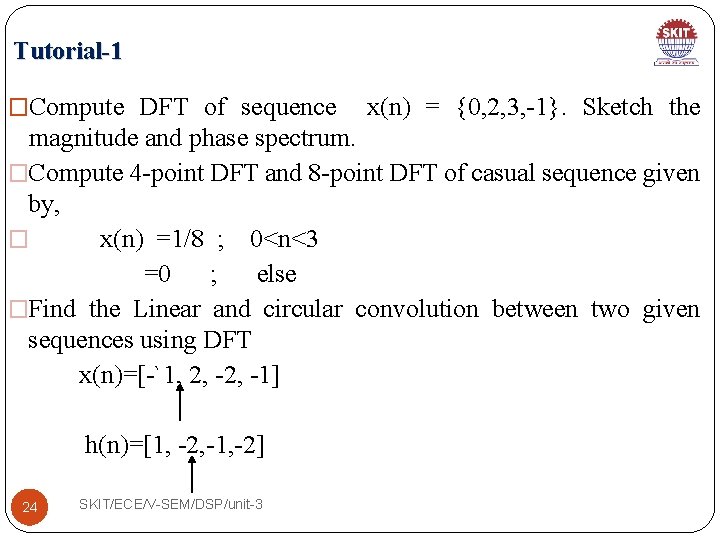

Tutorial-1 �Compute DFT of sequence x(n) = {0, 2, 3, -1}. Sketch the magnitude and phase spectrum. �Compute 4 -point DFT and 8 -point DFT of casual sequence given by, � x(n) =1/8 ; 0<n<3 =0 ; else �Find the Linear and circular convolution between two given sequences using DFT x(n)=[-`1, 2, -1] h(n)=[1, -2, -1, -2] 24 SKIT/ECE/V-SEM/DSP/unit-3

Lecture No. - 3 -3 �Fast Fourier Transform �DIT Algorithm 25 SKIT/ECE/V-SEM/DSP/unit-3

Fast Fourier Transform (FFT) Definition �The time taken to evaluate a DFT on a digital computer depends principally on the number of multiplications involved(the slowest operations). With the DFT, this number is directly related to , where N is the length of the transform. �Fast Fourier transforms (FFTs) are the algorithms rely on the fact that the standard DFT involves a lot of redundant calculations and , these are the techniques, often reducing the computation time by hundreds. 26 SKIT/ECE/V-SEM/DSP/unit-3

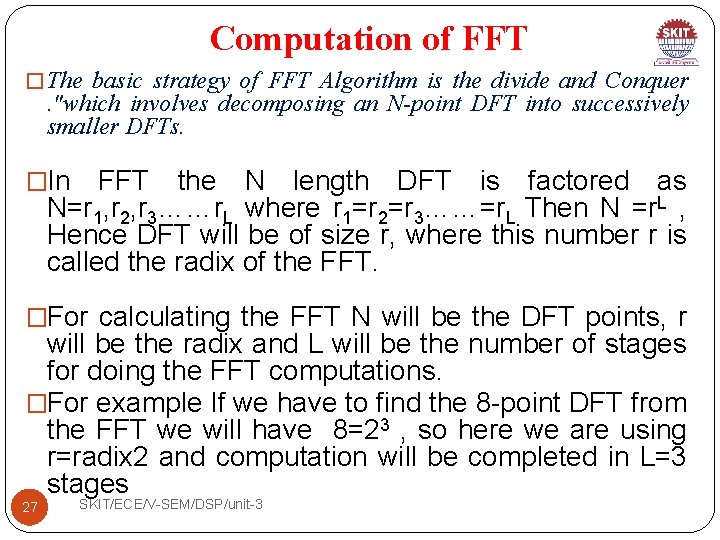

Computation of FFT � The basic strategy of FFT Algorithm is the divide and Conquer . "which involves decomposing an N-point DFT into successively smaller DFTs. �In FFT the N length DFT is factored as N=r 1, r 2, r 3……r. L where r 1=r 2=r 3……=r. L Then N =r. L , Hence DFT will be of size r, where this number r is called the radix of the FFT. �For calculating the FFT N will be the DFT points, r will be the radix and L will be the number of stages for doing the FFT computations. �For example If we have to find the 8 -point DFT from the FFT we will have 8=23 , so here we are using r=radix 2 and computation will be completed in L=3 stages 27 SKIT/ECE/V-SEM/DSP/unit-3

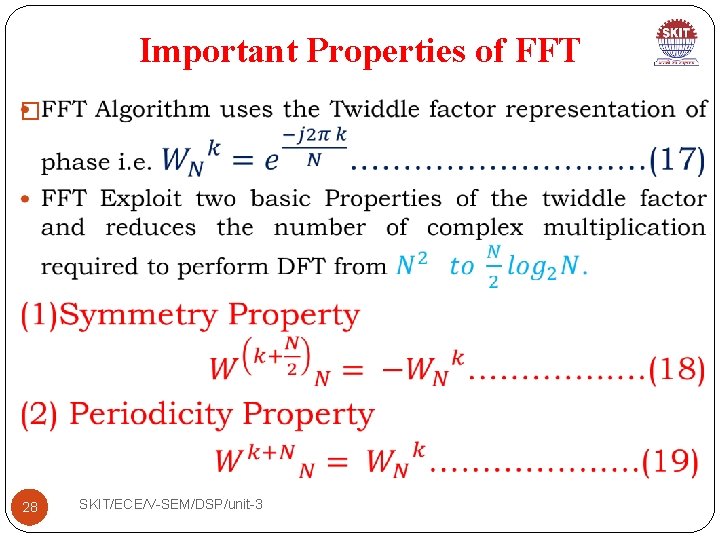

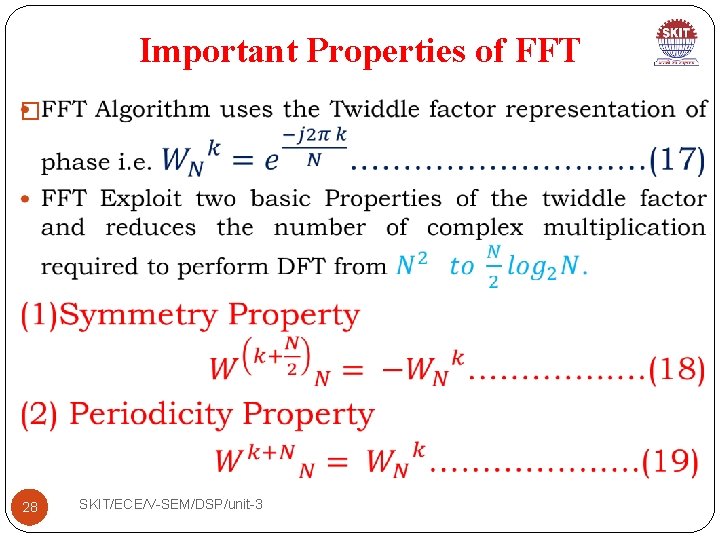

Important Properties of FFT � 28 SKIT/ECE/V-SEM/DSP/unit-3

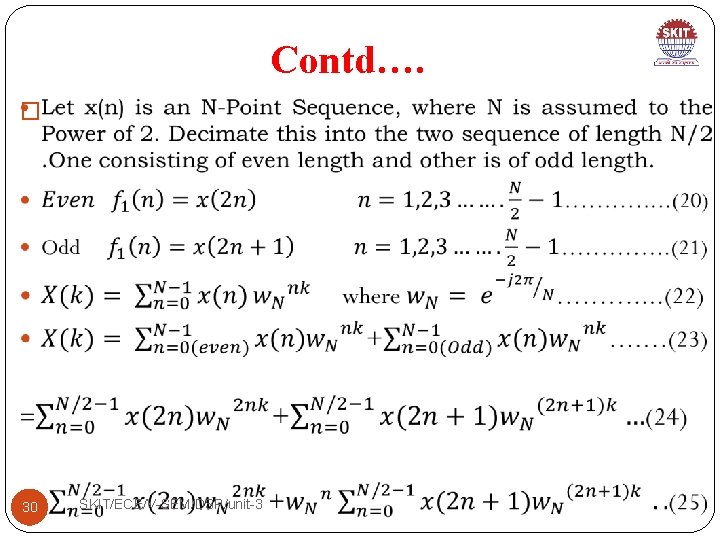

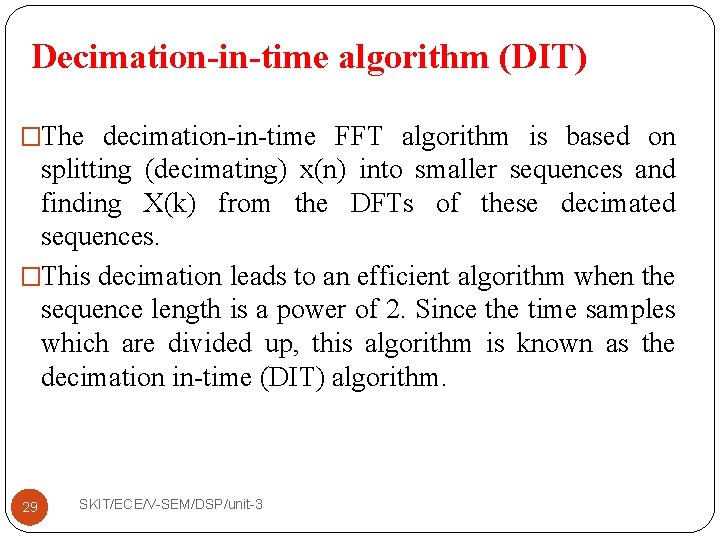

Decimation-in-time algorithm (DIT) �The decimation-in-time FFT algorithm is based on splitting (decimating) x(n) into smaller sequences and finding X(k) from the DFTs of these decimated sequences. �This decimation leads to an efficient algorithm when the sequence length is a power of 2. Since the time samples which are divided up, this algorithm is known as the decimation in-time (DIT) algorithm. 29 SKIT/ECE/V-SEM/DSP/unit-3

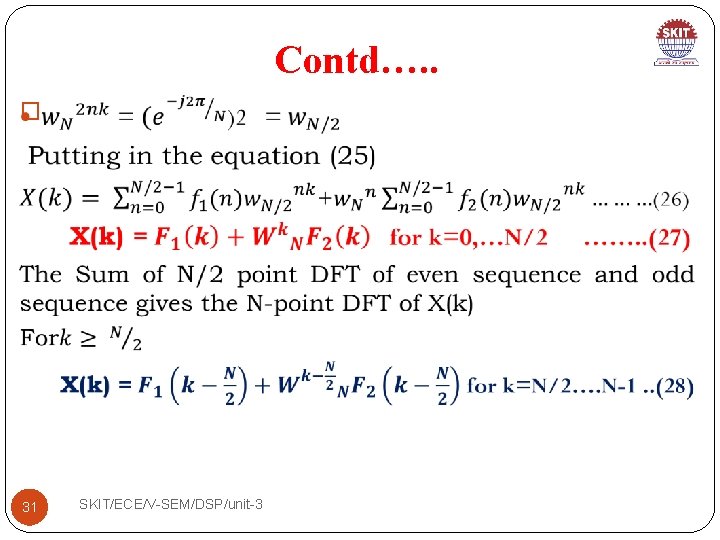

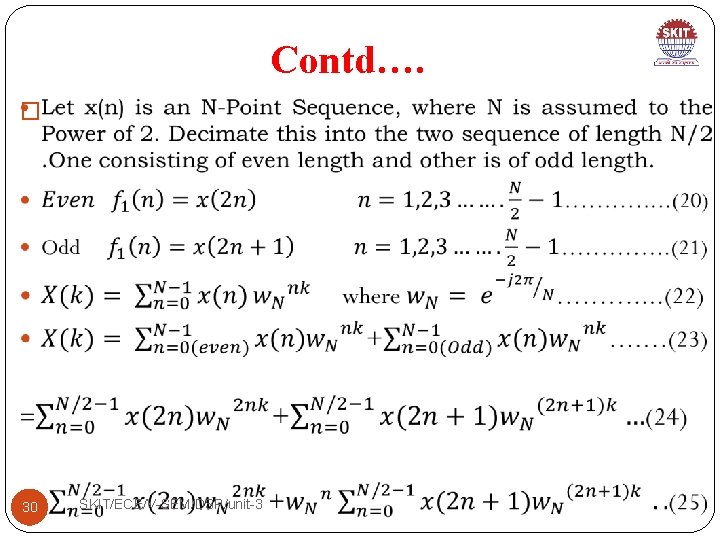

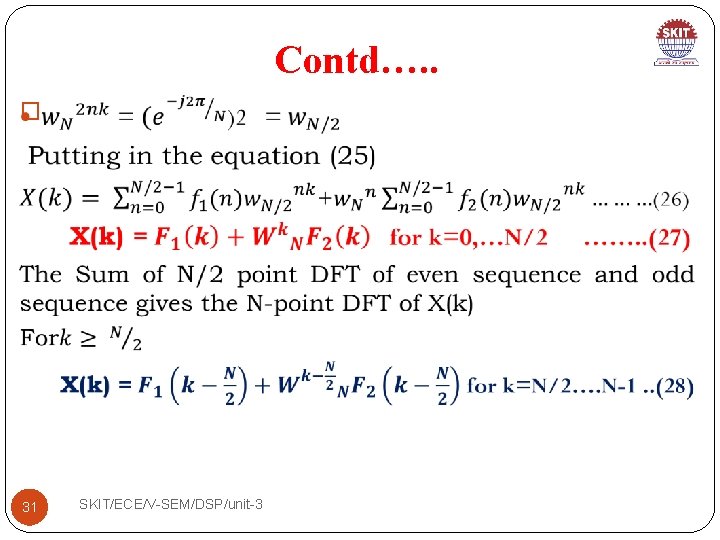

Contd…. � 30 SKIT/ECE/V-SEM/DSP/unit-3

Contd…. . � 31 SKIT/ECE/V-SEM/DSP/unit-3

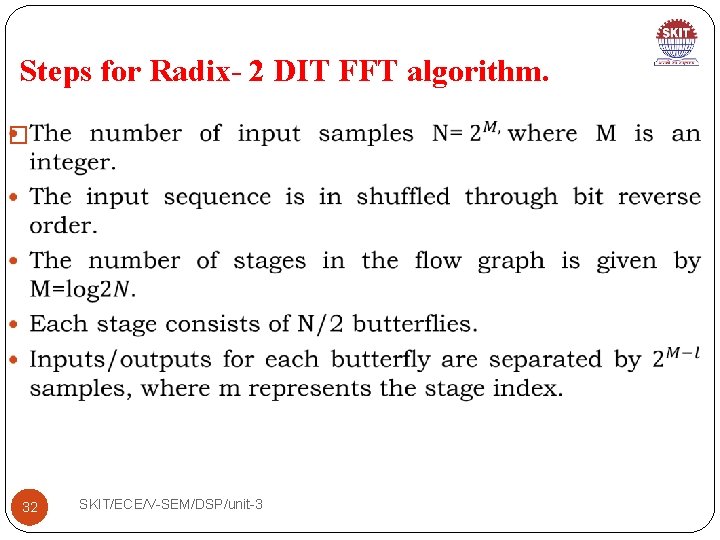

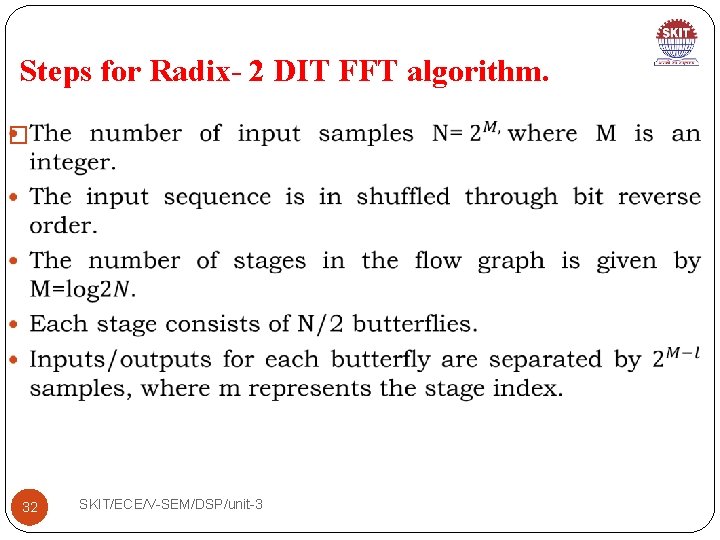

Steps for Radix- 2 DIT FFT algorithm. � 32 SKIT/ECE/V-SEM/DSP/unit-3

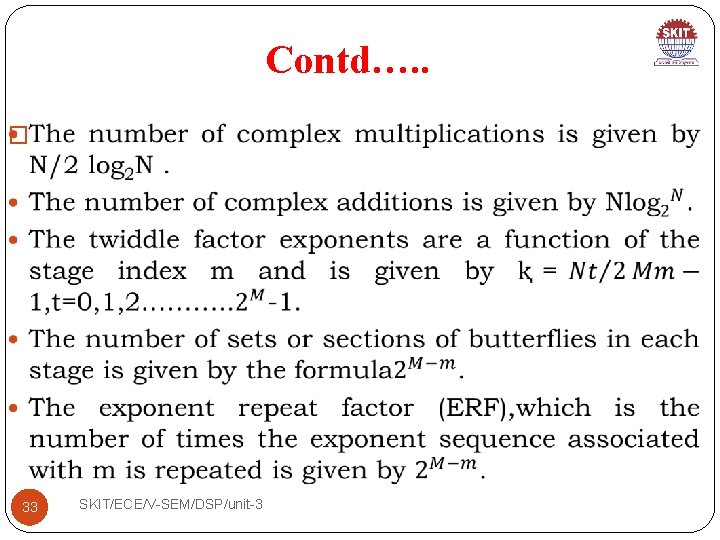

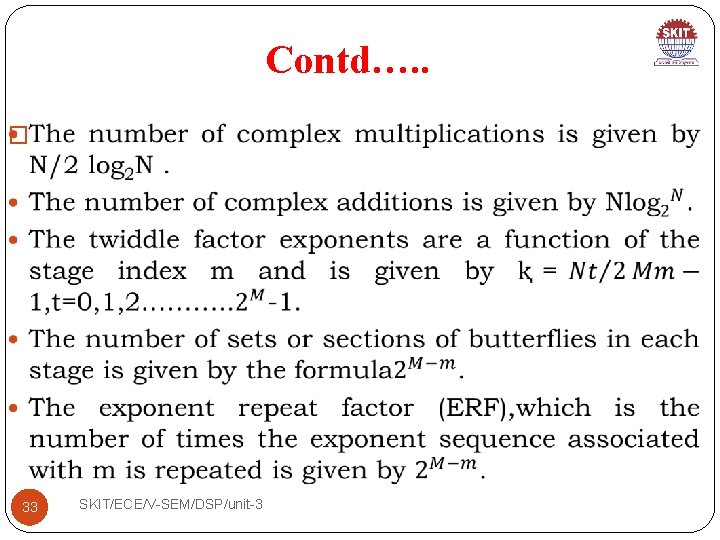

Contd…. . � 33 SKIT/ECE/V-SEM/DSP/unit-3

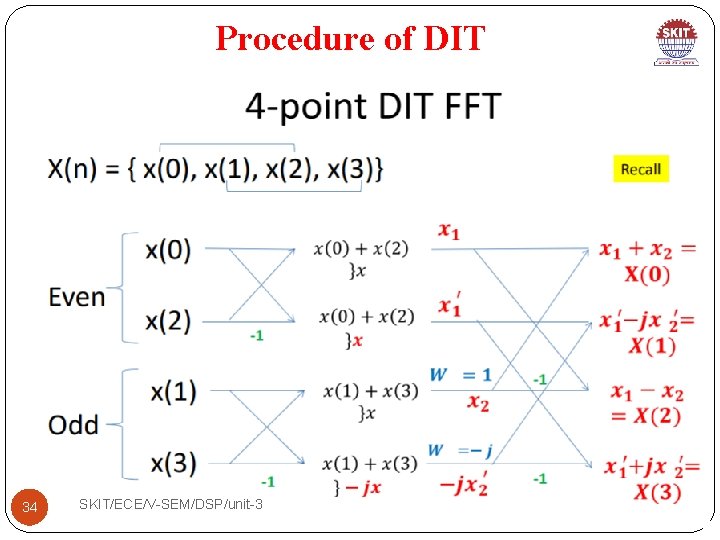

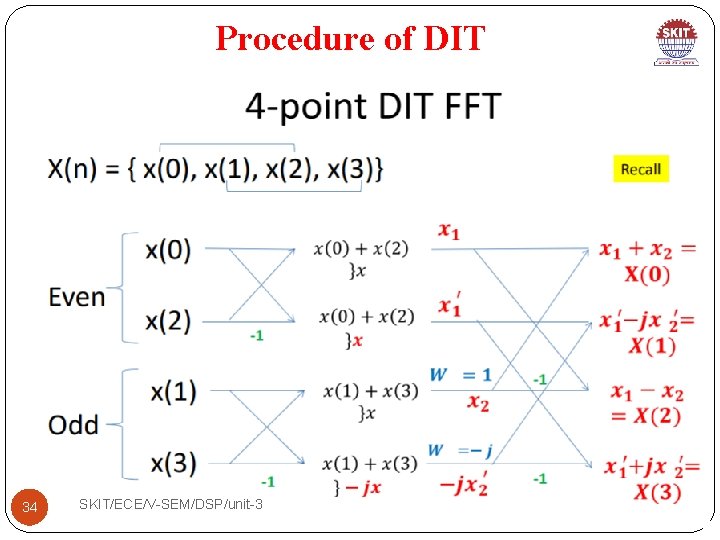

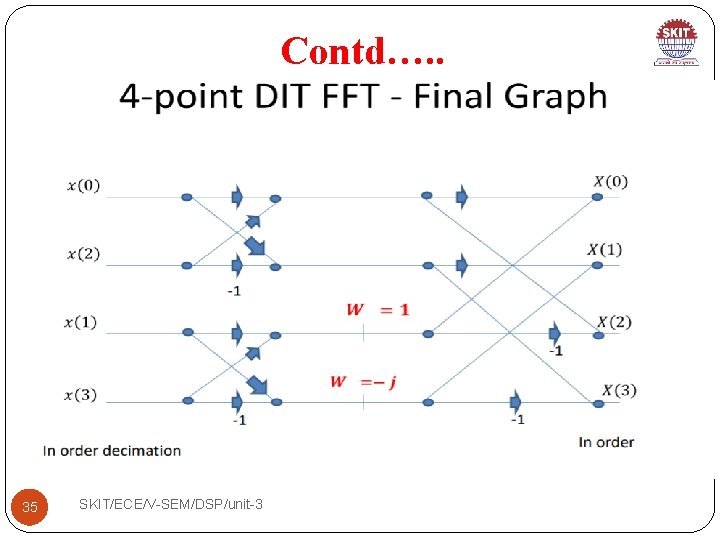

Procedure of DIT 34 SKIT/ECE/V-SEM/DSP/unit-3

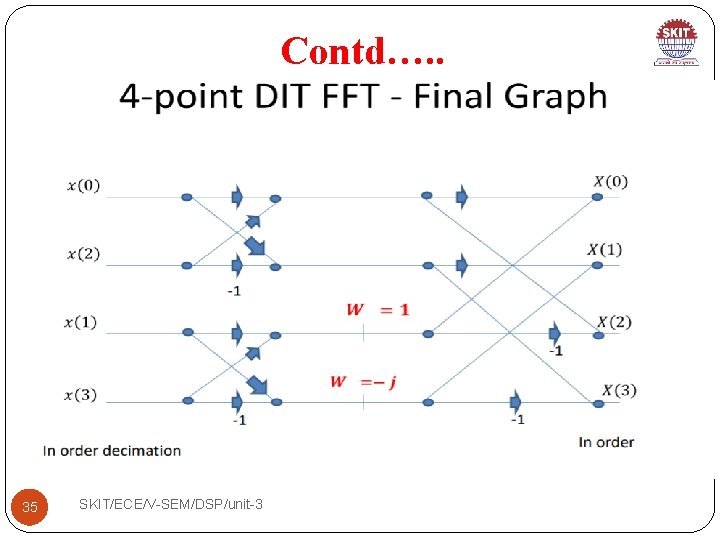

Contd…. . 35 SKIT/ECE/V-SEM/DSP/unit-3

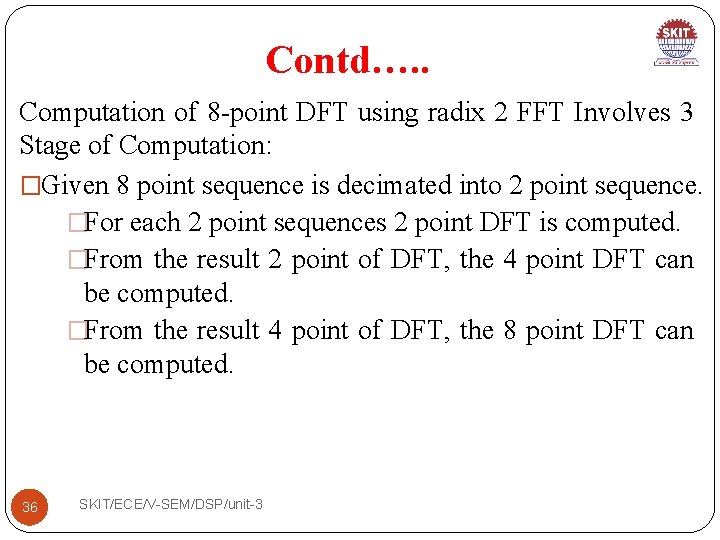

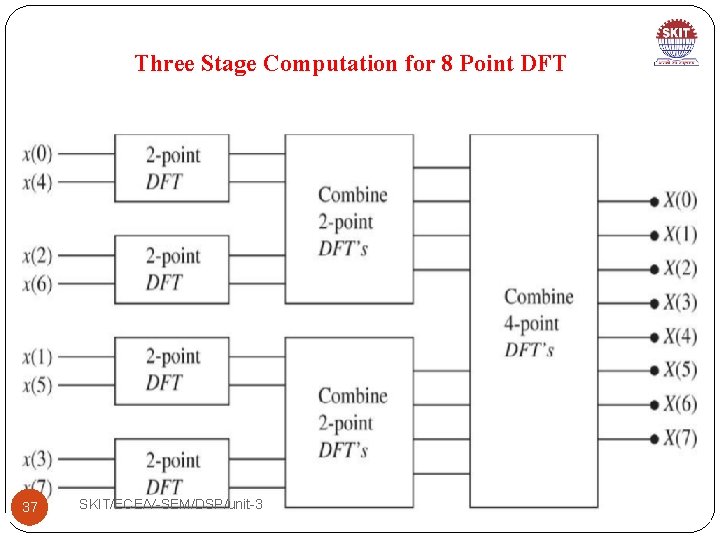

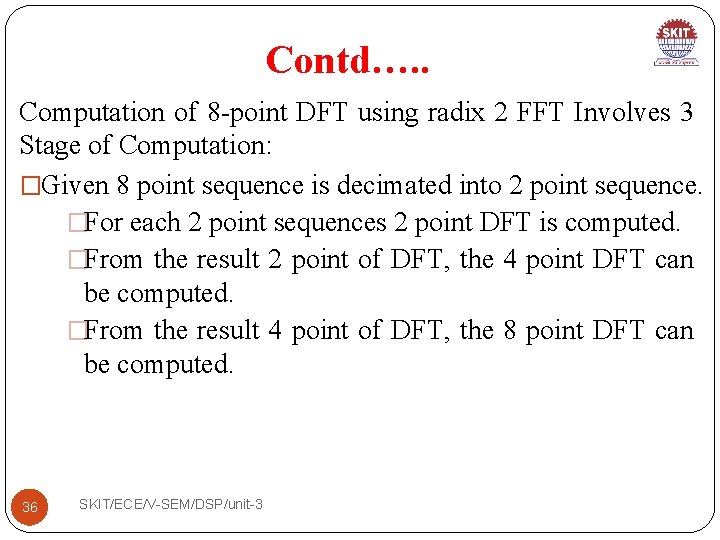

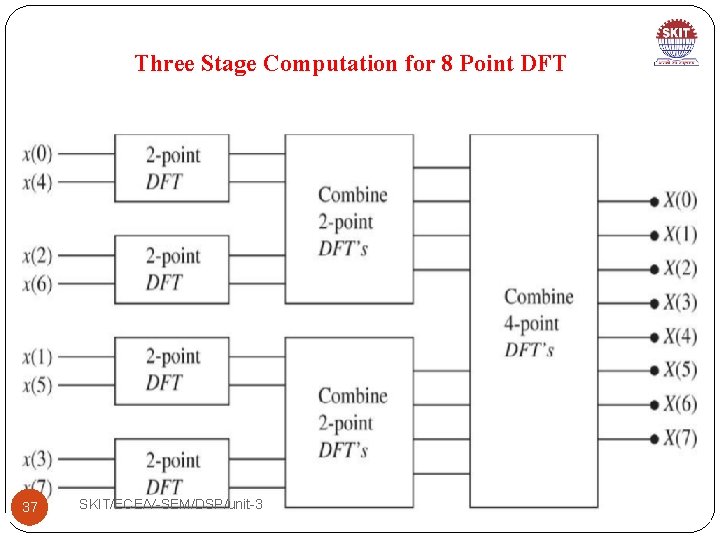

Contd…. . Computation of 8 -point DFT using radix 2 FFT Involves 3 Stage of Computation: �Given 8 point sequence is decimated into 2 point sequence. �For each 2 point sequences 2 point DFT is computed. �From the result 2 point of DFT, the 4 point DFT can be computed. �From the result 4 point of DFT, the 8 point DFT can be computed. 36 SKIT/ECE/V-SEM/DSP/unit-3

Three Stage Computation for 8 Point DFT 37 SKIT/ECE/V-SEM/DSP/unit-3

Combine Butterfly diagram for 8 - point FFT 38 SKIT/ECE/V-SEM/DSP/unit-3

Lecture No. - 3 -4 �Fast Fourier Transform �DIF Algorithm 39 SKIT/ECE/V-SEM/DSP/unit-3

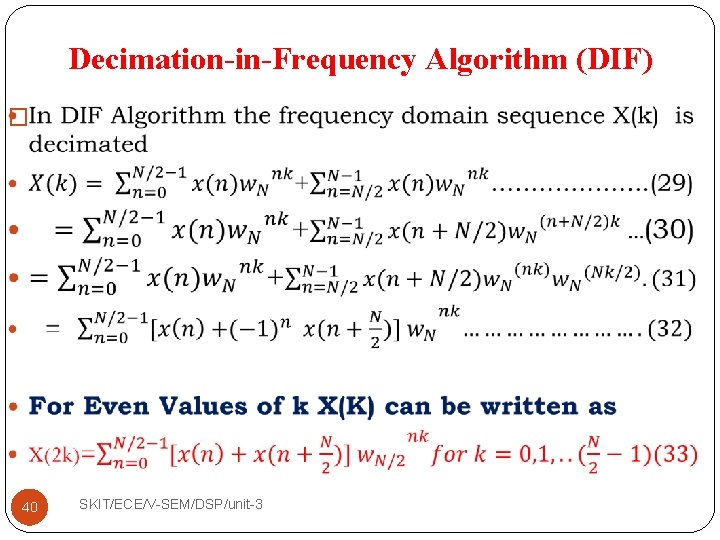

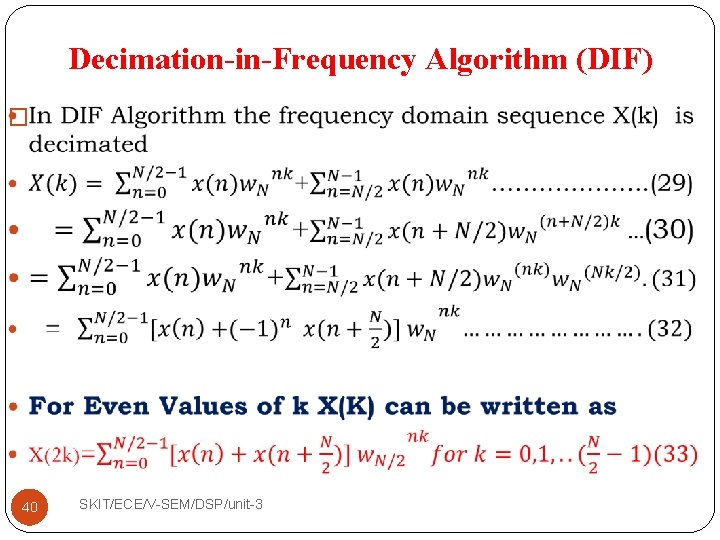

Decimation-in-Frequency Algorithm (DIF) � 40 SKIT/ECE/V-SEM/DSP/unit-3

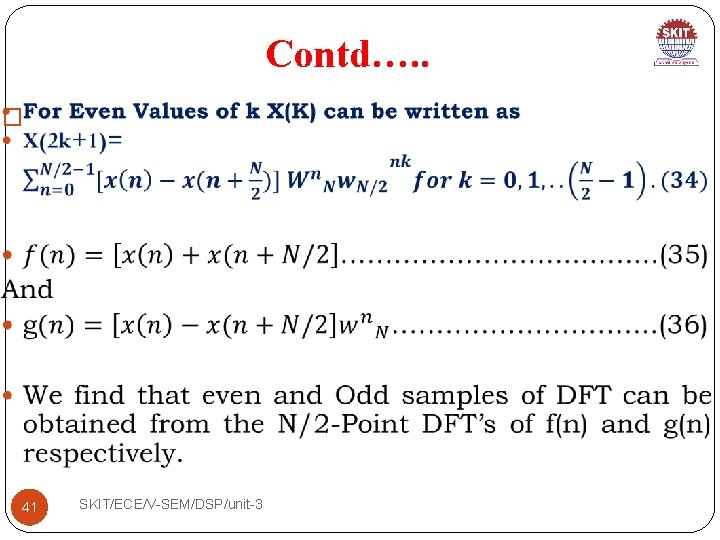

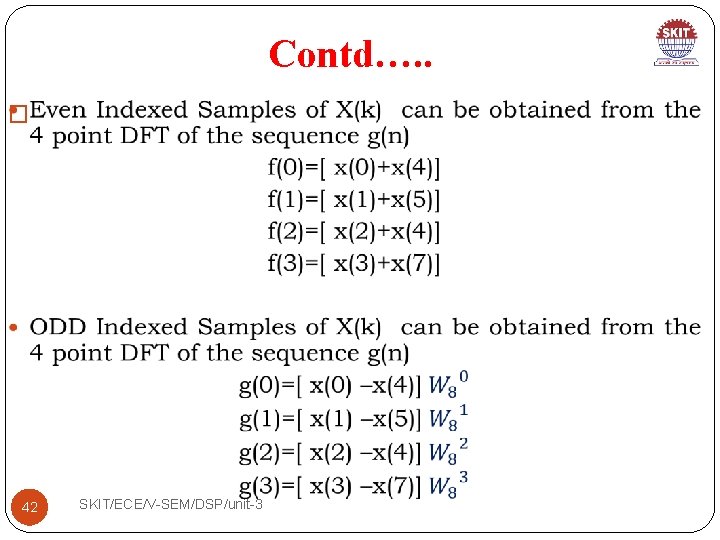

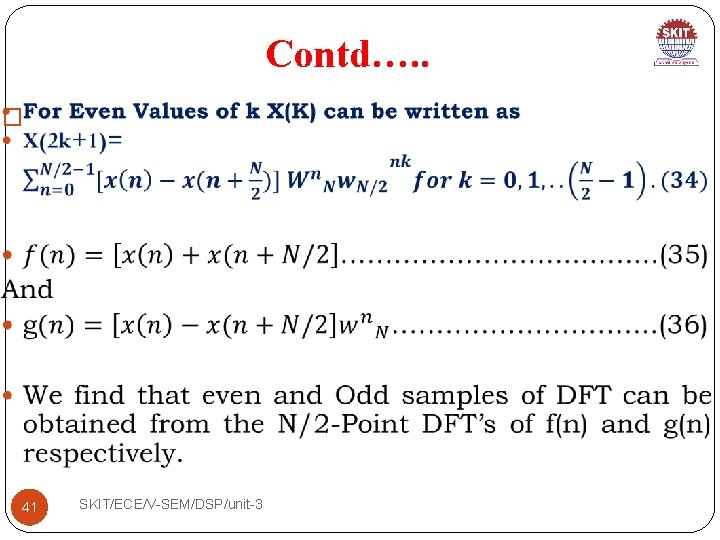

Contd…. . � 41 SKIT/ECE/V-SEM/DSP/unit-3

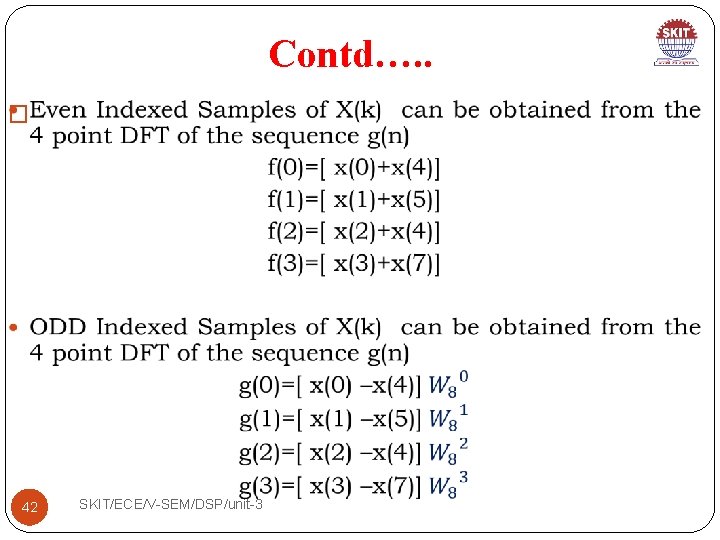

Contd…. . � 42 SKIT/ECE/V-SEM/DSP/unit-3

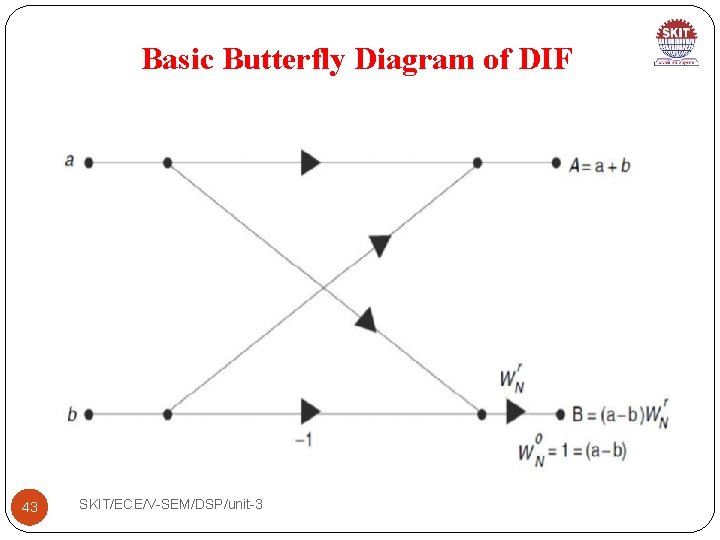

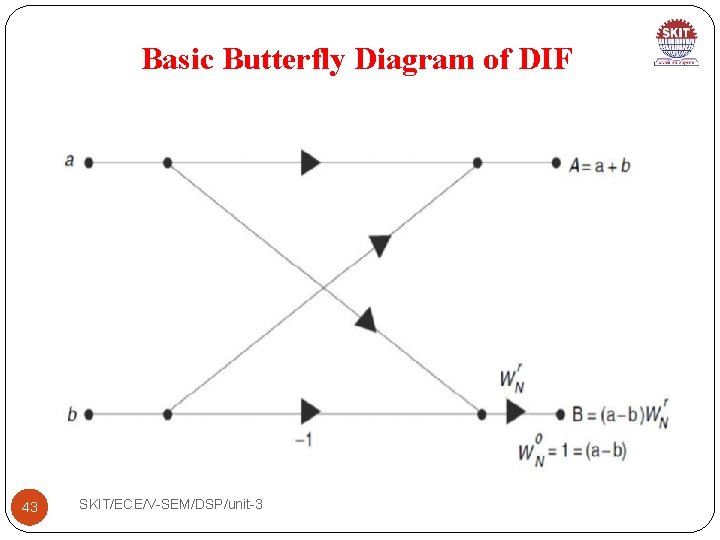

Basic Butterfly Diagram of DIF 43 SKIT/ECE/V-SEM/DSP/unit-3

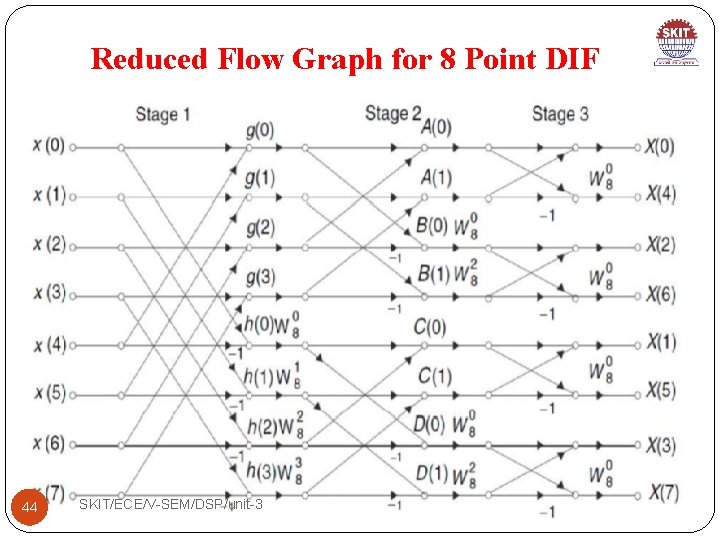

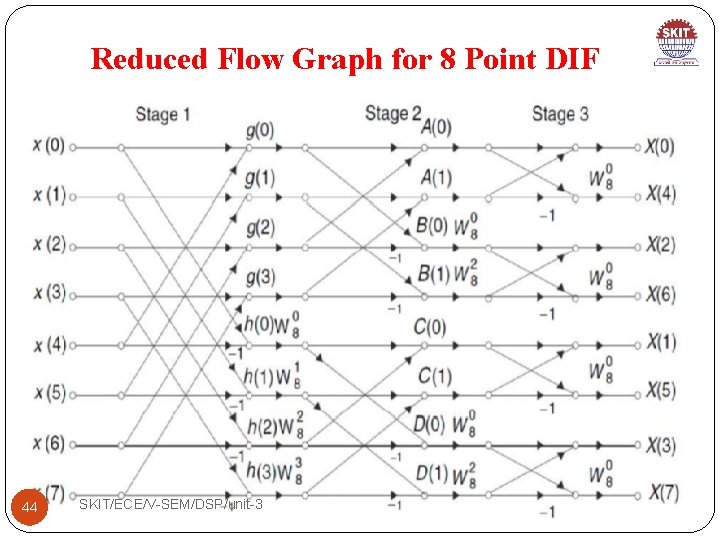

Reduced Flow Graph for 8 Point DIF 44 SKIT/ECE/V-SEM/DSP/unit-3

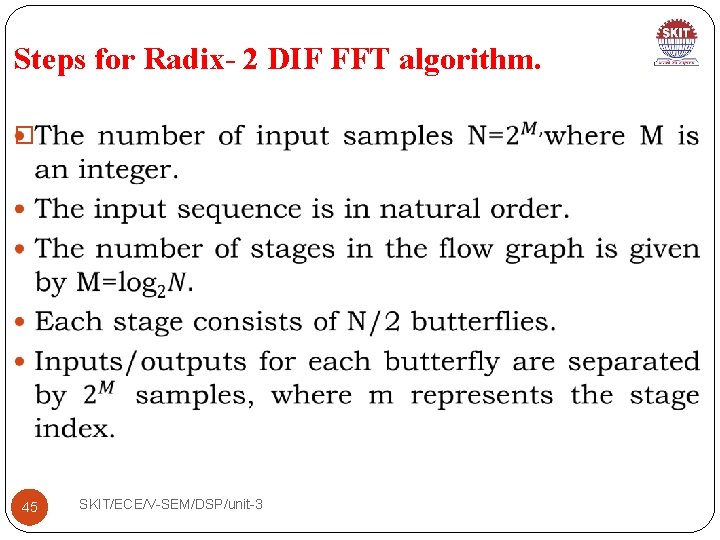

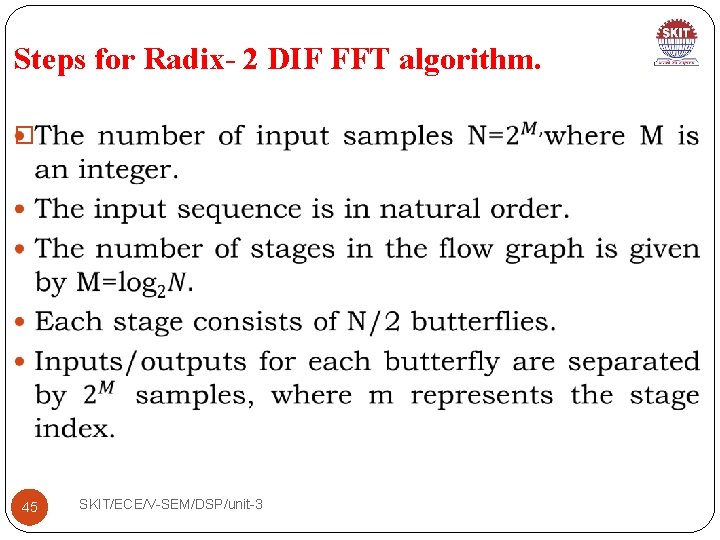

Steps for Radix- 2 DIF FFT algorithm. � 45 SKIT/ECE/V-SEM/DSP/unit-3

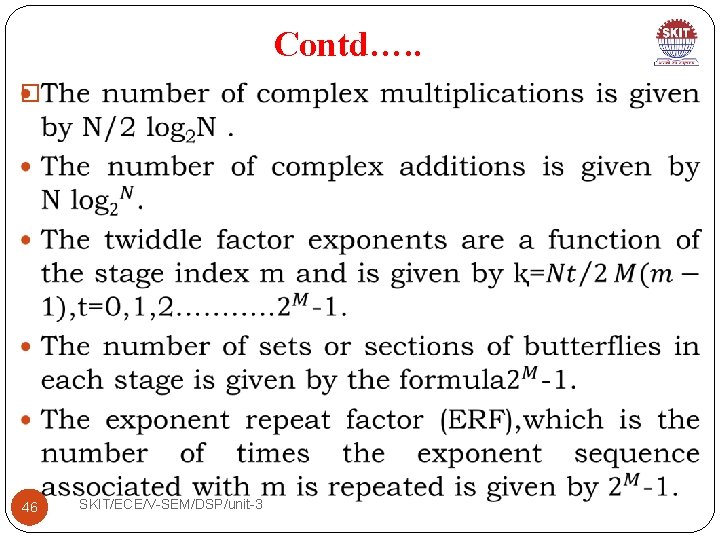

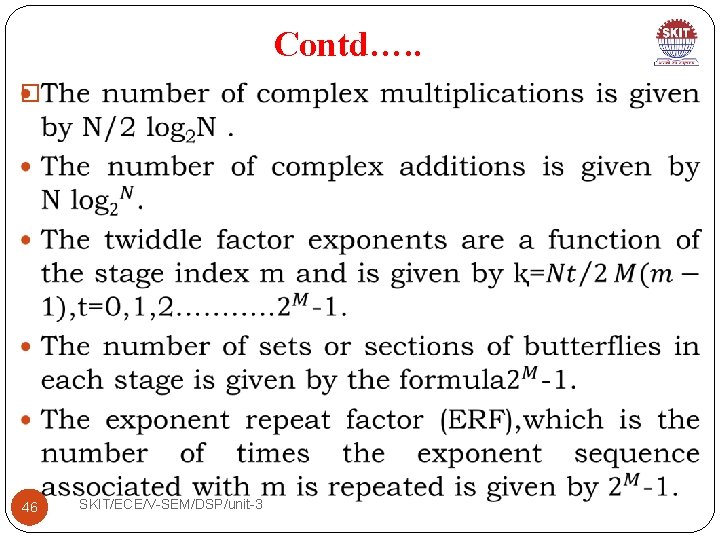

Contd…. . � 46 SKIT/ECE/V-SEM/DSP/unit-3

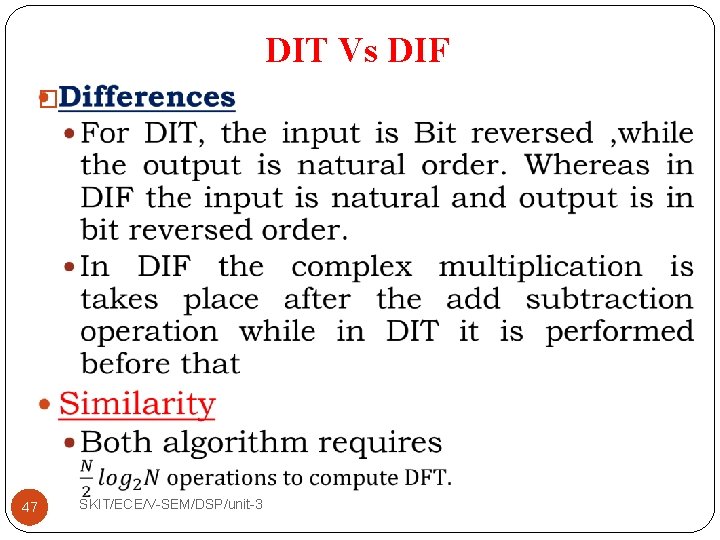

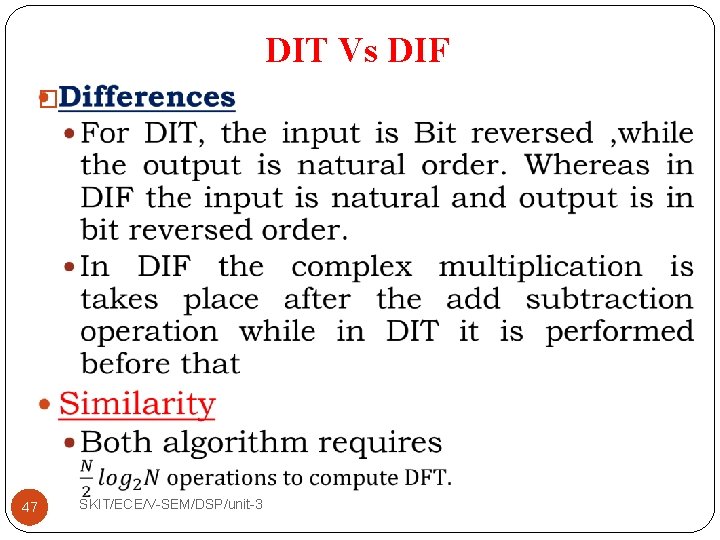

DIT Vs DIF � 47 SKIT/ECE/V-SEM/DSP/unit-3

Lecture No. - 3 -5 �Tutorial on Fast Fourier Transform 48 SKIT/ECE/V-SEM/DSP/unit-3

Tutorial Q 1. Find the 8 Point DFT of the sequence {2, 1, 1, 2, 1, 2} by using radix 2 DIT FFT. x(n)= Q 2. Determine the 8 -Point DFT of the sequence given in the above question by using the DIF Algorithm. 49 SKIT/ECE/V-SEM/DSP/unit-3

Lecture No. - 3 -6 �Implementation of Discrete Time System 50 SKIT/ECE/V-SEM/DSP/unit-3

Implementation of Discrete Time System �The processing of the discrete time signal by the digital hardware involves mathematical operations like addition, multiplications and delay. �Also the calculations are performed either by using fixed point arithmetic or floating point arithmetic. �The time taken to process the discrete time signal and the computational complexity, depend on number of calculations involved and the type of arithmetic used for computation. �These issues are addressed in structure for realization of discrete time system. 51 SKIT/ECE/V-SEM/DSP/unit-3

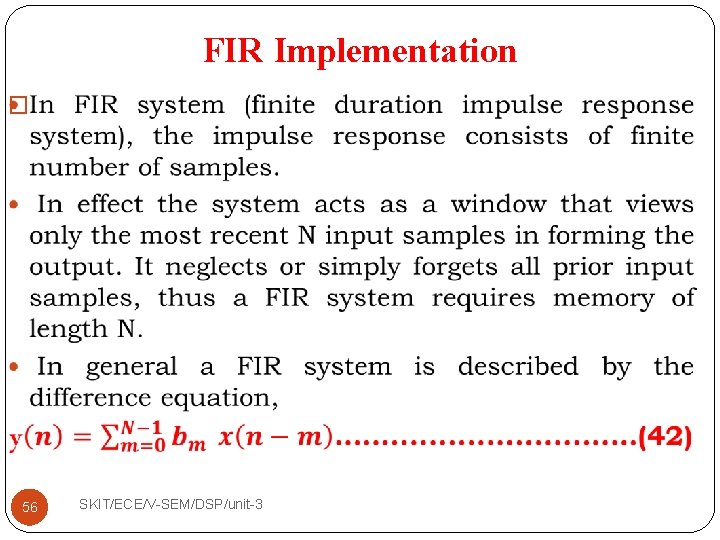

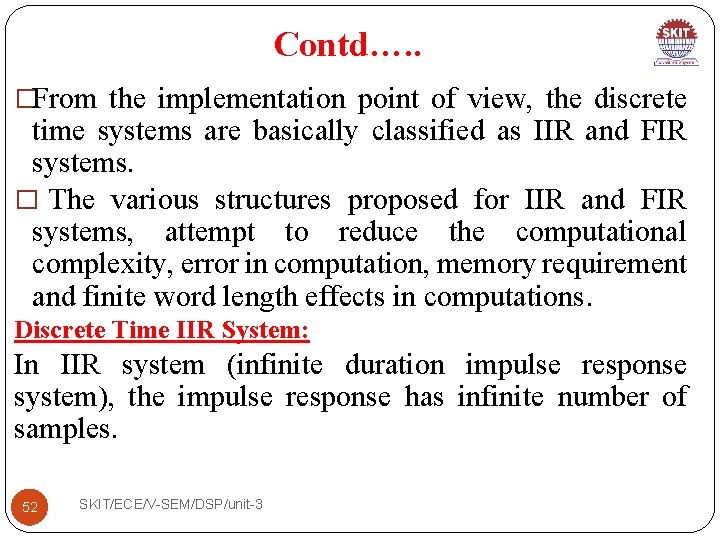

Contd…. . �From the implementation point of view, the discrete time systems are basically classified as IIR and FIR systems. � The various structures proposed for IIR and FIR systems, attempt to reduce the computational complexity, error in computation, memory requirement and finite word length effects in computations. Discrete Time IIR System: In IIR system (infinite duration impulse response system), the impulse response has infinite number of samples. 52 SKIT/ECE/V-SEM/DSP/unit-3

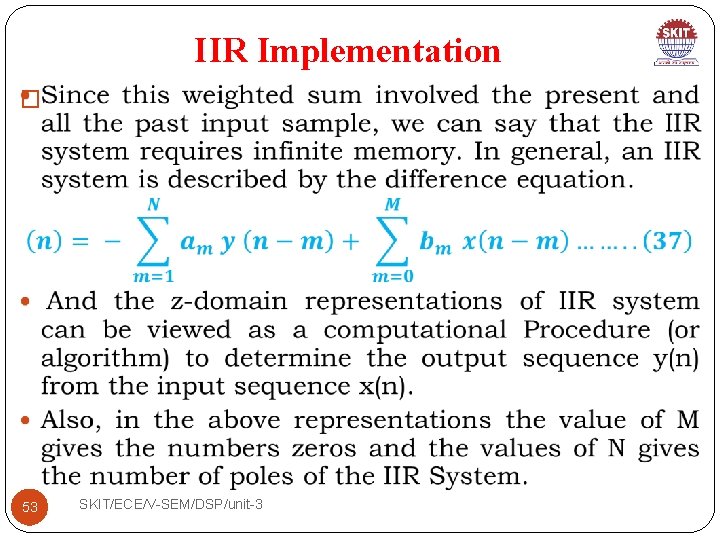

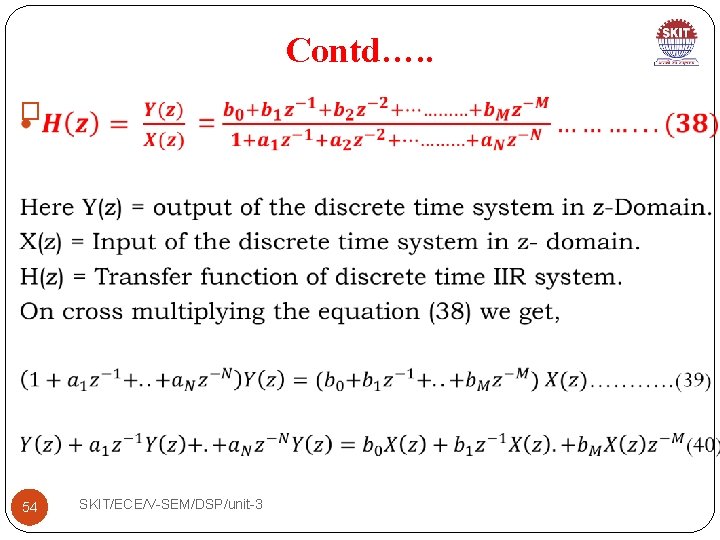

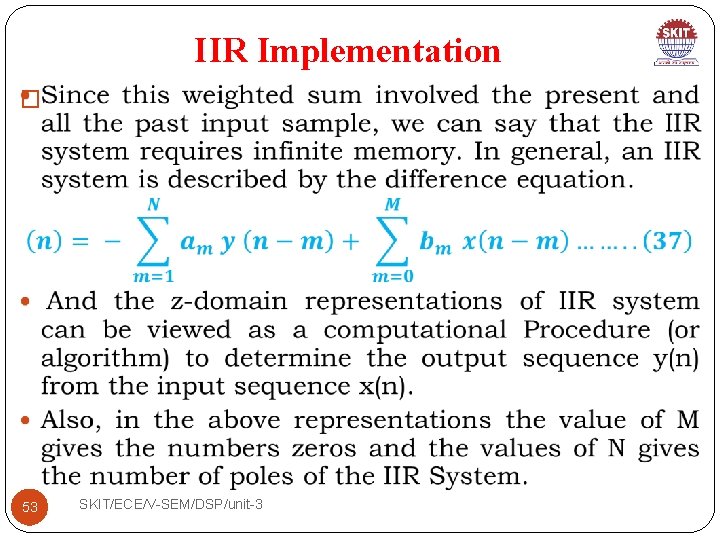

IIR Implementation � 53 SKIT/ECE/V-SEM/DSP/unit-3

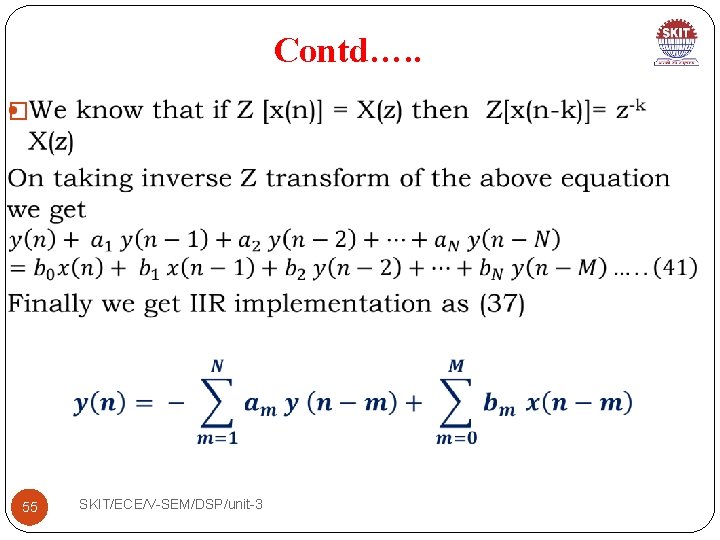

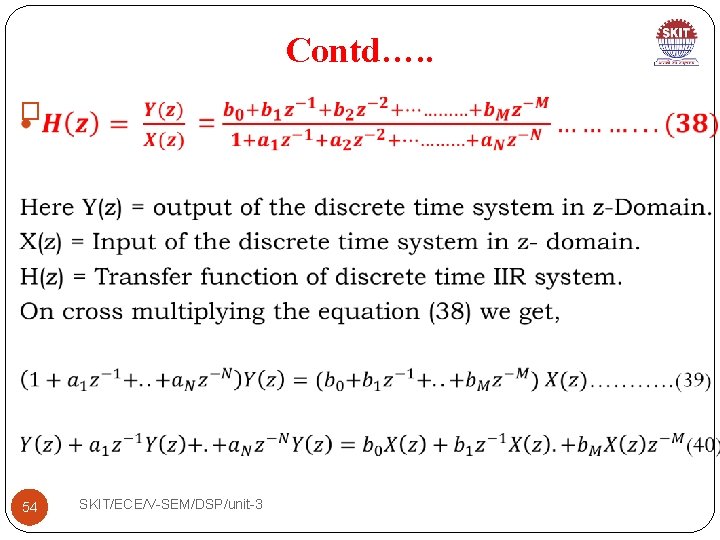

Contd…. . � 54 SKIT/ECE/V-SEM/DSP/unit-3

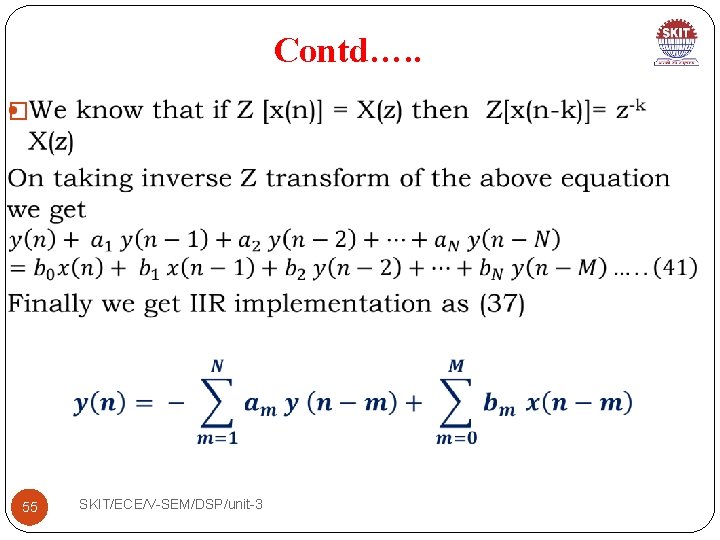

Contd…. . � 55 SKIT/ECE/V-SEM/DSP/unit-3

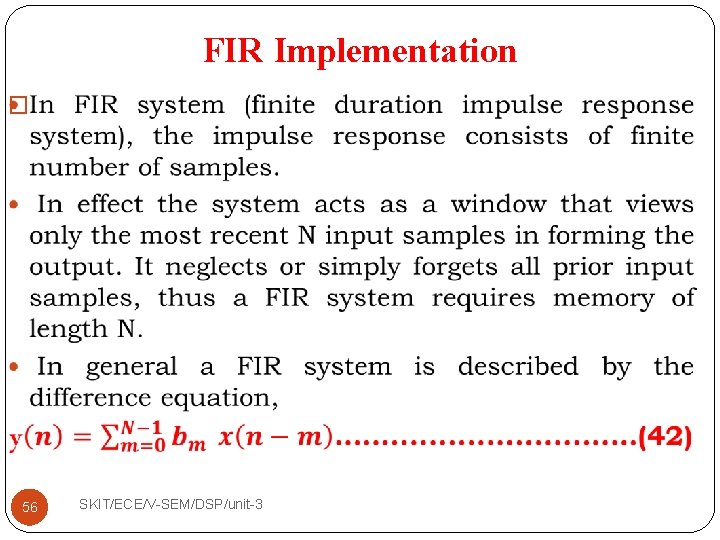

FIR Implementation � 56 SKIT/ECE/V-SEM/DSP/unit-3

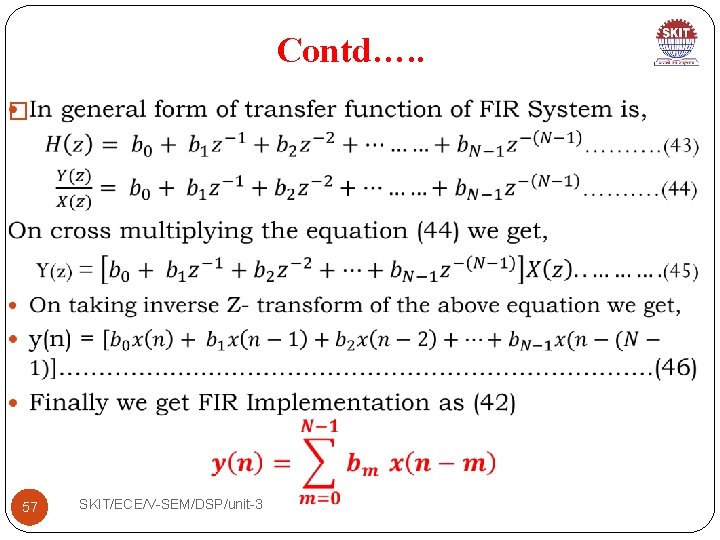

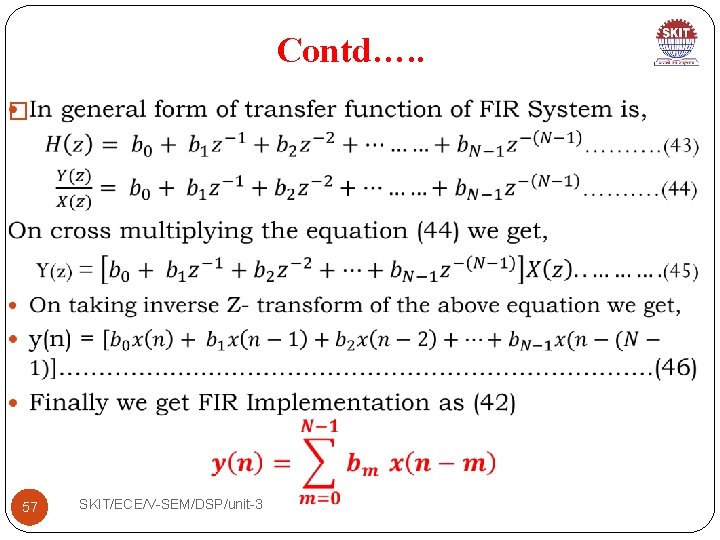

Contd…. . � 57 SKIT/ECE/V-SEM/DSP/unit-3

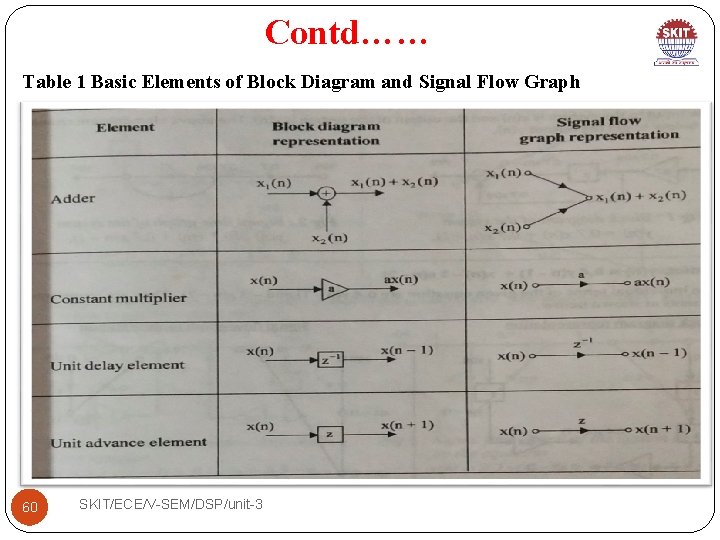

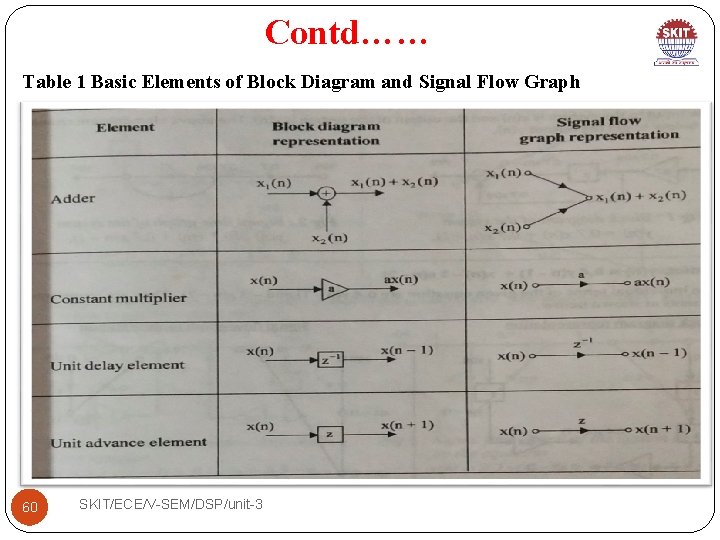

Realization of Systems � Block Diagram and Signal Flow Graph Representation of Discrete Time System �The discrete time system can be represented diagrammatically by block diagram or signal flow graph. These diagrammatic representations are useful for physical implementation of discrete time system in hardware or software. �The basic elements employed in block diagram or signal flow graph are adder, constant multiplier, unit delay element and unit advance element. 58 SKIT/ECE/V-SEM/DSP/unit-3

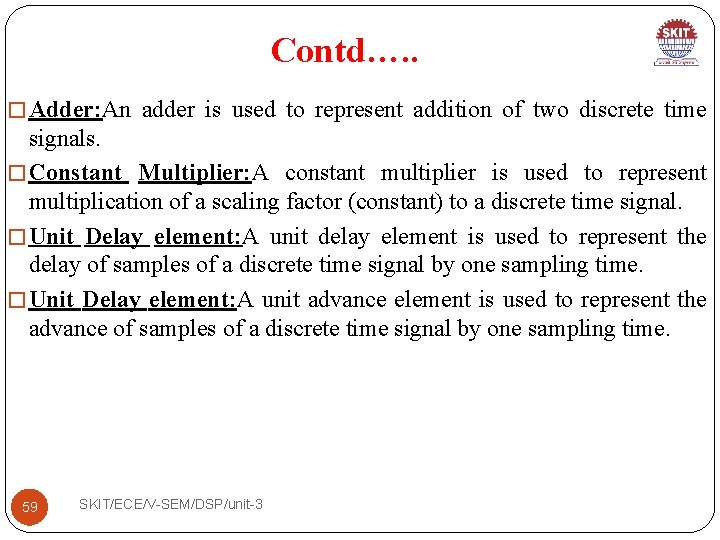

Contd…. . � Adder: An adder is used to represent addition of two discrete time signals. � Constant Multiplier: A constant multiplier is used to represent multiplication of a scaling factor (constant) to a discrete time signal. � Unit Delay element: A unit delay element is used to represent the delay of samples of a discrete time signal by one sampling time. � Unit Delay element: A unit advance element is used to represent the advance of samples of a discrete time signal by one sampling time. 59 SKIT/ECE/V-SEM/DSP/unit-3

Contd…… Table 1 Basic Elements of Block Diagram and Signal Flow Graph 60 SKIT/ECE/V-SEM/DSP/unit-3

Lecture No. - 3 -7 �Realization of IIR Filters 61 SKIT/ECE/V-SEM/DSP/unit-3

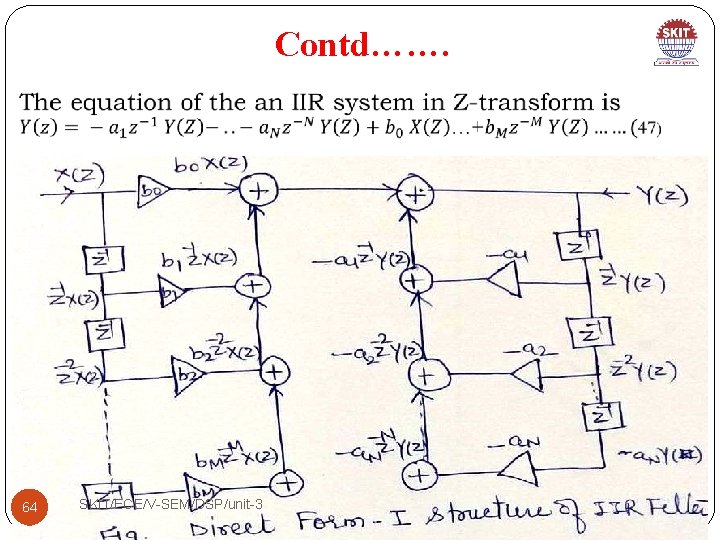

Realization of IIR Systems �The different types of structures for realizing the IIR systems are : Ø Direct form-II Ø Cascade form Realization Ø Parallel form Realization �Direct form-I structure �Consider the equation (20) for the IIR filter it can be directly represented by the block diagram. �The direct form–I structure provides a direct relationship between time domain and z-domain equations. 62 SKIT/ECE/V-SEM/DSP/unit-3

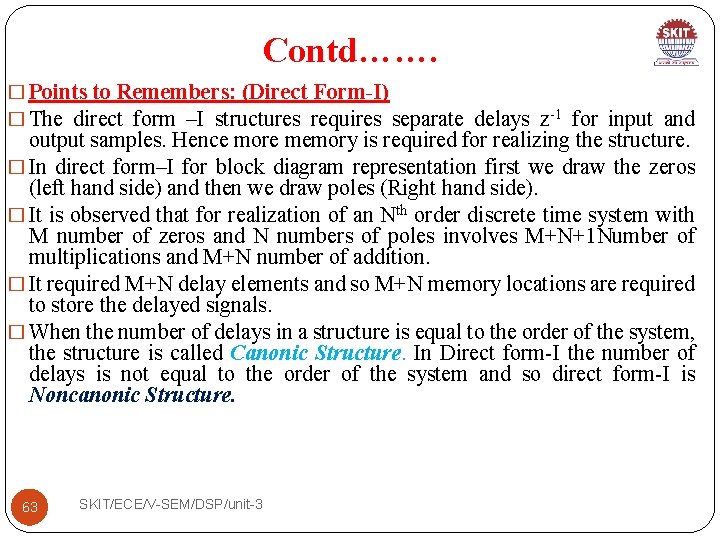

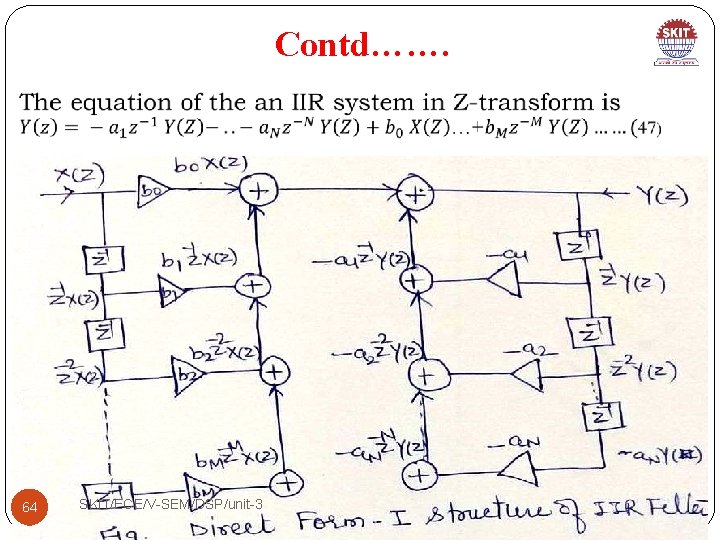

Contd……. � Points to Remembers: (Direct Form-I) � The direct form –I structures requires separate delays z-1 for input and output samples. Hence more memory is required for realizing the structure. � In direct form–I for block diagram representation first we draw the zeros (left hand side) and then we draw poles (Right hand side). � It is observed that for realization of an Nth order discrete time system with M number of zeros and N numbers of poles involves M+N+1 Number of multiplications and M+N number of addition. � It required M+N delay elements and so M+N memory locations are required to store the delayed signals. � When the number of delays in a structure is equal to the order of the system, the structure is called Canonic Structure. In Direct form-I the number of delays is not equal to the order of the system and so direct form-I is Noncanonic Structure. 63 SKIT/ECE/V-SEM/DSP/unit-3

Contd……. 64 SKIT/ECE/V-SEM/DSP/unit-3

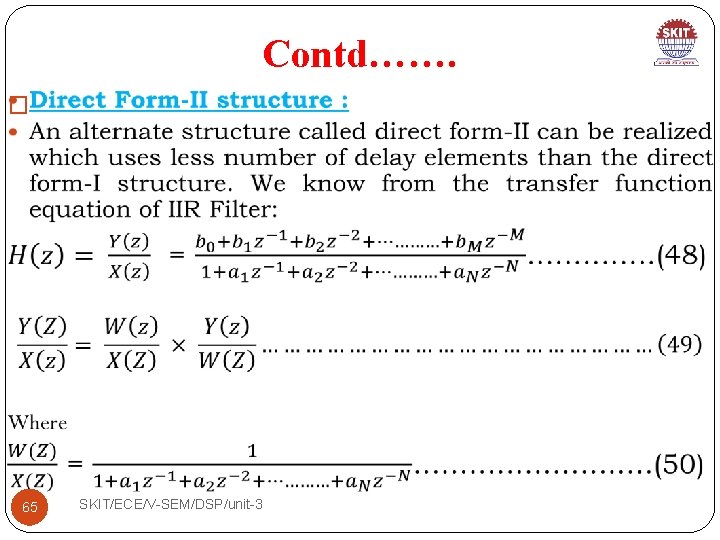

Contd……. � 65 SKIT/ECE/V-SEM/DSP/unit-3

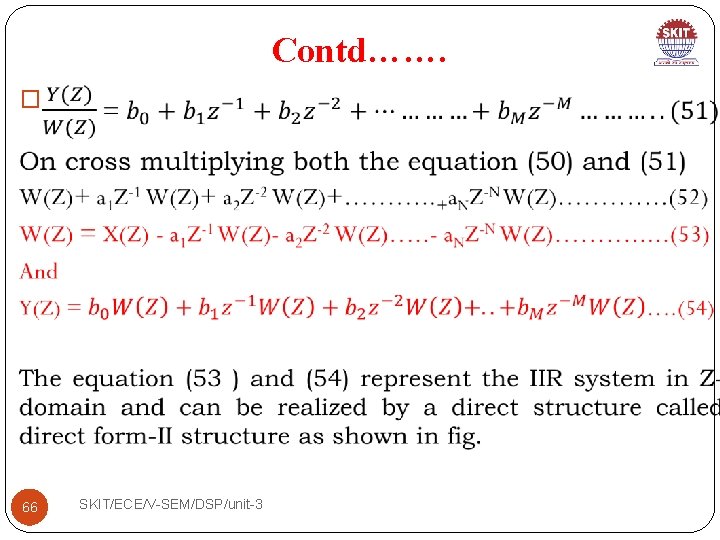

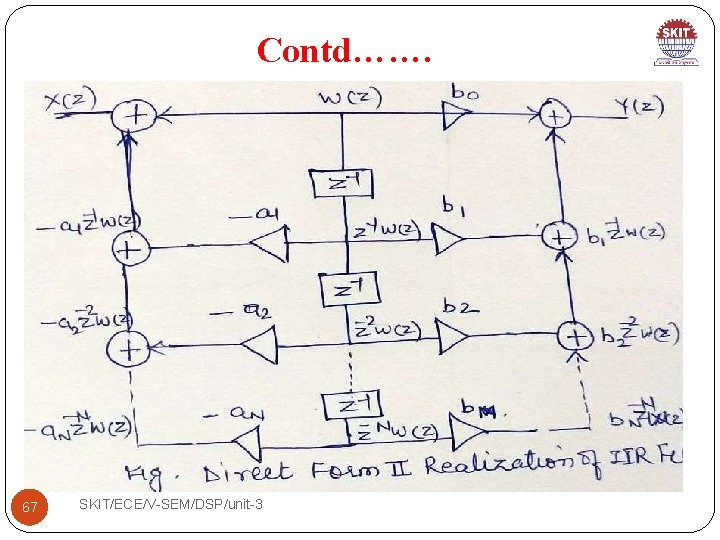

Contd……. � 66 SKIT/ECE/V-SEM/DSP/unit-3

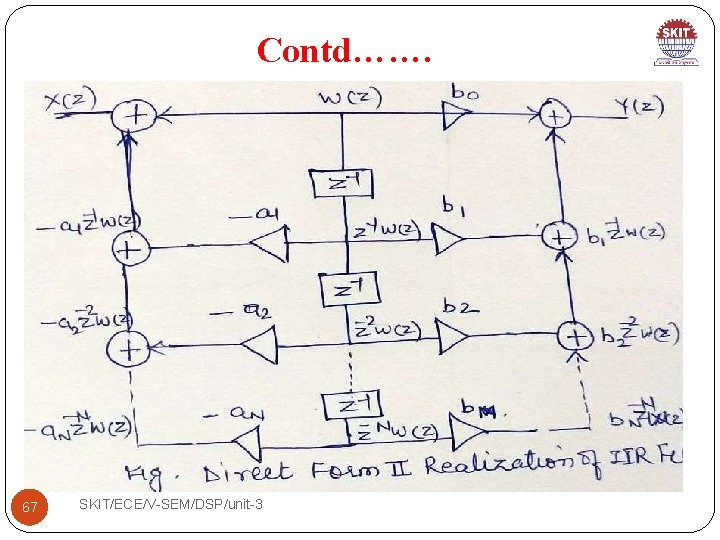

Contd……. 67 SKIT/ECE/V-SEM/DSP/unit-3

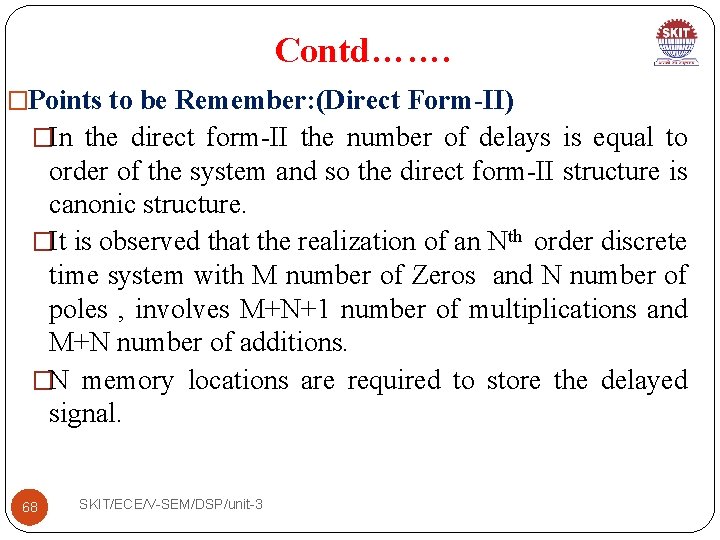

Contd……. �Points to be Remember: (Direct Form-II) �In the direct form-II the number of delays is equal to order of the system and so the direct form-II structure is canonic structure. �It is observed that the realization of an Nth order discrete time system with M number of Zeros and N number of poles , involves M+N+1 number of multiplications and M+N number of additions. �N memory locations are required to store the delayed signal. 68 SKIT/ECE/V-SEM/DSP/unit-3

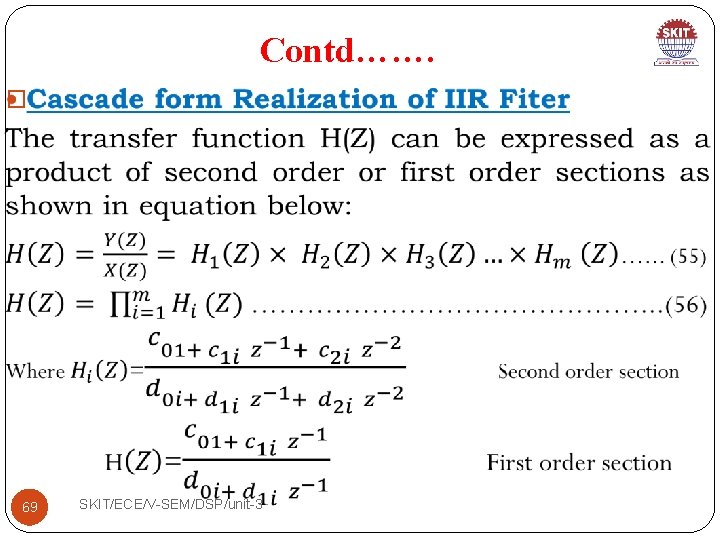

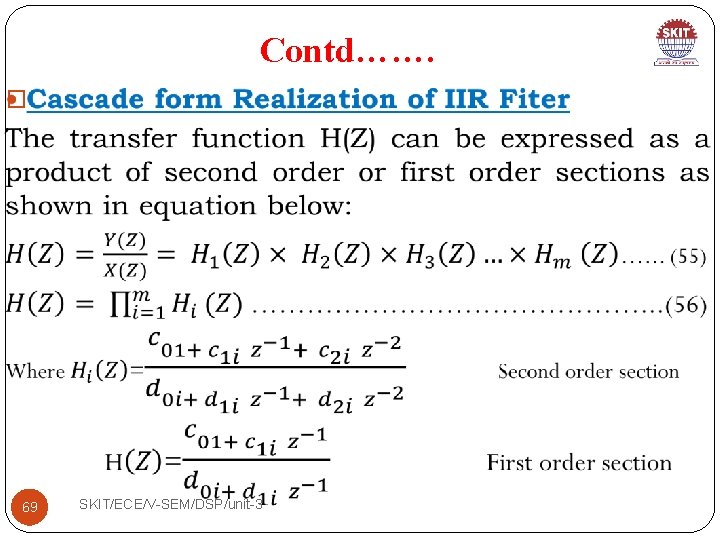

Contd……. � 69 SKIT/ECE/V-SEM/DSP/unit-3

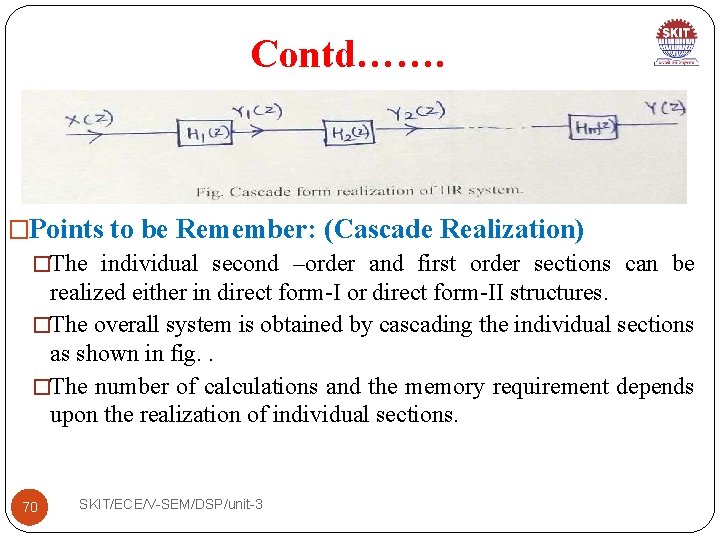

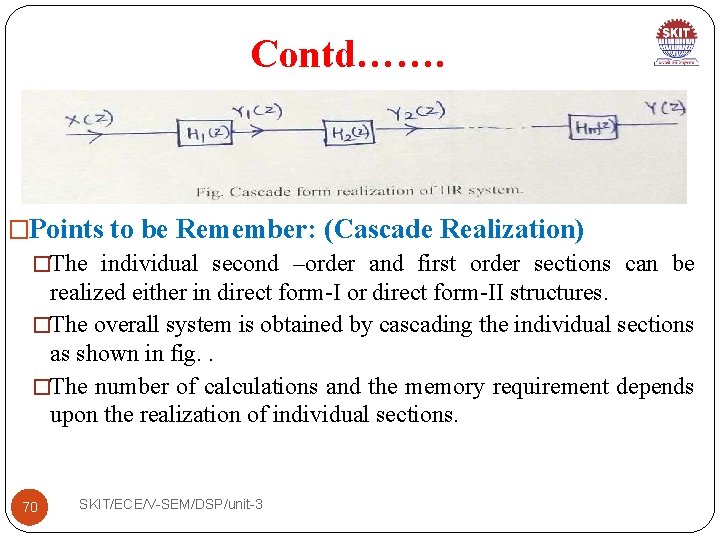

Contd……. �Points to be Remember: (Cascade Realization) �The individual second –order and first order sections can be realized either in direct form-I or direct form-II structures. �The overall system is obtained by cascading the individual sections as shown in fig. . �The number of calculations and the memory requirement depends upon the realization of individual sections. 70 SKIT/ECE/V-SEM/DSP/unit-3

Contd……. �The difficulties in cascade structure are, �Decision of pairing poles and zeros. �Deciding the order of cascading the first and second order sections. �Scaling multipliers should be provided between individual sections to prevent the system variables from becoming too large or too small. 71 SKIT/ECE/V-SEM/DSP/unit-3

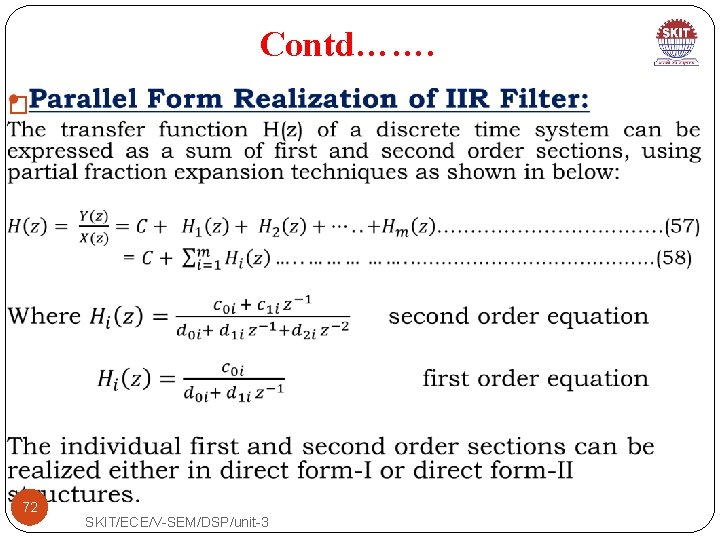

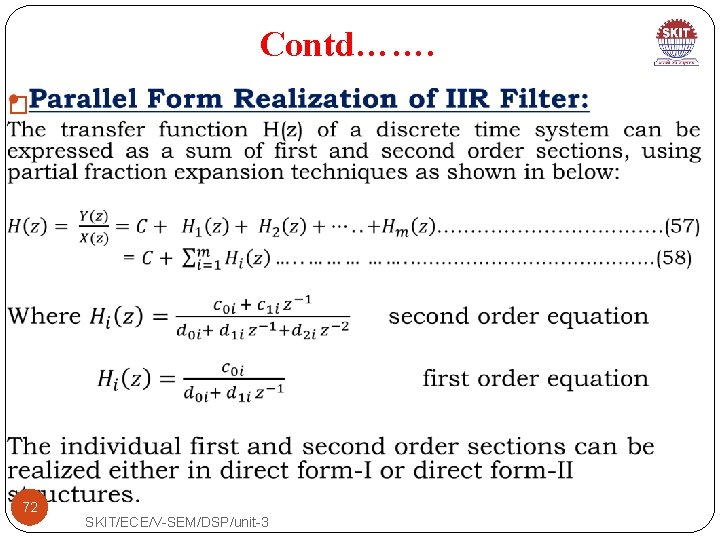

Contd……. � 72 SKIT/ECE/V-SEM/DSP/unit-3

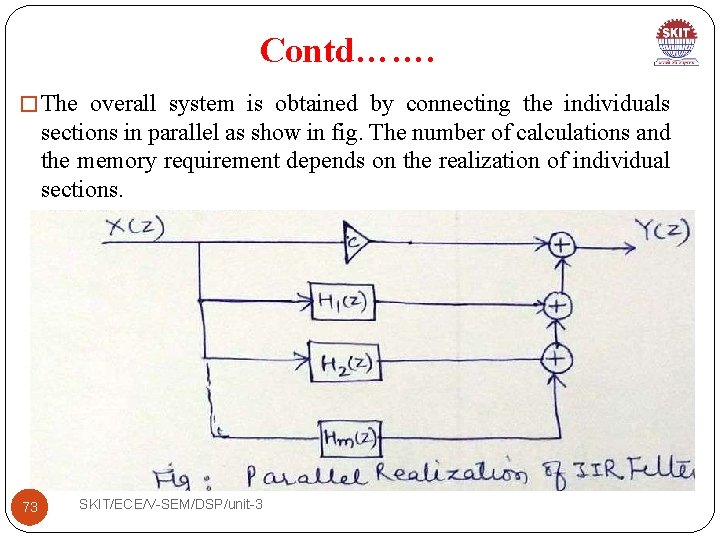

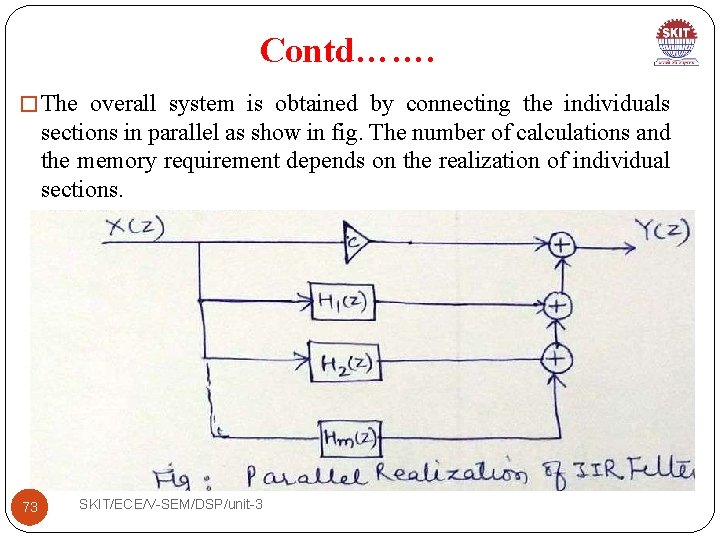

Contd……. � The overall system is obtained by connecting the individuals sections in parallel as show in fig. The number of calculations and the memory requirement depends on the realization of individual sections. 73 SKIT/ECE/V-SEM/DSP/unit-3

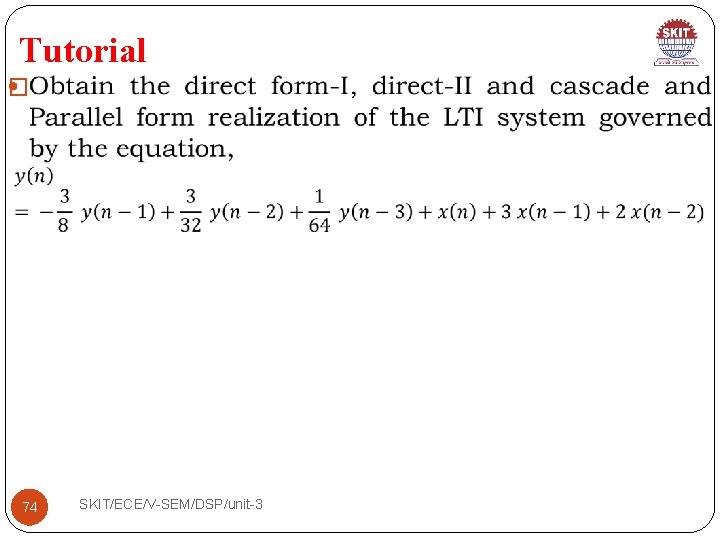

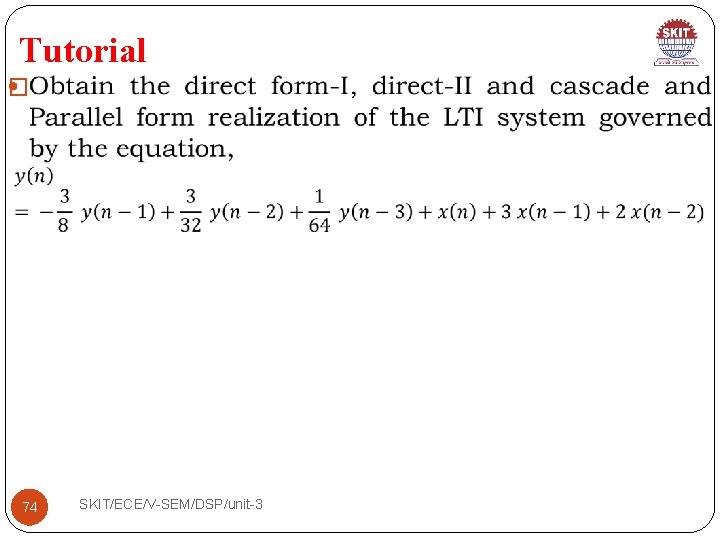

Tutorial � 74 SKIT/ECE/V-SEM/DSP/unit-3

Lecture No. - 3 -8 �Realization of IIR Filters 75 SKIT/ECE/V-SEM/DSP/unit-3

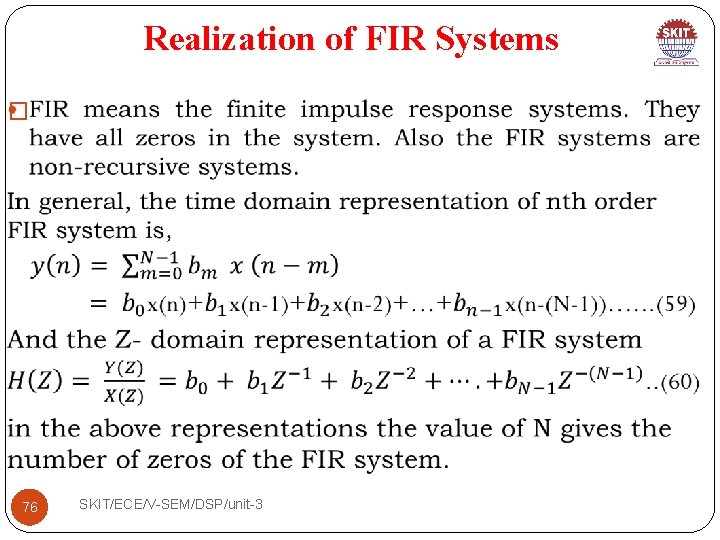

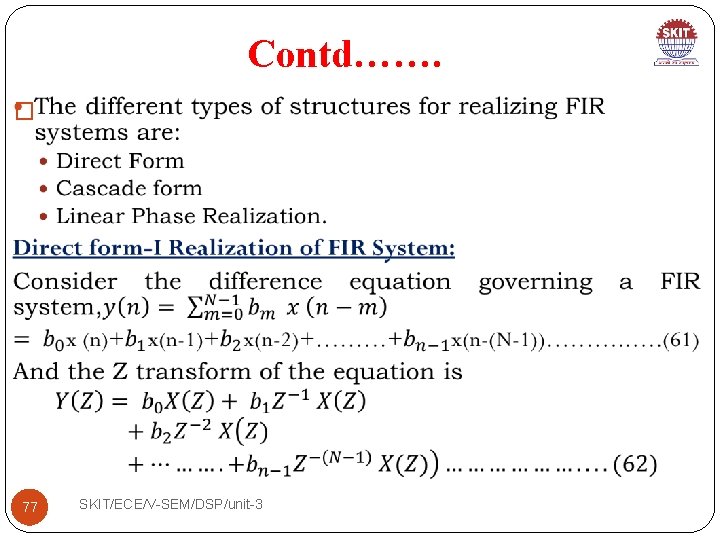

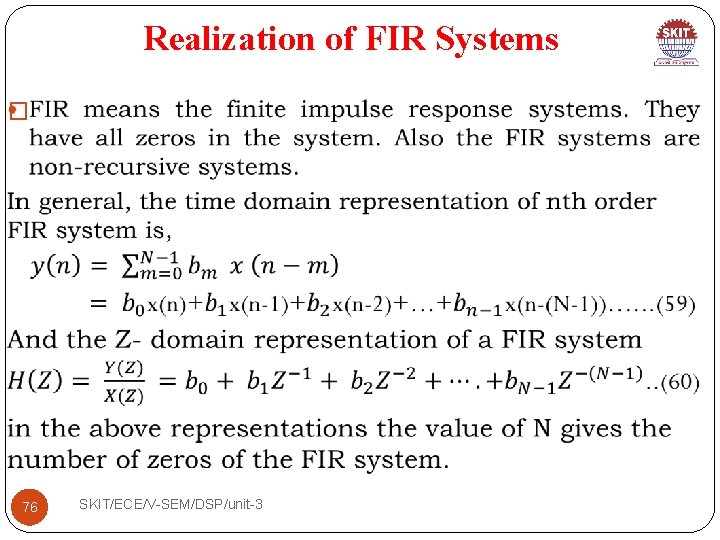

Realization of FIR Systems � 76 SKIT/ECE/V-SEM/DSP/unit-3

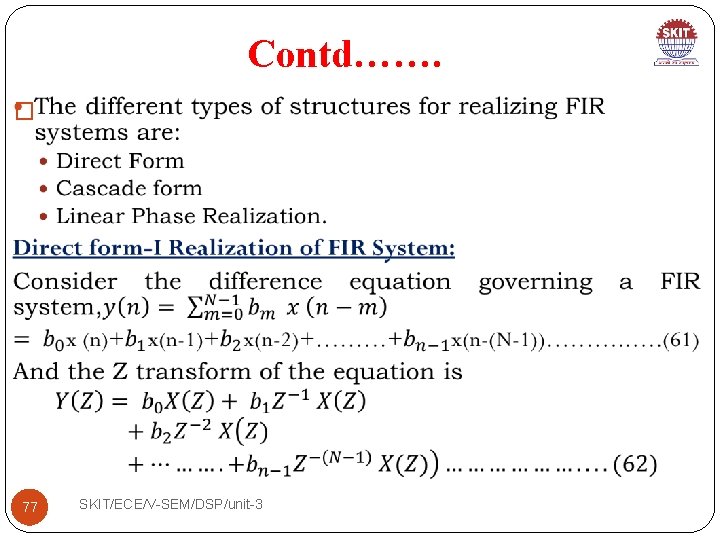

Contd……. � 77 SKIT/ECE/V-SEM/DSP/unit-3

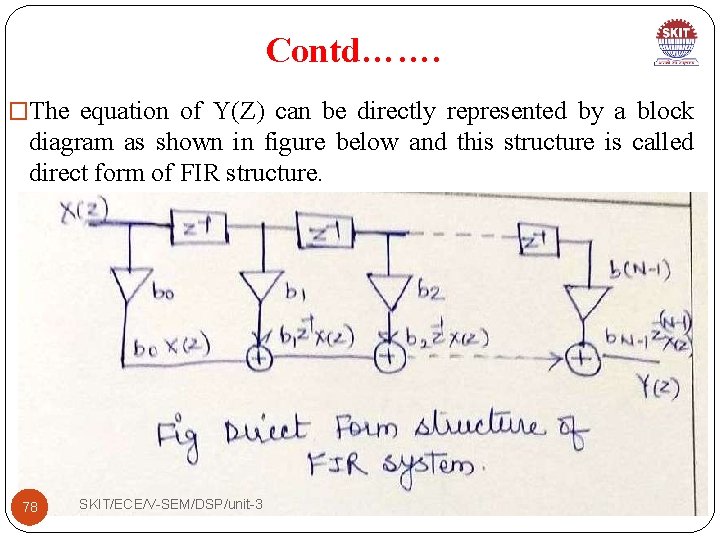

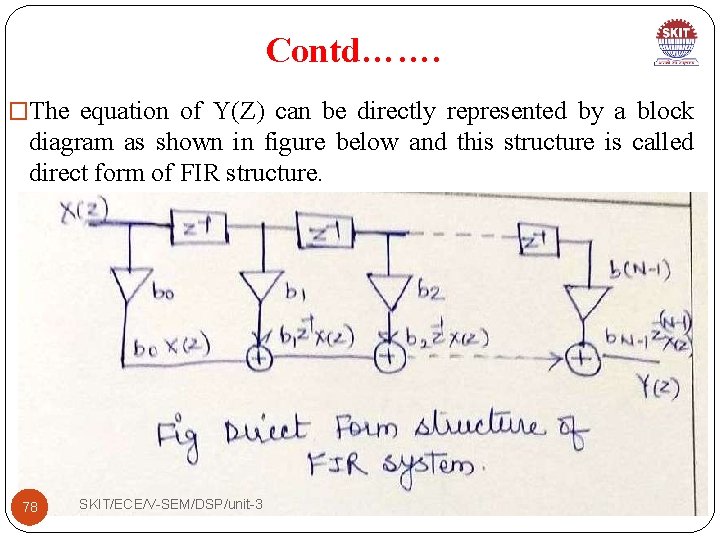

Contd……. �The equation of Y(Z) can be directly represented by a block diagram as shown in figure below and this structure is called direct form of FIR structure. 78 SKIT/ECE/V-SEM/DSP/unit-3

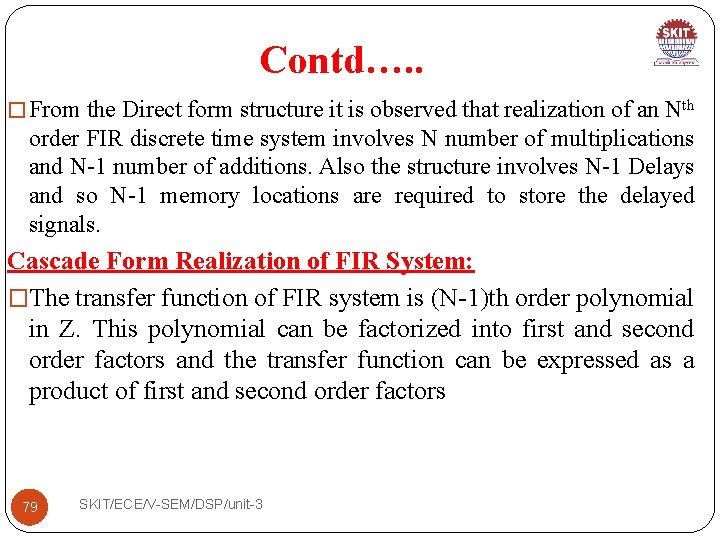

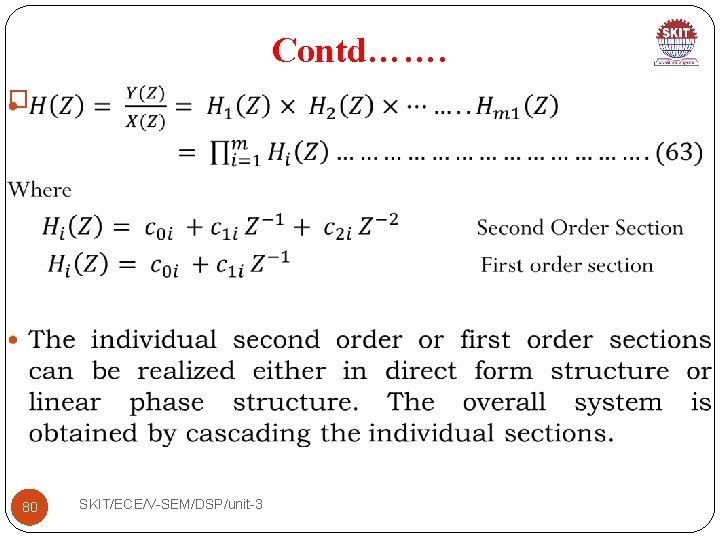

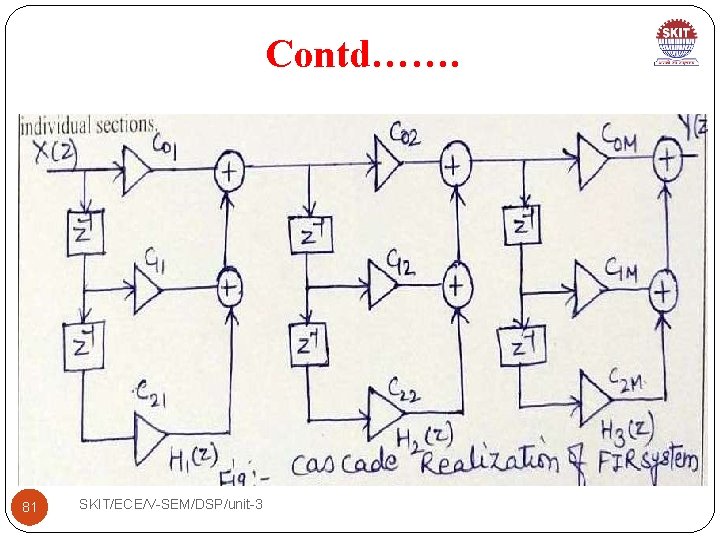

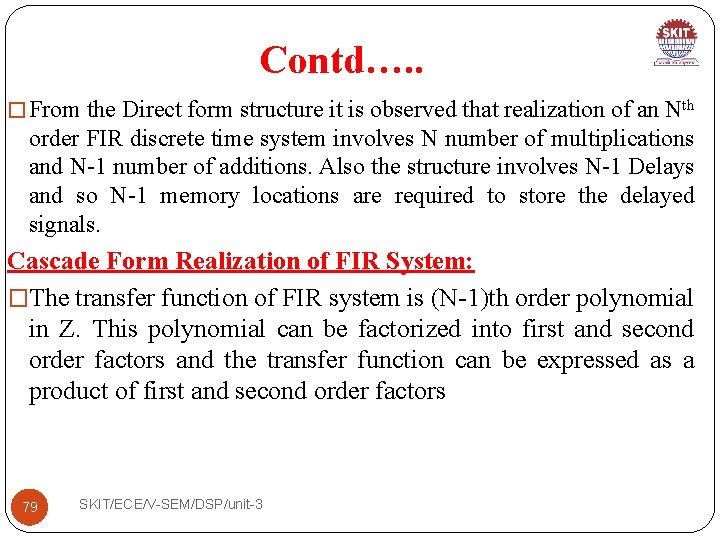

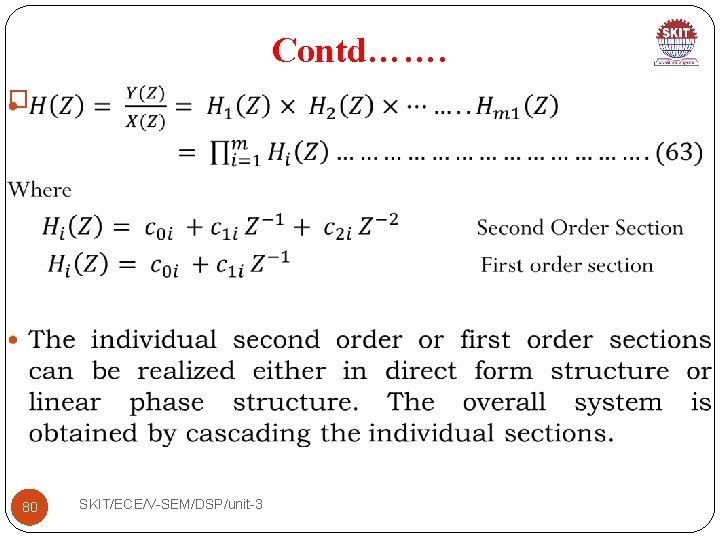

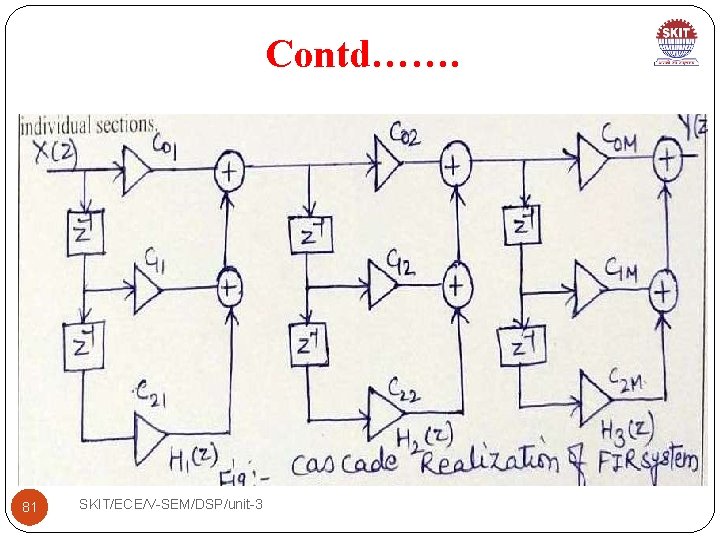

Contd…. . � From the Direct form structure it is observed that realization of an Nth order FIR discrete time system involves N number of multiplications and N-1 number of additions. Also the structure involves N-1 Delays and so N-1 memory locations are required to store the delayed signals. Cascade Form Realization of FIR System: �The transfer function of FIR system is (N-1)th order polynomial in Z. This polynomial can be factorized into first and second order factors and the transfer function can be expressed as a product of first and second order factors 79 SKIT/ECE/V-SEM/DSP/unit-3

Contd……. � 80 SKIT/ECE/V-SEM/DSP/unit-3

Contd……. 81 SKIT/ECE/V-SEM/DSP/unit-3

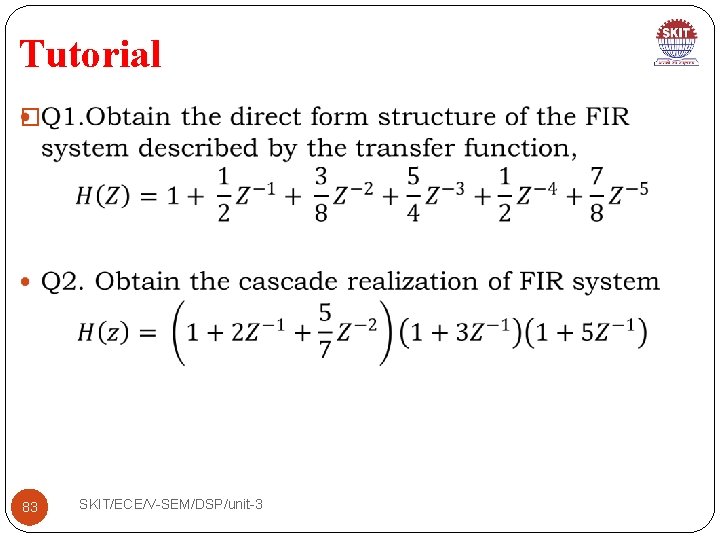

Lecture No. - 3 -9 �Tutorial on Realization of Filters 82 SKIT/ECE/V-SEM/DSP/unit-3

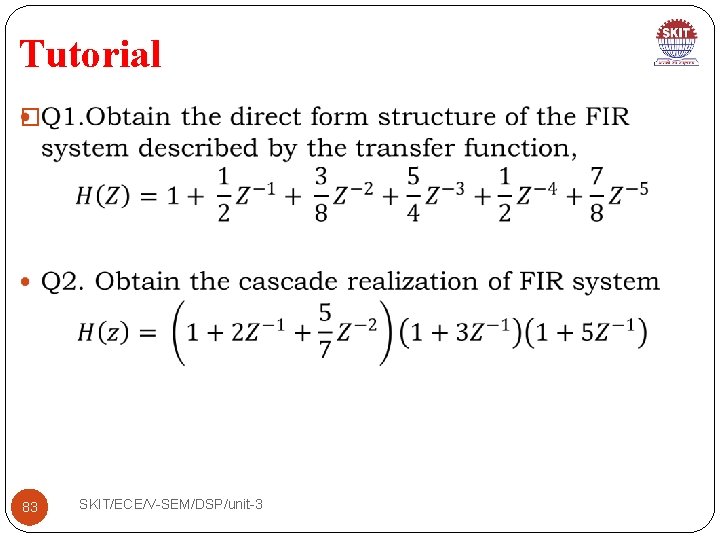

Tutorial � 83 SKIT/ECE/V-SEM/DSP/unit-3