SVT upgrade status A Annovi for the SVT

- Slides: 20

SVT upgrade status A. Annovi for the SVT group 22/04/05 1

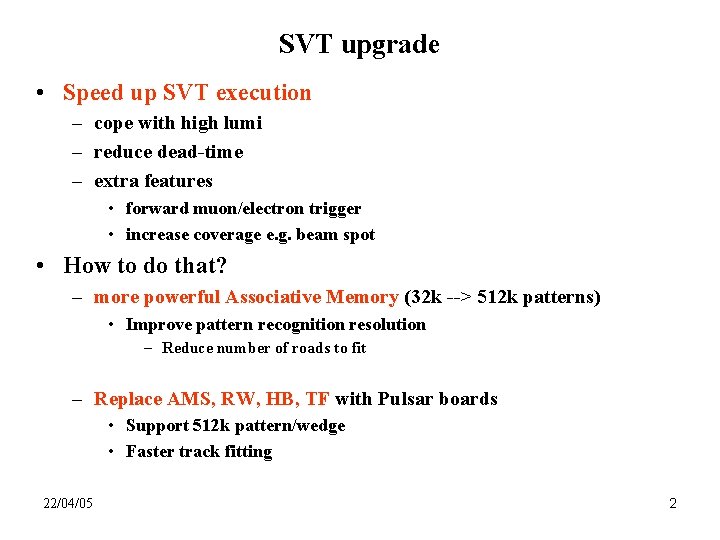

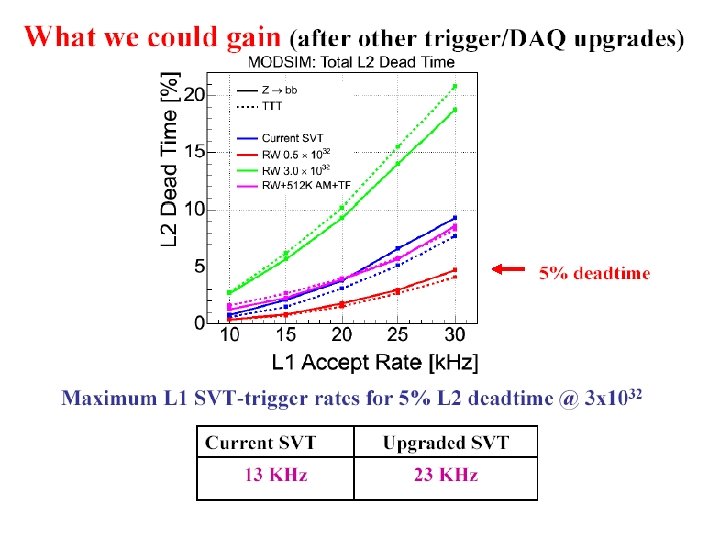

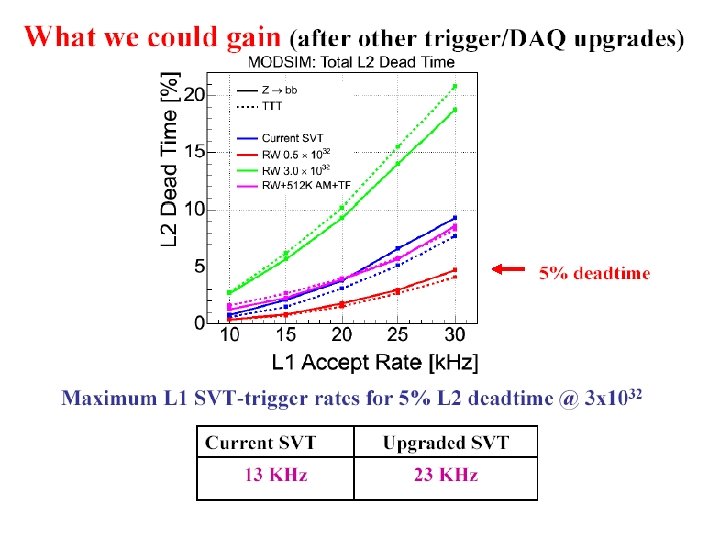

SVT upgrade • Speed up SVT execution – cope with high lumi – reduce dead-time – extra features • forward muon/electron trigger • increase coverage e. g. beam spot • How to do that? – more powerful Associative Memory (32 k --> 512 k patterns) • Improve pattern recognition resolution – Reduce number of roads to fit – Replace AMS, RW, HB, TF with Pulsar boards • Support 512 k pattern/wedge • Faster track fitting 22/04/05 2

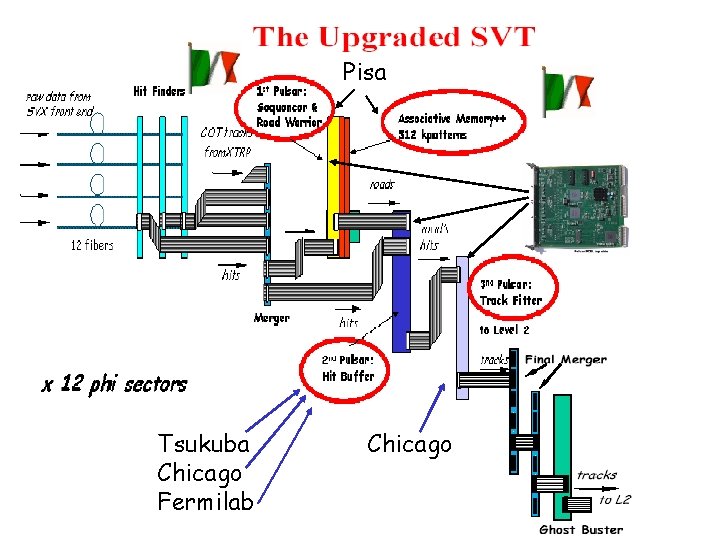

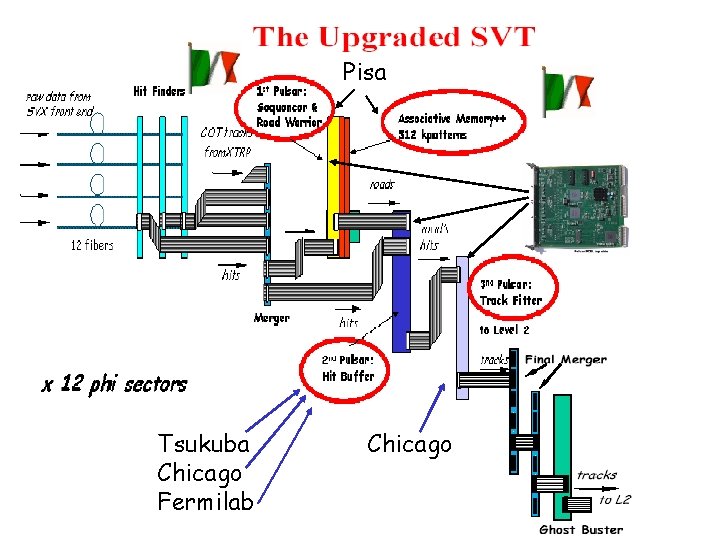

Pisa 22/04/05 Tsukuba Chicago Fermilab Chicago 3

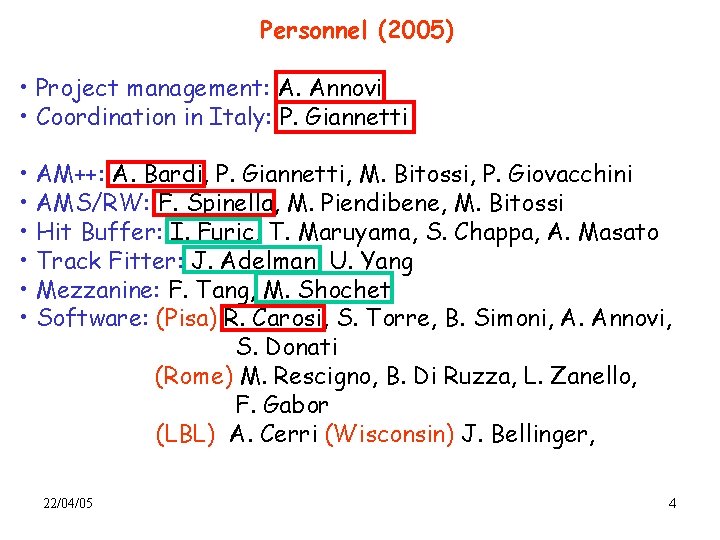

Personnel (2005) • Project management: A. Annovi • Coordination in Italy: P. Giannetti • AM++: A. Bardi, P. Giannetti, M. Bitossi, P. Giovacchini • AMS/RW: F. Spinella, M. Piendibene, M. Bitossi • Hit Buffer: I. Furic, T. Maruyama, S. Chappa, A. Masato • Track Fitter: J. Adelman, U. Yang • Mezzanine: F. Tang, M. Shochet • Software: (Pisa) R. Carosi, S. Torre, B. Simoni, A. Annovi, S. Donati (Rome) M. Rescigno, B. Di Ruzza, L. Zanello, F. Gabor (LBL) A. Cerri (Wisconsin) J. Bellinger, 22/04/05 4

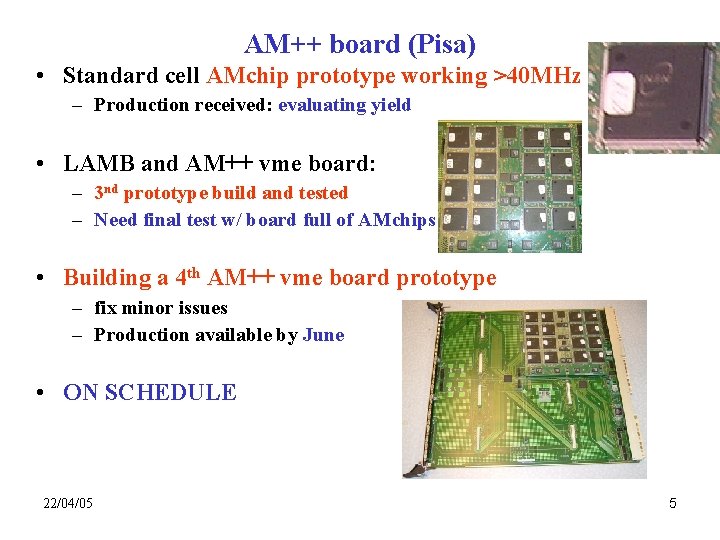

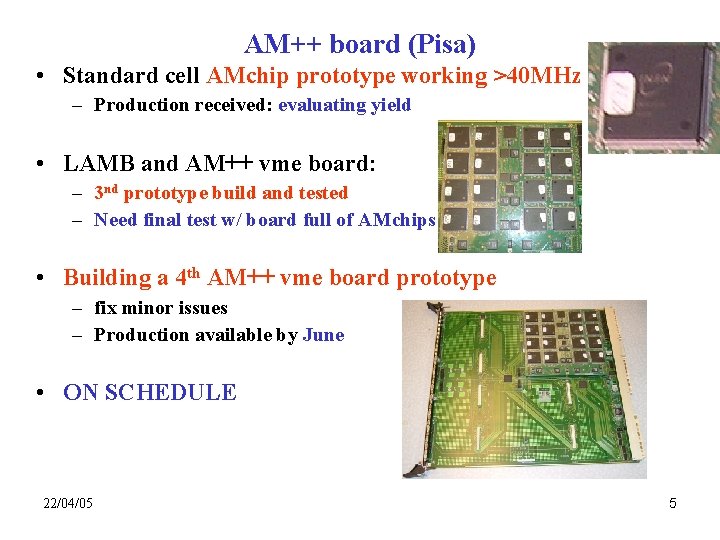

AM++ board (Pisa) • Standard cell AMchip prototype working >40 MHz – Production received: evaluating yield • LAMB and AM++ vme board: – 3 nd prototype build and tested – Need final test w/ board full of AMchips • Building a 4 th AM++ vme board prototype – fix minor issues – Production available by June • ON SCHEDULE 22/04/05 5

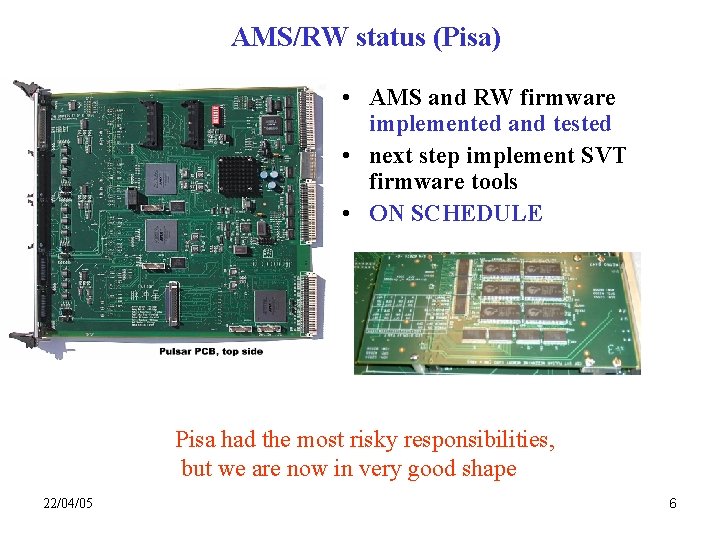

AMS/RW status (Pisa) • AMS and RW firmware implemented and tested • next step implement SVT firmware tools • ON SCHEDULE Pisa had the most risky responsibilities, but we are now in very good shape 22/04/05 6

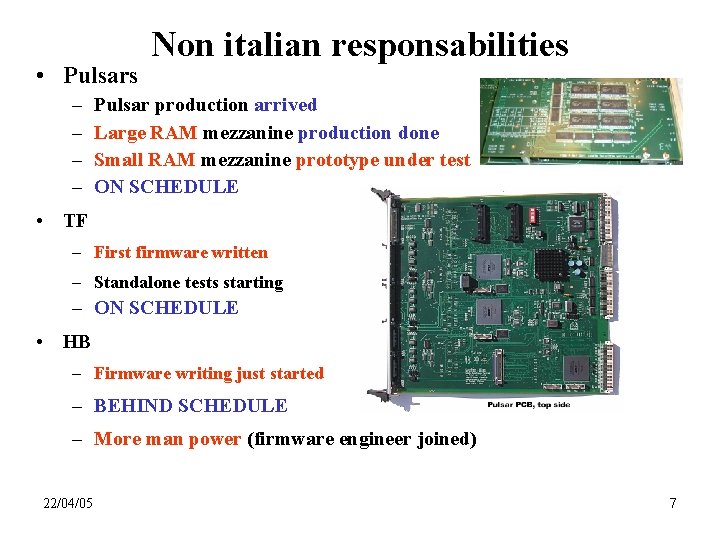

• Pulsars – – Non italian responsabilities Pulsar production arrived Large RAM mezzanine production done Small RAM mezzanine prototype under test ON SCHEDULE • TF – First firmware written – Standalone tests starting – ON SCHEDULE • HB – Firmware writing just started – BEHIND SCHEDULE – More man power (firmware engineer joined) 22/04/05 7

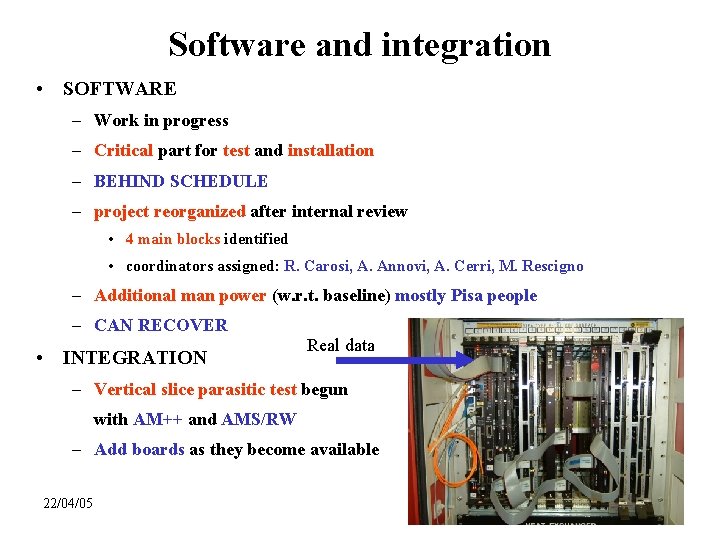

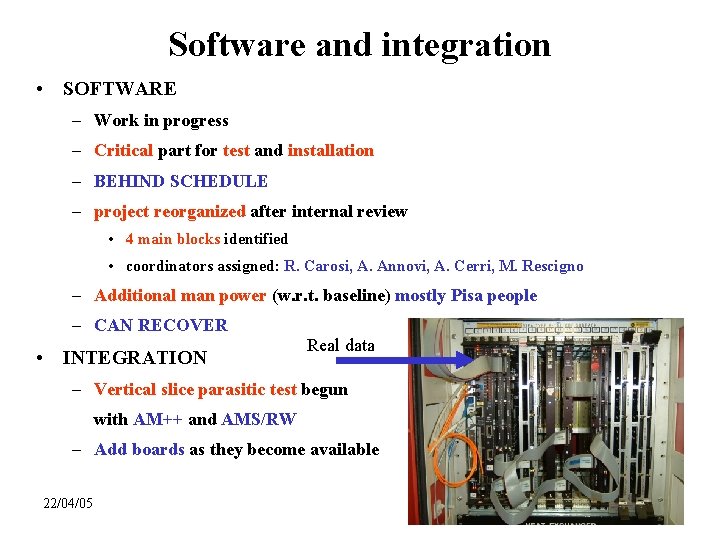

Software and integration • SOFTWARE – Work in progress – Critical part for test and installation – BEHIND SCHEDULE – project reorganized after internal review • 4 main blocks identified • coordinators assigned: R. Carosi, A. Annovi, A. Cerri, M. Rescigno – Additional man power (w. r. t. baseline) mostly Pisa people – CAN RECOVER • INTEGRATION Real data – Vertical slice parasitic test begun with AM++ and AMS/RW – Add boards as they become available 22/04/05 8

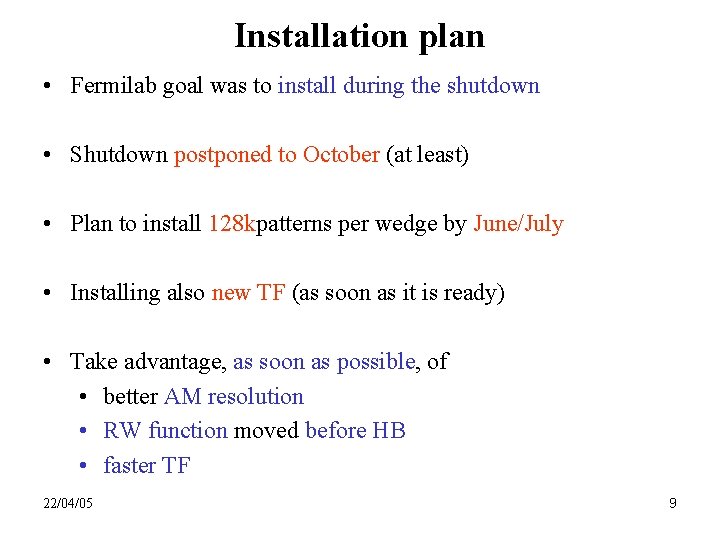

Installation plan • Fermilab goal was to install during the shutdown • Shutdown postponed to October (at least) • Plan to install 128 kpatterns per wedge by June/July • Installing also new TF (as soon as it is ready) • Take advantage, as soon as possible, of • better AM resolution • RW function moved before HB • faster TF 22/04/05 9

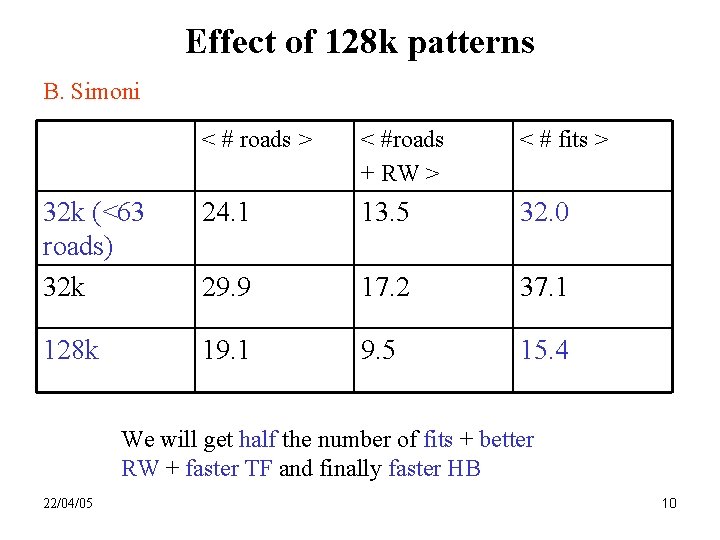

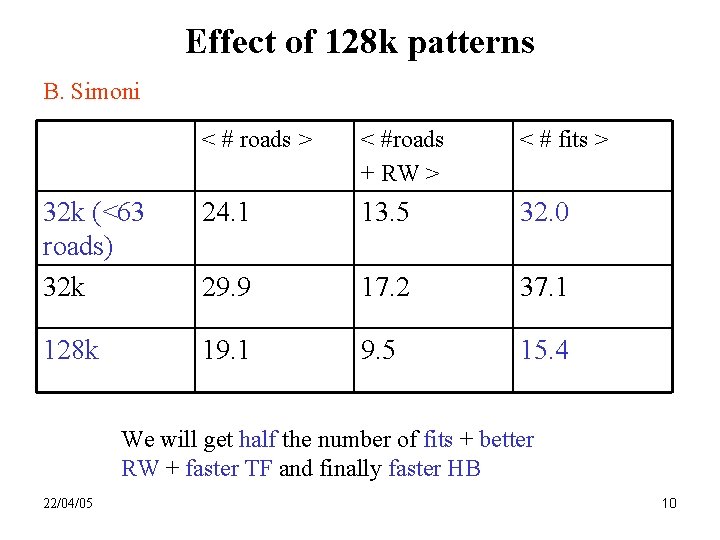

Effect of 128 k patterns B. Simoni < # roads > < #roads + RW > < # fits > 32 k (<63 roads) 32 k 24. 1 13. 5 32. 0 29. 9 17. 2 37. 1 128 k 19. 1 9. 5 15. 4 We will get half the number of fits + better RW + faster TF and finally faster HB 22/04/05 10

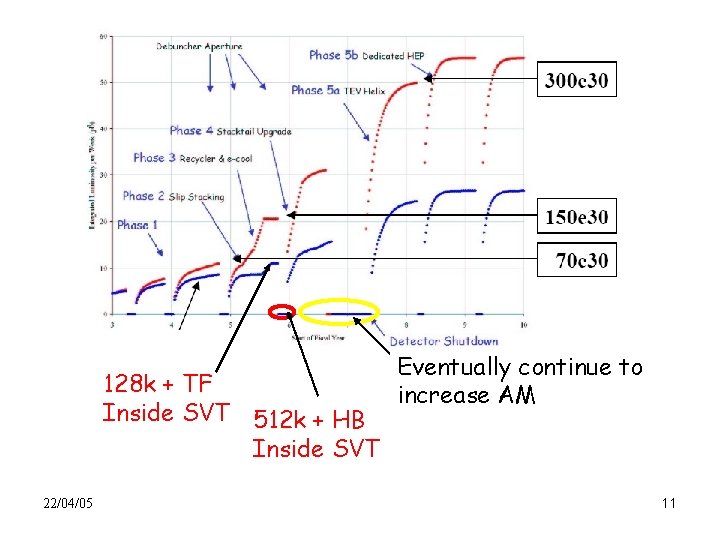

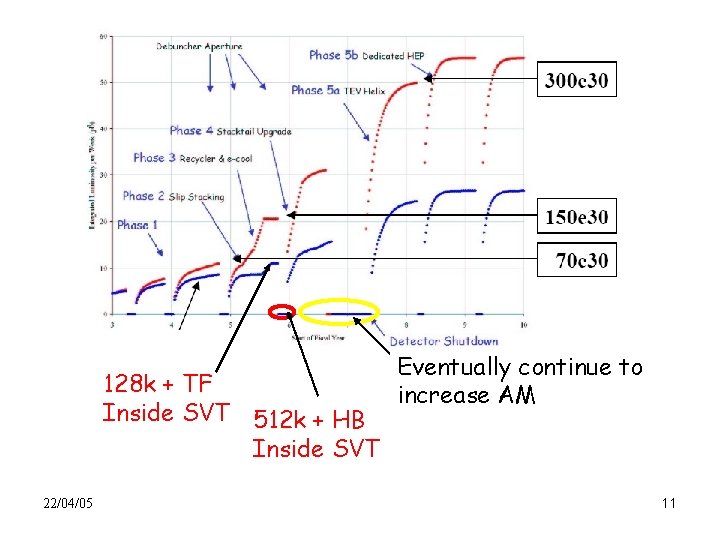

128 k + TF Inside SVT 512 k + HB Inside SVT 22/04/05 Eventually continue to increase AM 11

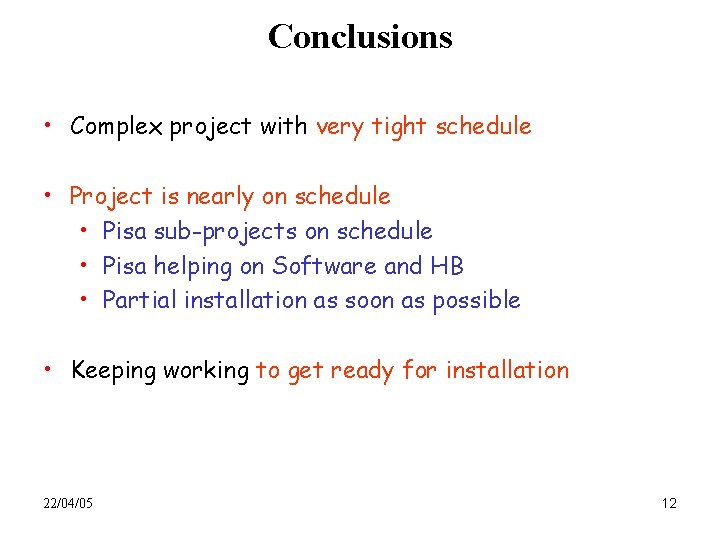

Conclusions • Complex project with very tight schedule • Project is nearly on schedule • Pisa sub-projects on schedule • Pisa helping on Software and HB • Partial installation as soon as possible • Keeping working to get ready for installation 22/04/05 12

SVT Backup slides c a b 22/04/05 p u k s e d i sl 13

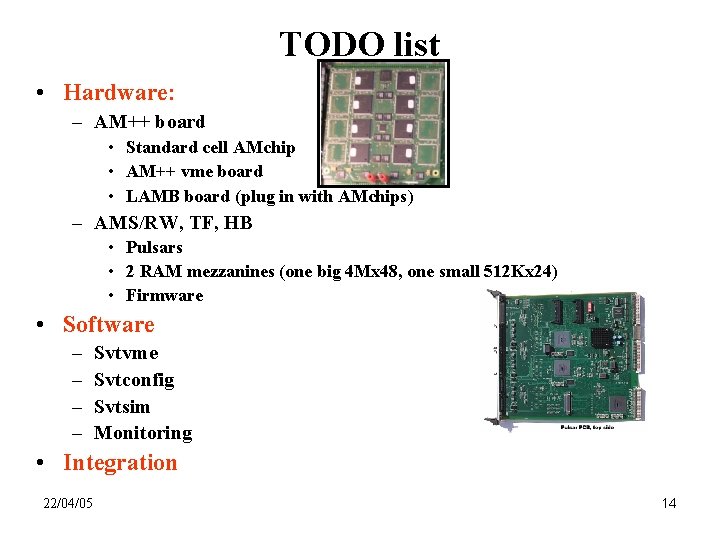

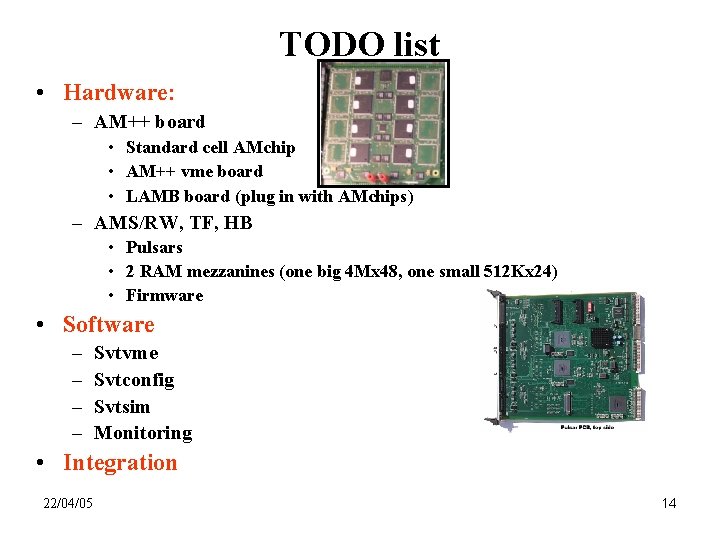

TODO list • Hardware: – AM++ board • Standard cell AMchip • AM++ vme board • LAMB board (plug in with AMchips) – AMS/RW, TF, HB • Pulsars • 2 RAM mezzanines (one big 4 Mx 48, one small 512 Kx 24) • Firmware • Software – – Svtvme Svtconfig Svtsim Monitoring • Integration 22/04/05 14

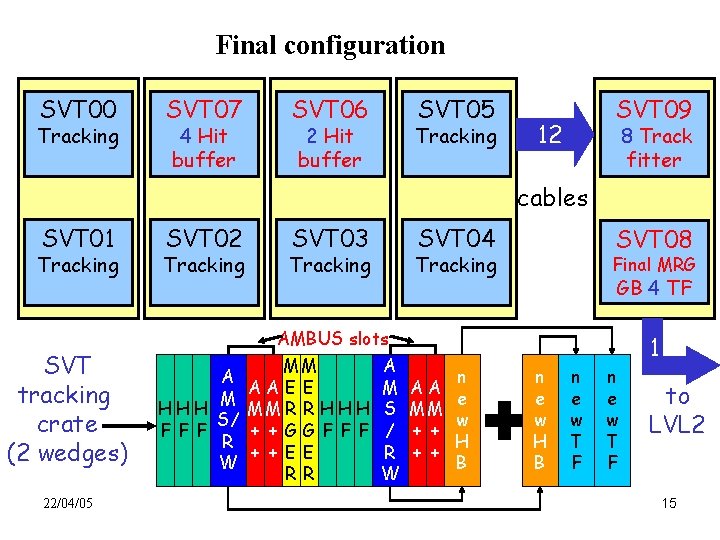

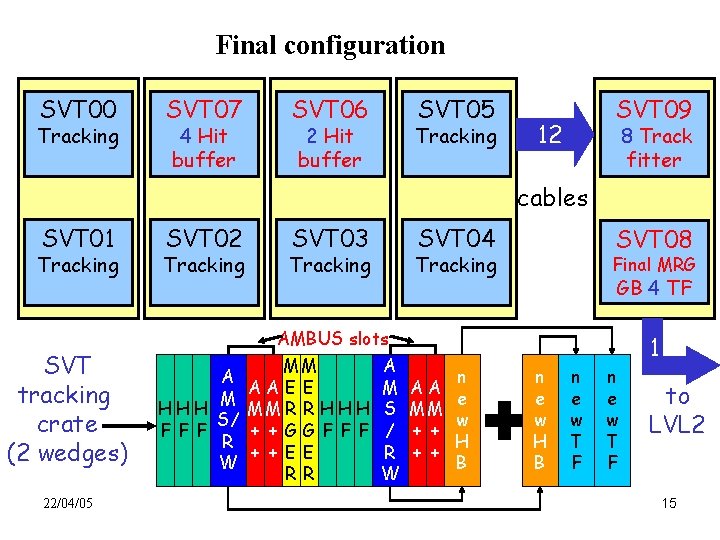

Final configuration SVT 00 Tracking SVT 07 4 Hit buffer SVT 06 SVT 05 2 Hit buffer Tracking SVT 09 12 8 Track fitter cables SVT 01 Tracking SVT tracking crate (2 wedges) 22/04/05 SVT 02 Tracking SVT 03 SVT 04 Tracking SVT 08 Tracking Final MRG GB 4 TF AMBUS slots A M HHH S/ FFF R W MM AAE E MM R R H H H + + GGFFF + + EE RR A M S / R W n AA e MM w + + H + + B n e w H B n e w T F 1 to LVL 2 15

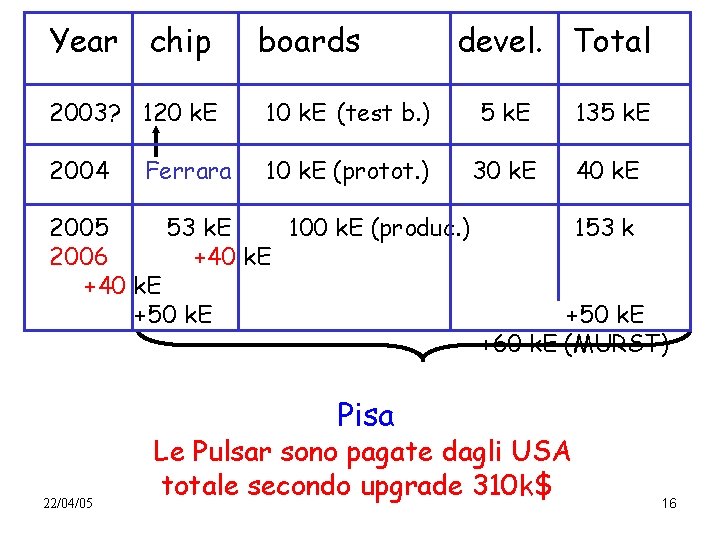

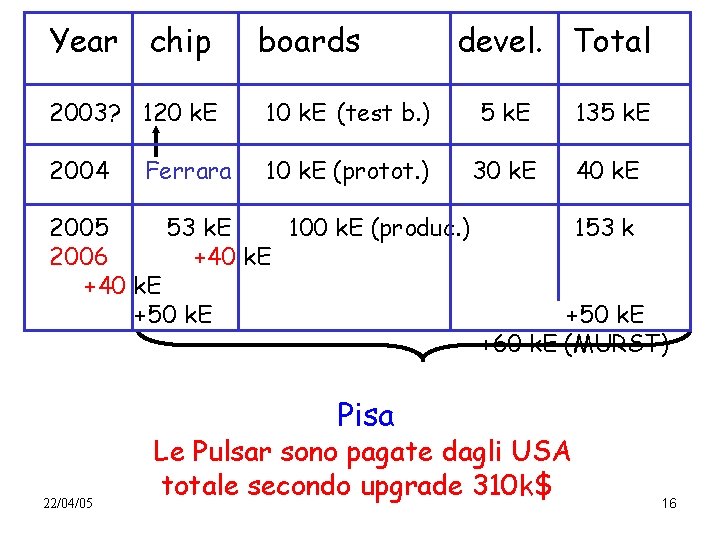

Year chip boards 2003? 120 k. E 10 k. E (test b. ) 5 k. E 135 k. E 2004 10 k. E (protot. ) 30 k. E 40 k. E Ferrara devel. Total 2005 53 k. E 100 k. E (produc. ) 2006 +40 k. E +50 k. E 153 k +50 k. E +60 k. E (MURST) Pisa 22/04/05 Le Pulsar sono pagate dagli USA totale secondo upgrade 310 k$ 16

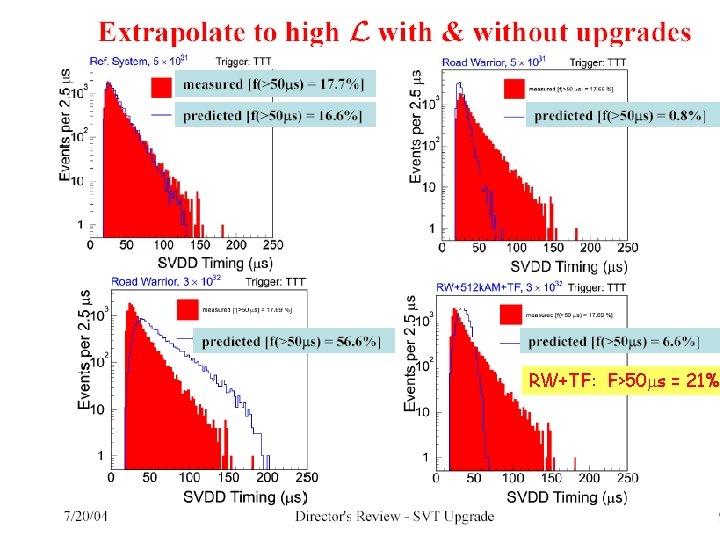

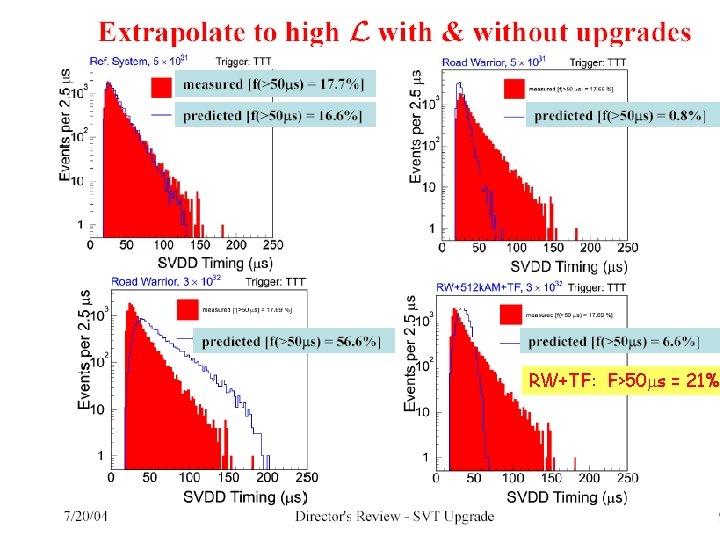

RW+TF: F>50 s = 21% 22/04/05 17

22/04/05 18

TEMPI DI REALIZZAZIONE • Nuova AM-board: inizio estate 2004 (Pisa) durante estate 2004: test con FPGA (Pisa) • Progetto prototipo AM-chip: luglio 2004 (Ferrara-Pisa) consegna chip ~2 mesi – disponibile ad ottobre. • Nuova LAMB: montare nuovo AM-chip a ottobre 2004 (Pisa) • test del chip + scheda: ottobre – dicembre 2004 (Pisa-Ferrara) • produzione: inizio 2005 (Pisa-Ferrara) • installazione: estate 2005 (Pisa-Ferrara) • Altri DAQ/Trigger upgrade: previsti nel 2006 Road Warrior: . . . (~60 k$ Fermilab) messa in opera entro fine 2003 F. Spinella (in funzione) 19 22/04/05

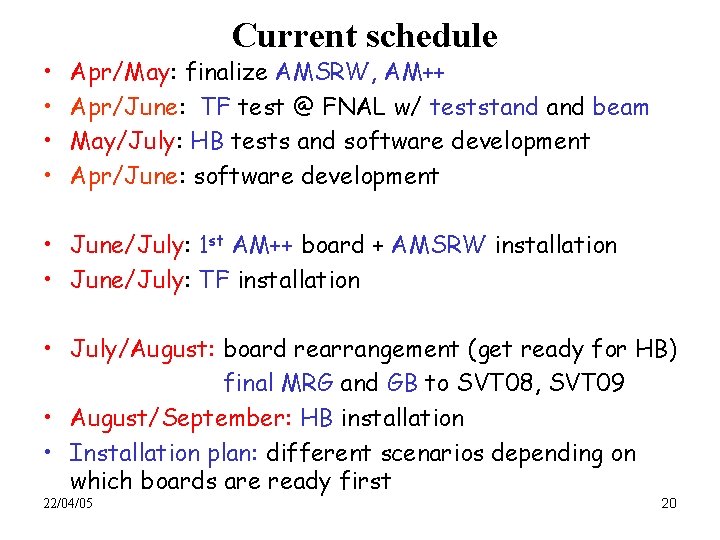

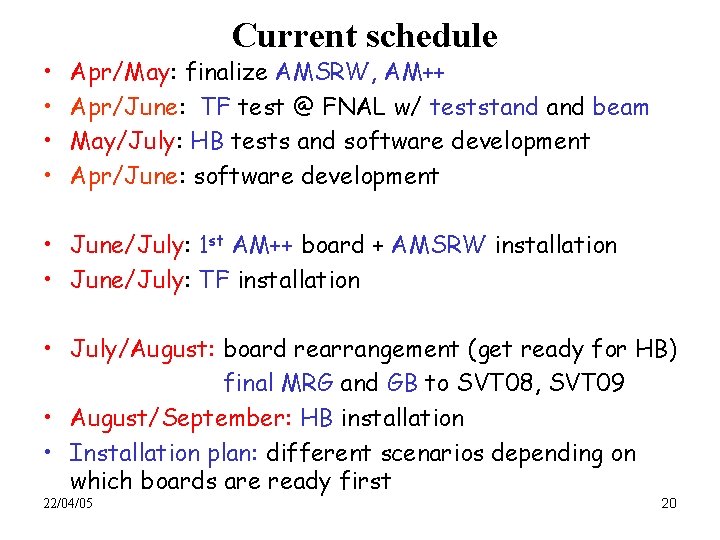

• • Current schedule Apr/May: finalize AMSRW, AM++ Apr/June: TF test @ FNAL w/ teststand beam May/July: HB tests and software development Apr/June: software development • June/July: 1 st AM++ board + AMSRW installation • June/July: TF installation • July/August: board rearrangement (get ready for HB) final MRG and GB to SVT 08, SVT 09 • August/September: HB installation • Installation plan: different scenarios depending on which boards are ready first 22/04/05 20