SVT Lupgrade del Silicon Vertex Trigger SVT di

- Slides: 42

SVT L’upgrade del Silicon Vertex Trigger (SVT) di CDF IFAE 2006 Alberto Annovi Istituto Nazionale di Fisica Nucleare Laboratori Nazionali di Frascati April 2006 Alberto Annovi- IFAE 2006 1

Outline SVT • the Silicon Vertex Trigger (SVT) • Motivations • Working principles • Performance • Upgrade April 2006 Alberto Annovi- IFAE 2006 2

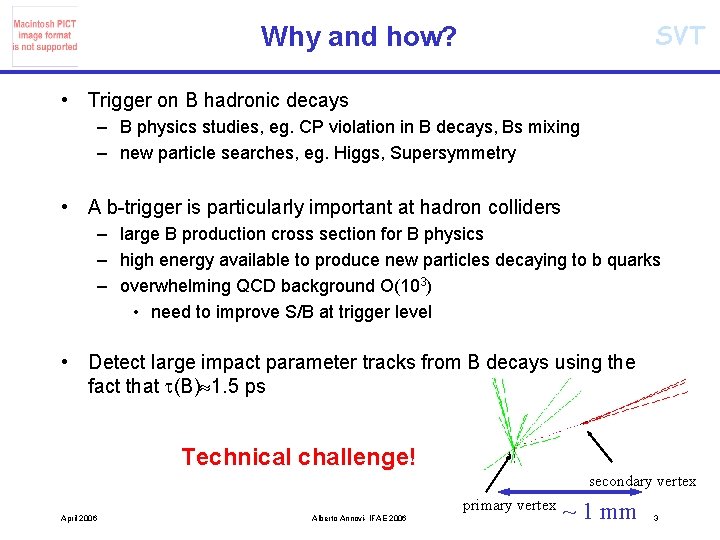

SVT Why and how? • Trigger on B hadronic decays – B physics studies, eg. CP violation in B decays, Bs mixing – new particle searches, eg. Higgs, Supersymmetry • A b-trigger is particularly important at hadron colliders – large B production cross section for B physics – high energy available to produce new particles decaying to b quarks – overwhelming QCD background O(103) • need to improve S/B at trigger level • Detect large impact parameter tracks from B decays using the fact that (B) 1. 5 ps Technical challenge! secondary vertex primary vertex April 2006 Alberto Annovi- IFAE 2006 ~ 1 mm 3

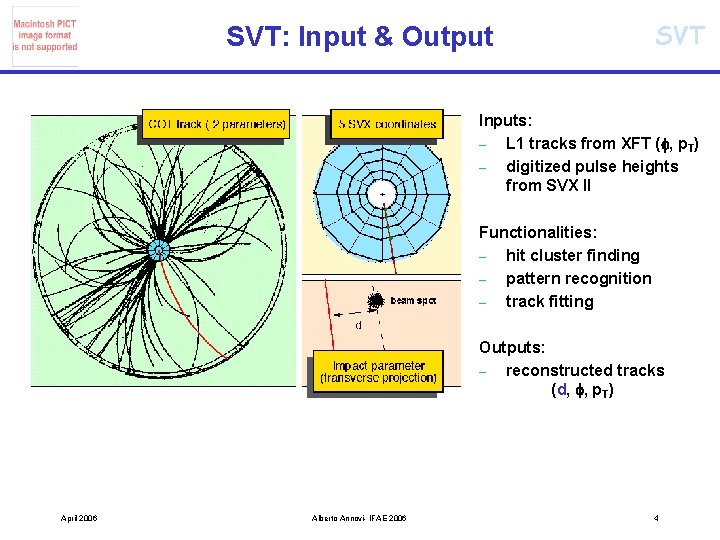

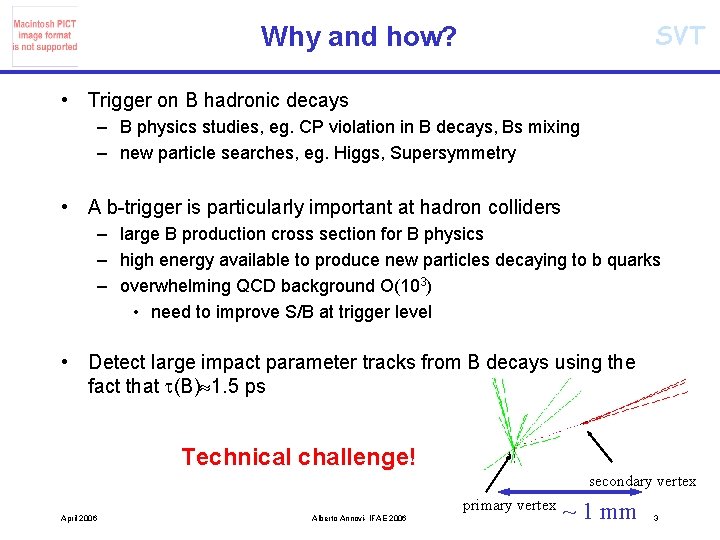

SVT: Input & Output SVT Inputs: – L 1 tracks from XFT ( , p. T) – digitized pulse heights from SVX II Functionalities: – hit cluster finding – pattern recognition – track fitting Outputs: – reconstructed tracks (d, , p. T) April 2006 Alberto Annovi- IFAE 2006 4

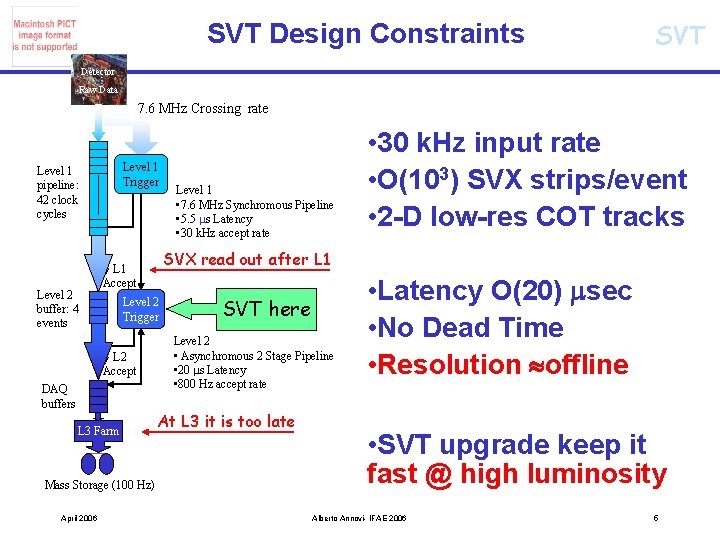

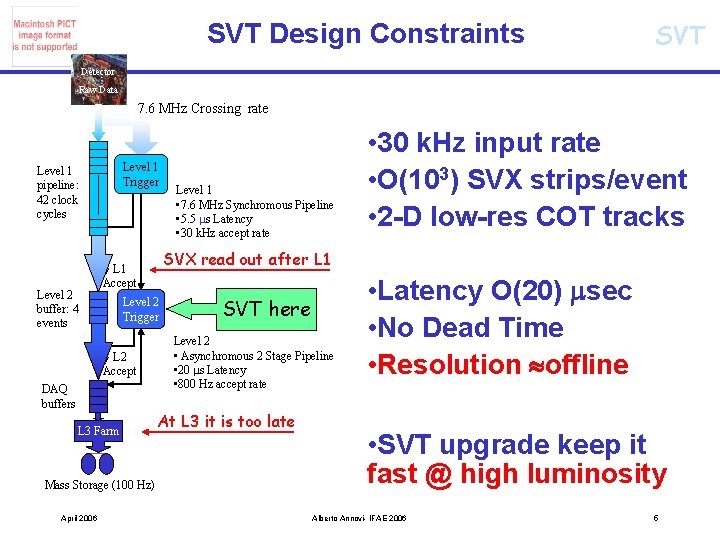

SVT Design Constraints SVT Detector Raw Data 7. 6 MHz Crossing rate Level 1 Trigger Level 1 pipeline: 42 clock cycles Level 2 buffer: 4 events Level 2 Trigger DAQ buffers L 3 Farm Mass Storage (100 Hz) April 2006 SVX read out after L 1 Accept L 2 Accept Level 1 • 7. 6 MHz Synchromous Pipeline • 5. 5 s Latency • 30 k. Hz accept rate • 30 k. Hz input rate • O(103) SVX strips/event • 2 -D low-res COT tracks SVT here Level 2 • Asynchromous 2 Stage Pipeline • 20 s Latency • 800 Hz accept rate At L 3 it is too late • Latency O(20) sec • No Dead Time • Resolution offline • SVT upgrade keep it fast @ high luminosity Alberto Annovi- IFAE 2006 5

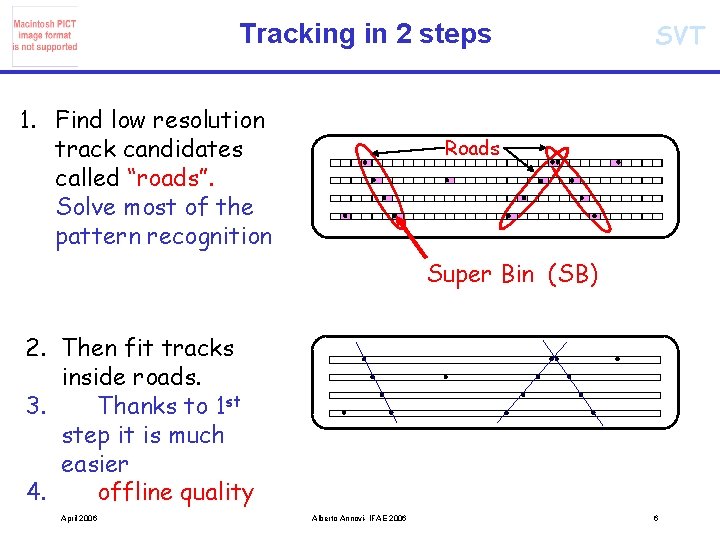

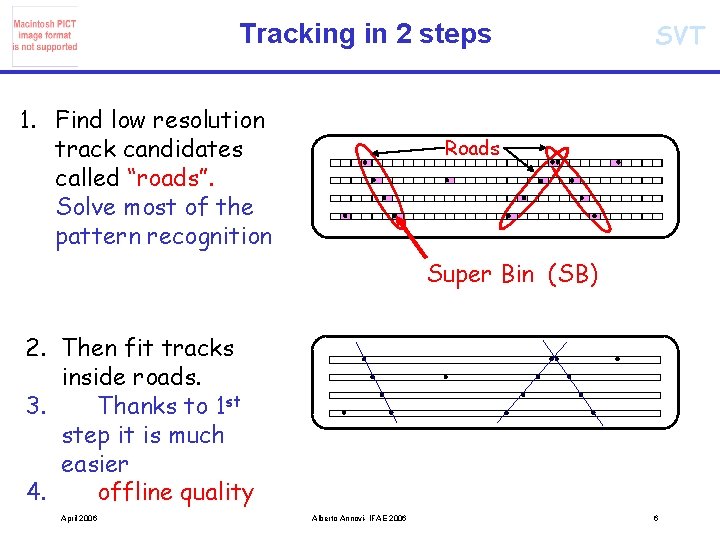

Tracking in 2 steps 1. Find low resolution track candidates called “roads”. Solve most of the pattern recognition SVT Roads Super Bin (SB) 2. Then fit tracks inside roads. 3. Thanks to 1 st step it is much easier 4. offline quality April 2006 Alberto Annovi- IFAE 2006 6

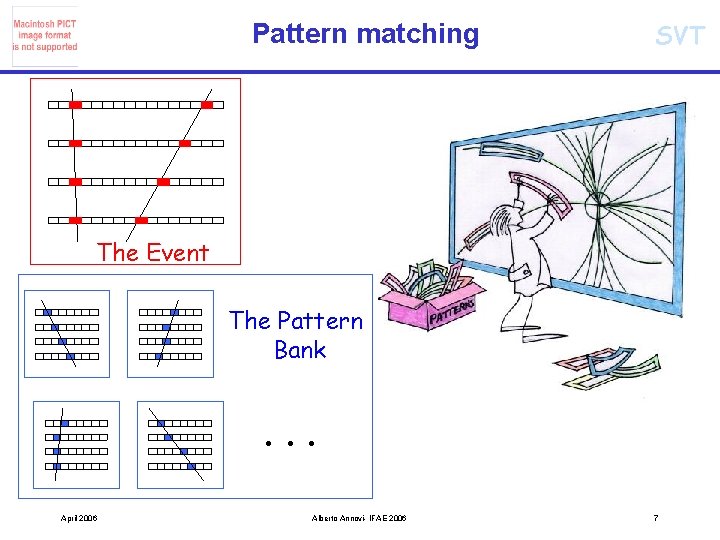

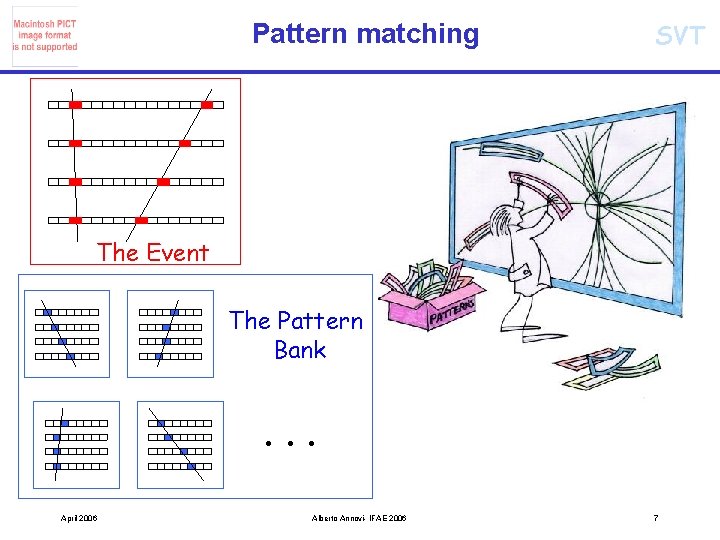

Pattern matching SVT The Event The Pattern Bank . . . April 2006 Alberto Annovi- IFAE 2006 7

AM: Associative Memory SVT Bingo scorecard • Dedicated device: maximum parallelism • Each pattern with private comparator • Track search during detector readout April 2006 Alberto Annovi- IFAE 2006 8

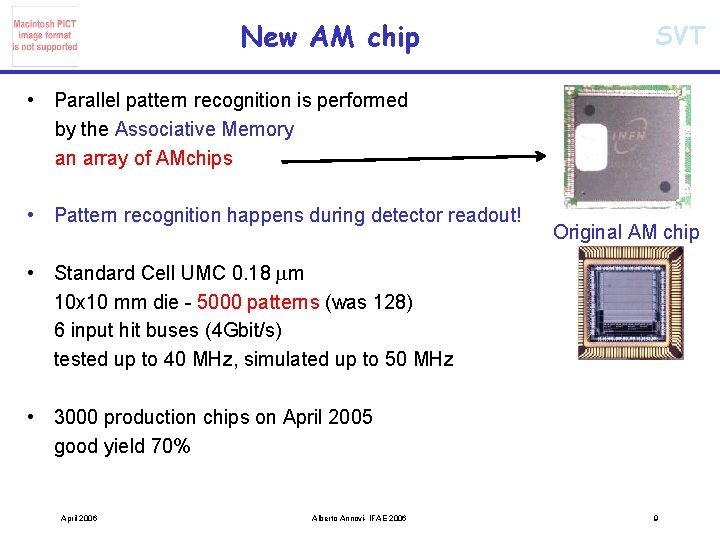

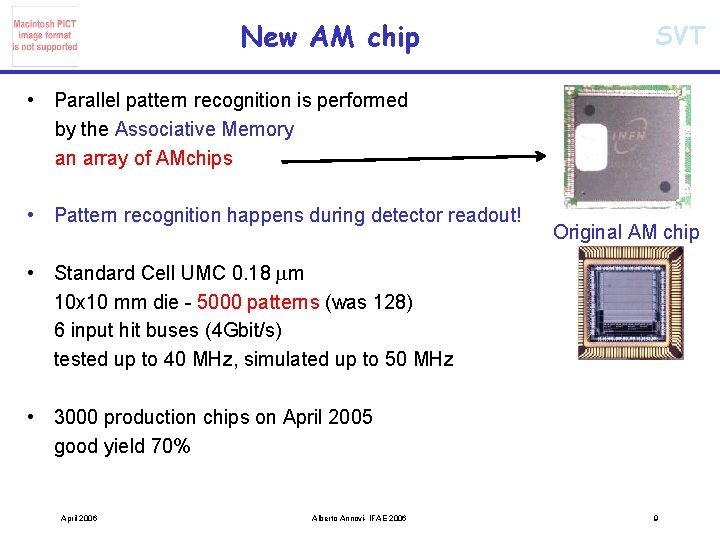

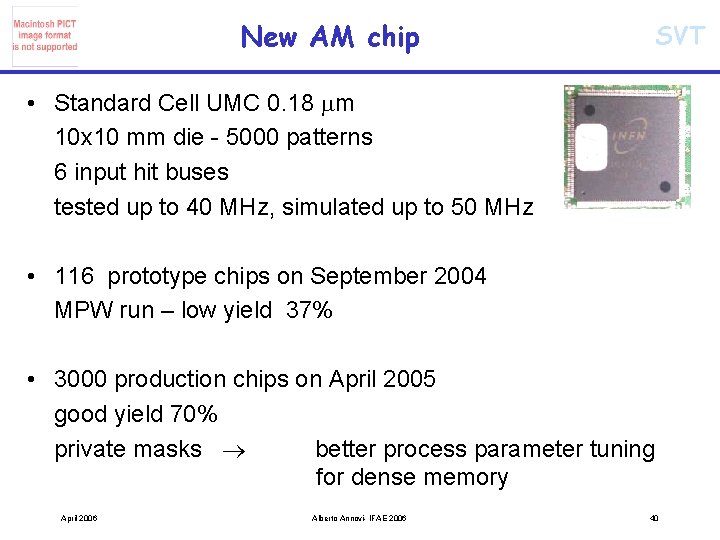

New AM chip SVT • Parallel pattern recognition is performed by the Associative Memory an array of AMchips • Pattern recognition happens during detector readout! Original AM chip • Standard Cell UMC 0. 18 m 10 x 10 mm die - 5000 patterns (was 128) 6 input hit buses (4 Gbit/s) tested up to 40 MHz, simulated up to 50 MHz • 3000 production chips on April 2005 good yield 70% April 2006 Alberto Annovi- IFAE 2006 9

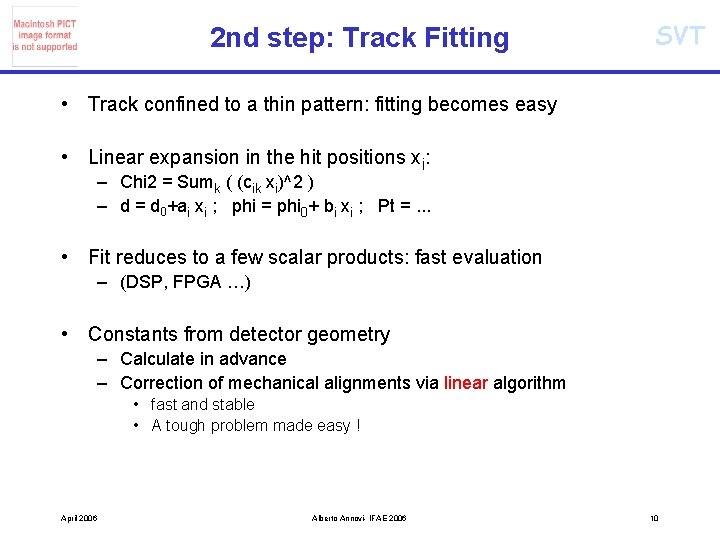

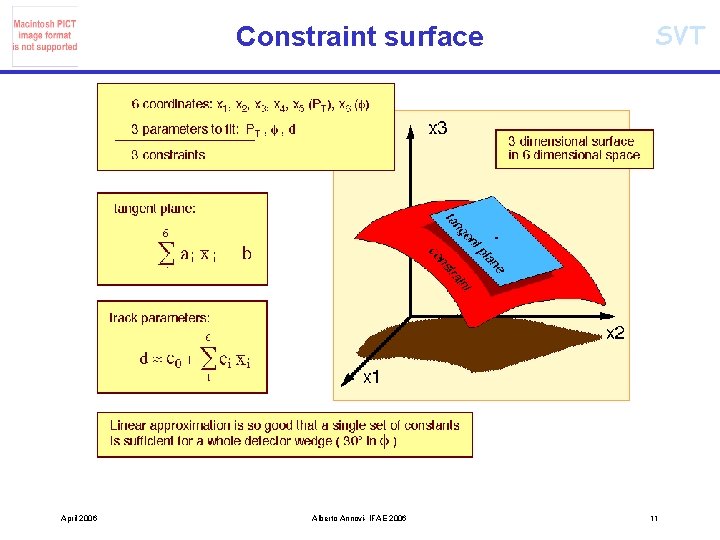

2 nd step: Track Fitting SVT • Track confined to a thin pattern: fitting becomes easy • Linear expansion in the hit positions xi: – Chi 2 = Sumk ( (cik xi)^2 ) – d = d 0+ai xi ; phi = phi 0+ bi xi ; Pt =. . . • Fit reduces to a few scalar products: fast evaluation – (DSP, FPGA …) • Constants from detector geometry – Calculate in advance – Correction of mechanical alignments via linear algorithm • fast and stable • A tough problem made easy ! April 2006 Alberto Annovi- IFAE 2006 10

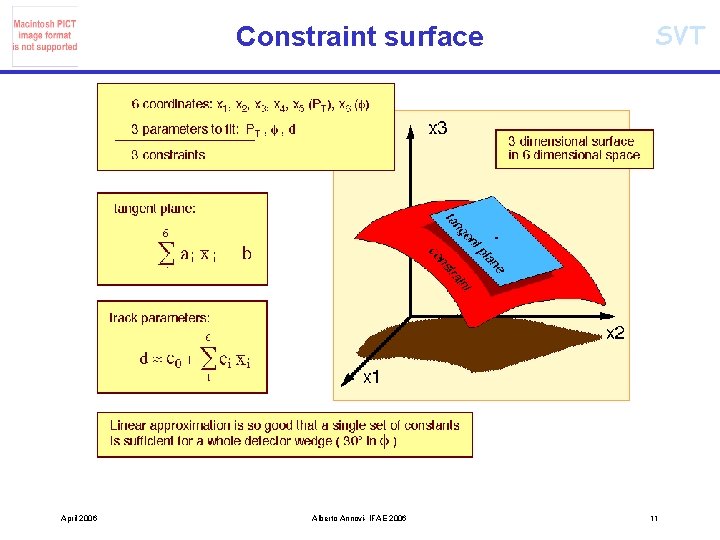

Constraint surface April 2006 Alberto Annovi- IFAE 2006 SVT 11

SVT crates in CDF counting room April 2006 Alberto Annovi- IFAE 2006 SVT 12

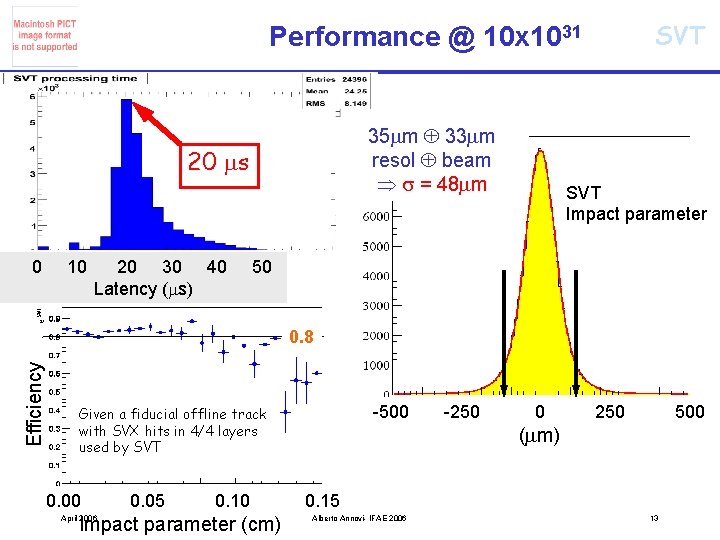

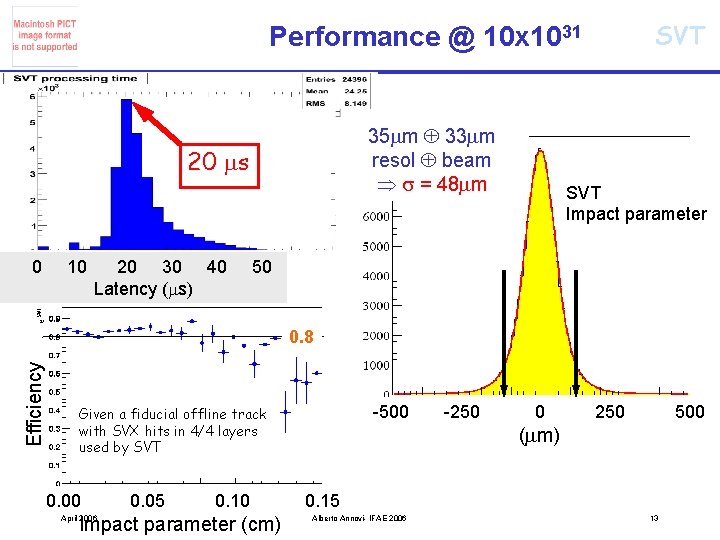

SVT Performance @ 10 x 1031 35 m 33 m resol beam s = 48 m 20 s 0 10 20 30 40 Latency ( s) SVT Impact parameter 50 Efficiency 0. 8 -500 Given a fiducial offline track with SVX hits in 4/4 layers used by SVT 0. 00 0. 05 0. 10 Impact parameter (cm) April 2006 -250 0 250 500 ( m) 0. 15 Alberto Annovi- IFAE 2006 13

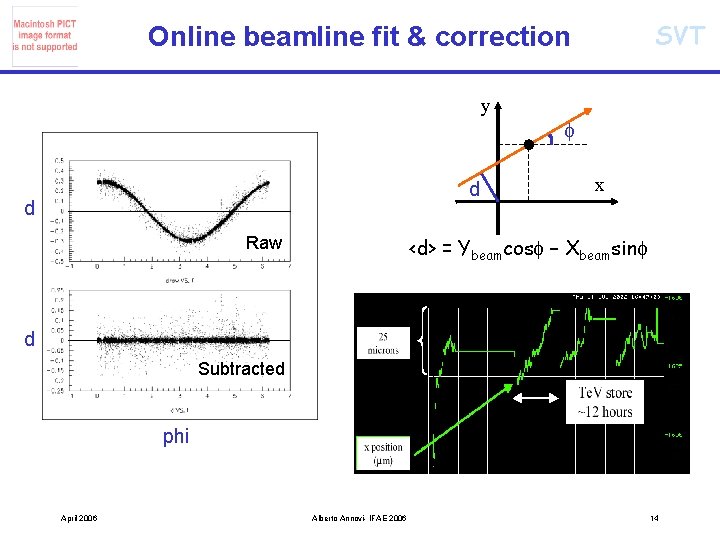

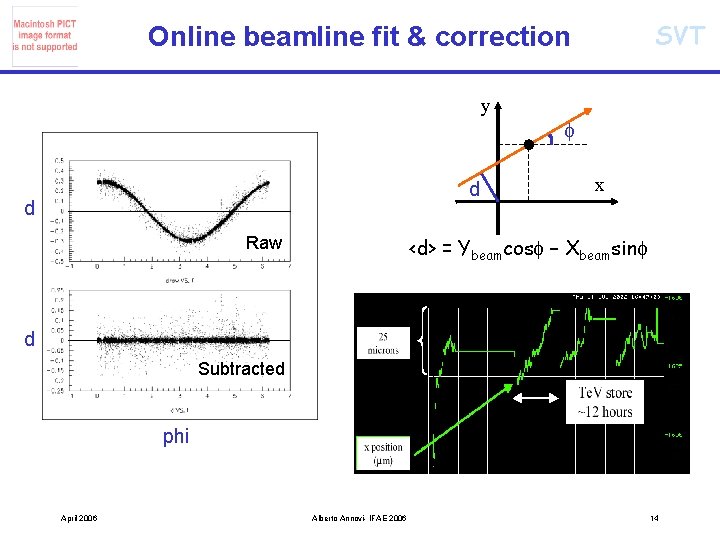

SVT Online beamline fit & correction y d d Raw x <d> = Ybeamcos – Xbeamsin d Subtracted phi April 2006 Alberto Annovi- IFAE 2006 14

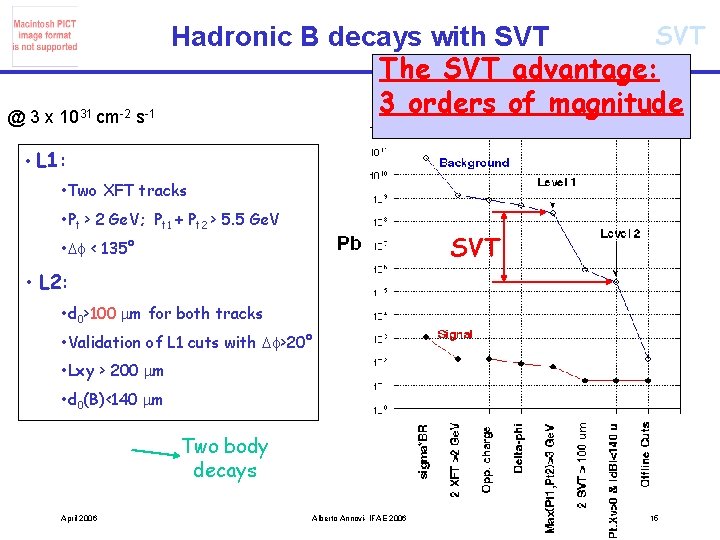

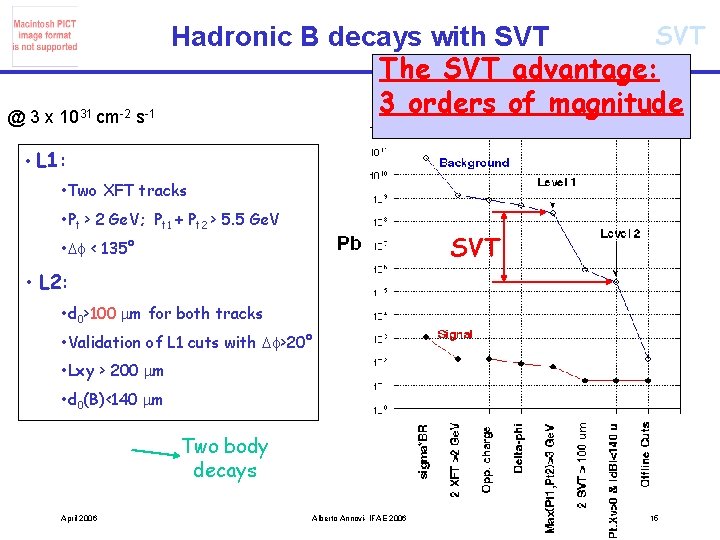

@ 3 x 1031 cm-2 s-1 SVT Hadronic B decays with SVT The SVT advantage: 3 orders of magnitude • L 1: • Two XFT tracks • Pt > 2 Ge. V; Pt 1 + Pt 2 > 5. 5 Ge. V SVT • < 135° • L 2: • d 0>100 m for both tracks • Validation of L 1 cuts with >20° • Lxy > 200 m • d 0(B)<140 m Two body decays April 2006 Alberto Annovi- IFAE 2006 15

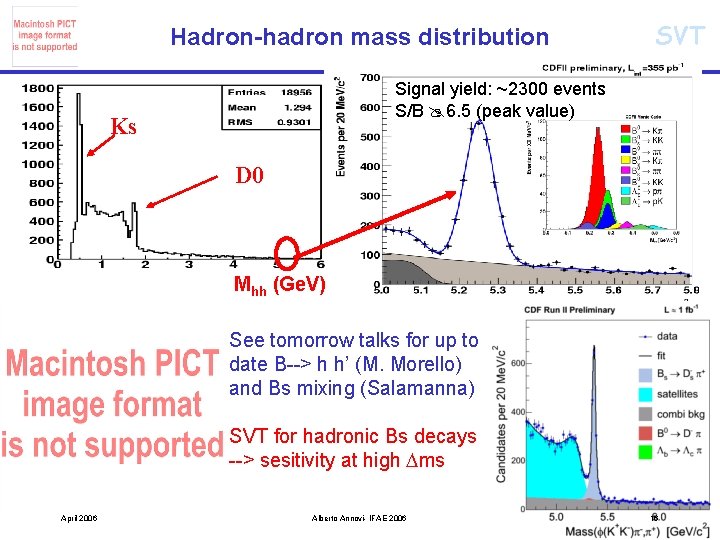

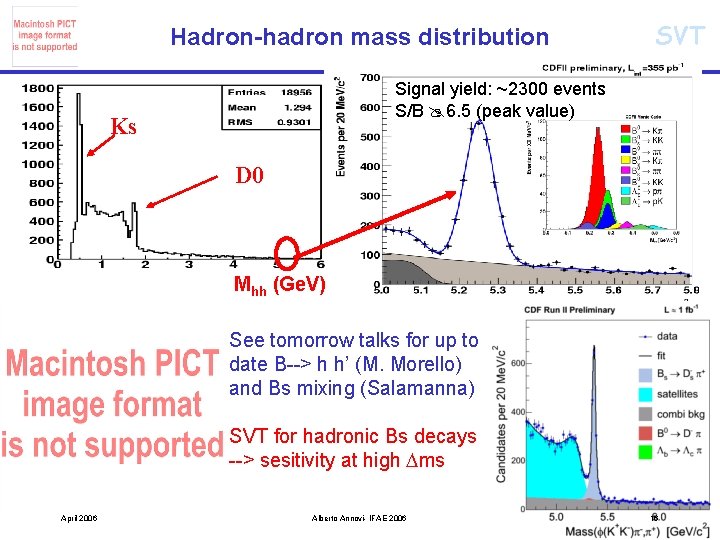

Hadron-hadron mass distribution SVT Signal yield: ~2300 events S/B 6. 5 (peak value) Ks D 0 Mhh (Ge. V) See tomorrow talks for up to date B--> h h’ (M. Morello) and Bs mixing (Salamanna) SVT for hadronic Bs decays --> sesitivity at high ms April 2006 Alberto Annovi- IFAE 2006 16

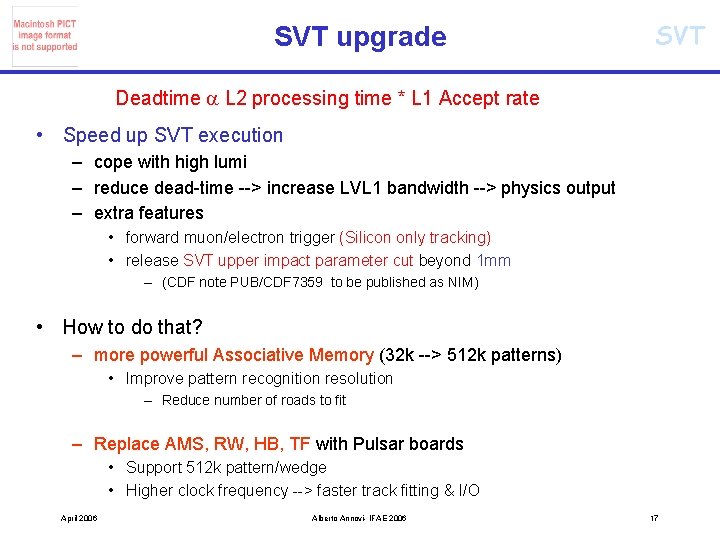

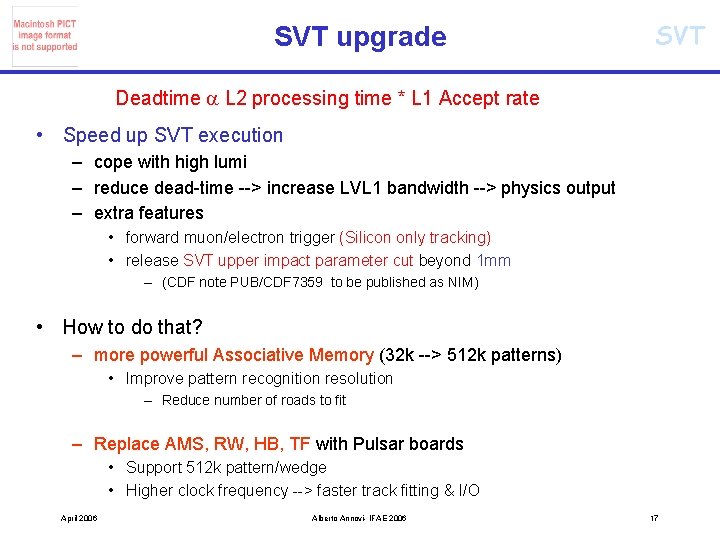

SVT upgrade SVT Deadtime a L 2 processing time * L 1 Accept rate • Speed up SVT execution – cope with high lumi – reduce dead-time --> increase LVL 1 bandwidth --> physics output – extra features • forward muon/electron trigger (Silicon only tracking) • release SVT upper impact parameter cut beyond 1 mm – (CDF note PUB/CDF 7359 to be published as NIM) • How to do that? – more powerful Associative Memory (32 k --> 512 k patterns) • Improve pattern recognition resolution – Reduce number of roads to fit – Replace AMS, RW, HB, TF with Pulsar boards • Support 512 k pattern/wedge • Higher clock frequency --> faster track fitting & I/O April 2006 Alberto Annovi- IFAE 2006 17

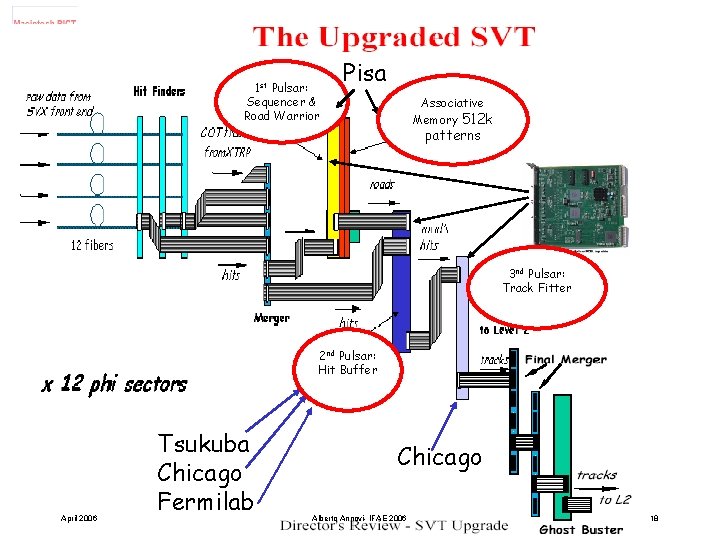

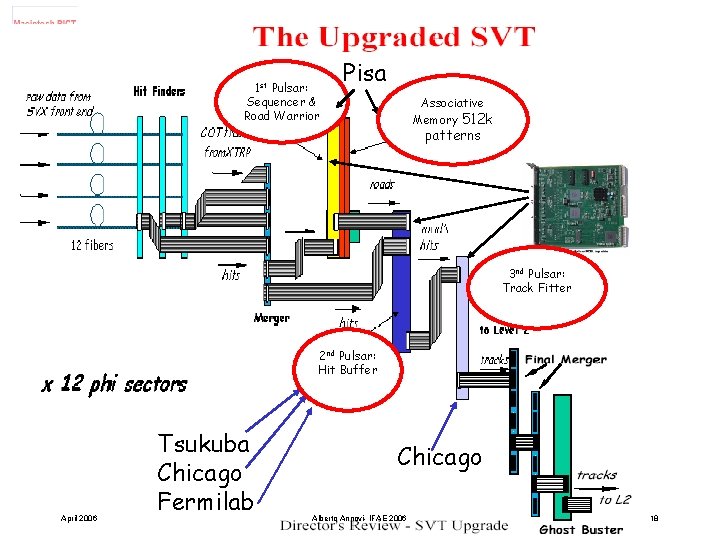

SVT 1 st Pulsar: Sequencer & Road Warrior Pisa Associative Memory 512 k patterns 3 nd Pulsar: Track Fitter 2 nd Pulsar: Hit Buffer April 2006 Tsukuba Chicago Fermilab Chicago Alberto Annovi- IFAE 2006 18

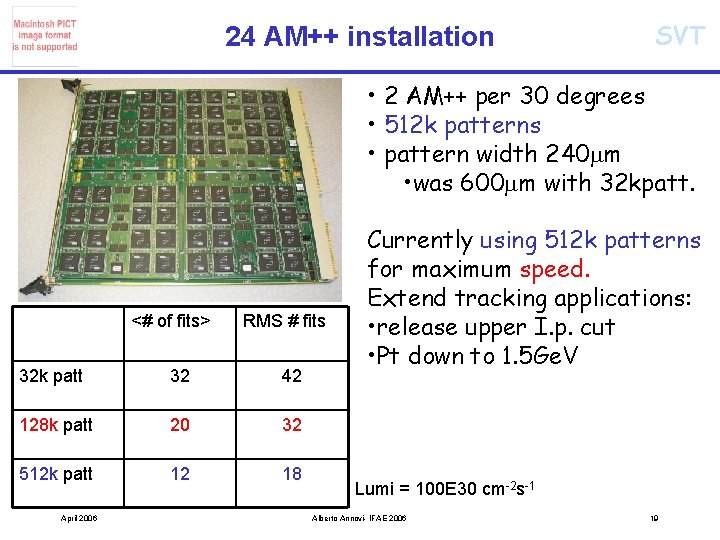

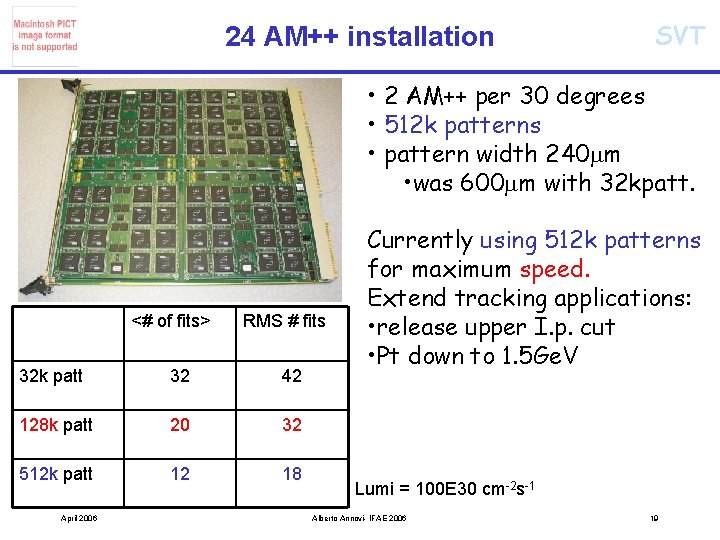

24 AM++ installation SVT • 2 AM++ per 30 degrees • 512 k patterns • pattern width 240 m • was 600 m with 32 kpatt. <# of fits> RMS # fits 32 k patt 32 42 128 k patt 20 32 512 k patt 12 18 April 2006 Currently using 512 k patterns for maximum speed. Extend tracking applications: • release upper I. p. cut • Pt down to 1. 5 Ge. V Lumi = 100 E 30 cm-2 s-1 Alberto Annovi- IFAE 2006 19

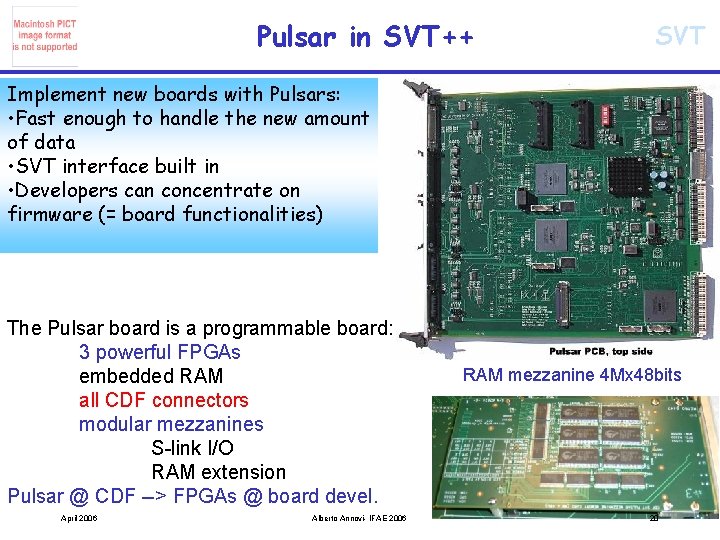

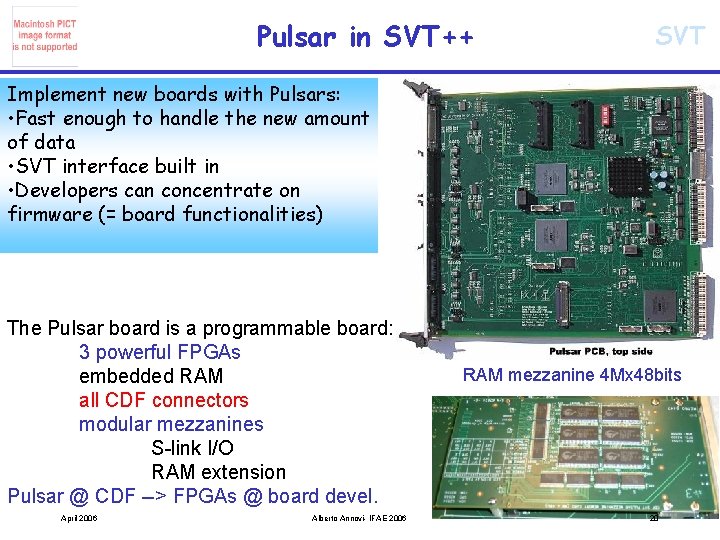

Pulsar in SVT++ SVT Implement new boards with Pulsars: • Fast enough to handle the new amount of data • SVT interface built in • Developers can concentrate on firmware (= board functionalities) The Pulsar board is a programmable board: 3 powerful FPGAs embedded RAM all CDF connectors modular mezzanines S-link I/O RAM extension Pulsar @ CDF --> FPGAs @ board devel. April 2006 Alberto Annovi- IFAE 2006 RAM mezzanine 4 Mx 48 bits 20

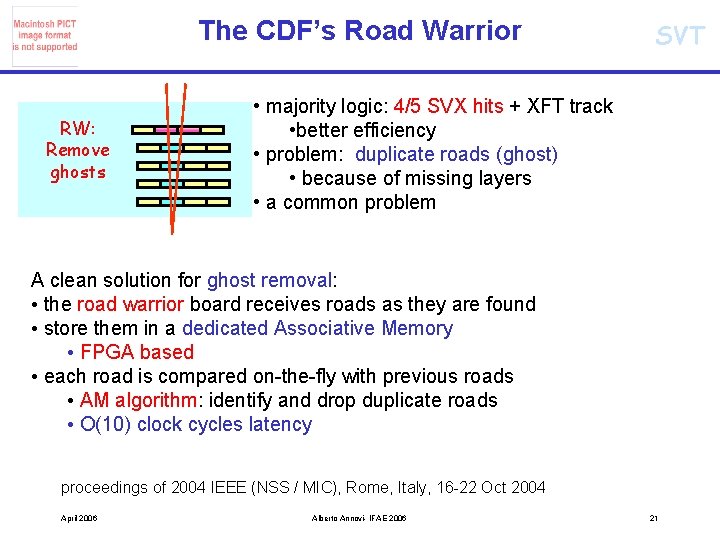

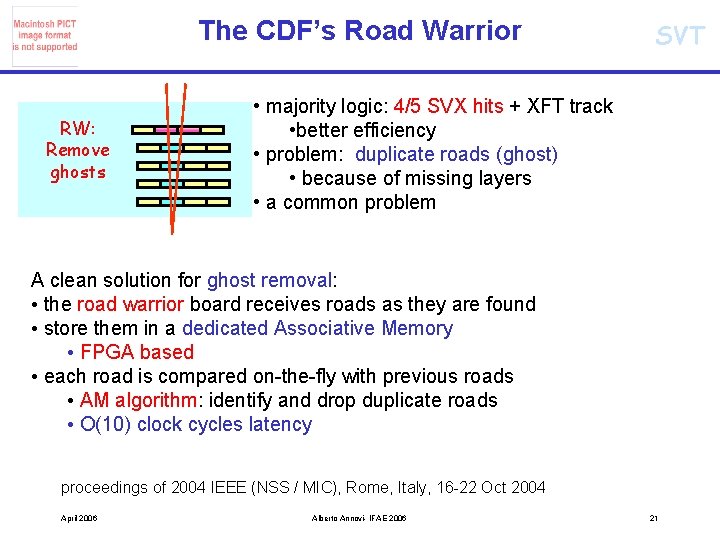

The CDF’s Road Warrior RW: Remove ghosts SVT • majority logic: 4/5 SVX hits + XFT track • better efficiency • problem: duplicate roads (ghost) • because of missing layers • a common problem A clean solution for ghost removal: • the road warrior board receives roads as they are found • store them in a dedicated Associative Memory • FPGA based • each road is compared on-the-fly with previous roads • AM algorithm: identify and drop duplicate roads • O(10) clock cycles latency proceedings of 2004 IEEE (NSS / MIC), Rome, Italy, 16 -22 Oct 2004 April 2006 Alberto Annovi- IFAE 2006 21

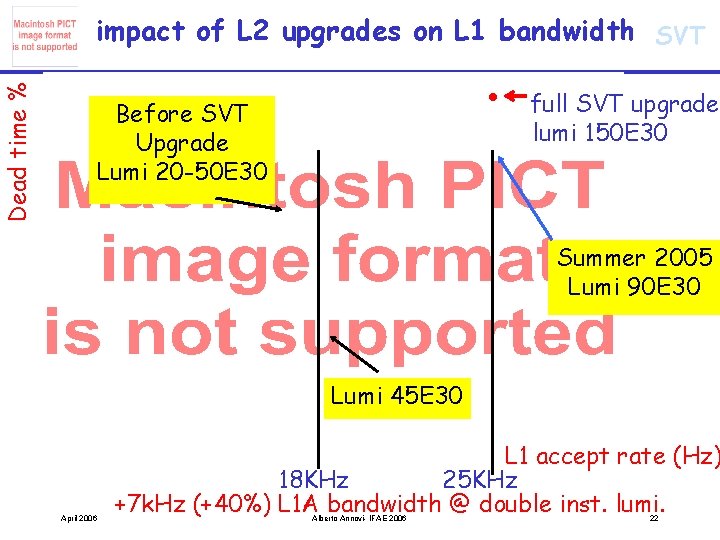

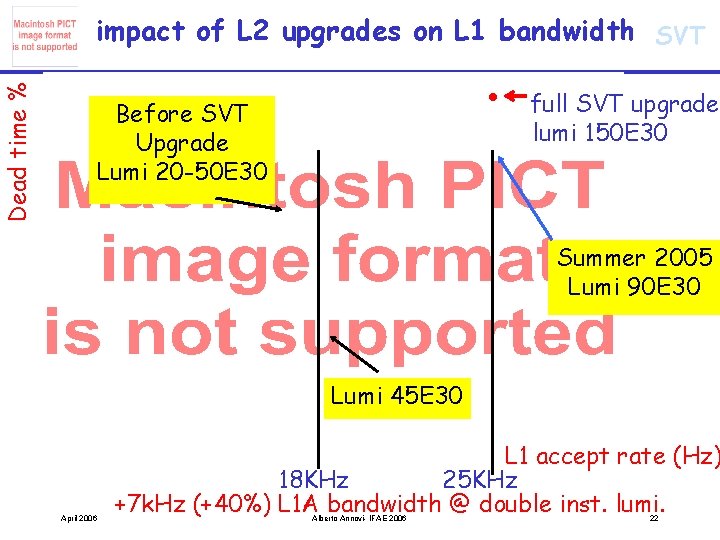

Dead time % impact of L 2 upgrades on L 1 bandwidth SVT • Before SVT Upgrade Lumi 20 -50 E 30 full SVT upgrade lumi 150 E 30 Summer 2005 Lumi 90 E 30 Lumi 45 E 30 April 2006 L 1 accept rate (Hz) 18 KHz 25 KHz +7 k. Hz (+40%) L 1 A bandwidth @ double inst. lumi. Alberto Annovi- IFAE 2006 22

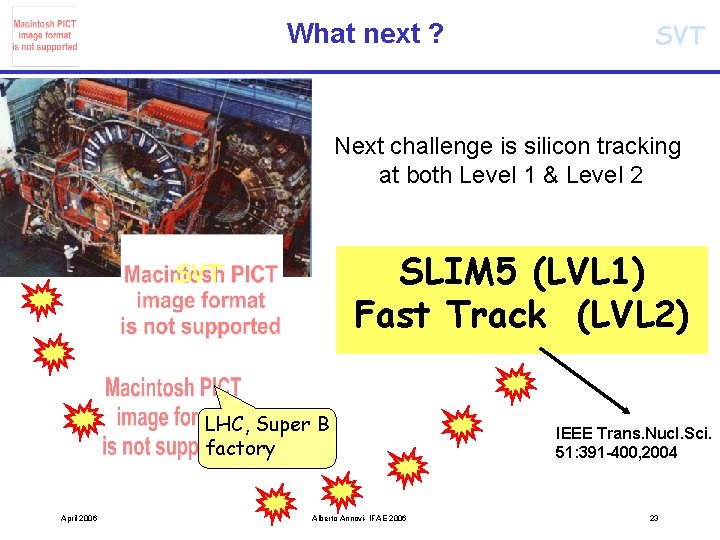

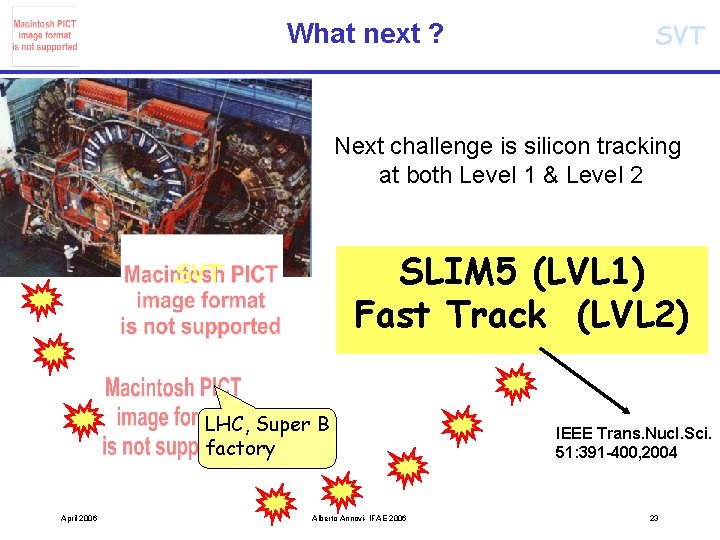

What next ? SVT Next challenge is silicon tracking at both Level 1 & Level 2 SLIM 5 (LVL 1) Fast Track (LVL 2) SVT LHC, Super B factory April 2006 Alberto Annovi- IFAE 2006 IEEE Trans. Nucl. Sci. 51: 391 -400, 2004 23

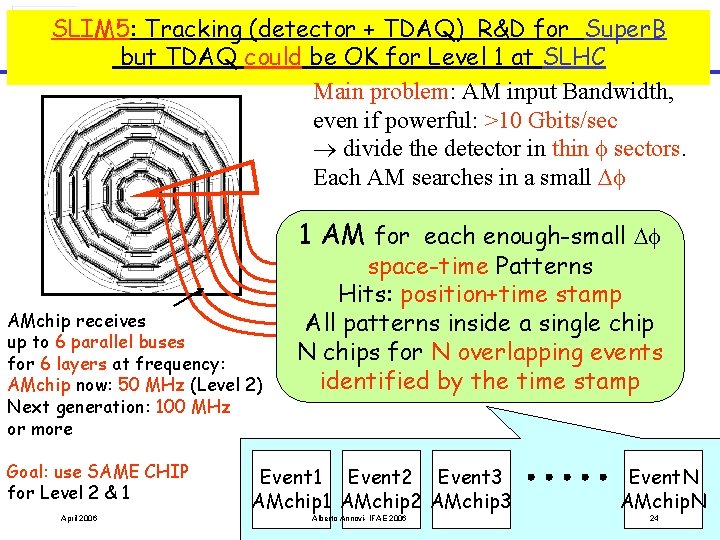

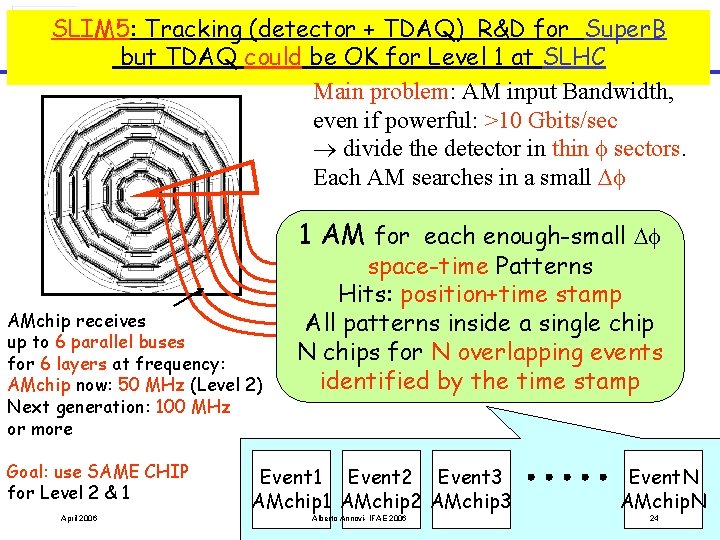

SLIM 5: Tracking (detector + TDAQ) R&D for Super. BSVT but TDAQ could be OK for Level 1 at SLHC Main problem: AM input Bandwidth, even if powerful: >10 Gbits/sec divide the detector in thin sectors. Each AM searches in a small 1 AM for each enough-small AMchip receives up to 6 parallel buses for 6 layers at frequency: AMchip now: 50 MHz (Level 2) Next generation: 100 MHz or more Goal: use SAME CHIP for Level 2 & 1 April 2006 space-time Patterns Hits: position+time stamp All patterns inside a single chip N chips for N overlapping events identified by the time stamp Event 1 Event 2 Event 3 AMchip 1 AMchip 2 AMchip 3 Alberto Annovi- IFAE 2006 Event. N AMchip. N 24

SUMMARY April 2006 • The design and construction of SVT was a significant step forward in the technology of fast track finding • We use a massively parallel/pipelined architecture combined with some innovative techniques such as the associative memory, linearized track fitting and road warrior • CDF is triggering on impact parameter and collecting data leading to significant physics results • B-physics, and not only, at hadron colliders substantially benefits of on-line tracking with off-line quality • The system is modular and easy to upgrade • The SVT technology is ready for other applications! Alberto Annovi- IFAE 2006 SVT 25

SVT BACKUP SLIDES April 2006 Alberto Annovi- IFAE 2006 26

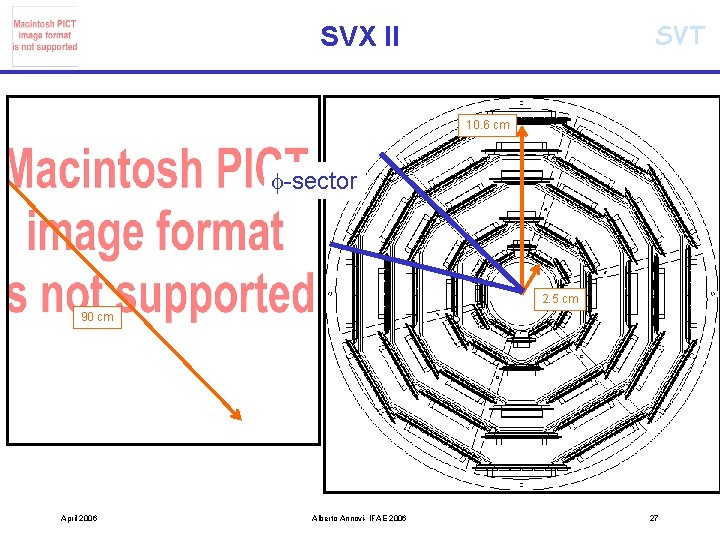

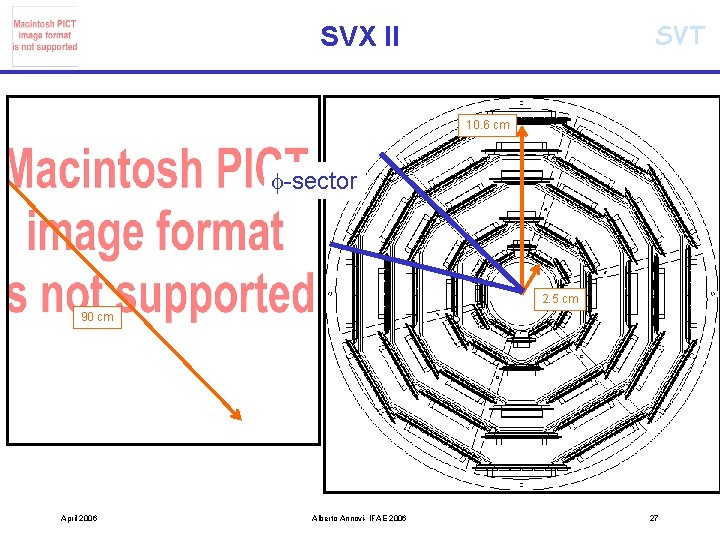

SVT SVX II 10. 6 cm -sector 2. 5 cm 90 cm April 2006 Alberto Annovi- IFAE 2006 27

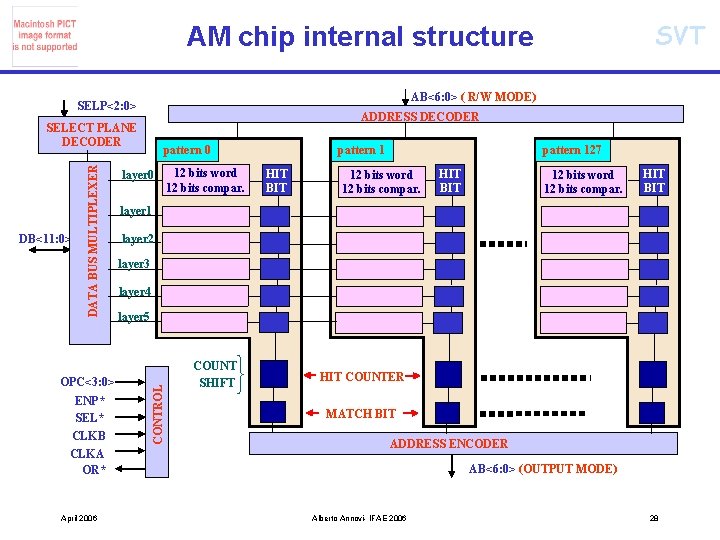

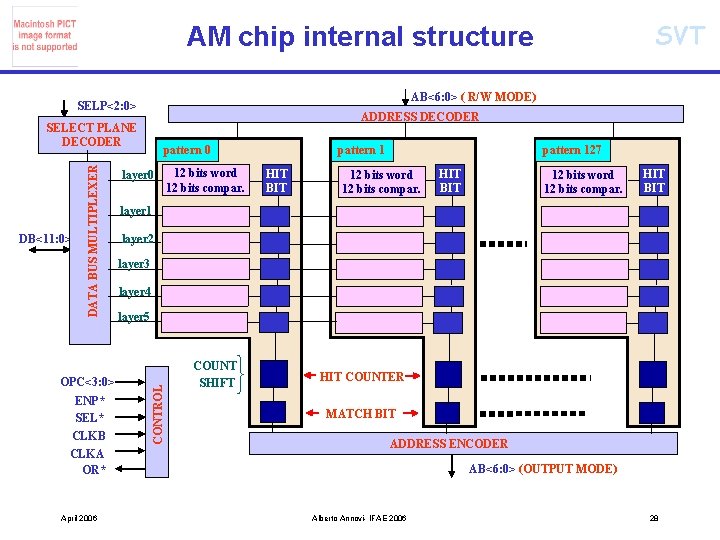

SVT AM chip internal structure AB<6: 0> ( R/W MODE) SELP<2: 0> ADDRESS DECODER OPC<3: 0> ENP* SEL* CLKB CLKA OR* April 2006 pattern 0 layer 0 12 bits word 12 bits compar. pattern 1 HIT BIT pattern 127 12 bits word 12 bits compar. HIT BIT layer 1 layer 2 layer 3 layer 4 layer 5 CONTROL DB<11: 0> DATA BUS MULTIPLEXER SELECT PLANE DECODER COUNT SHIFT HIT COUNTER MATCH BIT ADDRESS ENCODER AB<6: 0> (OUTPUT MODE) Alberto Annovi- IFAE 2006 28

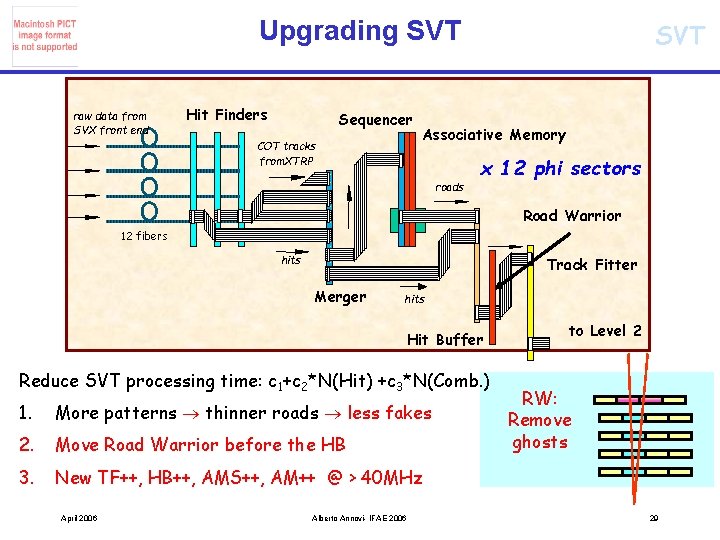

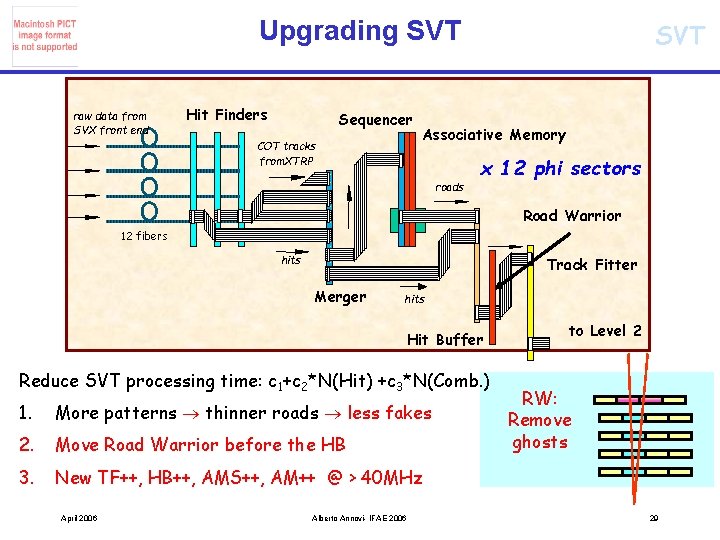

Upgrading SVT raw data from SVX front end Hit Finders Sequencer COT tracks from. XTRP SVT Associative Memory roads x 12 phi sectors Road Warrior 12 fibers hits Track Fitter Merger hits Hit Buffer Reduce SVT processing time: c 1+c 2*N(Hit) +c 3*N(Comb. ) 1. More patterns thinner roads less fakes 2. Move Road Warrior before the HB 3. New TF++, HB++, AMS++, AM++ @ > 40 MHz April 2006 Alberto Annovi- IFAE 2006 to Level 2 RW: Remove ghosts 29

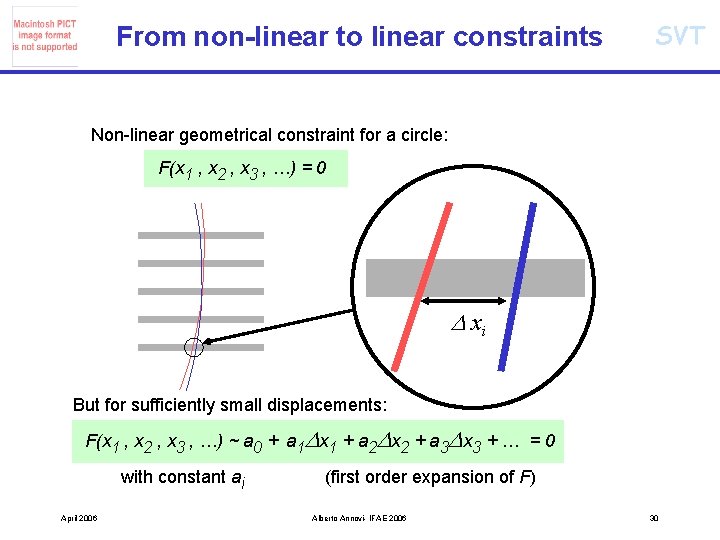

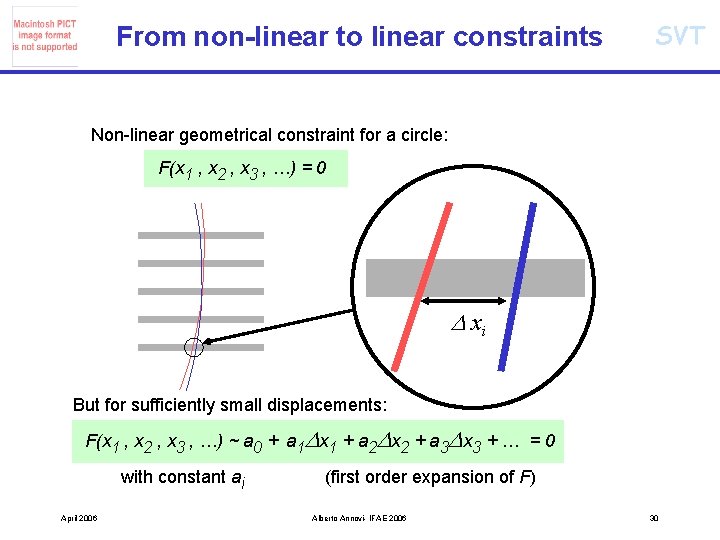

From non-linear to linear constraints SVT Non-linear geometrical constraint for a circle: F(x 1 , x 2 , x 3 , …) = 0 D xi But for sufficiently small displacements: F(x 1 , x 2 , x 3 , …) ~ a 0 + a 1 Dx 1 + a 2 Dx 2 + a 3 Dx 3 + … = 0 with constant ai April 2006 (first order expansion of F) Alberto Annovi- IFAE 2006 30

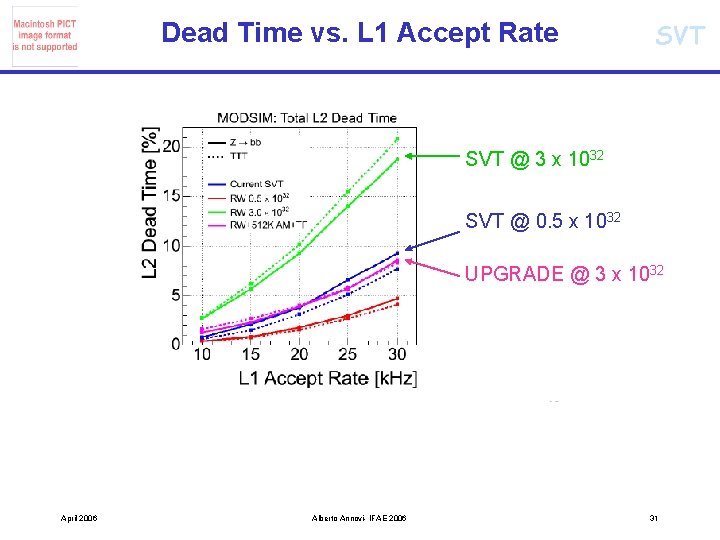

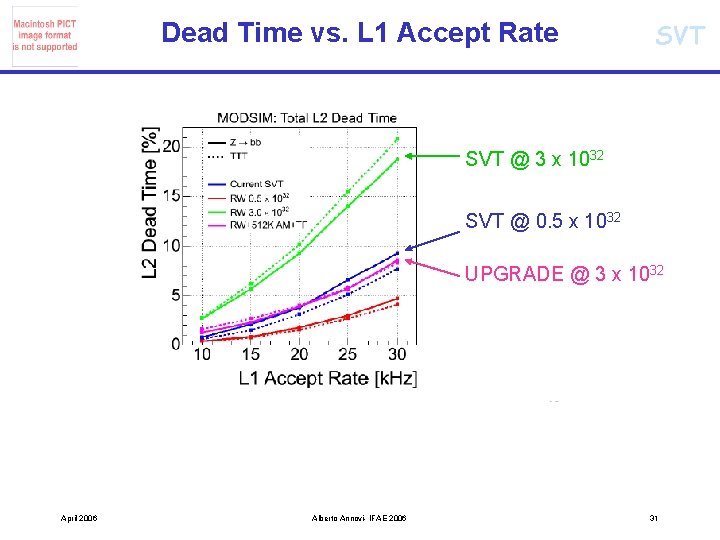

Dead Time vs. L 1 Accept Rate SVT @ 3 x 1032 SVT @ 0. 5 x 1032 UPGRADE @ 3 x 1032 April 2006 Alberto Annovi- IFAE 2006 31

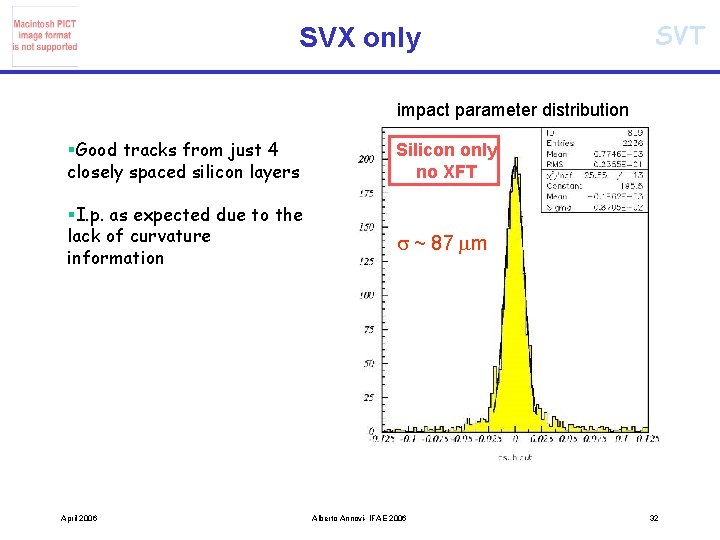

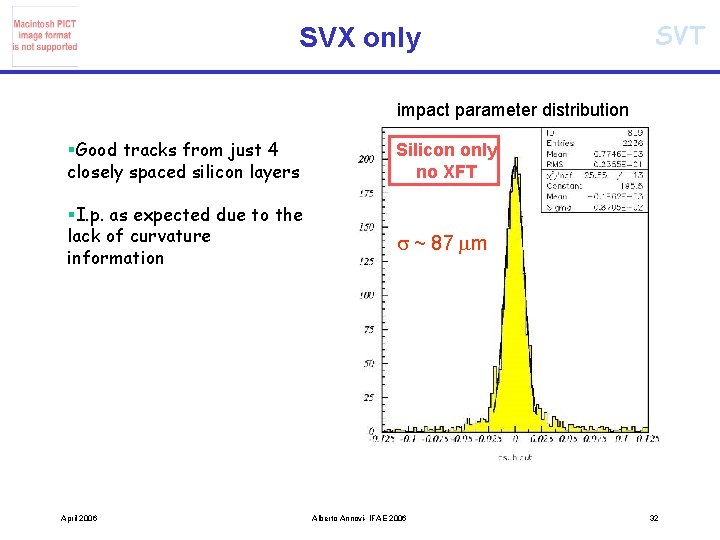

SVX only SVT impact parameter distribution §Good tracks from just 4 closely spaced silicon layers Silicon only no XFT §I. p. as expected due to the lack of curvature information s ~ 87 m April 2006 Alberto Annovi- IFAE 2006 32

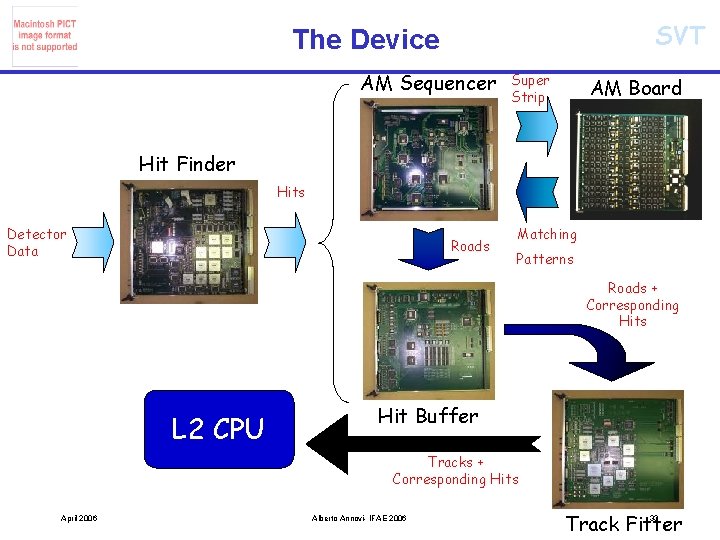

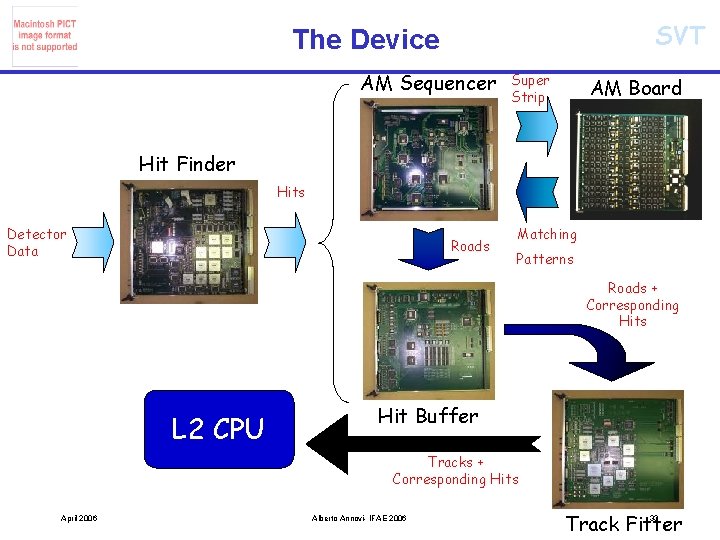

SVT The Device AM Sequencer Super Strip AM Board Hit Finder Hits Detector Data Roads Matching Patterns Roads + Corresponding Hits L 2 CPU Hit Buffer Tracks + Corresponding Hits April 2006 Alberto Annovi- IFAE 2006 Track Fitter 33

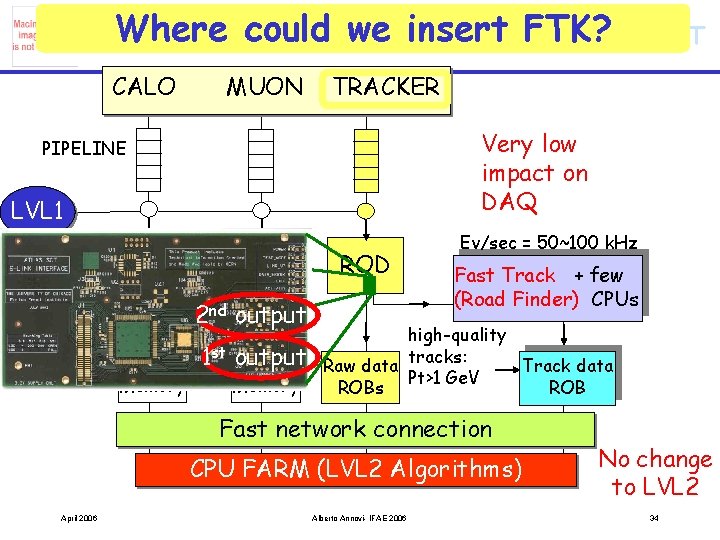

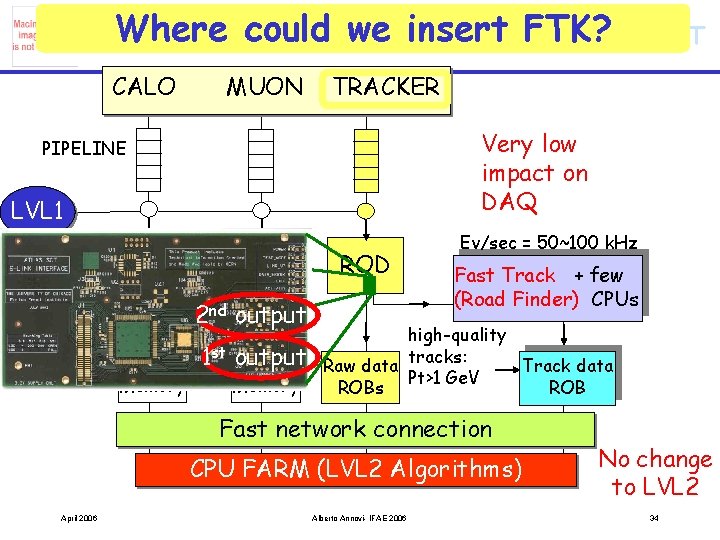

Where could we insert FTK? CALO MUON TRACKER Very low impact on DAQ PIPELINE LVL 1 FE FE 2 nd output Buffer Memory 1 st output Buffer Memory ROD Ev/sec = 50~100 k. Hz Fast Track + few (Road Finder) CPUs high-quality tracks: Track data Raw data Pt>1 Ge. V ROBs Fast network connection CPU FARM (LVL 2 Algorithms) April 2006 SVT Alberto Annovi- IFAE 2006 No change to LVL 2 34

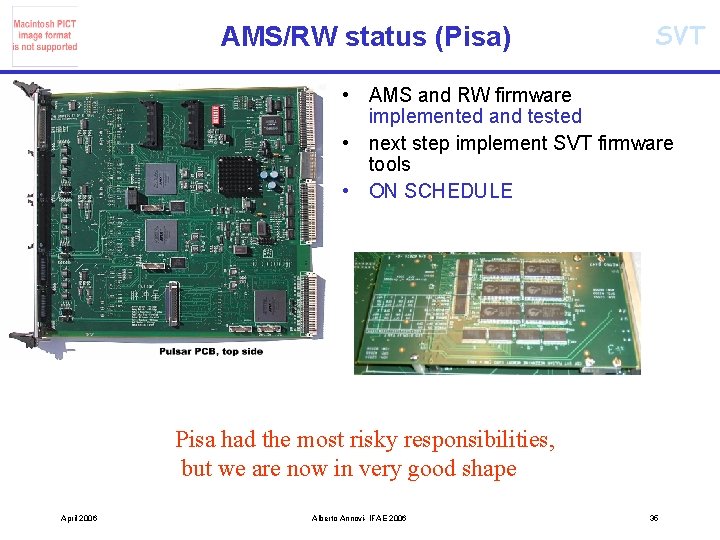

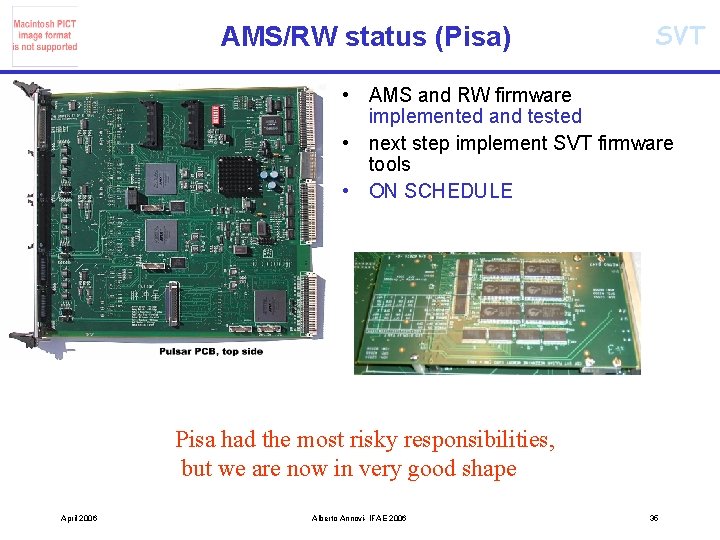

AMS/RW status (Pisa) SVT • AMS and RW firmware implemented and tested • next step implement SVT firmware tools • ON SCHEDULE Pisa had the most risky responsibilities, but we are now in very good shape April 2006 Alberto Annovi- IFAE 2006 35

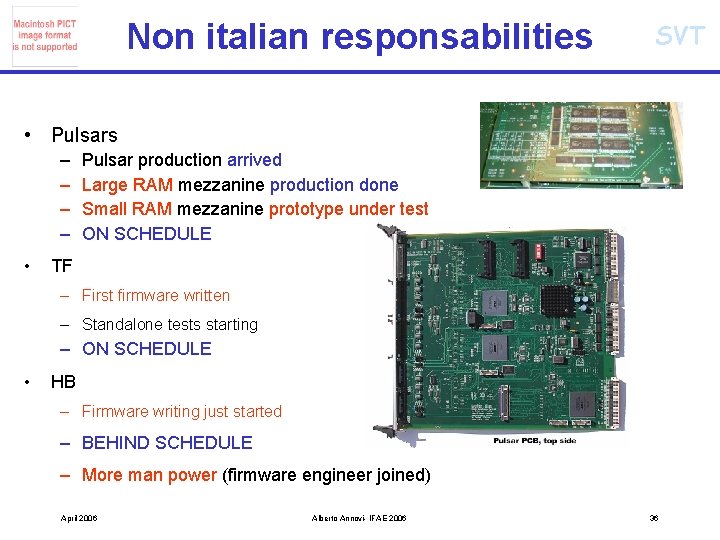

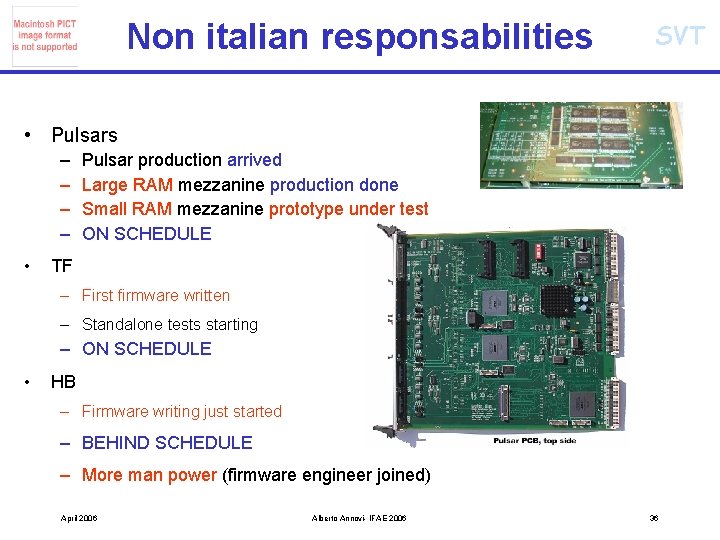

Non italian responsabilities SVT • Pulsars – – • Pulsar production arrived Large RAM mezzanine production done Small RAM mezzanine prototype under test ON SCHEDULE TF – First firmware written – Standalone tests starting – ON SCHEDULE • HB – Firmware writing just started – BEHIND SCHEDULE – More man power (firmware engineer joined) April 2006 Alberto Annovi- IFAE 2006 36

SVT upgrade people SVT • AM++ & AMSRW: A. Annovi, A. Bardi, M. Bitossi, M. Dell’Orso, P. Giannetti, P. Giovacchini, M. Piendibene, F. Spinella, L. Sartori, R. Tripiccione, S. Torre, I. Pedron, P. Catastini, S. Belforte, L. Ristori • HB++: I. Furic, T. Maruyama, S. Chappa, M. Aoki, E. Berry • TF++ & SRAM mezzanines: J. Adelman, U. Yang, F. Tang, M. Shochet, H. Sanders • Software: R. Carosi, S. Torre, B. Simoni, A. Annovi, P. Giovacchini, M. Rescigno, B. Di Ruzza, A. Cerri, J. Bellinger, G. Volpi, F. Sforza • Great support from Pulsar, DAQ, review committee, Silicon and operations people & Dervin’s group • INFN & Fermilab support April 2006 Alberto Annovi- IFAE 2006 37

TRIGGER: Tracking @ Level 2 & Level 1 SVT 1. Atlas/CDF USA-Pisa group working for physics case for FTK (Gruppo V –Pisa project 2000 -02) @ Level 2 http: //hep. uchicago. edu/cdf/shochet/ftk_12_05/meeting. html Proposal discussed during 2006 – If approved USA funds autumn 2006 a) small prototype (using CDF AMchip) as soon as possible; b) upgrade for high luminosity; c) upgrade for SLHC Italy will be required to partecipate 2. Try to use same AMchip for simplified tracking @ Level 1 3. 4. April 2006 Alberto Annovi- IFAE 2006 38

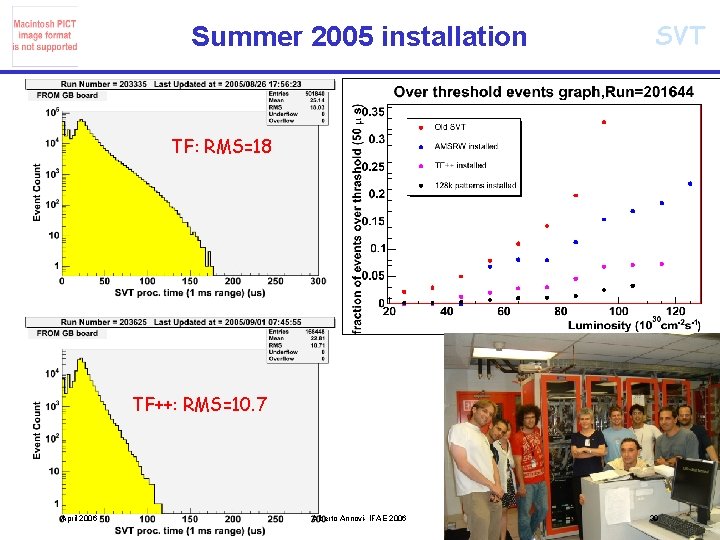

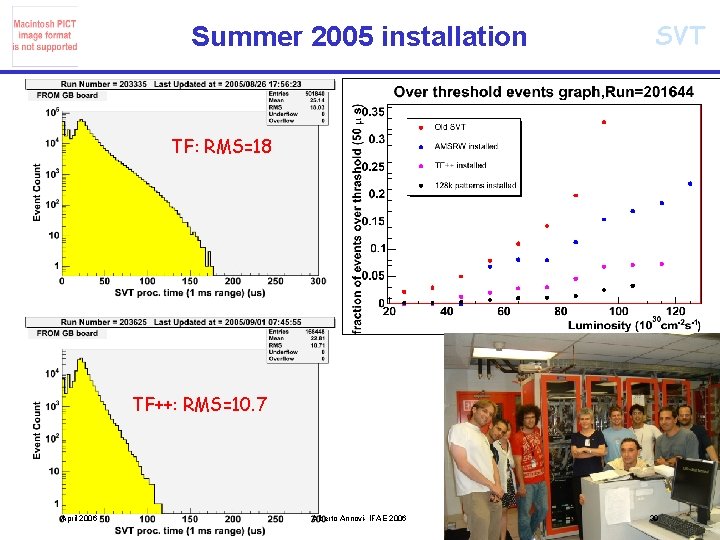

Summer 2005 installation SVT TF: RMS=18 TF++: RMS=10. 7 April 2006 Save ~10 s @ 100 E 30 Alberto Annovi- IFAE 2006 39

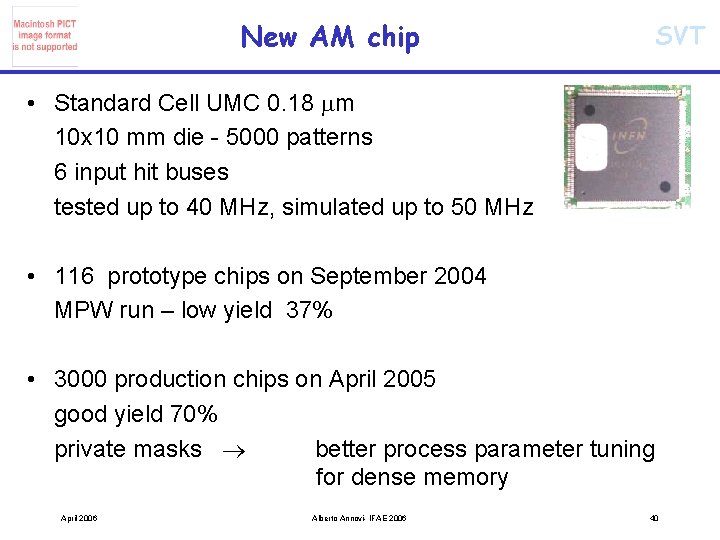

New AM chip SVT • Standard Cell UMC 0. 18 m 10 x 10 mm die - 5000 patterns 6 input hit buses tested up to 40 MHz, simulated up to 50 MHz • 116 prototype chips on September 2004 MPW run – low yield 37% • 3000 production chips on April 2005 good yield 70% private masks better process parameter tuning for dense memory April 2006 Alberto Annovi- IFAE 2006 40

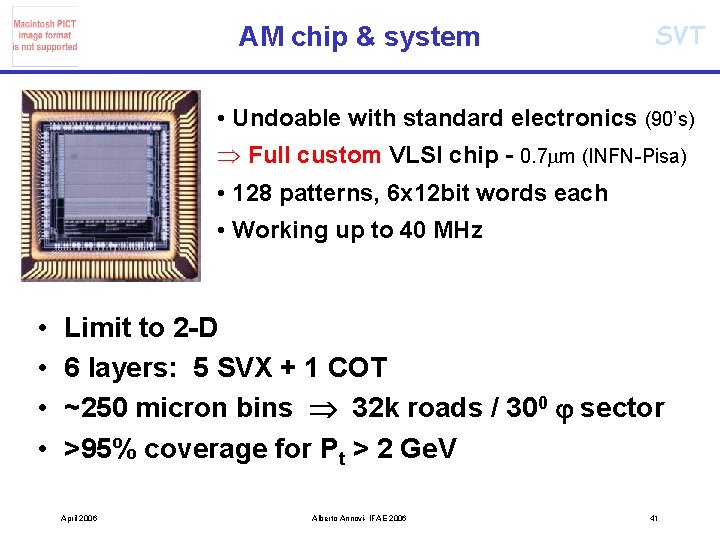

AM chip & system SVT • Undoable with standard electronics (90’s) Full custom VLSI chip - 0. 7 m (INFN-Pisa) • 128 patterns, 6 x 12 bit words each • Working up to 40 MHz • • Limit to 2 -D 6 layers: 5 SVX + 1 COT ~250 micron bins 32 k roads / 300 j sector >95% coverage for Pt > 2 Ge. V April 2006 Alberto Annovi- IFAE 2006 41

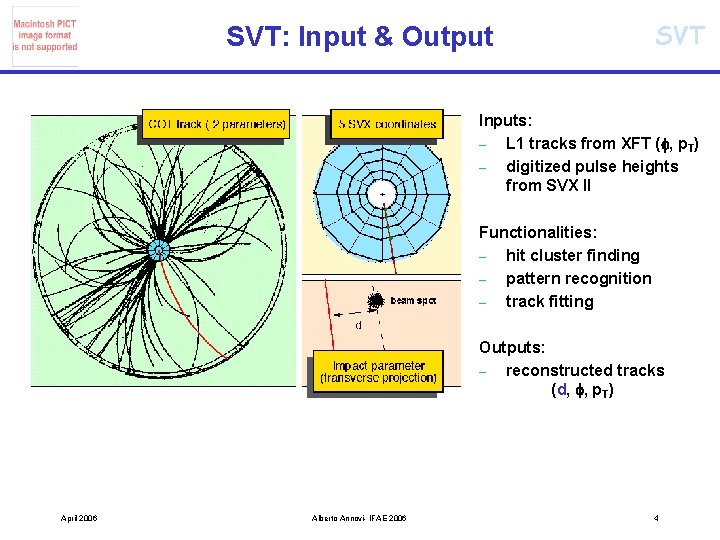

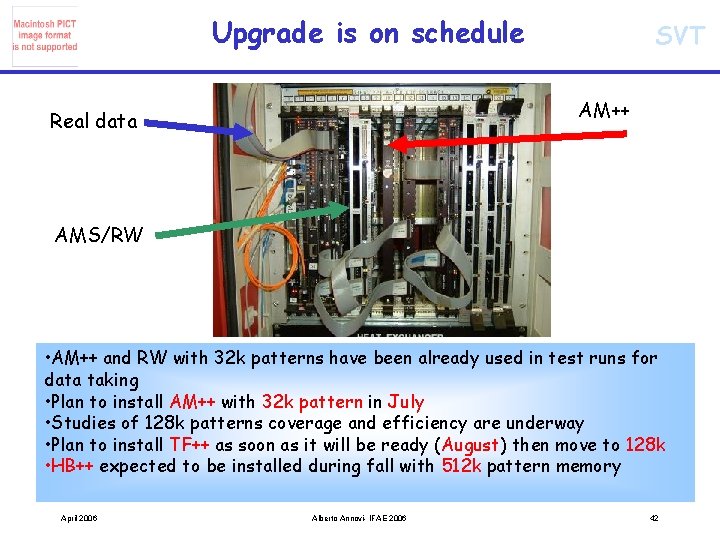

Upgrade is on schedule SVT AM++ Real data AMS/RW • AM++ and RW with 32 k patterns have been already used in test runs for data taking • Plan to install AM++ with 32 k pattern in July • Studies of 128 k patterns coverage and efficiency are underway • Plan to install TF++ as soon as it will be ready (August) then move to 128 k • HB++ expected to be installed during fall with 512 k pattern memory April 2006 Alberto Annovi- IFAE 2006 42