SVD DAQ 25 Jan 2011 Belle 2 DAQ

SVD DAQ 25 Jan 2011 Belle 2 DAQ meeting @Beijing T. Tsuboyama (KEK)

Outline l FADC l FTB and Timing distribution l Schedule This talk is based on slides shown in Krakow meeting in Dec. 2010 and B 2 GM in Nov. 2010, especially by M. Friedl and W. Ostrowicz. 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 2

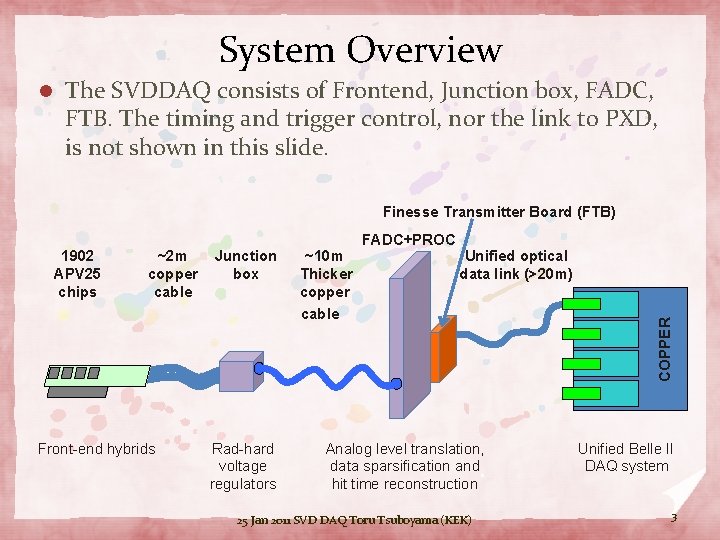

System Overview l The SVDDAQ consists of Frontend, Junction box, FADC, FTB. The timing and trigger control, nor the link to PXD, is not shown in this slide. Finesse Transmitter Board (FTB) ~2 m copper cable Front-end hybrids Junction box Rad-hard voltage regulators ~10 m Thicker copper cable Unified optical data link (>20 m) Analog level translation, data sparsification and hit time reconstruction 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) COPPER 1902 APV 25 chips FADC+PROC Unified Belle II DAQ system 3

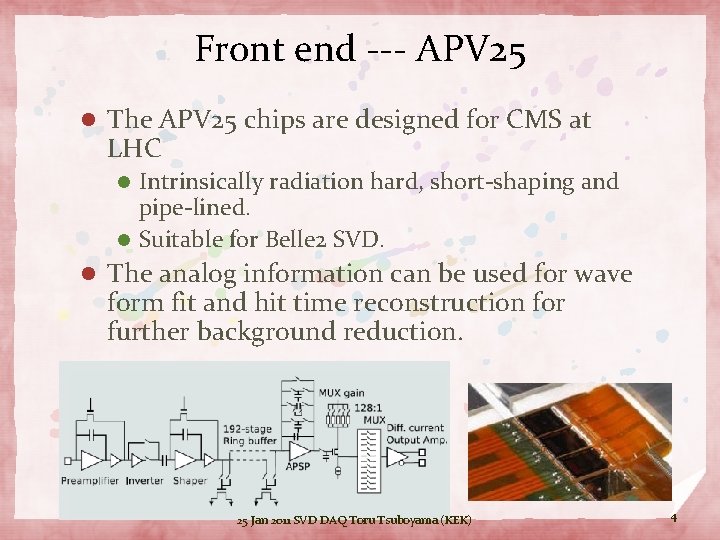

Front end --- APV 25 l The APV 25 chips are designed for CMS at LHC Intrinsically radiation hard, short-shaping and pipe-lined. l Suitable for Belle 2 SVD. l l The analog information can be used for wave form fit and hit time reconstruction for further background reduction. 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 4

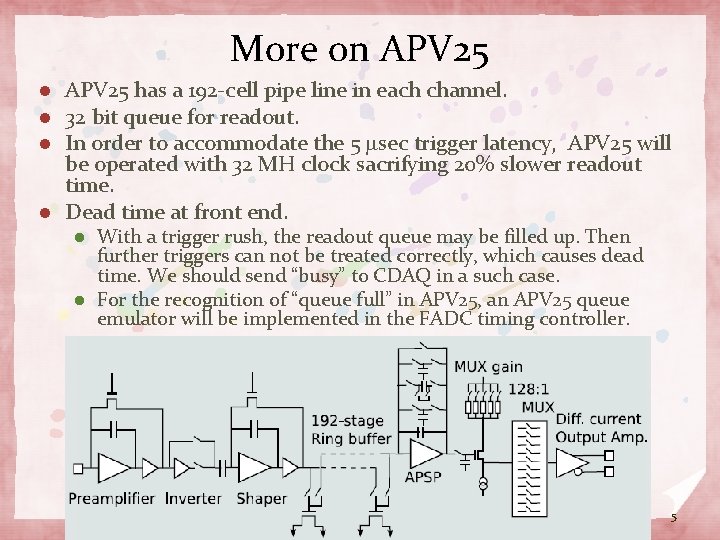

More on APV 25 has a 192 -cell pipe line in each channel. 32 bit queue for readout. In order to accommodate the 5 msec trigger latency, APV 25 will be operated with 32 MH clock sacrifying 20% slower readout time. l Dead time at front end. l l l With a trigger rush, the readout queue may be filled up. Then further triggers can not be treated correctly, which causes dead time. We should send “busy” to CDAQ in a such case. l For the recognition of “queue full” in APV 25, an APV 25 queue emulator will be implemented in the FADC timing controller. l 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 5

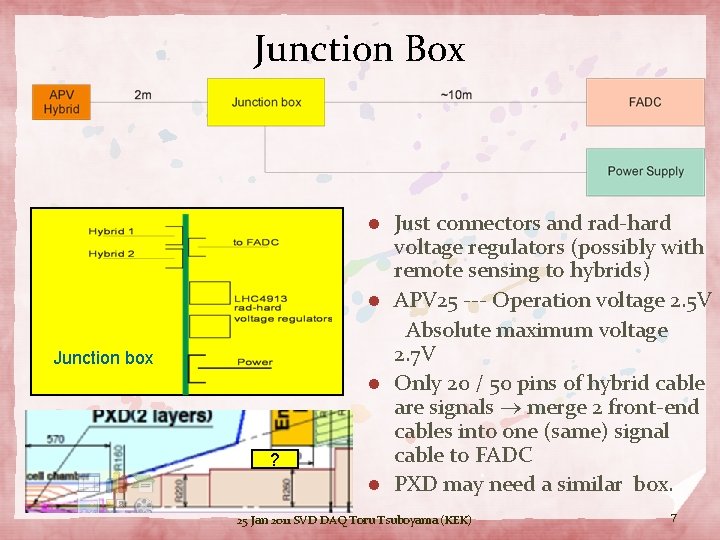

Junction Box Just connectors and rad-hard voltage regulators (possibly with remote sensing to hybrids) l APV 25 --- Operation voltage 2. 5 V Absolute maximum voltage 2. 7 V l Only 20 / 50 pins of hybrid cable are signals merge 2 front-end cables into one (same) signal cable to FADC l PXD may need a similar box. l Junction box ? 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 7

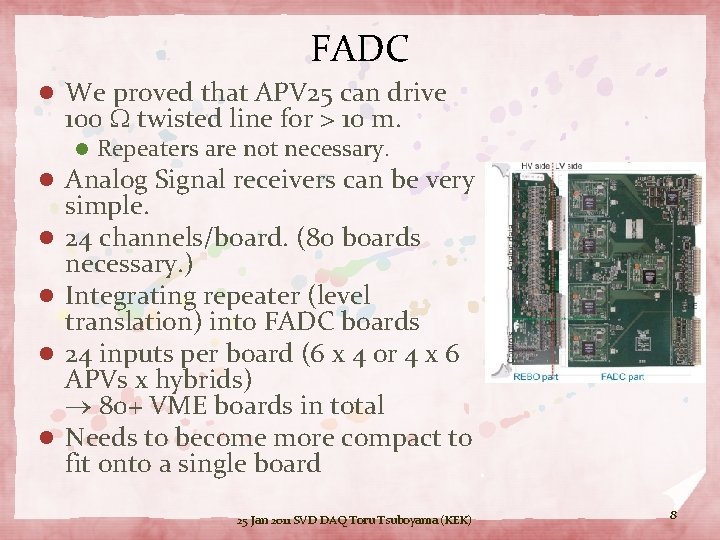

FADC l We proved that APV 25 can drive 100 W twisted line for > 10 m. l l l Repeaters are not necessary. Analog Signal receivers can be very simple. 24 channels/board. (80 boards necessary. ) Integrating repeater (level translation) into FADC boards 24 inputs per board (6 x 4 or 4 x 6 APVs x hybrids) 80+ VME boards in total Needs to become more compact to fit onto a single board 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 8

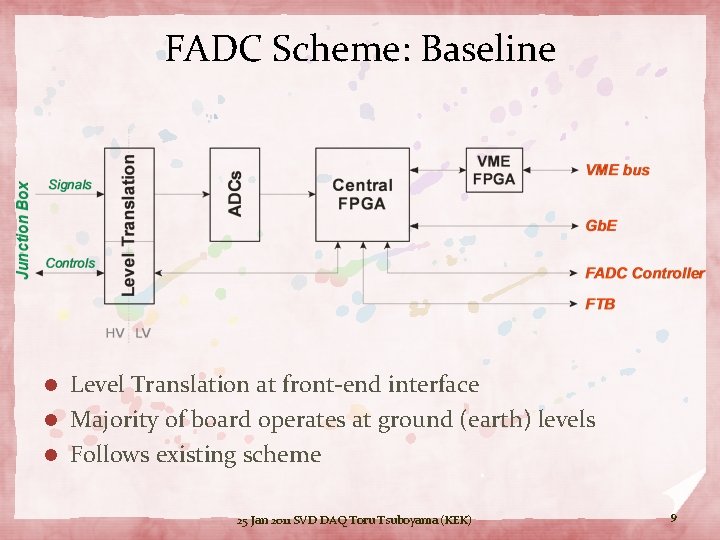

FADC Scheme: Baseline Level Translation at front-end interface l Majority of board operates at ground (earth) levels l Follows existing scheme l 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 9

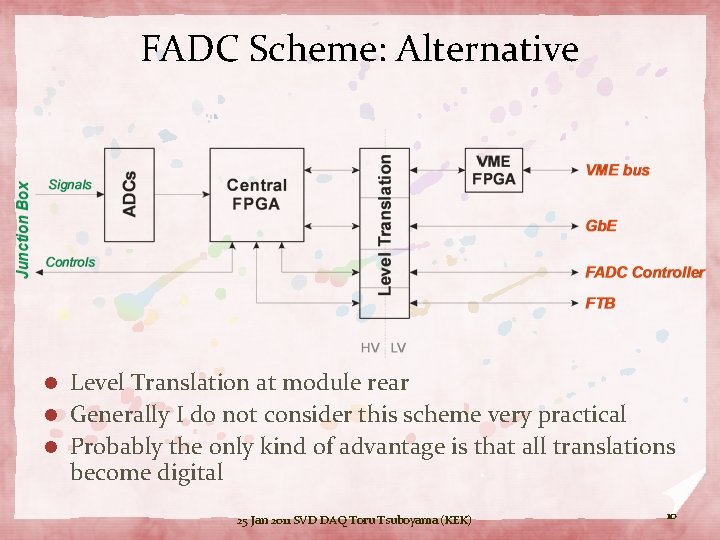

FADC Scheme: Alternative Level Translation at module rear l Generally I do not consider this scheme very practical l Probably the only kind of advantage is that all translations become digital l 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 10

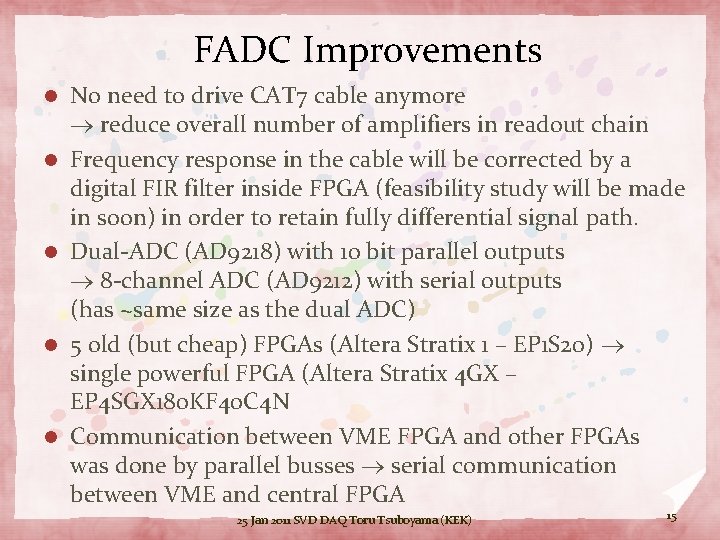

FADC Improvements l l l No need to drive CAT 7 cable anymore reduce overall number of amplifiers in readout chain Frequency response in the cable will be corrected by a digital FIR filter inside FPGA (feasibility study will be made in soon) in order to retain fully differential signal path. Dual-ADC (AD 9218) with 10 bit parallel outputs 8 -channel ADC (AD 9212) with serial outputs (has ~same size as the dual ADC) 5 old (but cheap) FPGAs (Altera Stratix 1 – EP 1 S 20) single powerful FPGA (Altera Stratix 4 GX – EP 4 SGX 180 KF 40 C 4 N Communication between VME FPGA and other FPGAs was done by parallel busses serial communication between VME and central FPGA 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 15

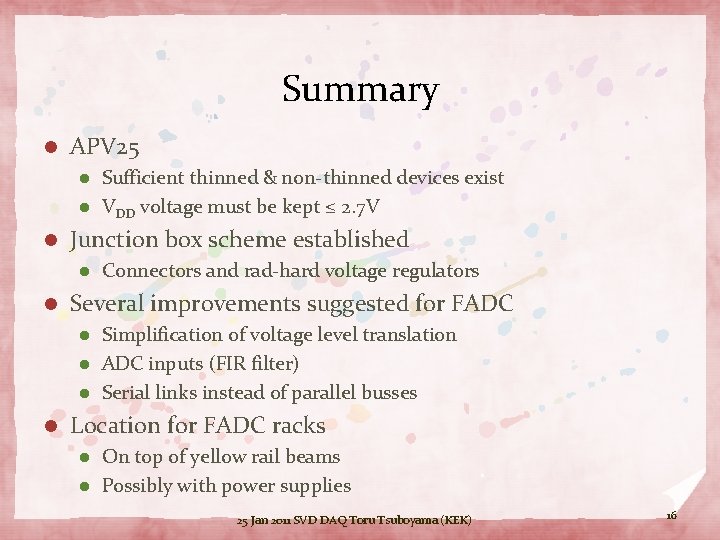

Summary l APV 25 Sufficient thinned & non-thinned devices exist l VDD voltage must be kept ≤ 2. 7 V l l Junction box scheme established l l Connectors and rad-hard voltage regulators Several improvements suggested for FADC Simplification of voltage level translation l ADC inputs (FIR filter) l Serial links instead of parallel busses l l Location for FADC racks On top of yellow rail beams l Possibly with power supplies l 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 16

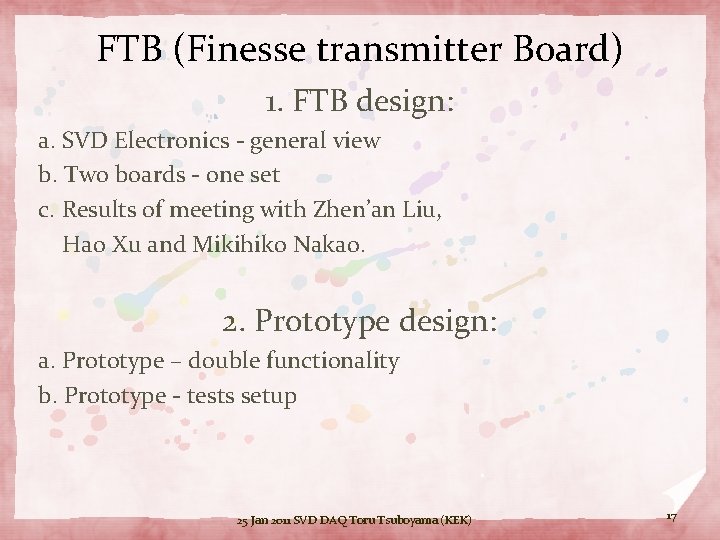

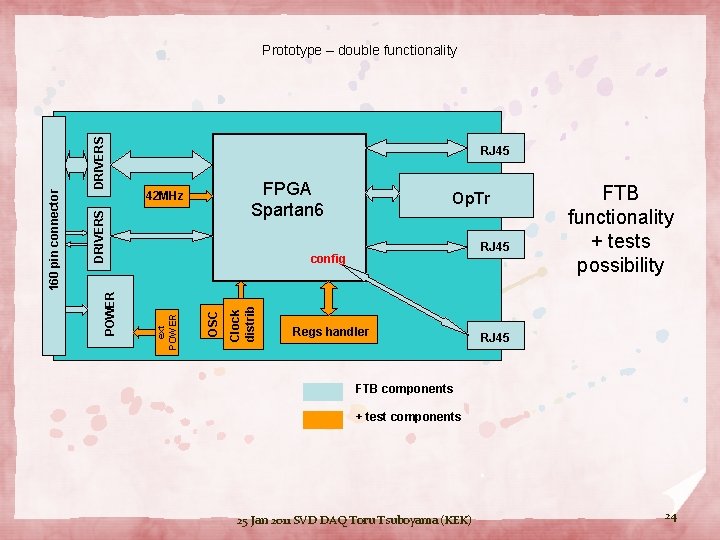

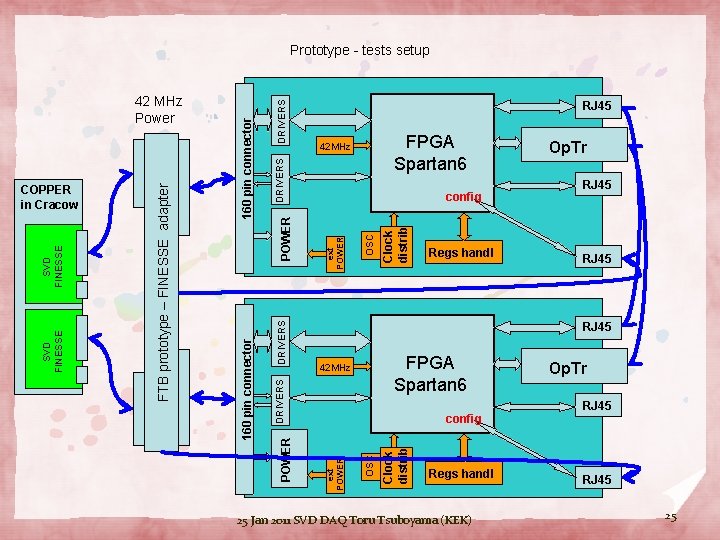

FTB (Finesse transmitter Board) 1. FTB design: a. SVD Electronics - general view b. Two boards - one set c. Results of meeting with Zhen’an Liu, Hao Xu and Mikihiko Nakao. 2. Prototype design: a. Prototype – double functionality b. Prototype - tests setup 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 17

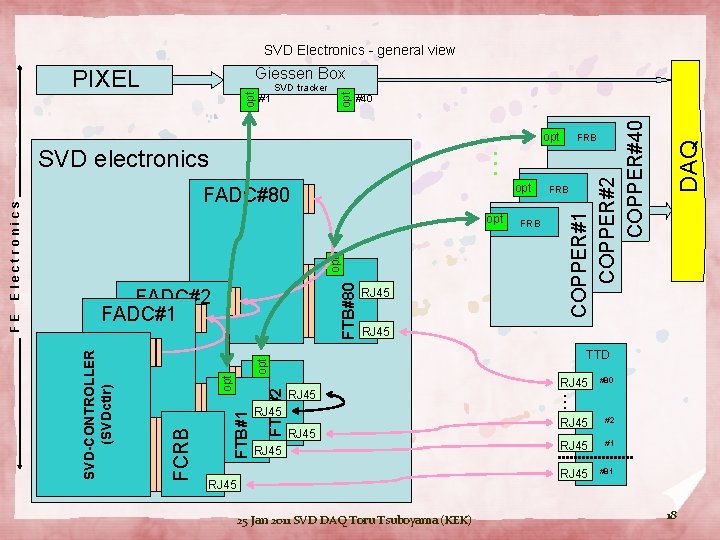

SVD Electronics - general view opt … opt FADC#80 FTB#80 opt FADC#2 FADC#1 RJ 45 FRB RJ 45 FTB#2 FTB#1 FCRB opt TTD RJ 45 RJ 45 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) RJ 45 #80 … SVD-CONTROLLER (SVDctlr) FE Electronics SVD electronics FRB DAQ #40 COPPER#1 COPPER#2 COPPER#40 opt SVD tracker #1 opt Giessen Box PIXEL RJ 45 #2 RJ 45 #1 RJ 45 #81 18

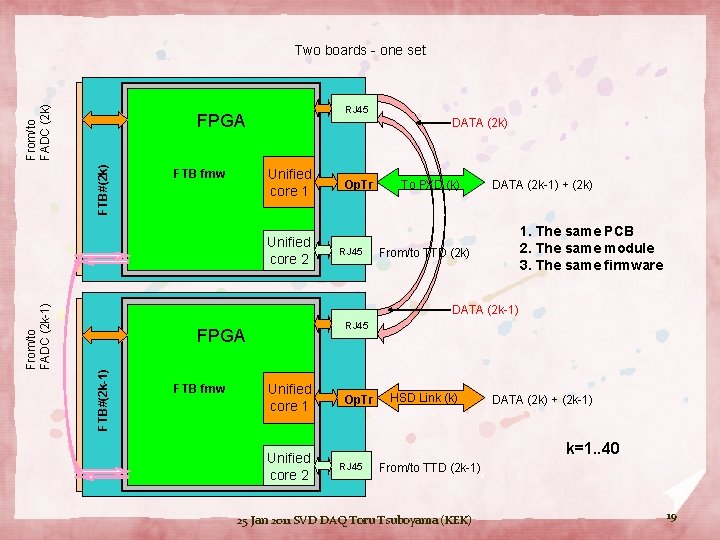

From/to FADC (2 k) Two boards - one set RJ 45 FTB#(2 k) FPGA DATA (2 k) Unified core 1 FTB fmw RJ 45 To PXD (k) DATA (2 k-1) + (2 k) 1. The same PCB 2. The same module 3. The same firmware From/to TTD (2 k) DATA (2 k-1) RJ 45 FPGA FTB#(2 k-1) From/to FADC (2 k-1) Unified core 2 Op. Tr FTB fmw Unified core 1 Unified core 2 Op. Tr HSD Link (k) DATA (2 k) + (2 k-1) k=1. . 40 RJ 45 From/to TTD (2 k-1) 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 19

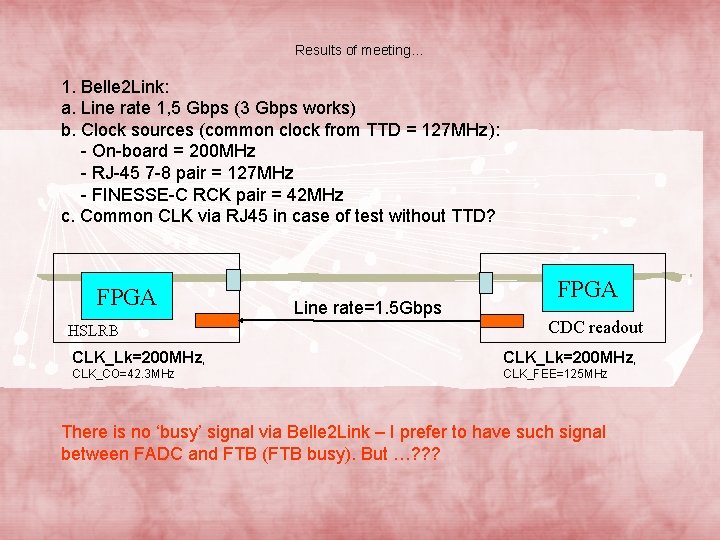

Results of meeting… 1. Belle 2 Link: a. Line rate 1, 5 Gbps (3 Gbps works) b. Clock sources (common clock from TTD = 127 MHz): - On-board = 200 MHz - RJ-45 7 -8 pair = 127 MHz - FINESSE-C RCK pair = 42 MHz c. Common CLK via RJ 45 in case of test without TTD? FPGA HSLRB Line rate=1. 5 Gbps FPGA CDC readout CLK_Lk=200 MHz, CLK_CO=42. 3 MHz CLK_FEE=125 MHz There is no ‘busy’ signal via Belle 2 Link – I prefer to have such signal between FADC and FTB (FTB busy). But …? ? ?

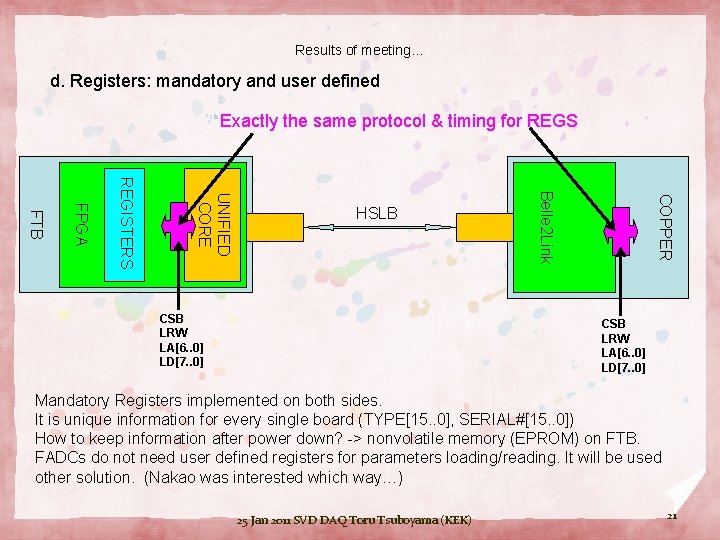

Results of meeting… d. Registers: mandatory and user defined Exactly the same protocol & timing for REGS COPPER CSB LRW LA[6. . 0] LD[7. . 0] Belle 2 Link UNIFIED CORE REGISTERS FPGA FTB HSLB CSB LRW LA[6. . 0] LD[7. . 0] Mandatory Registers implemented on both sides. It is unique information for every single board (TYPE[15. . 0], SERIAL#[15. . 0]) How to keep information after power down? -> nonvolatile memory (EPROM) on FTB. FADCs do not need user defined registers for parameters loading/reading. It will be used other solution. (Nakao was interested which way…) 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 21

Results of meeting… Future (near? ? ? ): - universal firmware? – in plans - modules for sub-groups for testing? – they plan… - any NOTE describing rules and requirements – not yet but… 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 22

Results of meeting… 2. TTD link: ACK, TRG, CLK, RSV. a) ‘ACK signal (1 -2 pair) is a serialized response information to the central timing system’ – is it the same/similar as ‘BUSY’ signal? - similar. Any description how to manage the ACK signal. – not yet b) any RESET via TTD link? – yes. As minimum TRGnb = 0, clear Data Fifos, no reload the firmware. What does RESET mean for FADC? c) any firmware? – maybe soon? ? d) any NOTE describing rules and requirements – not yet but… 3. JTAG link e) For firmware loading – one cable per one board? – not decided yet f) After firmware loading – what with info in mandatory regs? – ext. EPROM

DRIVERS RJ 45 FPGA Spartan 6 DRIVERS 42 MHz Op. Tr RJ 45 Clock distrib OSC config ext POWER 160 pin connector Prototype – double functionality Regs handler FTB functionality + tests possibility RJ 45 FTB components + test components 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 24

FPGA Spartan 6 42 MHz Clock distrib OSC ext POWER config Regs handl Op. Tr RJ 45 FPGA Spartan 6 42 MHz OSC ext POWER config Clock distrib DRIVERS POWER DRIVERS RJ 45 DRIVERS POWER 160 pin connector SVD FINESSE COPPER in Cracow FTB prototype – FINESSE adapter 42 MHz Power 160 pin connector Prototype - tests setup Regs handl 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) Op. Tr RJ 45 25

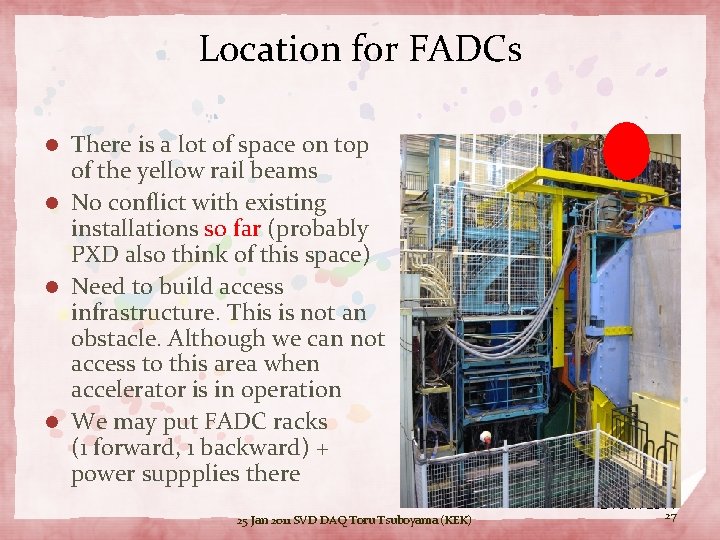

Location for FADCs There is a lot of space on top of the yellow rail beams l No conflict with existing installations so far (probably PXD also think of this space) l Need to build access infrastructure. This is not an obstacle. Although we can not access to this area when accelerator is in operation l We may put FADC racks (1 forward, 1 backward) + power suppplies there l 24 Jan 2011 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 27

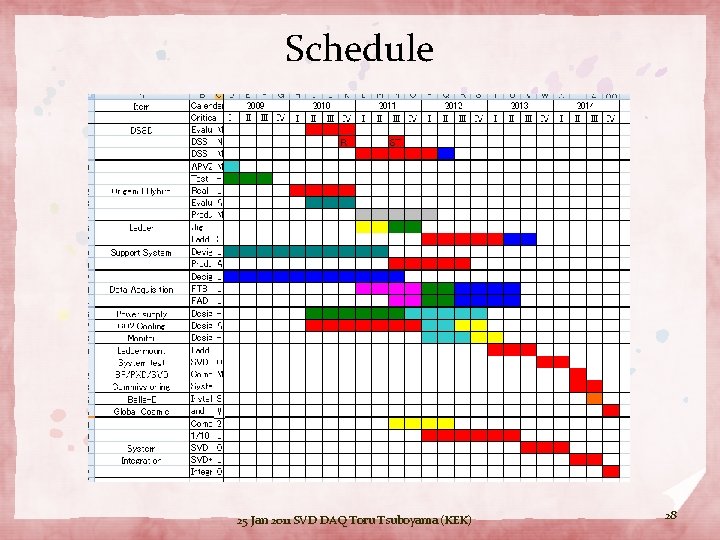

Schedule 25 Jan 2011 SVD DAQ Toru Tsuboyama (KEK) 28

- Slides: 22