Svak inversjon Nr gate source spenningen er lavere

- Slides: 30

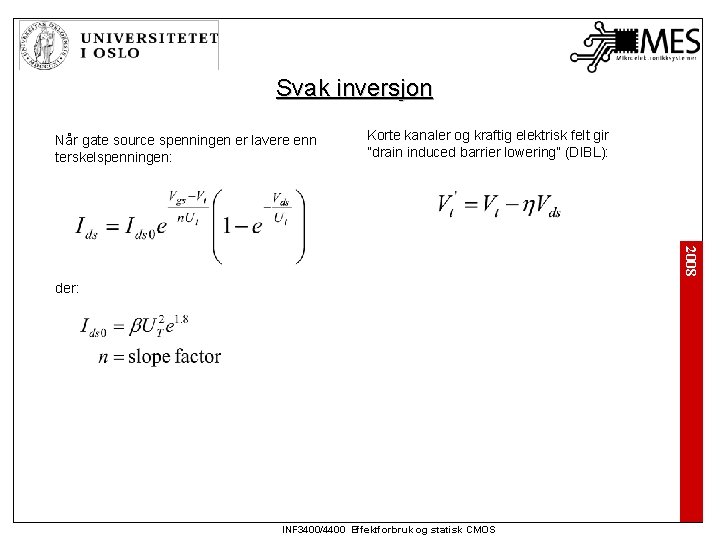

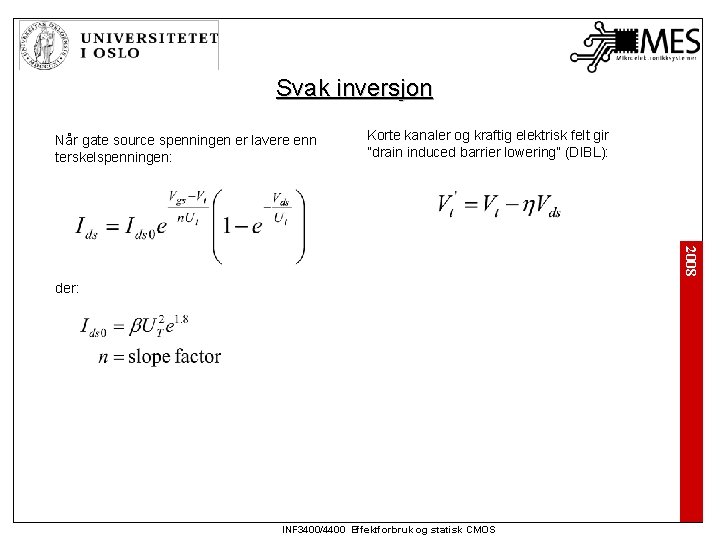

Svak inversjon Når gate source spenningen er lavere enn terskelspenningen: Korte kanaler og kraftig elektrisk felt gir ”drain induced barrier lowering” (DIBL): 2008 der: INF 3400/4400 Effektforbruk og statisk CMOS

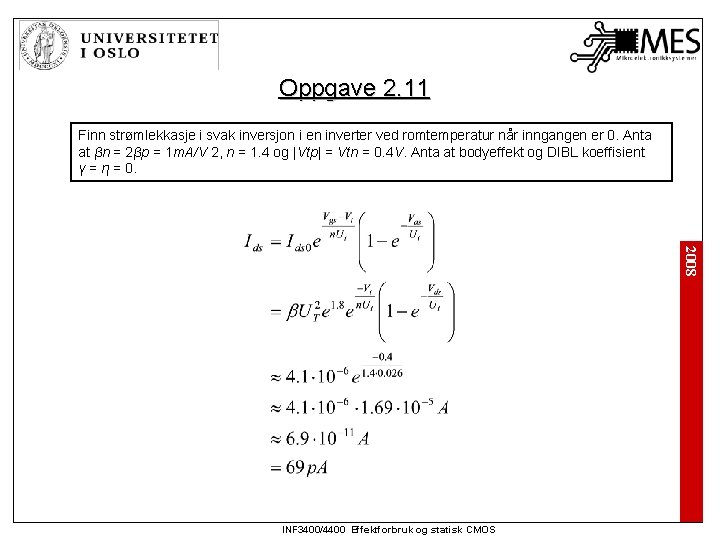

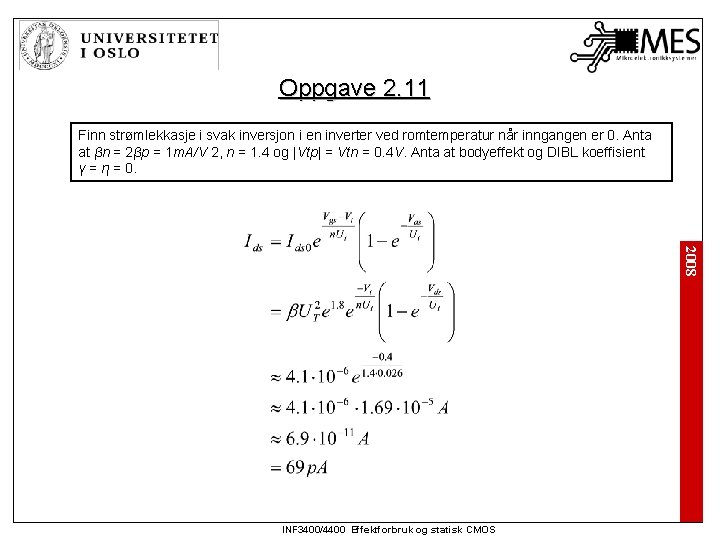

Oppgave 2. 11 Finn strømlekkasje i svak inversjon i en inverter ved romtemperatur når inngangen er 0. Anta at βn = 2βp = 1 m. A/V 2, n = 1. 4 og |Vtp| = Vtn = 0. 4 V. Anta at bodyeffekt og DIBL koeffisient γ = η = 0. 2008 INF 3400/4400 Effektforbruk og statisk CMOS

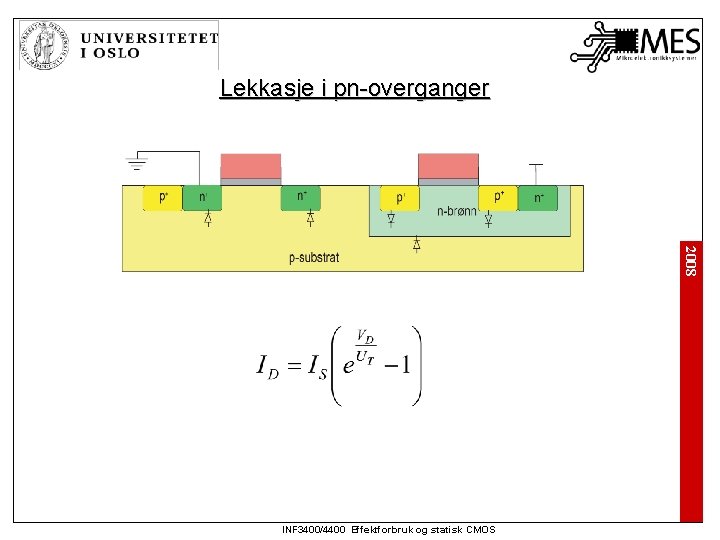

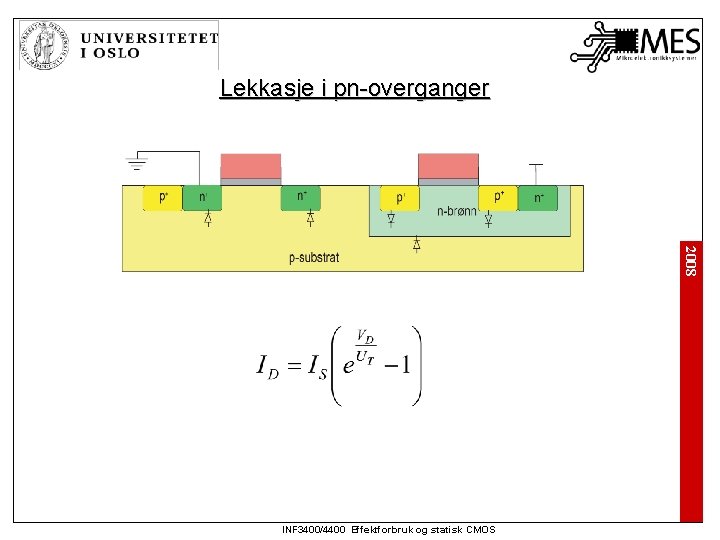

Lekkasje i pn-overganger 2008 INF 3400/4400 Effektforbruk og statisk CMOS

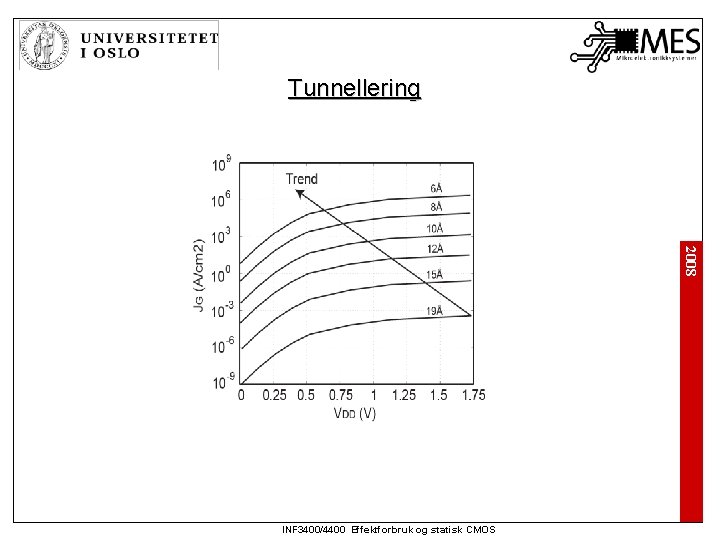

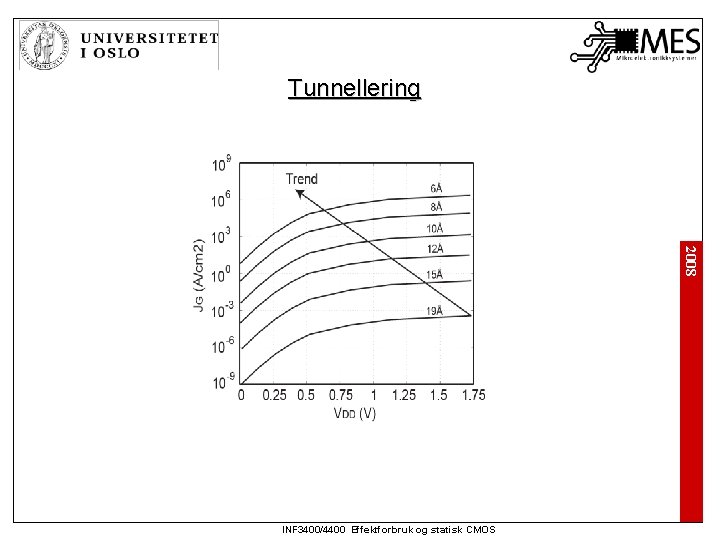

Tunnellering 2008 INF 3400/4400 Effektforbruk og statisk CMOS

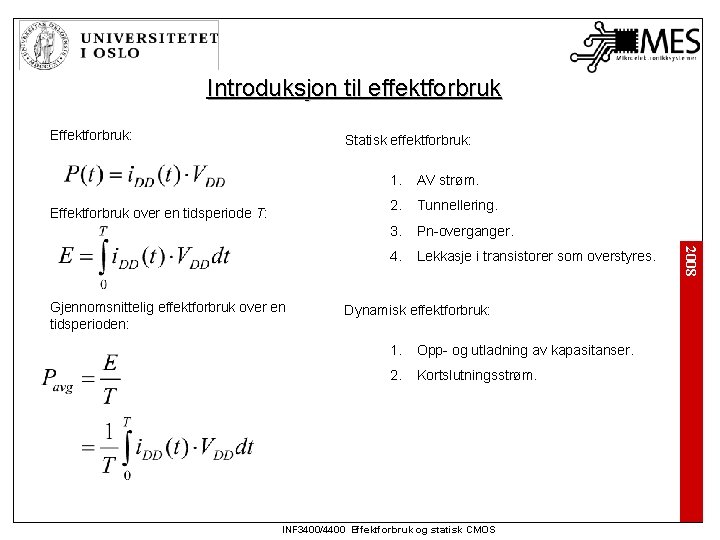

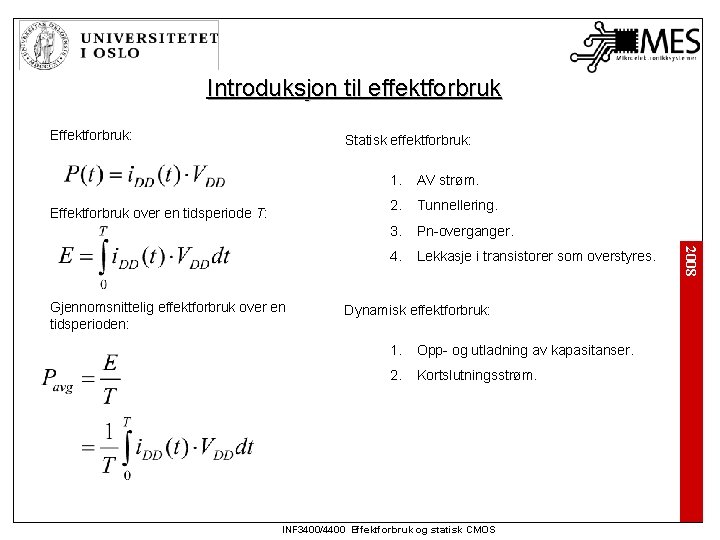

Introduksjon til effektforbruk Effektforbruk: Statisk effektforbruk: Effektforbruk over en tidsperiode T: AV strøm. 2. Tunnellering. 3. Pn-overganger. 4. Lekkasje i transistorer som overstyres. Dynamisk effektforbruk: 1. Opp- og utladning av kapasitanser. 2. Kortslutningsstrøm. INF 3400/4400 Effektforbruk og statisk CMOS 2008 Gjennomsnittelig effektforbruk over en tidsperioden: 1.

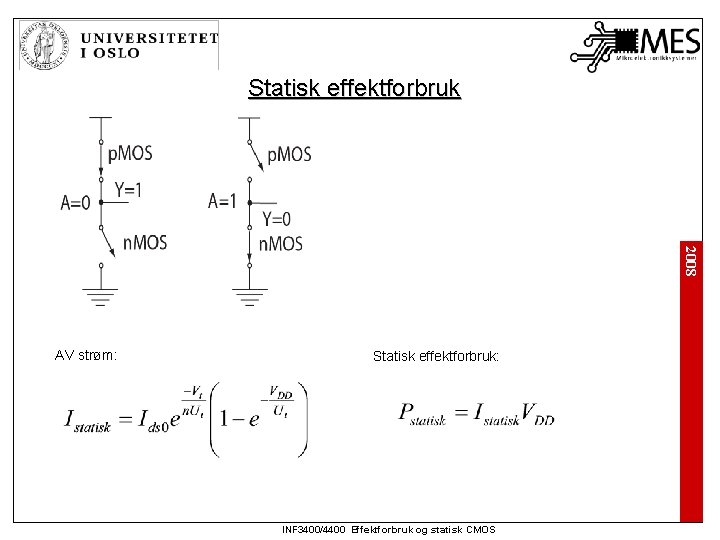

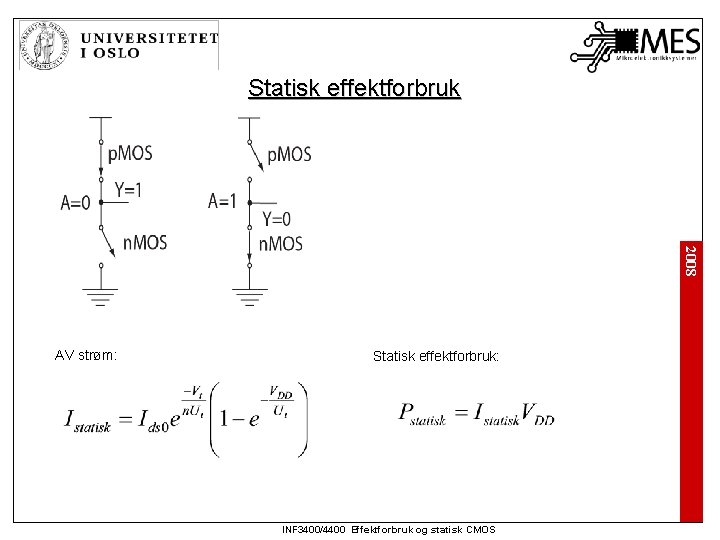

Statisk effektforbruk 2008 AV strøm: Statisk effektforbruk: INF 3400/4400 Effektforbruk og statisk CMOS

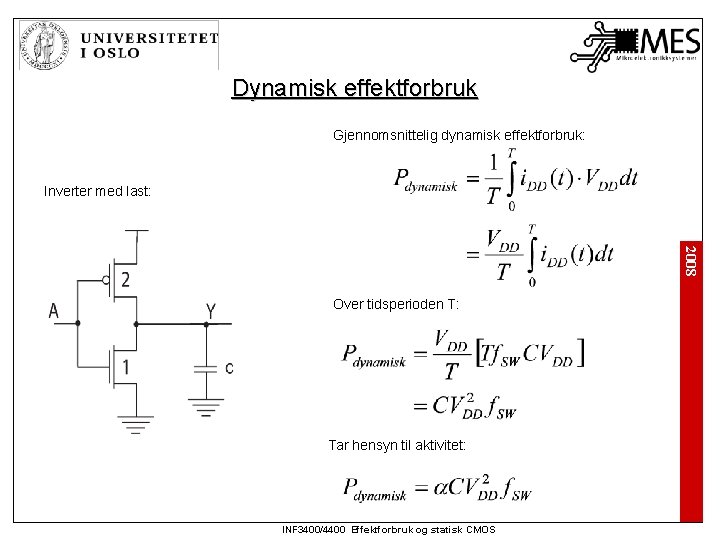

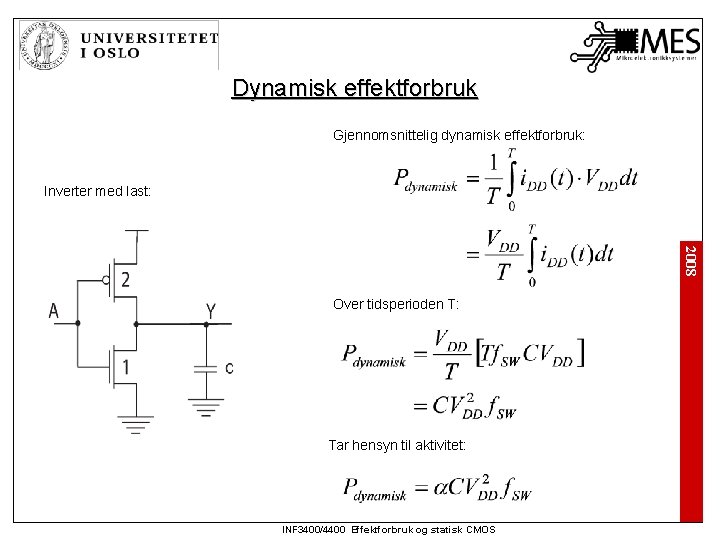

Dynamisk effektforbruk Gjennomsnittelig dynamisk effektforbruk: Inverter med last: 2008 Over tidsperioden T: Tar hensyn til aktivitet: INF 3400/4400 Effektforbruk og statisk CMOS

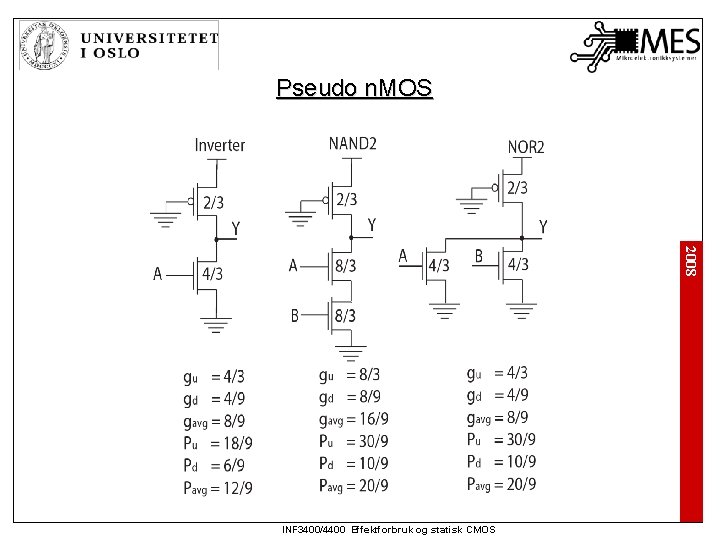

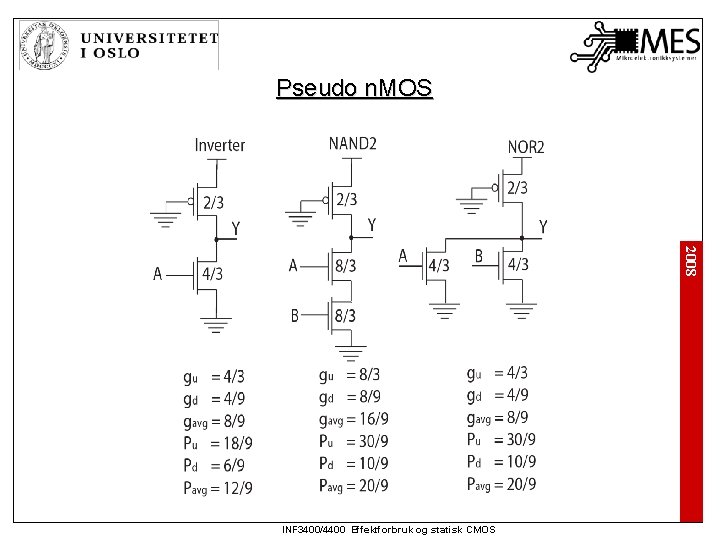

Pseudo n. MOS 2008 INF 3400/4400 Effektforbruk og statisk CMOS

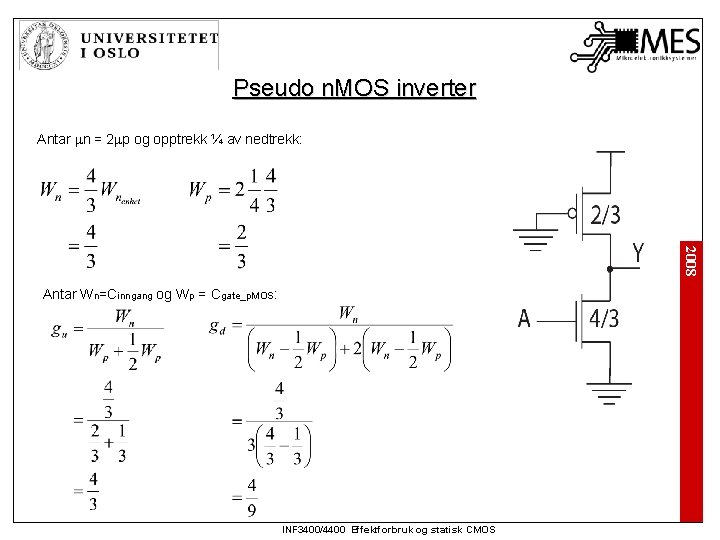

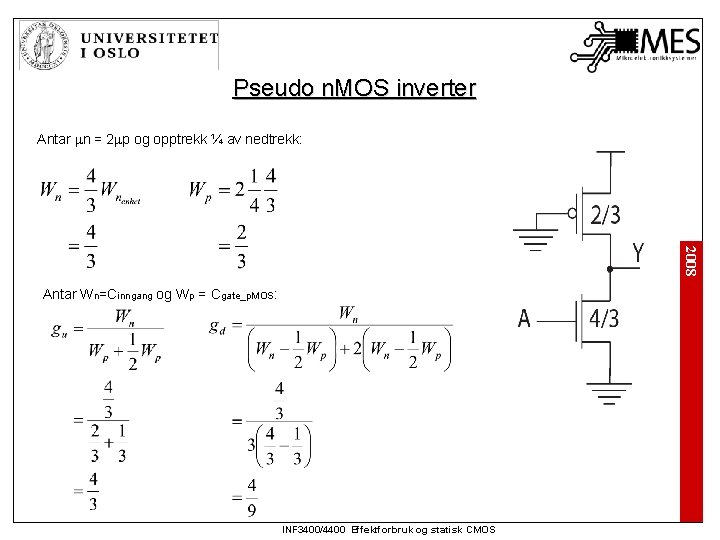

Pseudo n. MOS inverter Antar mn = 2 mp og opptrekk ¼ av nedtrekk: 2008 Antar Wn=Cinngang og Wp = Cgate_p. MOS: INF 3400/4400 Effektforbruk og statisk CMOS

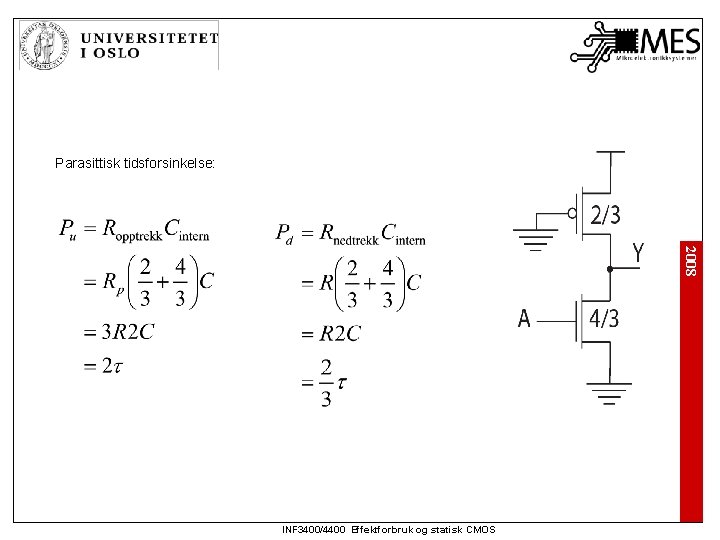

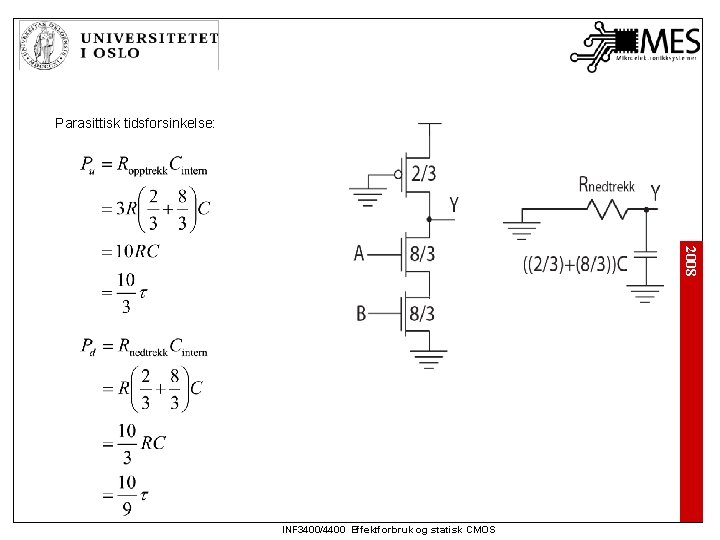

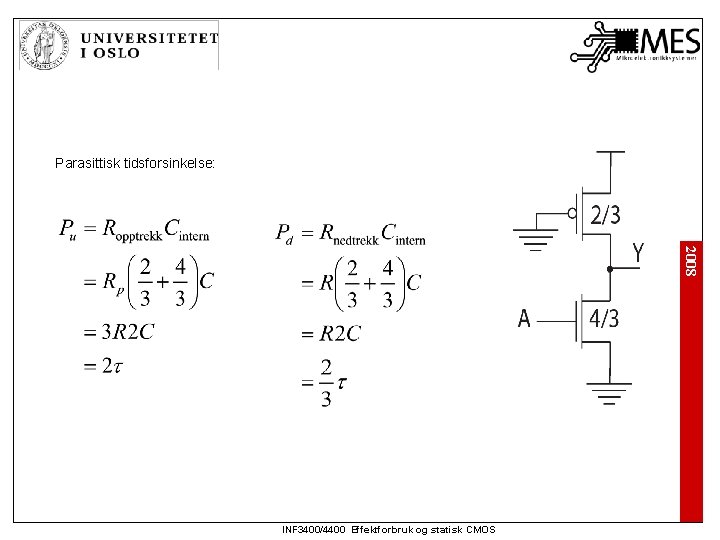

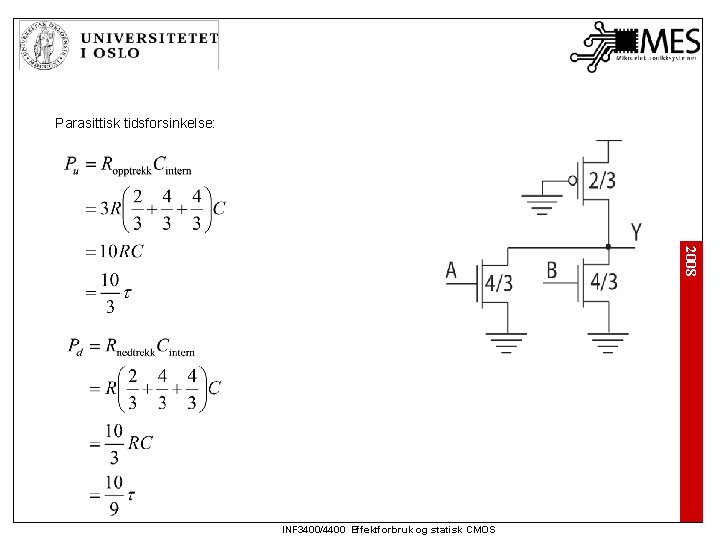

Parasittisk tidsforsinkelse: 2008 INF 3400/4400 Effektforbruk og statisk CMOS

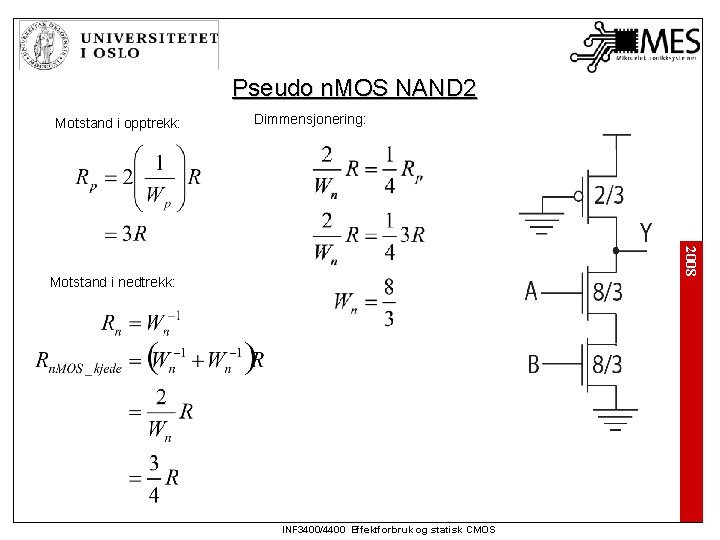

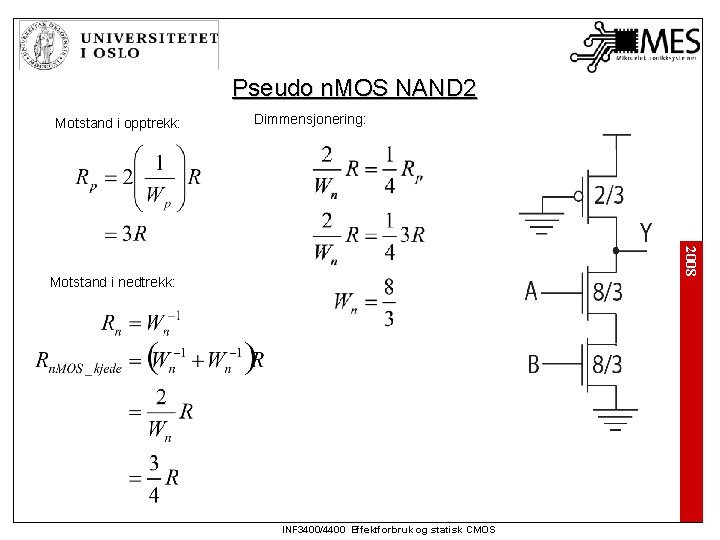

Pseudo n. MOS NAND 2 Motstand i opptrekk: Dimmensjonering: 2008 Motstand i nedtrekk: INF 3400/4400 Effektforbruk og statisk CMOS

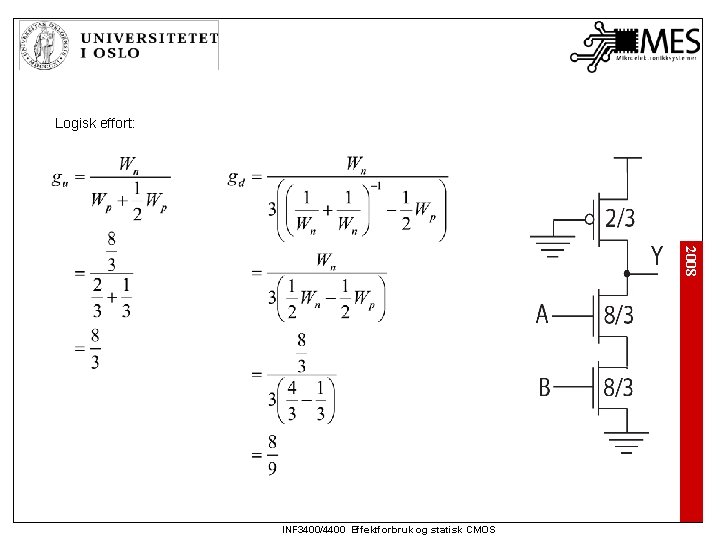

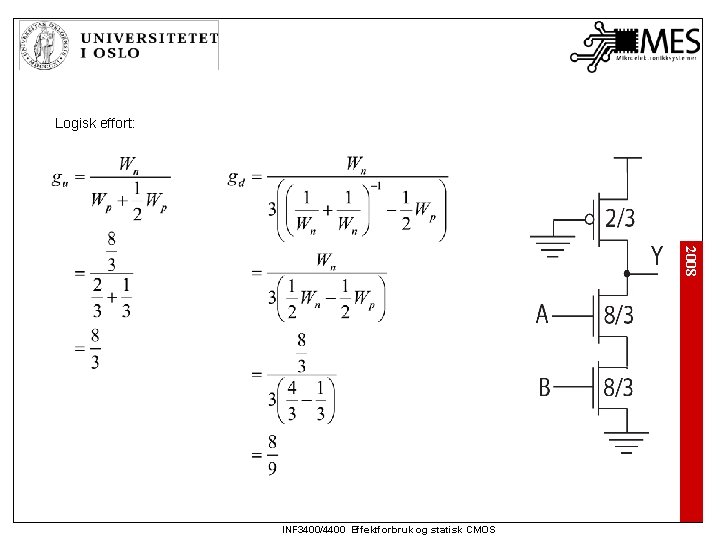

Logisk effort: 2008 INF 3400/4400 Effektforbruk og statisk CMOS

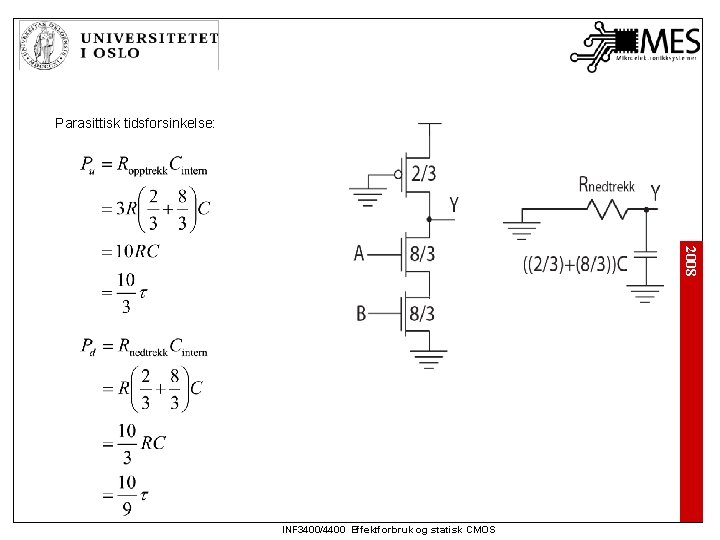

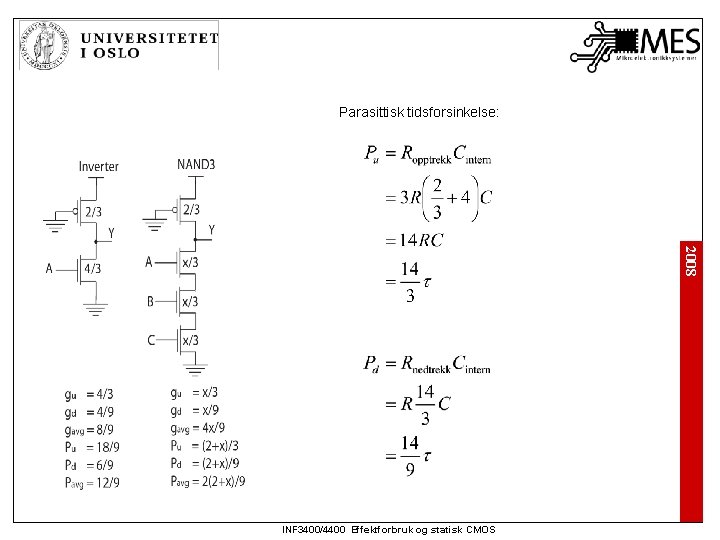

Parasittisk tidsforsinkelse: 2008 INF 3400/4400 Effektforbruk og statisk CMOS

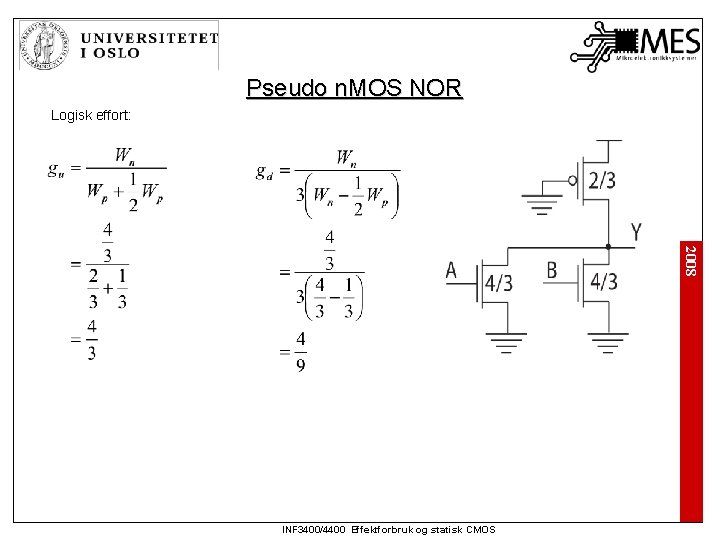

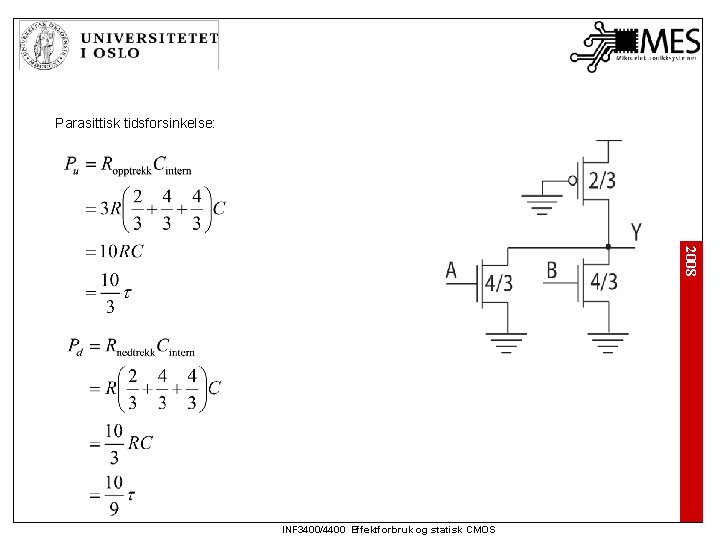

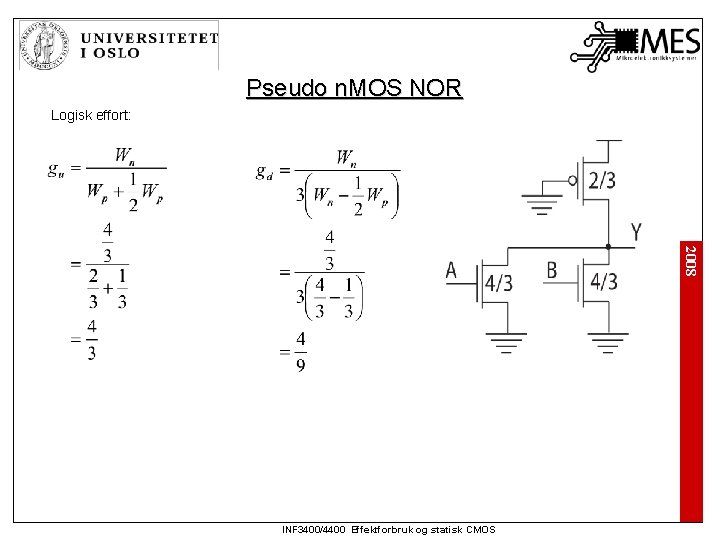

Pseudo n. MOS NOR Logisk effort: 2008 INF 3400/4400 Effektforbruk og statisk CMOS

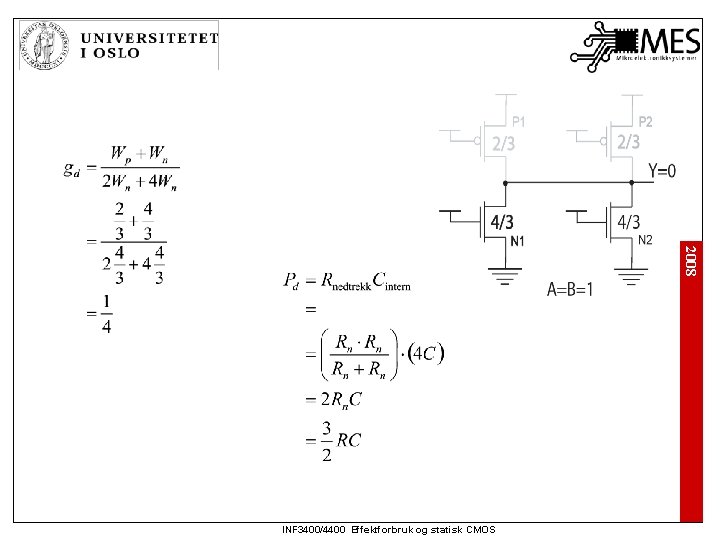

Parasittisk tidsforsinkelse: 2008 INF 3400/4400 Effektforbruk og statisk CMOS

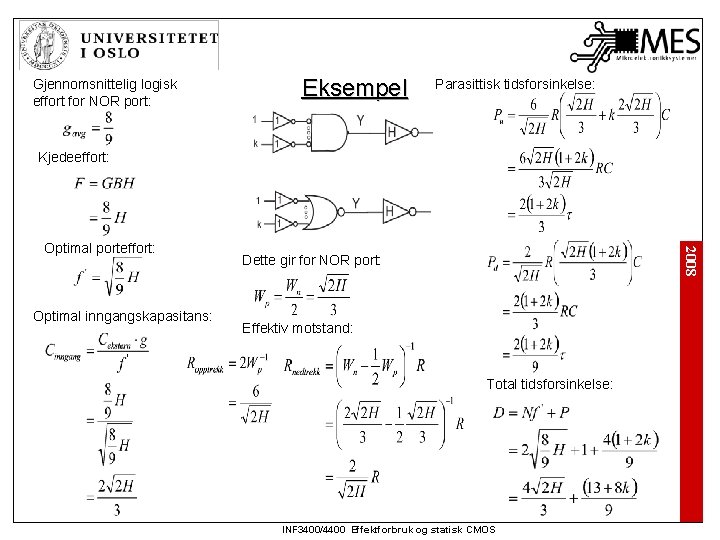

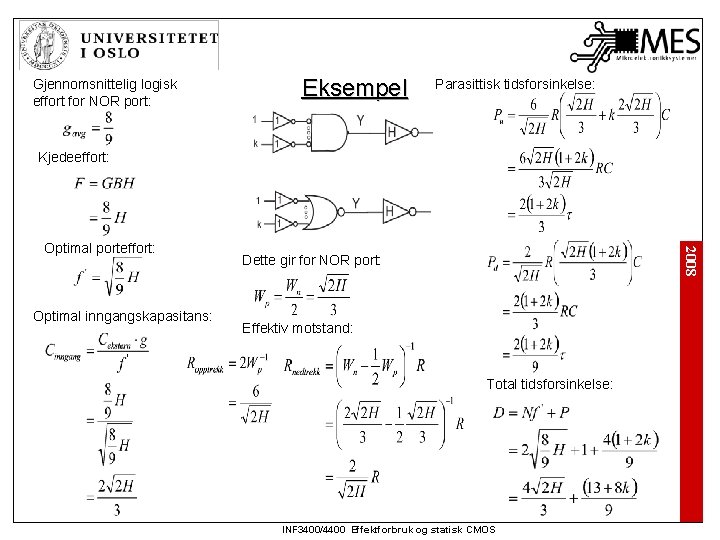

Gjennomsnittelig logisk effort for NOR port: Eksempel Parasittisk tidsforsinkelse: Kjedeeffort: Optimal inngangskapasitans: 2008 Optimal porteffort: Dette gir for NOR port: Effektiv motstand: Total tidsforsinkelse: INF 3400/4400 Effektforbruk og statisk CMOS

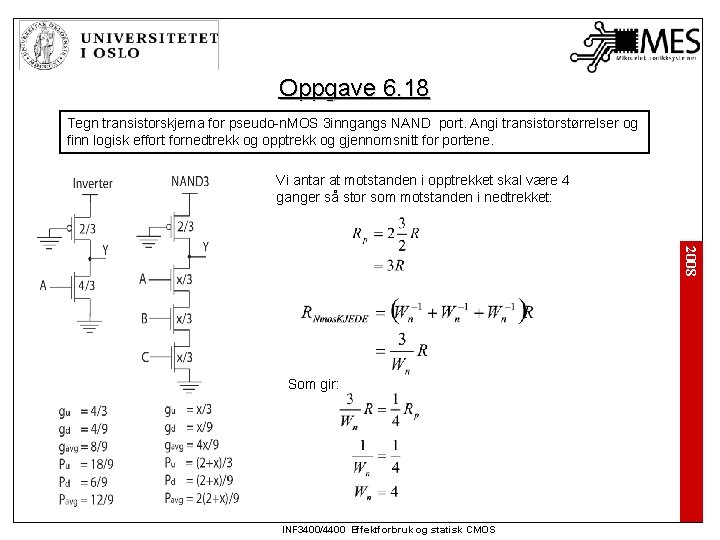

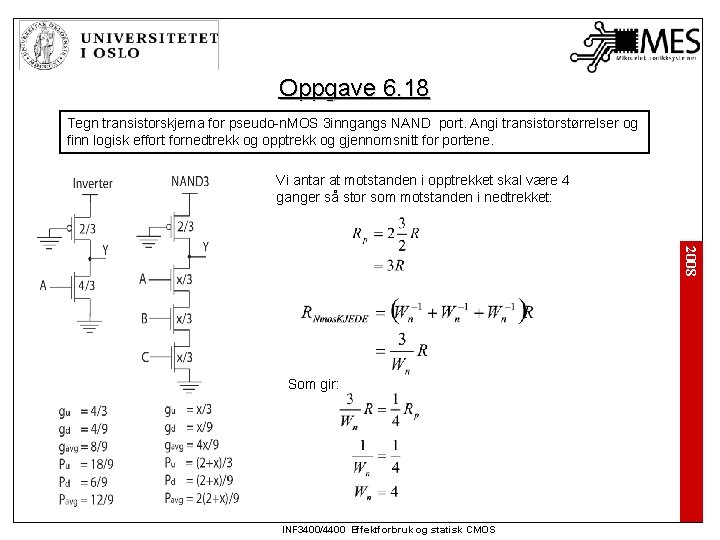

Oppgave 6. 18 Tegn transistorskjema for pseudo-n. MOS 3 inngangs NAND port. Angi transistorstørrelser og finn logisk effort fornedtrekk og opptrekk og gjennomsnitt for portene. Vi antar at motstanden i opptrekket skal være 4 ganger så stor som motstanden i nedtrekket: 2008 Som gir: INF 3400/4400 Effektforbruk og statisk CMOS

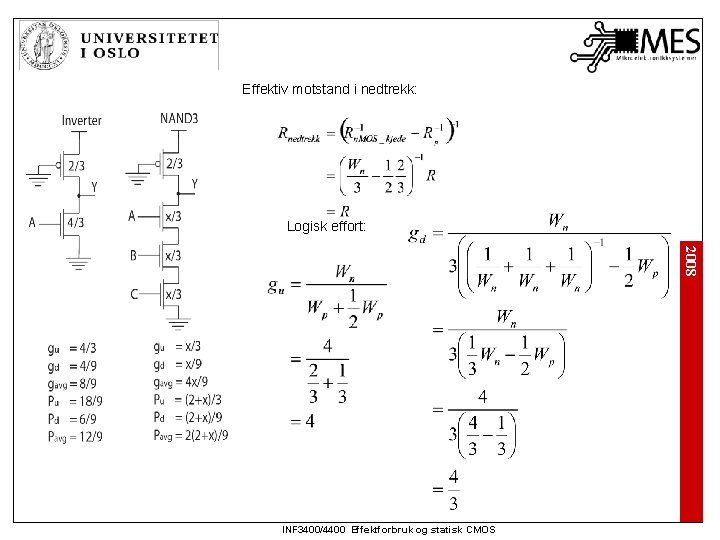

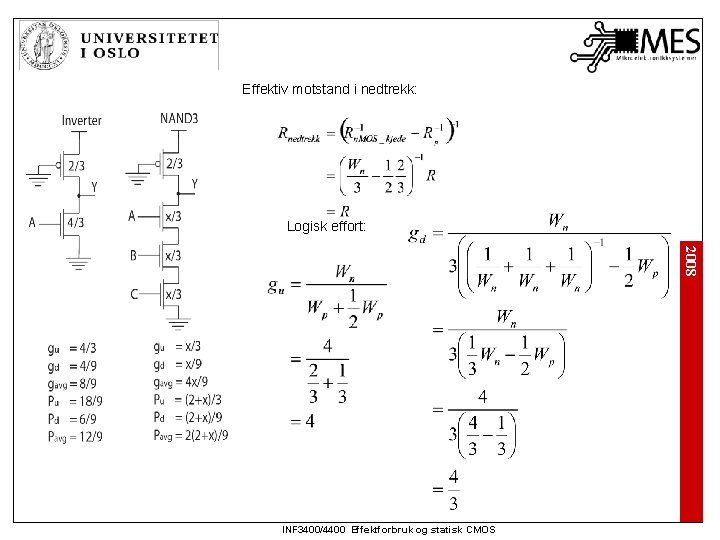

Effektiv motstand i nedtrekk: Logisk effort: 2008 INF 3400/4400 Effektforbruk og statisk CMOS

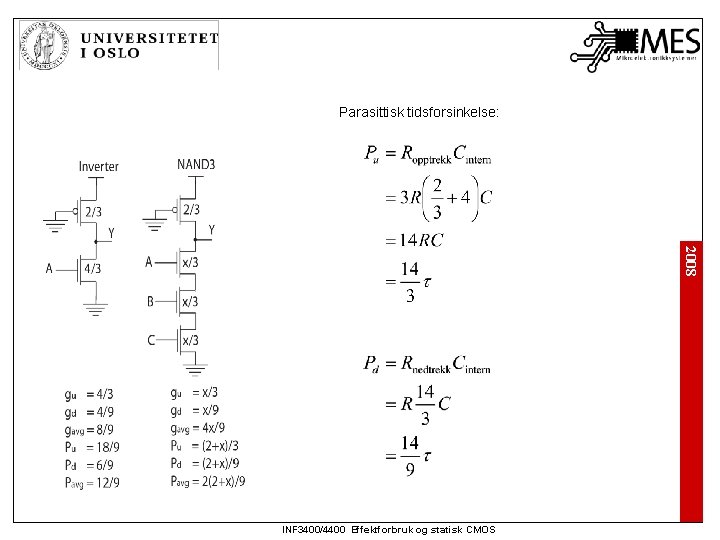

Parasittisk tidsforsinkelse: 2008 INF 3400/4400 Effektforbruk og statisk CMOS

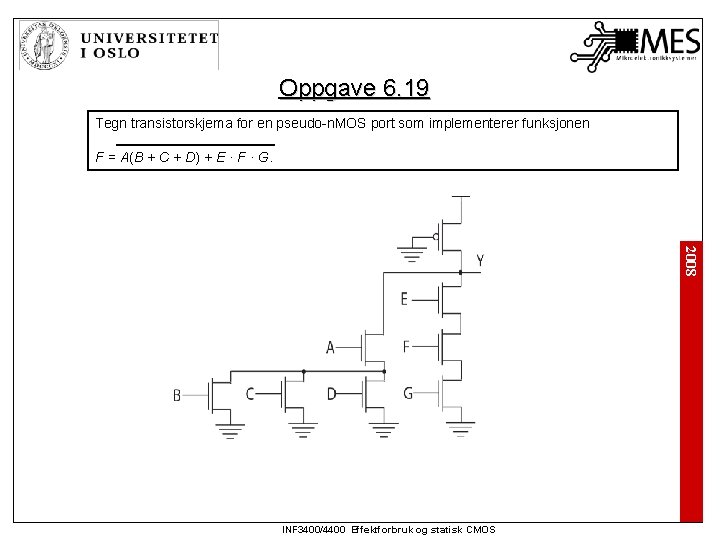

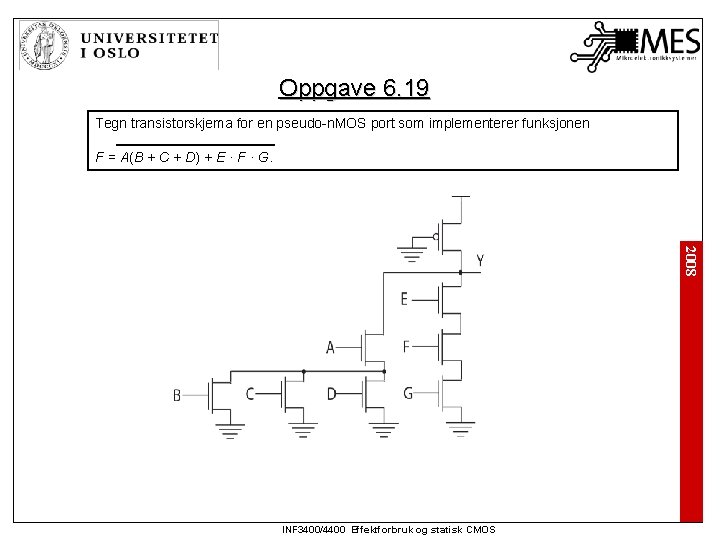

Oppgave 6. 19 Tegn transistorskjema for en pseudo-n. MOS port som implementerer funksjonen F = A(B + C + D) + E · F · G. 2008 INF 3400/4400 Effektforbruk og statisk CMOS

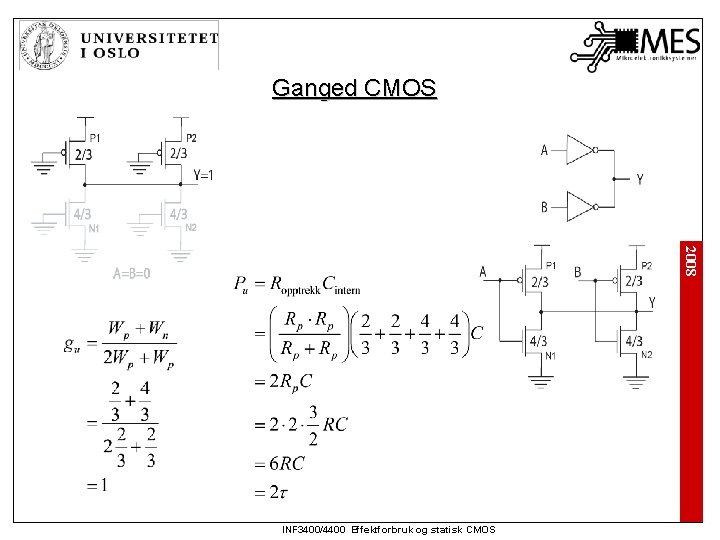

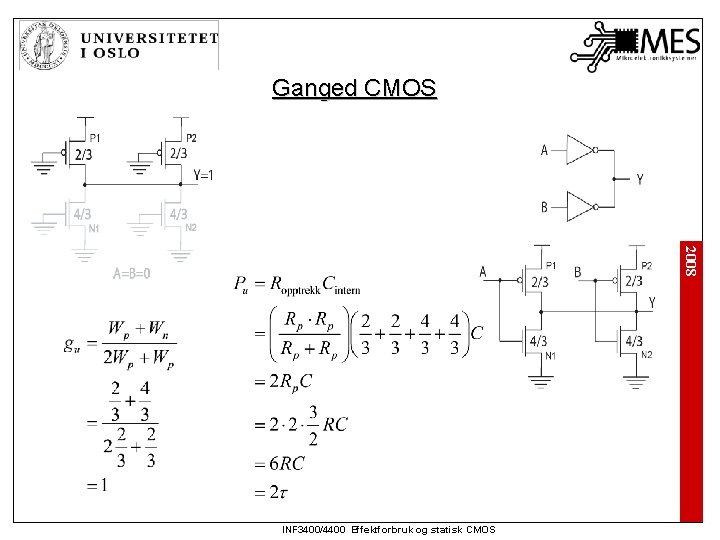

Ganged CMOS 2008 INF 3400/4400 Effektforbruk og statisk CMOS

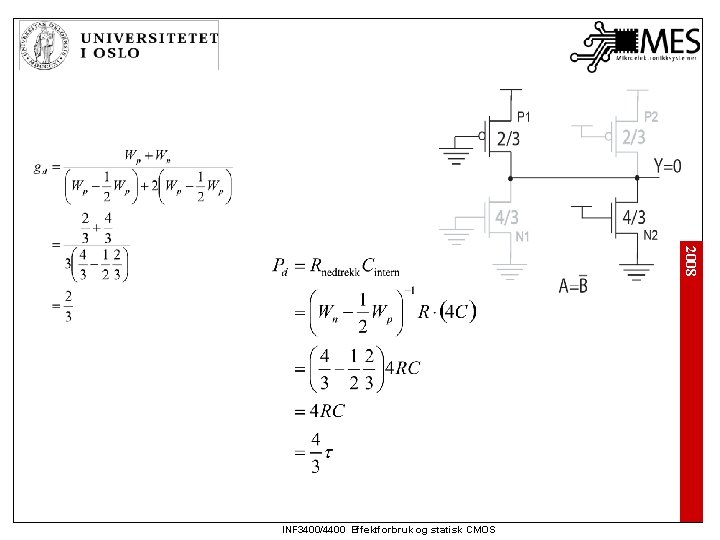

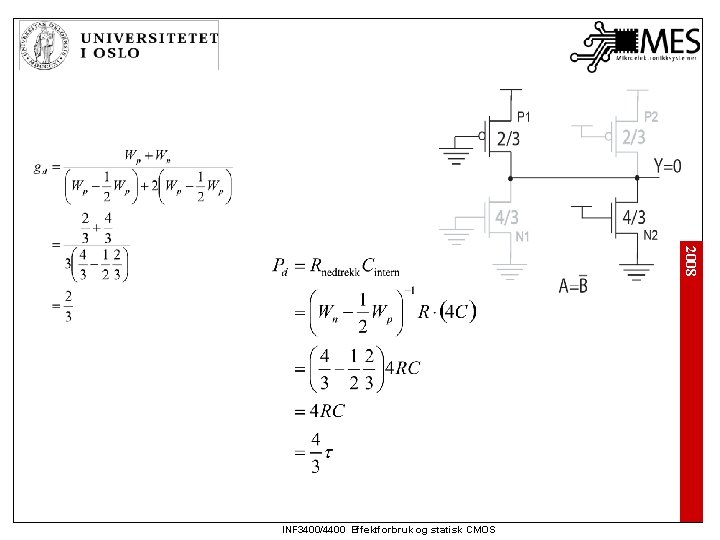

2008 INF 3400/4400 Effektforbruk og statisk CMOS

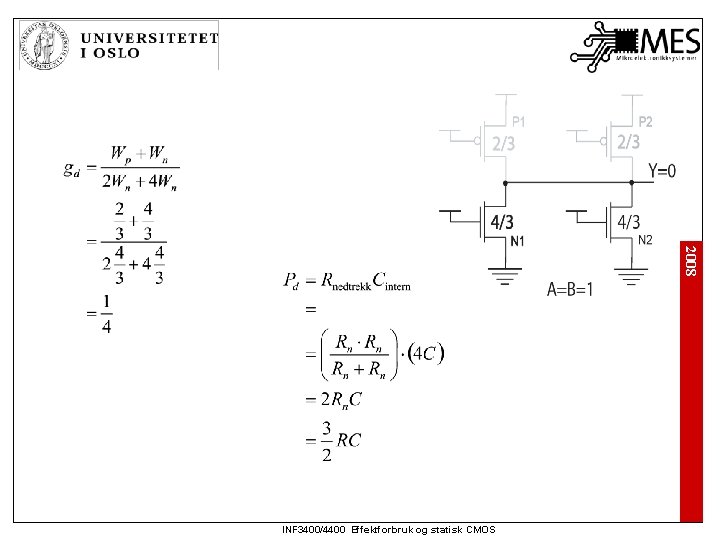

2008 INF 3400/4400 Effektforbruk og statisk CMOS

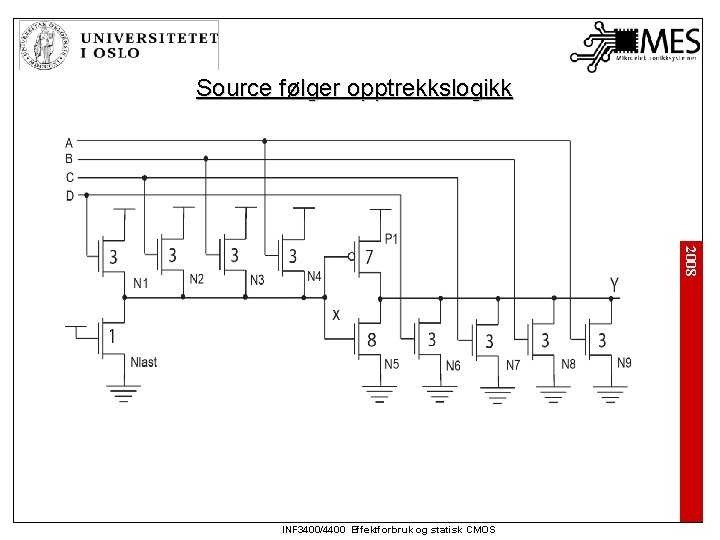

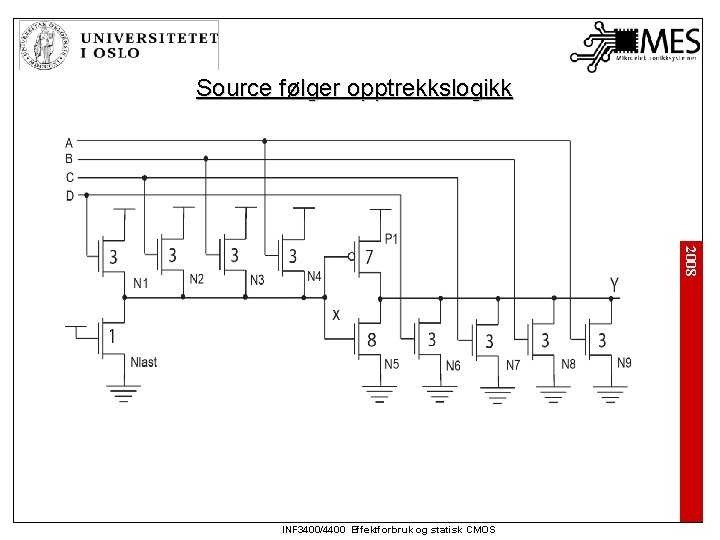

Source følger opptrekkslogikk 2008 INF 3400/4400 Effektforbruk og statisk CMOS

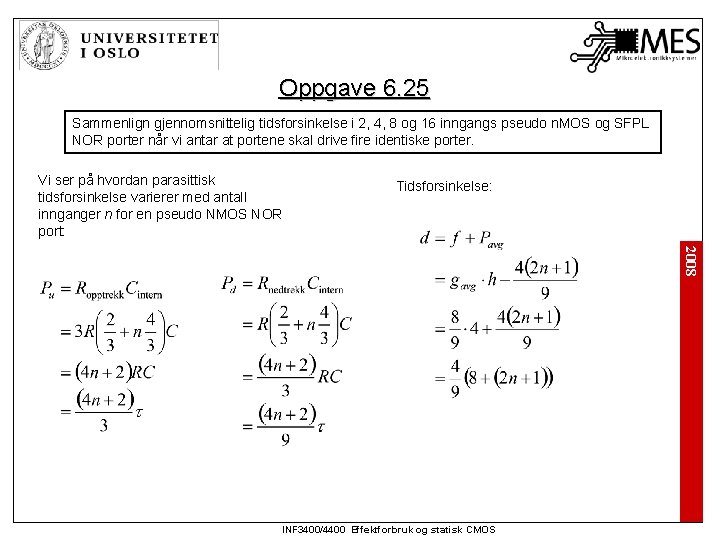

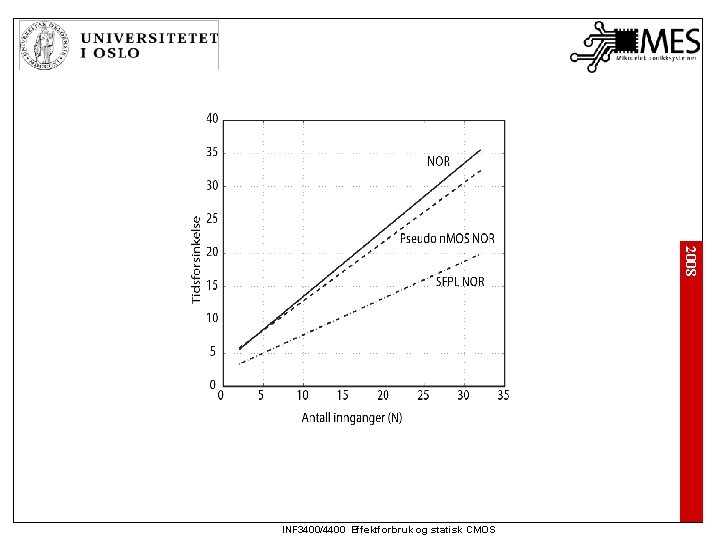

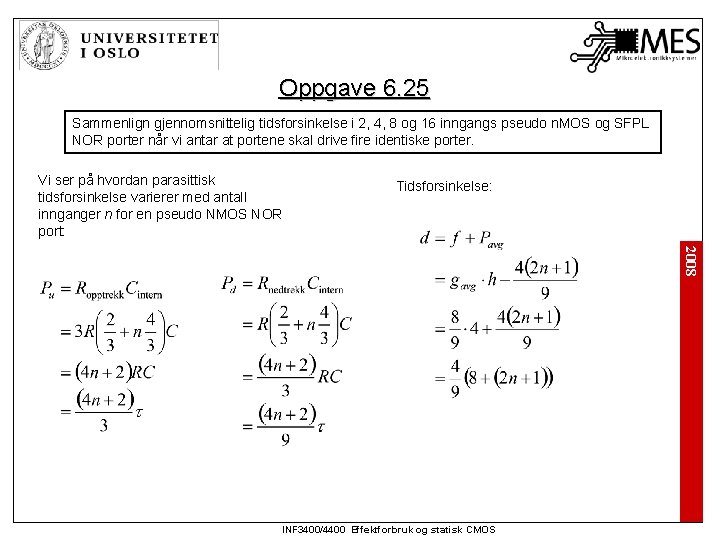

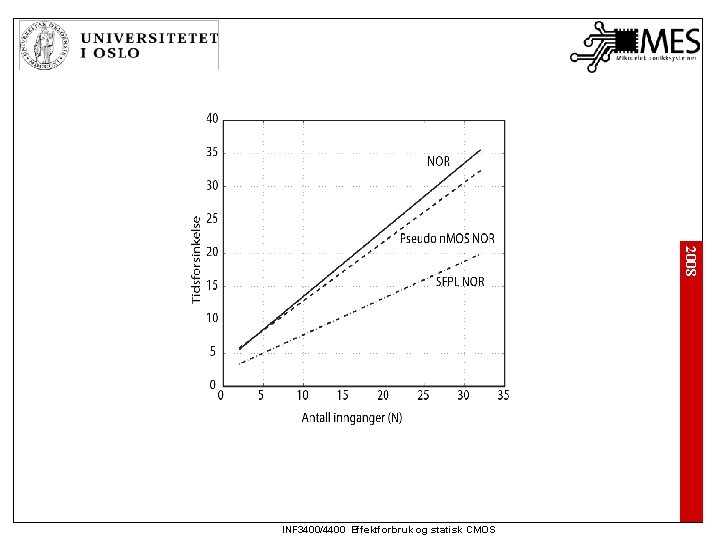

Oppgave 6. 25 Sammenlign gjennomsnittelig tidsforsinkelse i 2, 4, 8 og 16 inngangs pseudo n. MOS og SFPL NOR porter når vi antar at portene skal drive fire identiske porter. Vi ser på hvordan parasittisk tidsforsinkelse varierer med antall innganger n for en pseudo NMOS NOR port: Tidsforsinkelse: 2008 INF 3400/4400 Effektforbruk og statisk CMOS

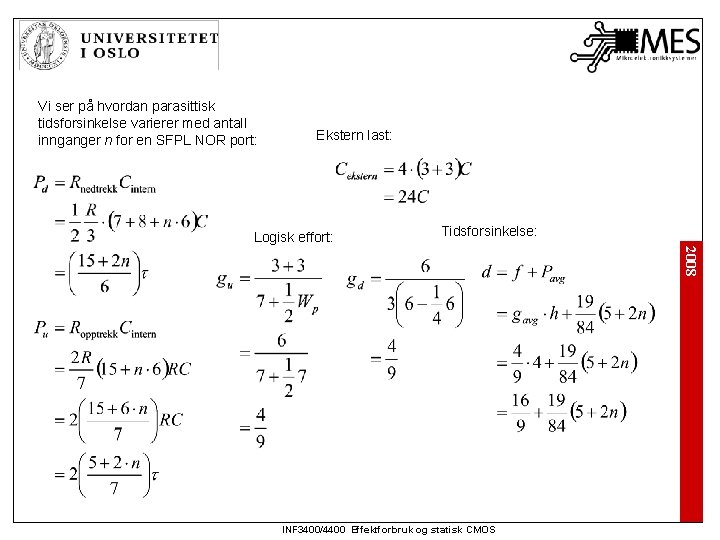

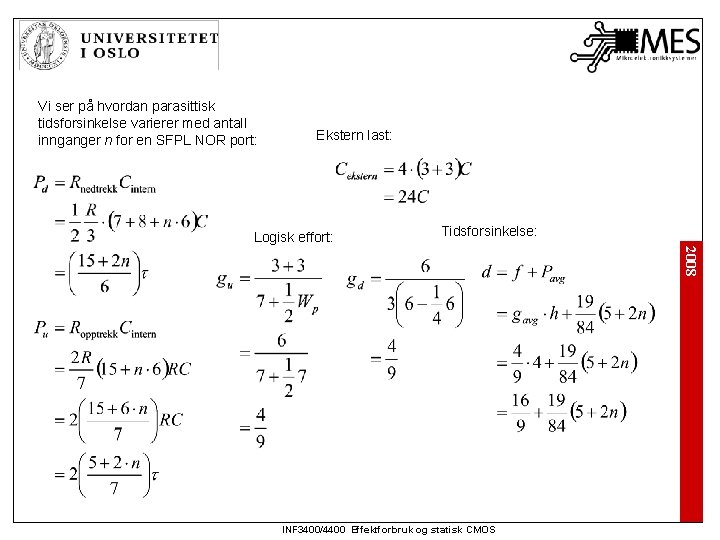

Vi ser på hvordan parasittisk tidsforsinkelse varierer med antall innganger n for en SFPL NOR port: Ekstern last: Logisk effort: Tidsforsinkelse: 2008 INF 3400/4400 Effektforbruk og statisk CMOS

2008 INF 3400/4400 Effektforbruk og statisk CMOS

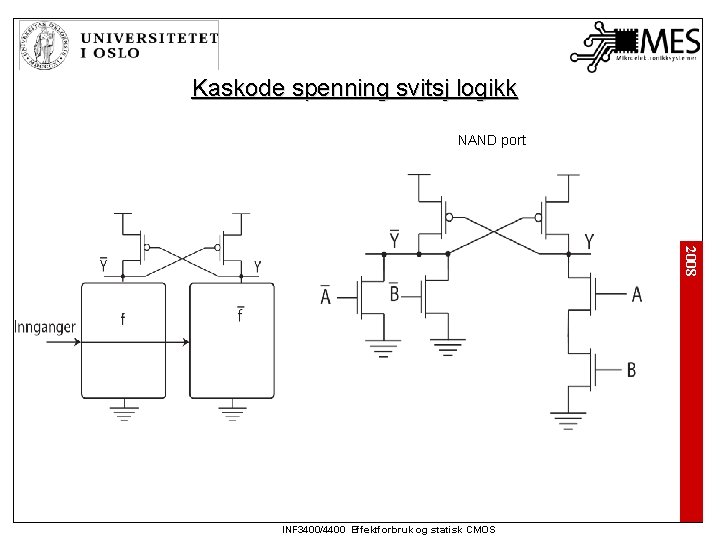

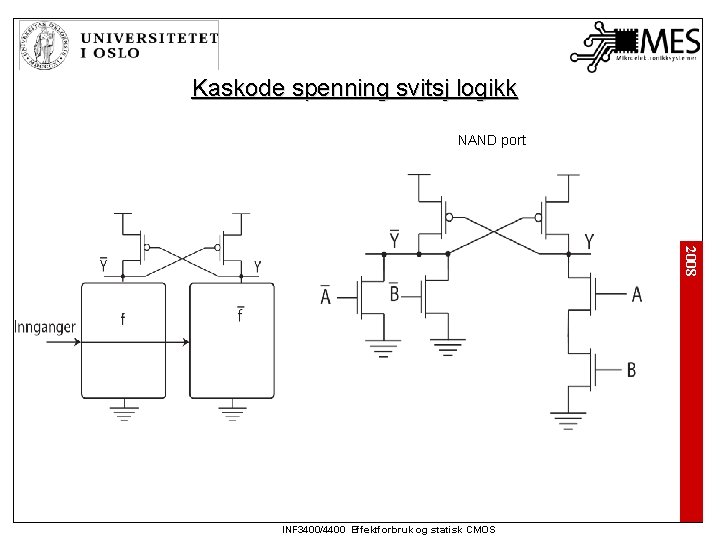

Kaskode spenning svitsj logikk NAND port 2008 INF 3400/4400 Effektforbruk og statisk CMOS

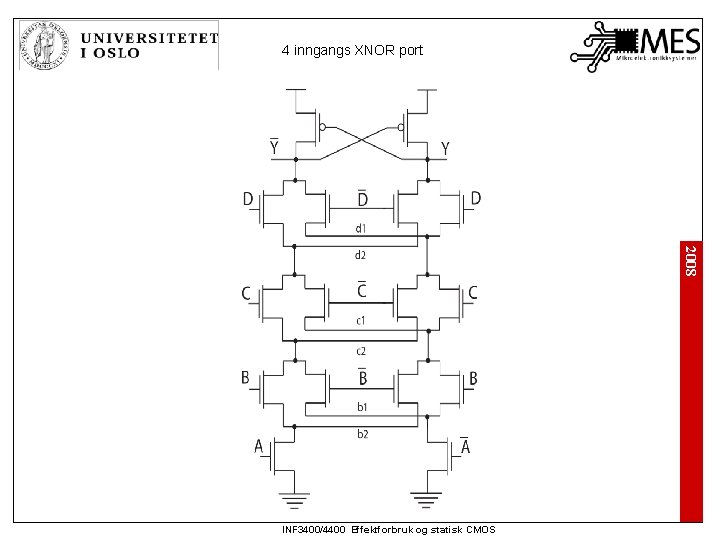

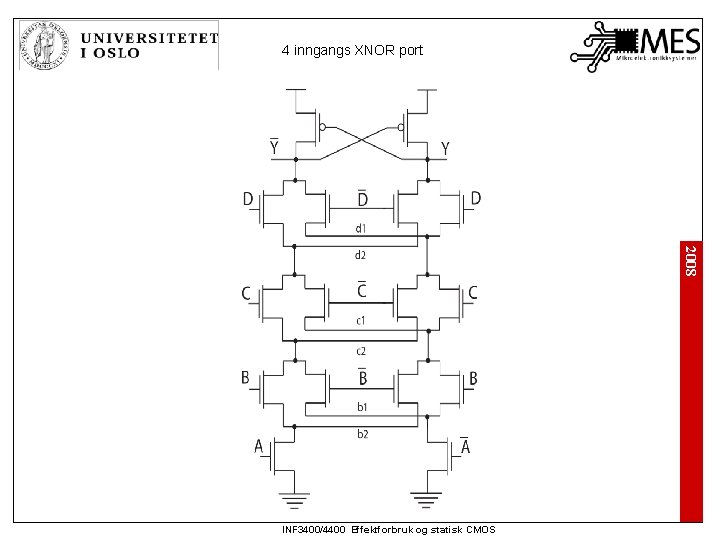

4 inngangs XNOR port 2008 INF 3400/4400 Effektforbruk og statisk CMOS

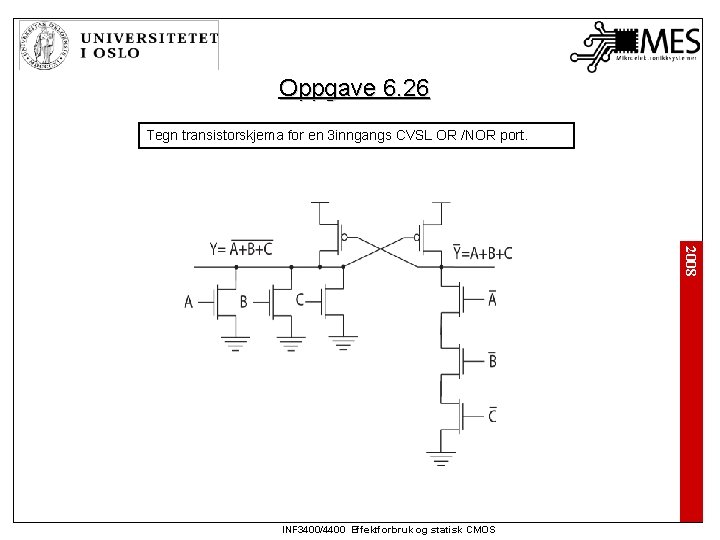

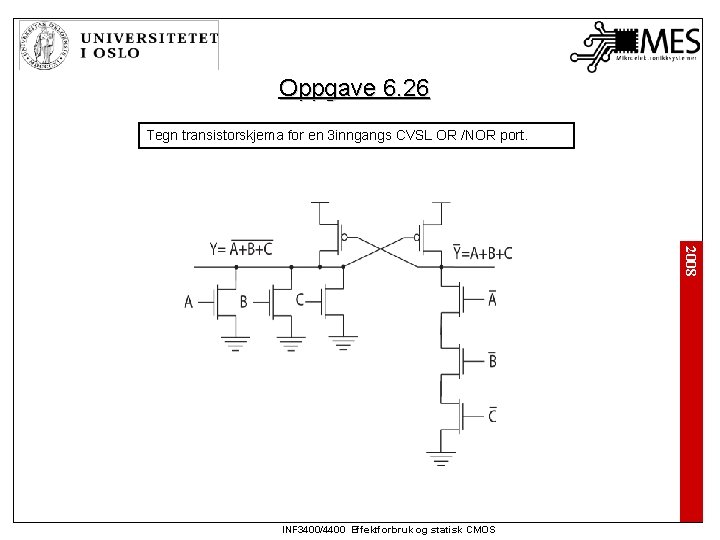

Oppgave 6. 26 Tegn transistorskjema for en 3 inngangs CVSL OR /NOR port. 2008 INF 3400/4400 Effektforbruk og statisk CMOS