Superescalares Scheduling esttico Introduccin La CPU ejecuta las

- Slides: 29

Superescalares Scheduling estático

Introducción La CPU ejecuta las instrucciones en orden. El compilador: Puede cambiar el orden de ejecución. Genera el paquete de emisión. Trata de prevenir o reducir los peligros de datos y de control. Paquete de emisión (issue packet): el conjunto de instrucciones que se emiten juntas en un ciclo de reloj. Universidad de Sonora Arquitectura de Computadoras 2

Introducción La mayoría de CPUs móviles (tipo ARM) son superescalares con scheduling estático. Universidad de Sonora Arquitectura de Computadoras 3

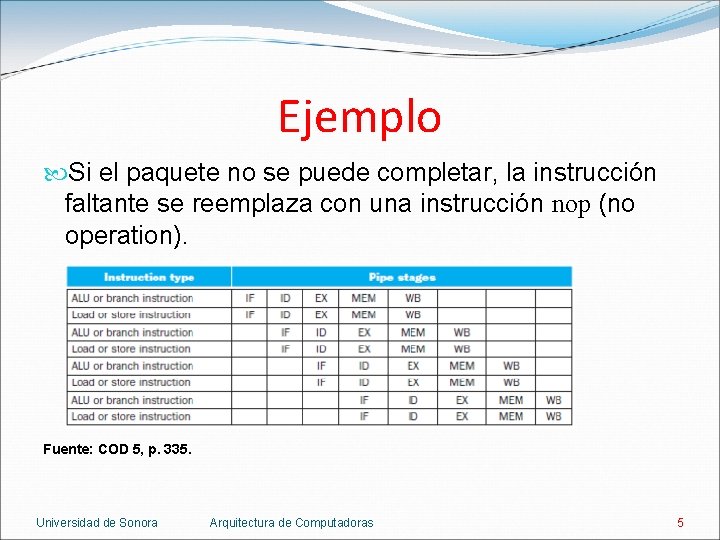

Ejemplo Considerar una CPU MIPS superescalar con scheduling estático y doble emisión. Limitación: solo una instrucción puede ser de tipo R o brinco y la otra puede ser una carga o un store. El paquete de emisión tiene 8 bytes (2 instrucciones). La instrucción R o de brinco se pone primero y luego la instrucción de memoria. Universidad de Sonora Arquitectura de Computadoras 4

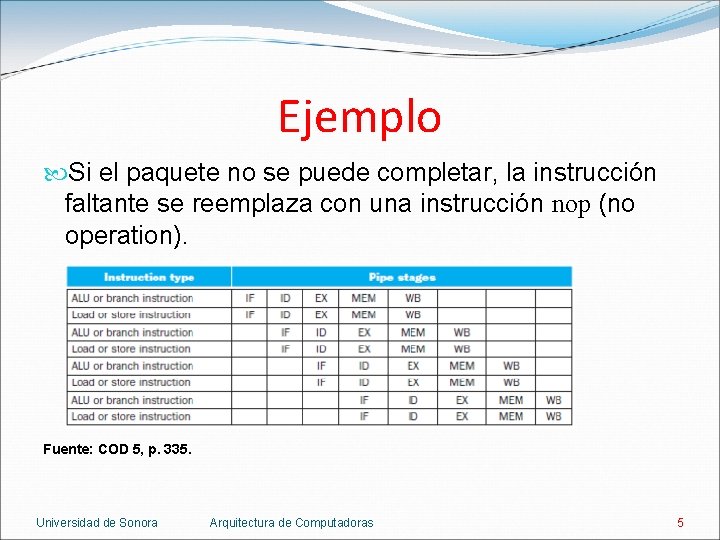

Ejemplo Si el paquete no se puede completar, la instrucción faltante se reemplaza con una instrucción nop (no operation). Fuente: COD 5, p. 335. Universidad de Sonora Arquitectura de Computadoras 5

Peligros La forma de tratar los peligros depende de cada arquitectura. En algunas arquitecturas: El compilador quita todos los peligros insertando nops si es necesario. No hay detección de peligros por hardware ni detenciones (stalls). Universidad de Sonora Arquitectura de Computadoras 6

Peligros Por ejemplo, en una CPU con doble emisión el compilador convierte el siguiente código: add $t 0, $t 1, $t 2 # paquete i sub $t 3, $t 0, $t 4 # paquete i en: add $t 0, $t 1, $t 2 # paquete i nop # paquete i sub $t 3, $t 0, $t 4 # paquete i + 1 Universidad de Sonora Arquitectura de Computadoras 7

Peligros En otras arquitecturas: El hardware detecta peligros de datos verdaderos y genera detenciones entre dos paquetes de emisión. El compilador evita todas las dependencias entre cada instrucción dentro del mismo paquete de emisión. Universidad de Sonora Arquitectura de Computadoras 8

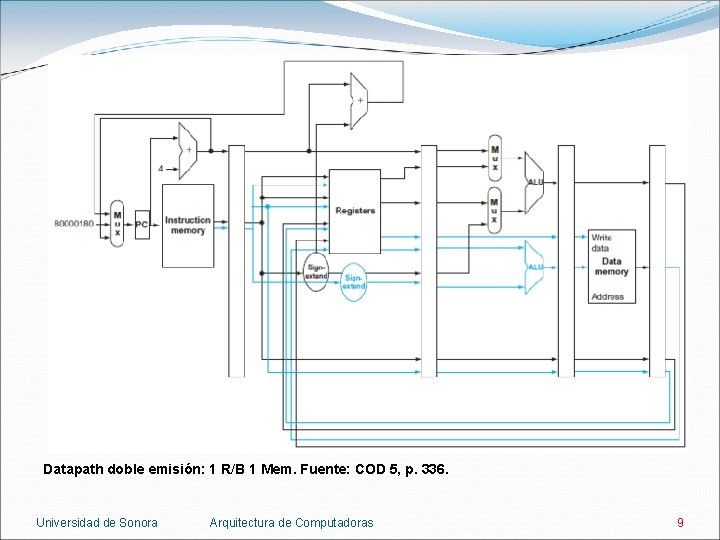

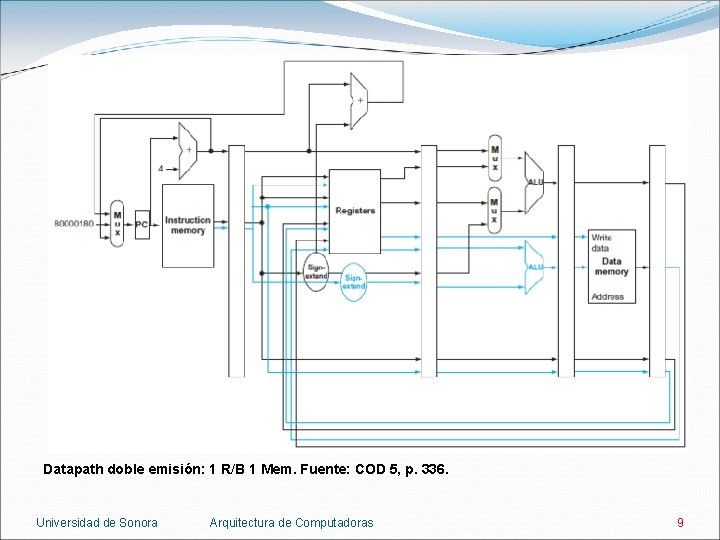

Datapath doble emisión: 1 R/B 1 Mem. Fuente: COD 5, p. 336. Universidad de Sonora Arquitectura de Computadoras 9

Explicación En cada ciclo se obtienen 2 instrucciones. En cada ciclo se leen hasta 4 registros: 2 de la instrucción R o beq. 1 de la instrucción lw o 2 de sw. Hay 2 ALUs: 1 para la instrucción R/beq. 1 para instrucción lw/sw. La memoria de datos no cambia (en cada ciclo solo hay máximo una instrucción de acceso a memoria). Universidad de Sonora Arquitectura de Computadoras 10

Explicación En cada ciclo hasta dos instrucciones necesitan escribir registros: Instrucciones R. Instrucciones lw. La carga sigue teniendo una latencia de uso de 1. El siguiente paquete de emisión a una carga no puede depender de su registro de destino. Universidad de Sonora Arquitectura de Computadoras 11

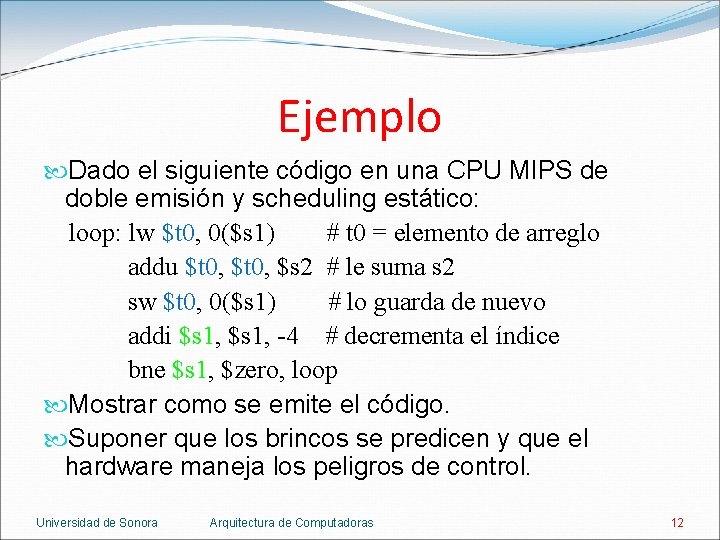

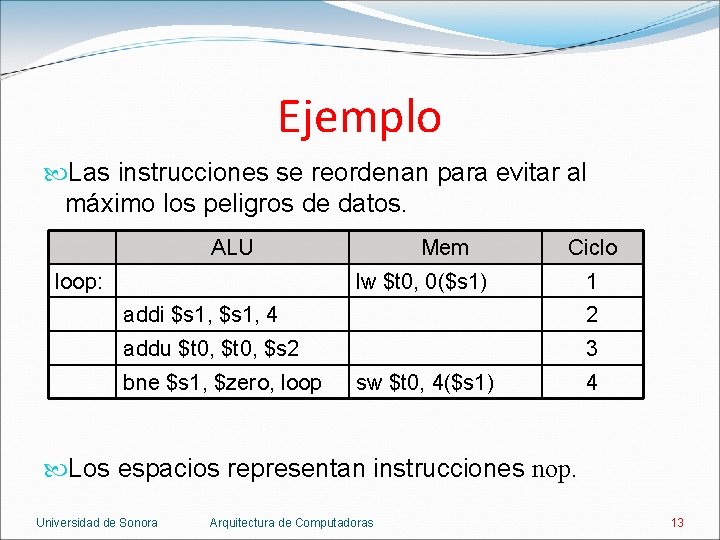

Ejemplo Dado el siguiente código en una CPU MIPS de doble emisión y scheduling estático: loop: lw $t 0, 0($s 1) # t 0 = elemento de arreglo addu $t 0, $s 2 # le suma s 2 sw $t 0, 0($s 1) # lo guarda de nuevo addi $s 1, -4 # decrementa el índice bne $s 1, $zero, loop Mostrar como se emite el código. Suponer que los brincos se predicen y que el hardware maneja los peligros de control. Universidad de Sonora Arquitectura de Computadoras 12

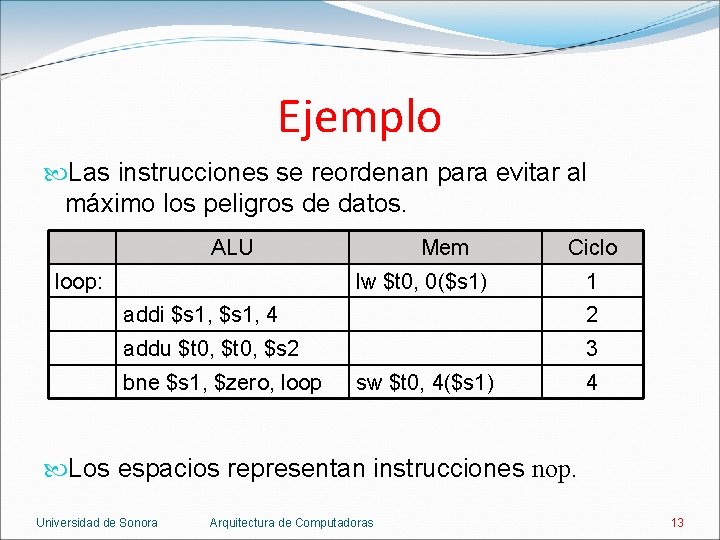

Ejemplo Las instrucciones se reordenan para evitar al máximo los peligros de datos. ALU loop: Mem Ciclo lw $t 0, 0($s 1) 1 addi $s 1, 4 2 addu $t 0, $s 2 3 bne $s 1, $zero, loop sw $t 0, 4($s 1) 4 Los espacios representan instrucciones nop. Universidad de Sonora Arquitectura de Computadoras 13

Ejemplo Las 5 instrucciones se ejecutan en 4 ciclos. CPI = 0. 8 IPC = 1. 25 Lo ideal es CPI = 0. 5 y, por lo tanto, IPC = 2. Importante: los nops no se cuentan. Universidad de Sonora Arquitectura de Computadoras 14

Loop unrolling Técnica de compilación que consiste en extender (desenrollar) un ciclo. De esta forma se pueden emitir juntas instrucciones de distintas iteraciones. Universidad de Sonora Arquitectura de Computadoras 15

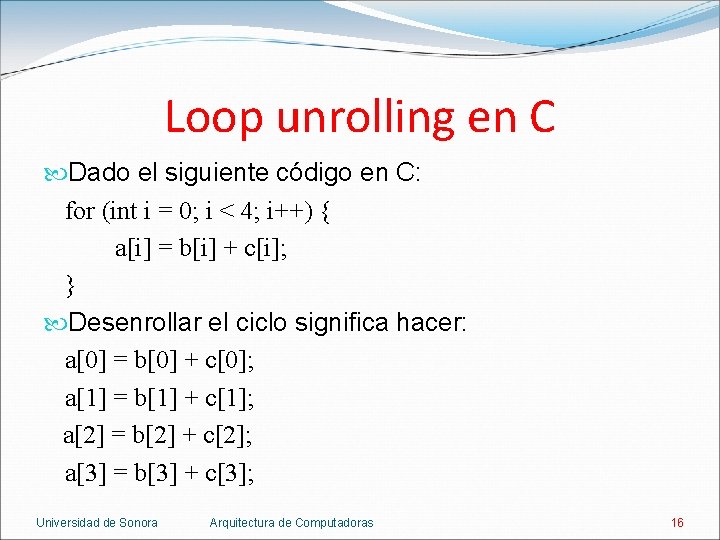

Loop unrolling en C Dado el siguiente código en C: for (int i = 0; i < 4; i++) { a[i] = b[i] + c[i]; } Desenrollar el ciclo significa hacer: a[0] = b[0] + c[0]; a[1] = b[1] + c[1]; a[2] = b[2] + c[2]; a[3] = b[3] + c[3]; Universidad de Sonora Arquitectura de Computadoras 16

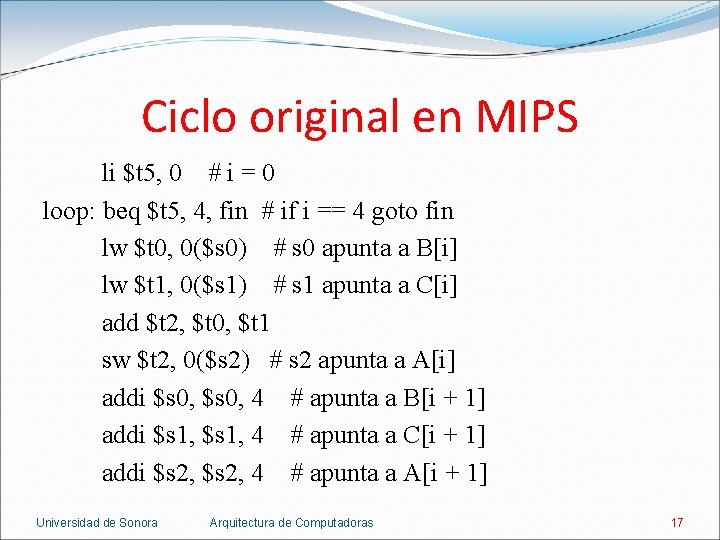

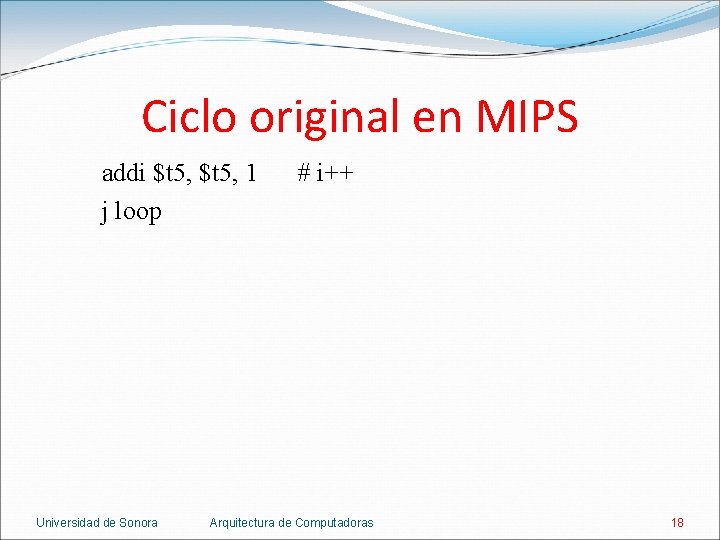

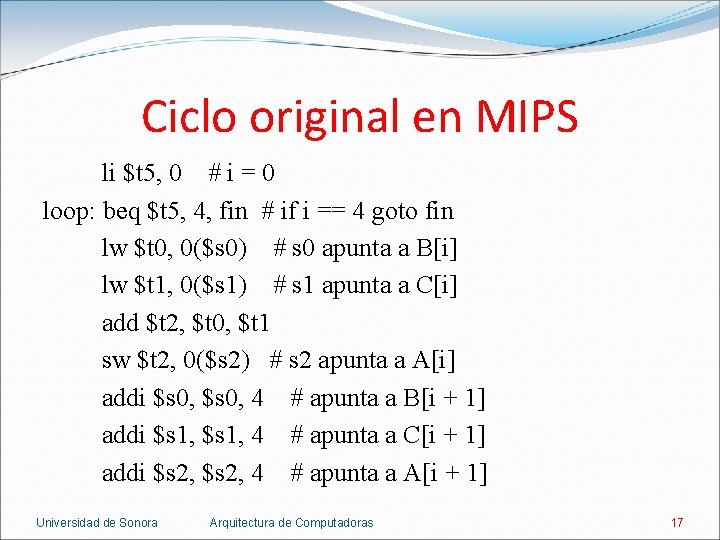

Ciclo original en MIPS li $t 5, 0 # i = 0 loop: beq $t 5, 4, fin # if i == 4 goto fin lw $t 0, 0($s 0) # s 0 apunta a B[i] lw $t 1, 0($s 1) # s 1 apunta a C[i] add $t 2, $t 0, $t 1 sw $t 2, 0($s 2) # s 2 apunta a A[i] addi $s 0, 4 # apunta a B[i + 1] addi $s 1, 4 # apunta a C[i + 1] addi $s 2, 4 # apunta a A[i + 1] Universidad de Sonora Arquitectura de Computadoras 17

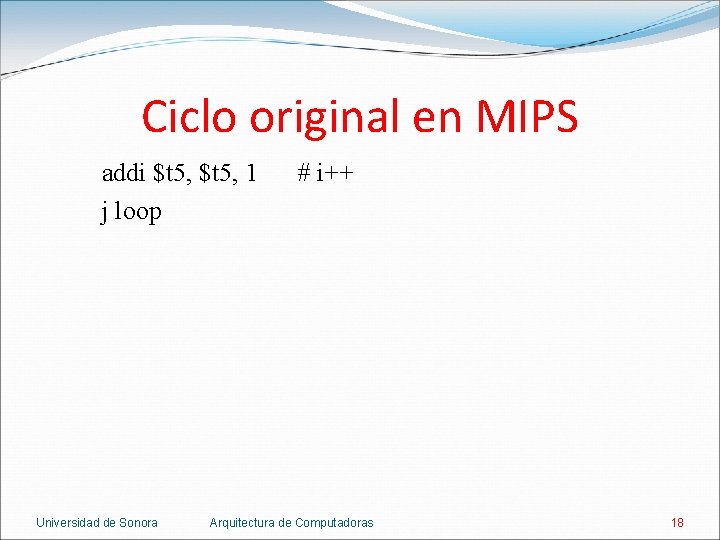

Ciclo original en MIPS addi $t 5, 1 j loop Universidad de Sonora # i++ Arquitectura de Computadoras 18

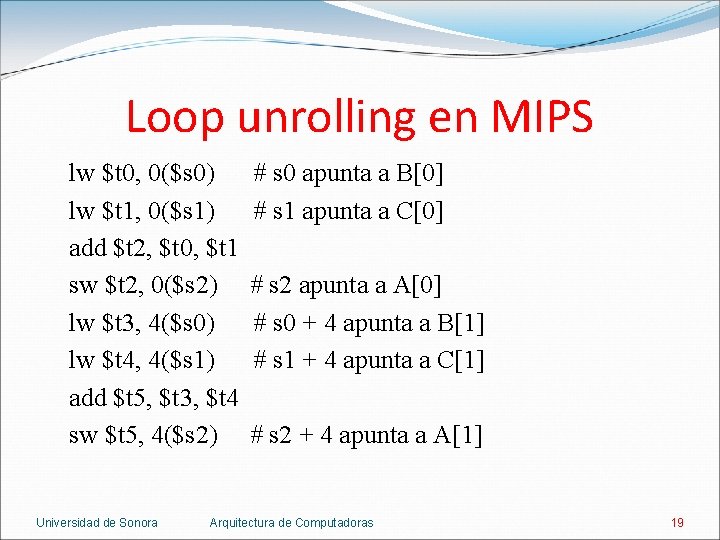

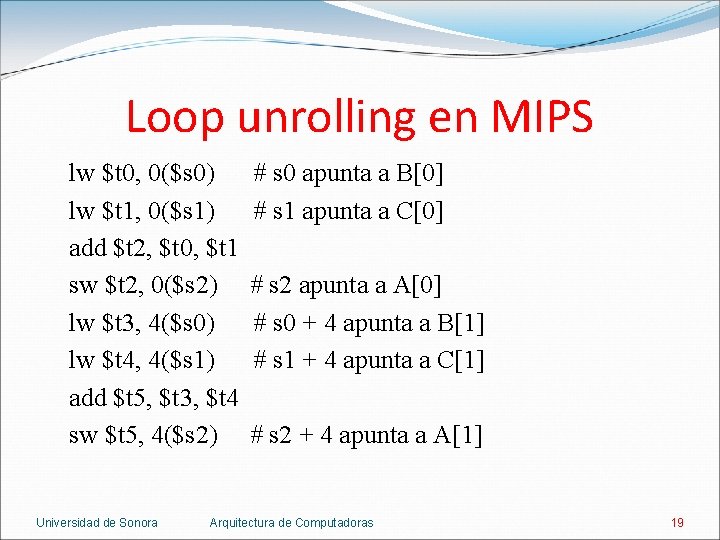

Loop unrolling en MIPS lw $t 0, 0($s 0) lw $t 1, 0($s 1) add $t 2, $t 0, $t 1 sw $t 2, 0($s 2) lw $t 3, 4($s 0) lw $t 4, 4($s 1) add $t 5, $t 3, $t 4 sw $t 5, 4($s 2) Universidad de Sonora # s 0 apunta a B[0] # s 1 apunta a C[0] # s 2 apunta a A[0] # s 0 + 4 apunta a B[1] # s 1 + 4 apunta a C[1] # s 2 + 4 apunta a A[1] Arquitectura de Computadoras 19

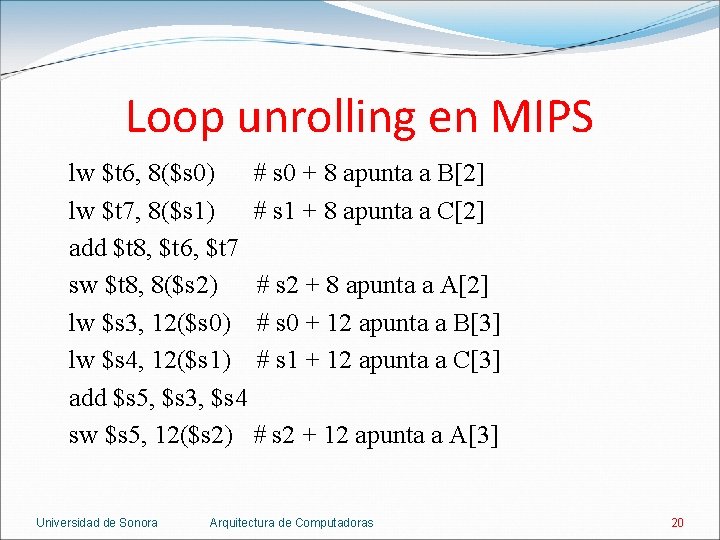

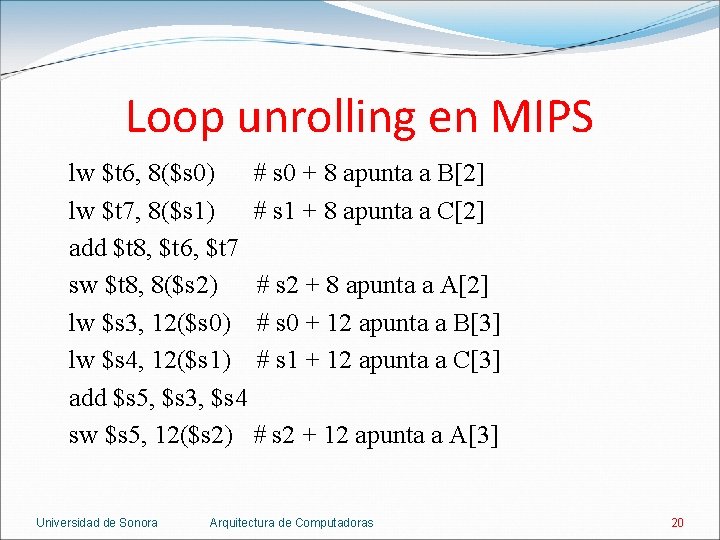

Loop unrolling en MIPS lw $t 6, 8($s 0) # s 0 + 8 apunta a B[2] lw $t 7, 8($s 1) # s 1 + 8 apunta a C[2] add $t 8, $t 6, $t 7 sw $t 8, 8($s 2) # s 2 + 8 apunta a A[2] lw $s 3, 12($s 0) # s 0 + 12 apunta a B[3] lw $s 4, 12($s 1) # s 1 + 12 apunta a C[3] add $s 5, $s 3, $s 4 sw $s 5, 12($s 2) # s 2 + 12 apunta a A[3] Universidad de Sonora Arquitectura de Computadoras 20

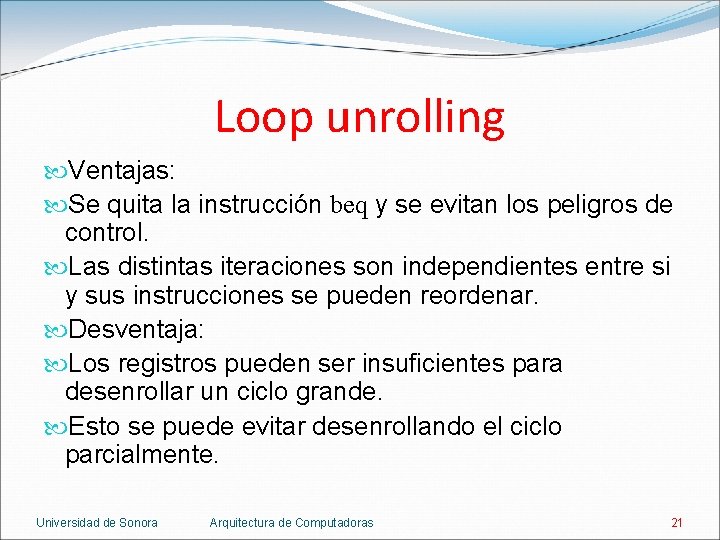

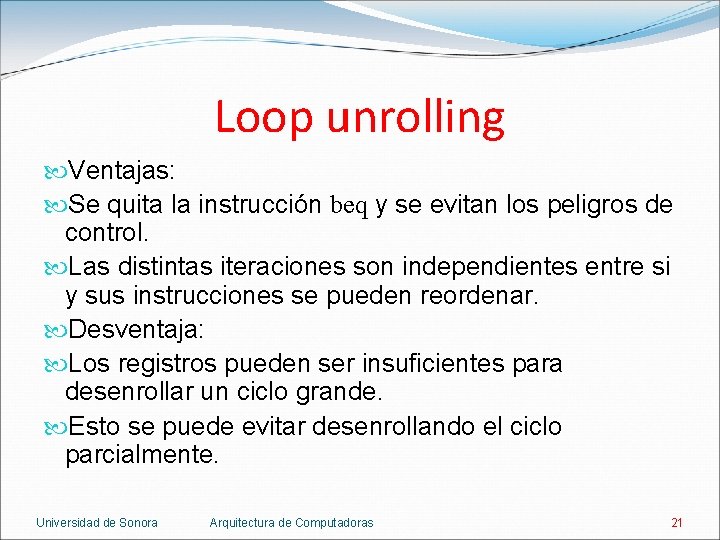

Loop unrolling Ventajas: Se quita la instrucción beq y se evitan los peligros de control. Las distintas iteraciones son independientes entre si y sus instrucciones se pueden reordenar. Desventaja: Los registros pueden ser insuficientes para desenrollar un ciclo grande. Esto se puede evitar desenrollando el ciclo parcialmente. Universidad de Sonora Arquitectura de Computadoras 21

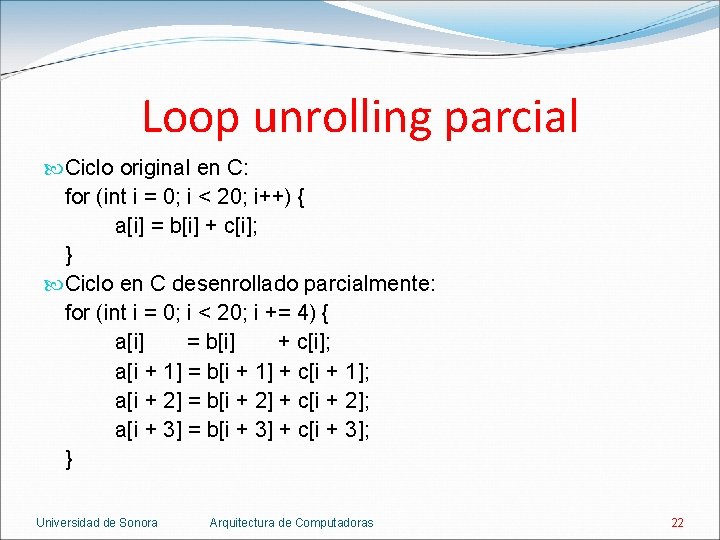

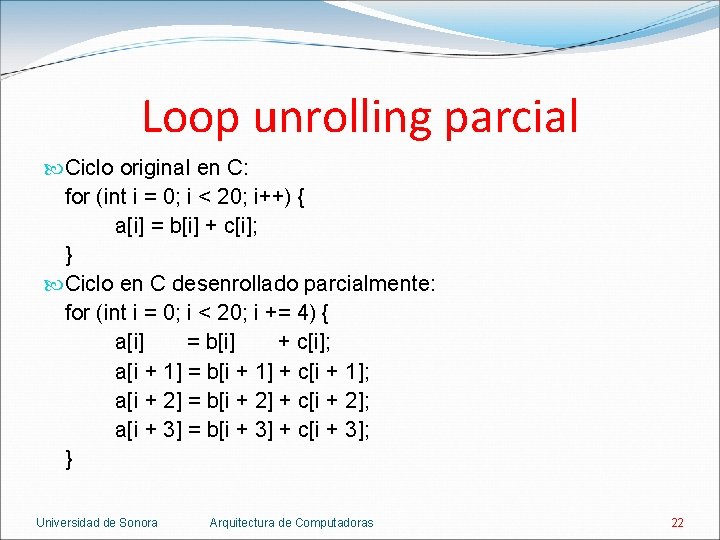

Loop unrolling parcial Ciclo original en C: for (int i = 0; i < 20; i++) { a[i] = b[i] + c[i]; } Ciclo en C desenrollado parcialmente: for (int i = 0; i < 20; i += 4) { a[i] = b[i] + c[i]; a[i + 1] = b[i + 1] + c[i + 1]; a[i + 2] = b[i + 2] + c[i + 2]; a[i + 3] = b[i + 3] + c[i + 3]; } Universidad de Sonora Arquitectura de Computadoras 22

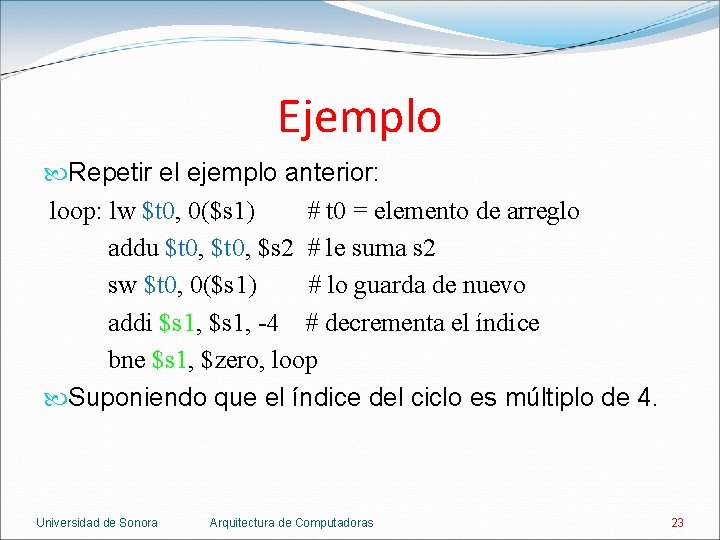

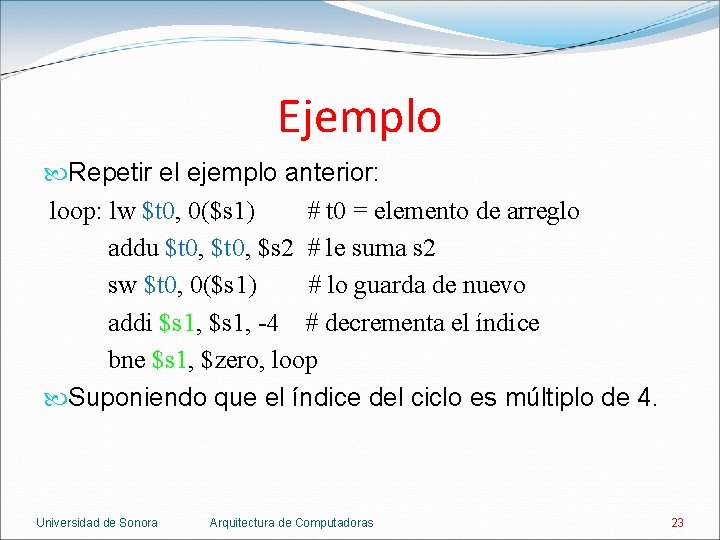

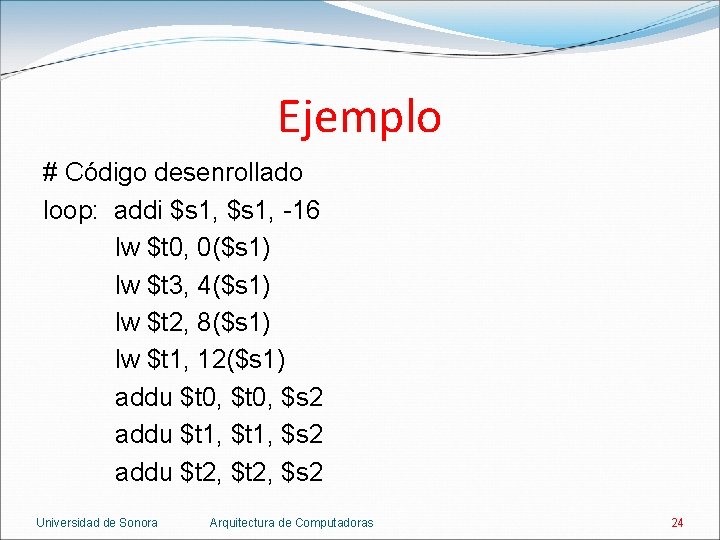

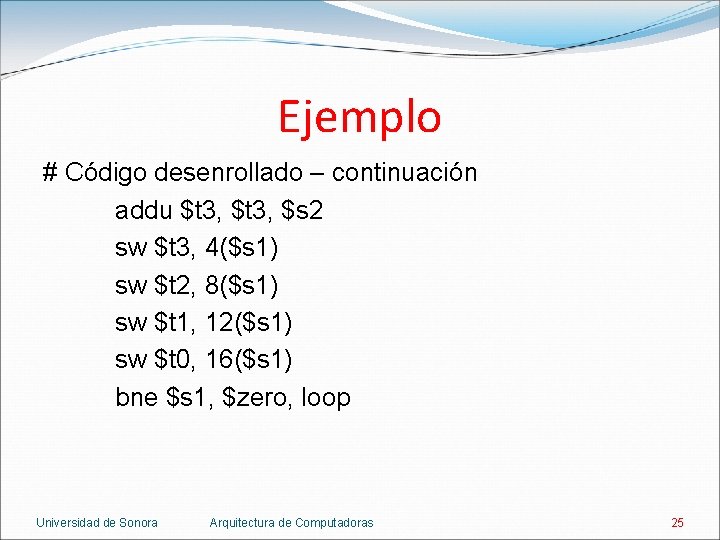

Ejemplo Repetir el ejemplo anterior: loop: lw $t 0, 0($s 1) # t 0 = elemento de arreglo addu $t 0, $s 2 # le suma s 2 sw $t 0, 0($s 1) # lo guarda de nuevo addi $s 1, -4 # decrementa el índice bne $s 1, $zero, loop Suponiendo que el índice del ciclo es múltiplo de 4. Universidad de Sonora Arquitectura de Computadoras 23

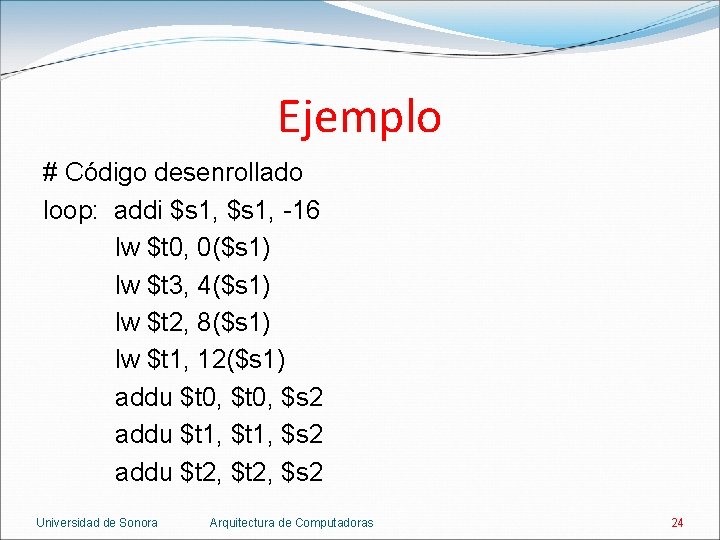

Ejemplo # Código desenrollado loop: addi $s 1, -16 lw $t 0, 0($s 1) lw $t 3, 4($s 1) lw $t 2, 8($s 1) lw $t 1, 12($s 1) addu $t 0, $s 2 addu $t 1, $s 2 addu $t 2, $s 2 Universidad de Sonora Arquitectura de Computadoras 24

Ejemplo # Código desenrollado – continuación addu $t 3, $s 2 sw $t 3, 4($s 1) sw $t 2, 8($s 1) sw $t 1, 12($s 1) sw $t 0, 16($s 1) bne $s 1, $zero, loop Universidad de Sonora Arquitectura de Computadoras 25

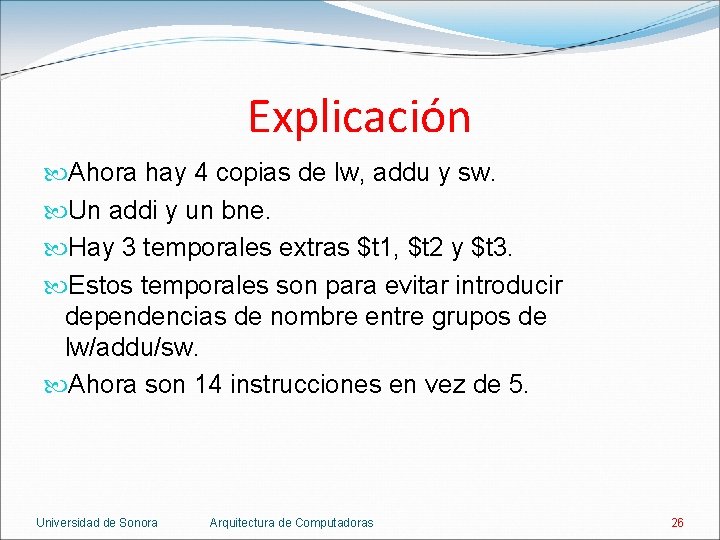

Explicación Ahora hay 4 copias de lw, addu y sw. Un addi y un bne. Hay 3 temporales extras $t 1, $t 2 y $t 3. Estos temporales son para evitar introducir dependencias de nombre entre grupos de lw/addu/sw. Ahora son 14 instrucciones en vez de 5. Universidad de Sonora Arquitectura de Computadoras 26

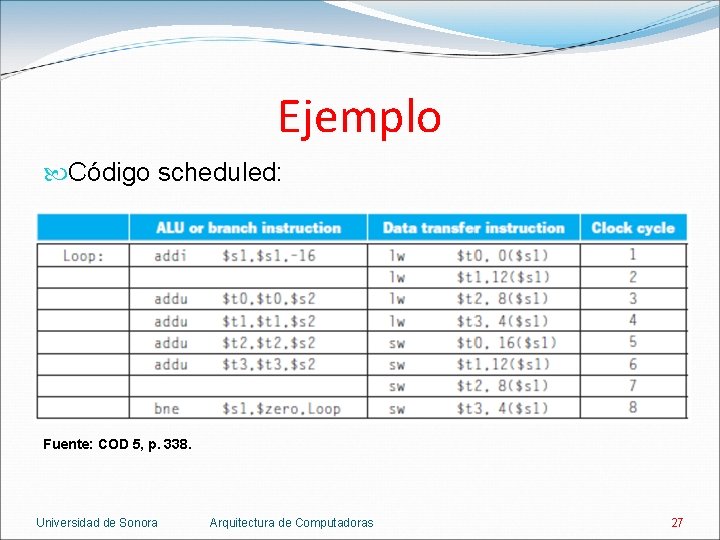

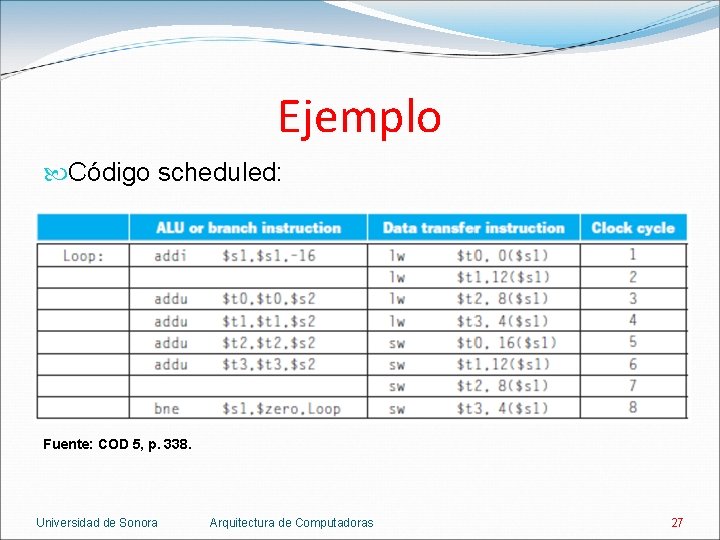

Ejemplo Código scheduled: Fuente: COD 5, p. 338. Universidad de Sonora Arquitectura de Computadoras 27

Explicación Las 14 instrucciones se ejecutan en 8 ciclos. CPI = 8 / 14 = 0. 57 IPC = 1. 75. El CPI está cerca del ideal de 0. 5. El costo es usar 4 registros temporales en vez de 1 y utilizar 14 instrucciones en vez de 5. Universidad de Sonora Arquitectura de Computadoras 28

Conclusiones Scheduling estático: Las instrucciones corren en el orden dictado por el compilador. Si los peligros no se detectan por hardware, el compilador debe hacerlo. Es más fácil de implementar que el scheduling dinámico. Se usa principalmente en CPUs móviles. Universidad de Sonora Arquitectura de Computadoras 29