Super FGD electronics Alain Blondel Margherita BuizzaAvanzini Olivier

Super. FGD electronics Alain Blondel, Margherita Buizza-Avanzini, Olivier Drapier, Yannick Favre, Franck Gastaldi, Michel Gonin, Etam Noah, Federico Sanchez … and many more to come. 25/07/2018 Alain Blondel for LLR+UNIGE teams 1

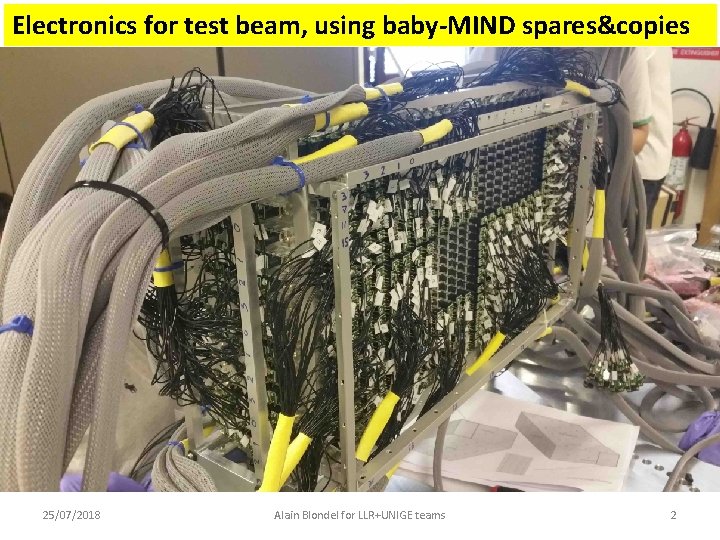

Electronics for test beam, using baby-MIND spares&copies 25/07/2018 Alain Blondel for LLR+UNIGE teams 2

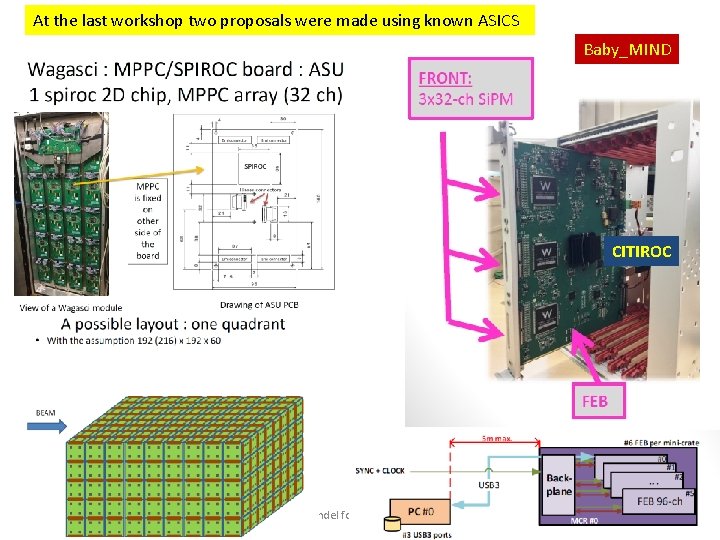

At the last workshop two proposals were made using known ASICS Baby_MIND CITIROC 25/07/2018 Alain Blondel for LLR+UNIGE teams 3

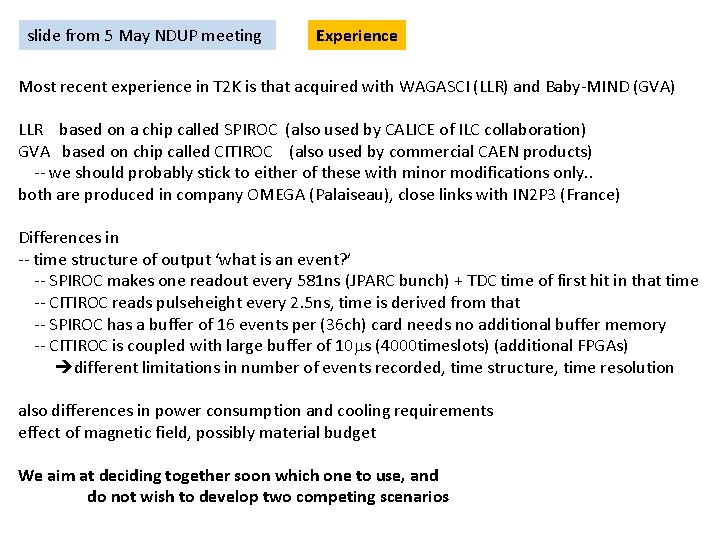

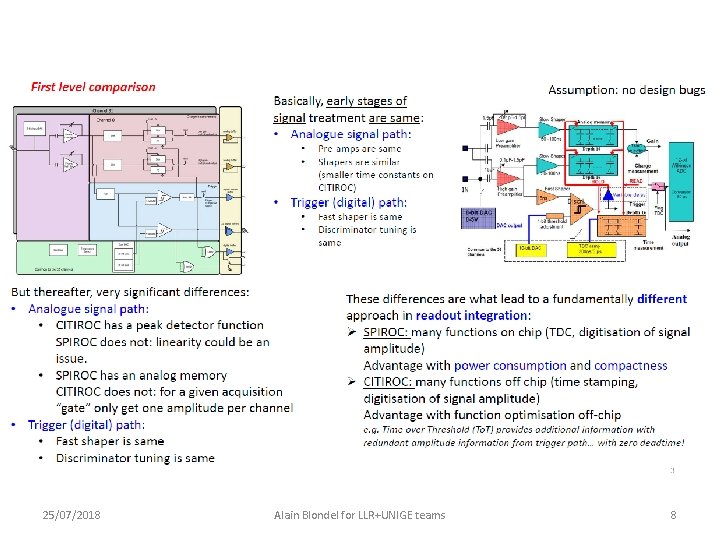

slide from 5 May NDUP meeting Experience Most recent experience in T 2 K is that acquired with WAGASCI (LLR) and Baby-MIND (GVA) LLR based on a chip called SPIROC (also used by CALICE of ILC collaboration) GVA based on chip called CITIROC (also used by commercial CAEN products) -- we should probably stick to either of these with minor modifications only. . both are produced in company OMEGA (Palaiseau), close links with IN 2 P 3 (France) Differences in -- time structure of output ‘what is an event? ’ -- SPIROC makes one readout every 581 ns (JPARC bunch) + TDC time of first hit in that time -- CITIROC reads pulseheight every 2. 5 ns, time is derived from that -- SPIROC has a buffer of 16 events per (36 ch) card needs no additional buffer memory -- CITIROC is coupled with large buffer of 10 s (4000 timeslots) (additional FPGAs) different limitations in number of events recorded, time structure, time resolution also differences in power consumption and cooling requirements effect of magnetic field, possibly material budget We aim at deciding together soon which one to use, and do not wish to develop two competing scenarios

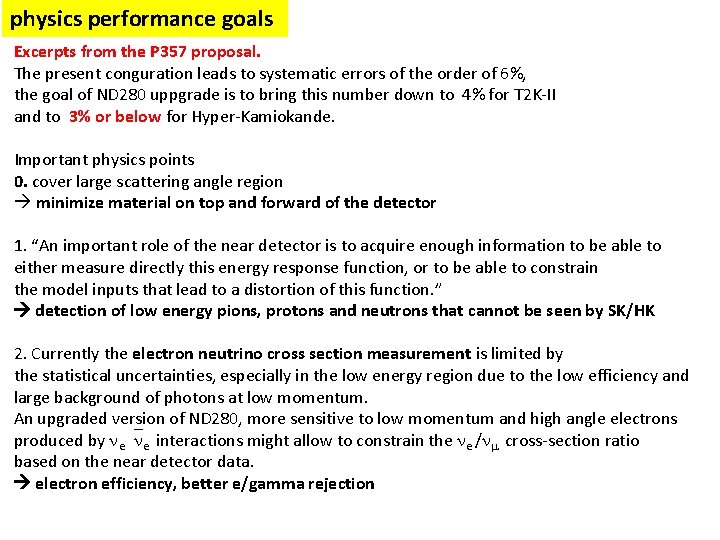

physics performance goals Excerpts from the P 357 proposal. The present conguration leads to systematic errors of the order of 6%, the goal of ND 280 uppgrade is to bring this number down to 4% for T 2 K-II and to 3% or below for Hyper-Kamiokande. Important physics points 0. cover large scattering angle region minimize material on top and forward of the detector 1. “An important role of the near detector is to acquire enough information to be able to either measure directly this energy response function, or to be able to constrain the model inputs that lead to a distortion of this function. ” detection of low energy pions, protons and neutrons that cannot be seen by SK/HK 2. Currently the electron neutrino cross section measurement is limited by the statistical uncertainties, especially in the low energy region due to the low efficiency and large background of photons at low momentum. An upgraded version of ND 280, more sensitive to low momentum and high angle electrons produced by e e interactions might allow to constrain the e / cross-section ratio based on the near detector data. electron efficiency, better e/gamma rejection

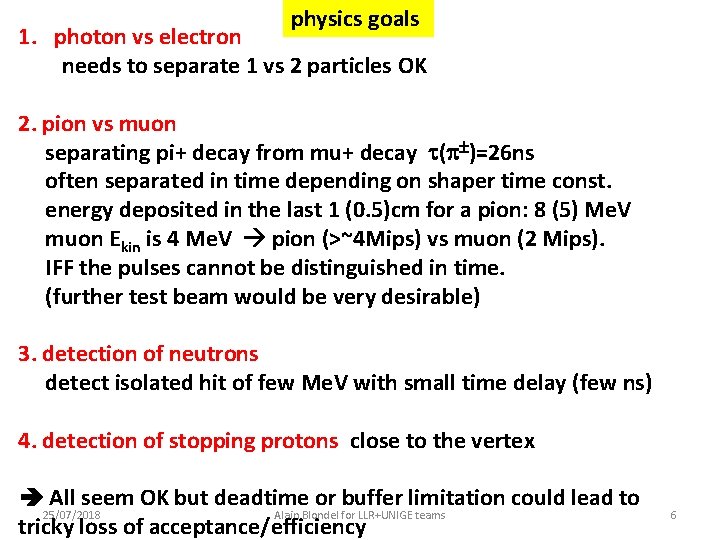

physics goals 1. photon vs electron needs to separate 1 vs 2 particles OK 2. pion vs muon separating pi+ decay from mu+ decay ( )=26 ns often separated in time depending on shaper time const. energy deposited in the last 1 (0. 5)cm for a pion: 8 (5) Me. V muon Ekin is 4 Me. V pion (>~4 Mips) vs muon (2 Mips). IFF the pulses cannot be distinguished in time. (further test beam would be very desirable) 3. detection of neutrons detect isolated hit of few Me. V with small time delay (few ns) 4. detection of stopping protons close to the vertex All seem OK but deadtime or buffer limitation could lead to 25/07/2018 Alain Blondel for LLR+UNIGE teams tricky loss of acceptance/efficiency 6

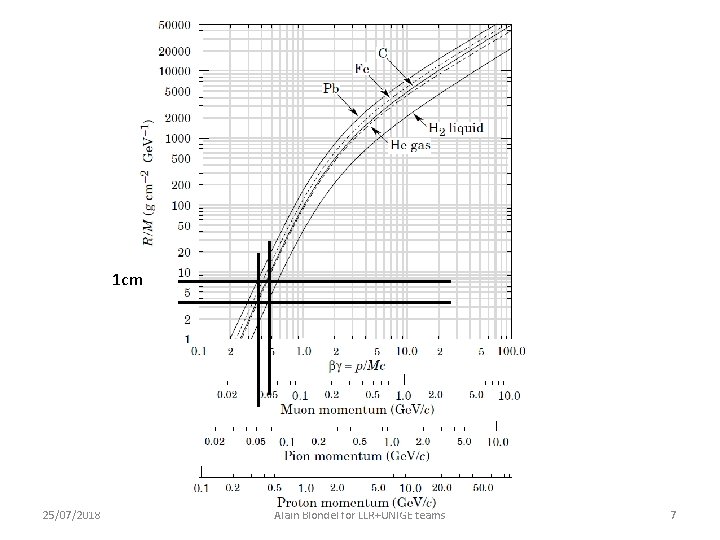

1 cm 25/07/2018 Alain Blondel for LLR+UNIGE teams 7

25/07/2018 Alain Blondel for LLR+UNIGE teams 8

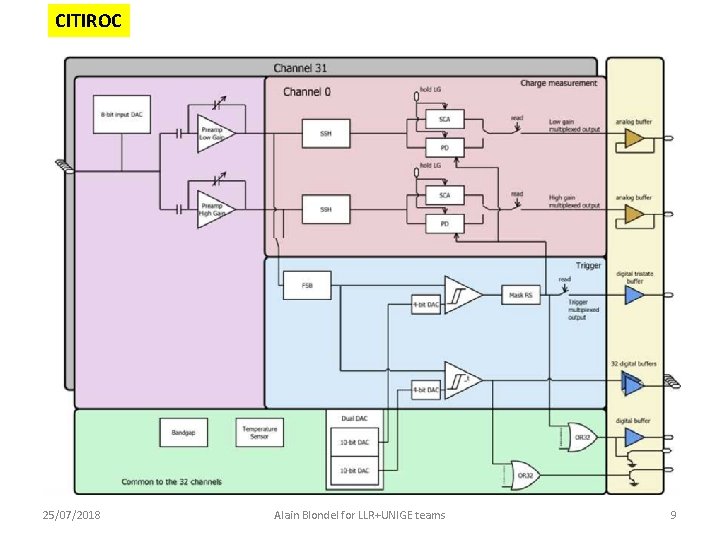

CITIROC 25/07/2018 Alain Blondel for LLR+UNIGE teams 9

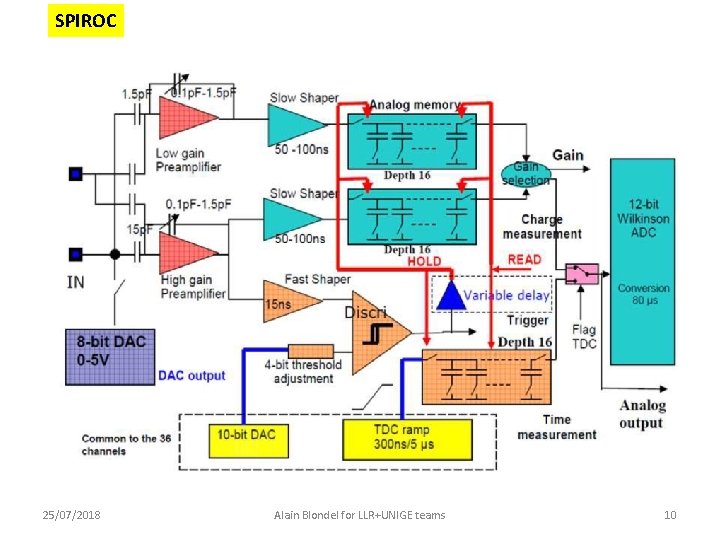

SPIROC 25/07/2018 Alain Blondel for LLR+UNIGE teams 10

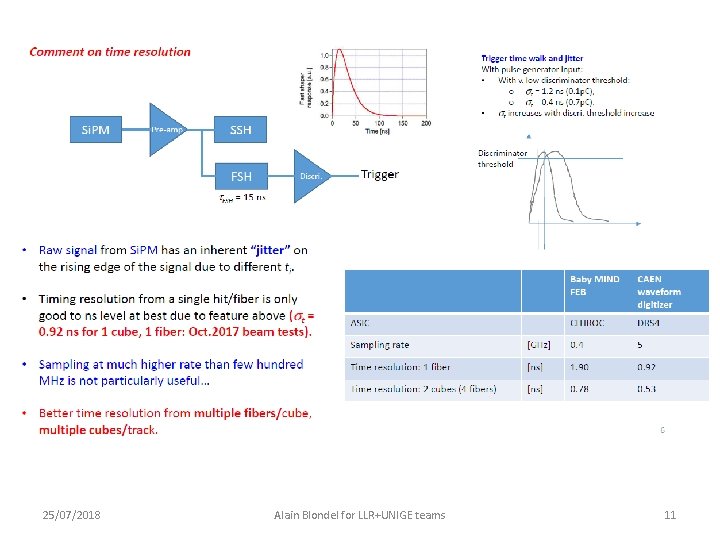

25/07/2018 Alain Blondel for LLR+UNIGE teams 11

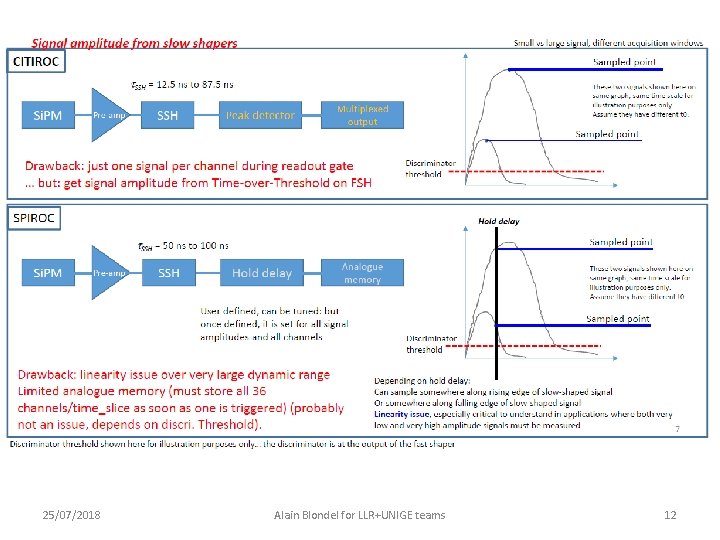

25/07/2018 Alain Blondel for LLR+UNIGE teams 12

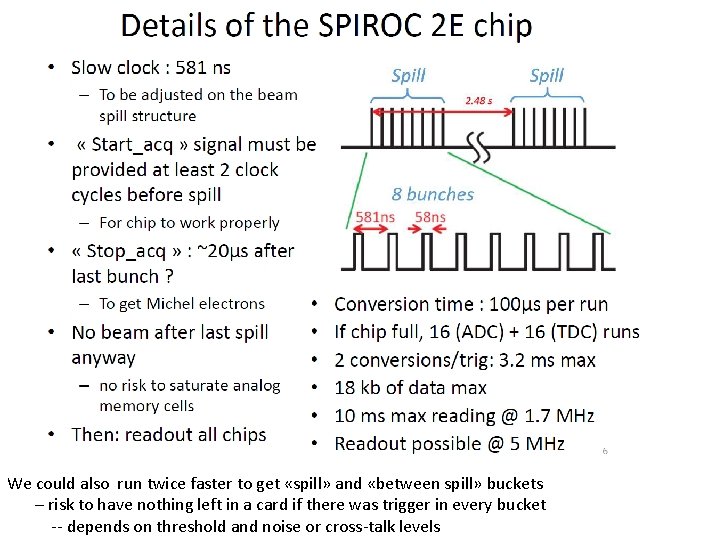

We could also run twice faster to get «spill» and «between spill» buckets – risk to have nothing left in a card if there was trigger in every bucket -- depends on threshold and noise or cross-talk levels

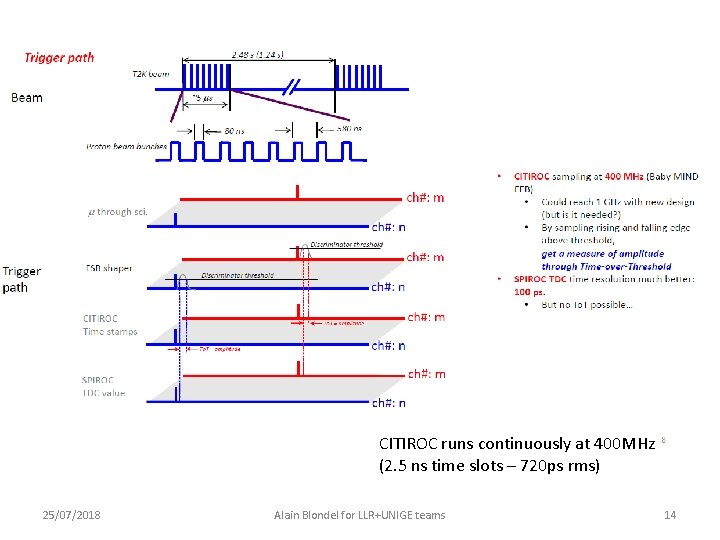

CITIROC runs continuously at 400 MHz (2. 5 ns time slots – 720 ps rms) 25/07/2018 Alain Blondel for LLR+UNIGE teams 14

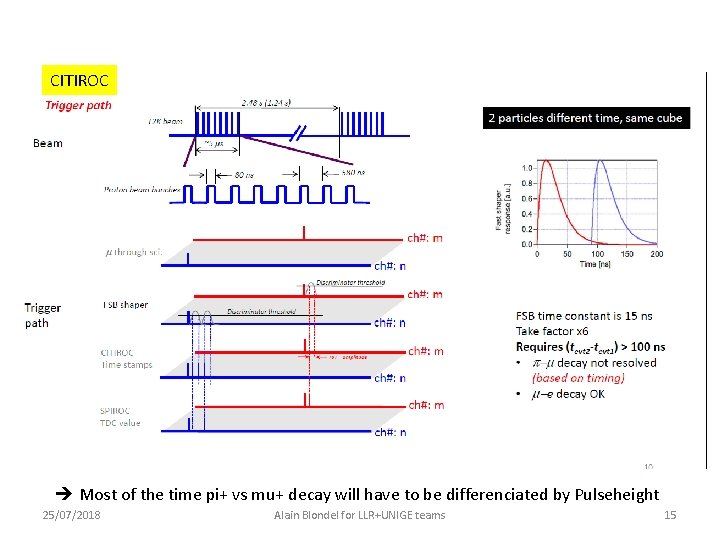

CITIROC Most of the time pi+ vs mu+ decay will have to be differenciated by Pulseheight 25/07/2018 Alain Blondel for LLR+UNIGE teams 15

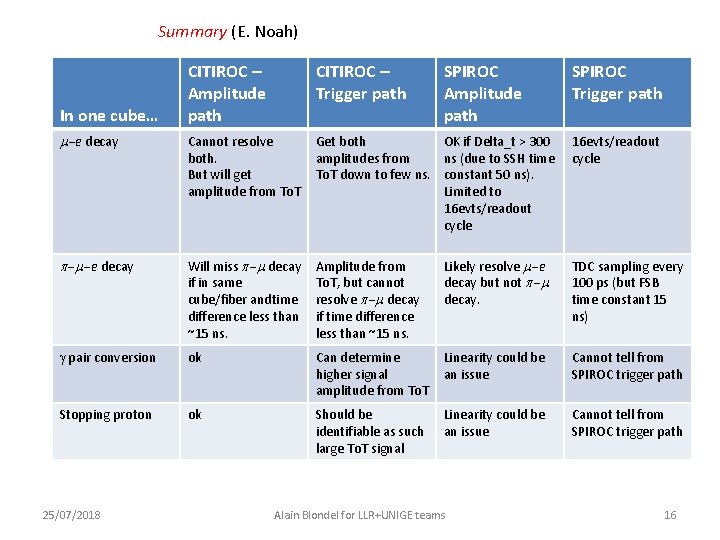

Summary (E. Noah) CITIROC – Amplitude path CITIROC – Trigger path m-e decay Cannot resolve both. But will get amplitude from To. T Get both OK if Delta_t > 300 amplitudes from ns (due to SSH time To. T down to few ns. constant 50 ns). Limited to 16 evts/readout cycle p-m-e decay Will miss p-m decay if in same cube/fiber andtime difference less than ~15 ns. Amplitude from To. T, but cannot resolve p-m decay if time difference less than ~15 ns. Likely resolve m-e decay but not p-m decay. TDC sampling every 100 ps (but FSB time constant 15 ns) g pair conversion ok Can determine higher signal amplitude from To. T Linearity could be an issue Cannot tell from SPIROC trigger path Stopping proton ok Should be identifiable as such large To. T signal Linearity could be an issue Cannot tell from SPIROC trigger path In one cube… 25/07/2018 SPIROC Amplitude path Alain Blondel for LLR+UNIGE teams SPIROC Trigger path 16 evts/readout cycle 16

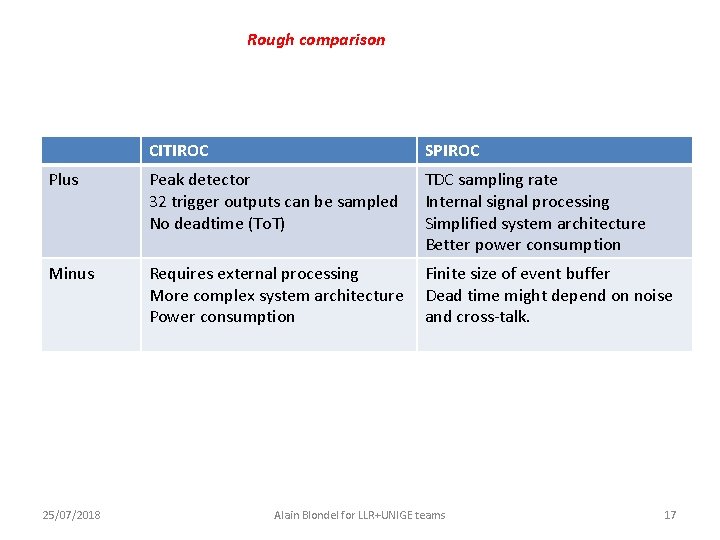

Rough comparison CITIROC SPIROC Plus Peak detector 32 trigger outputs can be sampled No deadtime (To. T) TDC sampling rate Internal signal processing Simplified system architecture Better power consumption Minus Requires external processing More complex system architecture Power consumption Finite size of event buffer Dead time might depend on noise and cross-talk. 25/07/2018 Alain Blondel for LLR+UNIGE teams 17

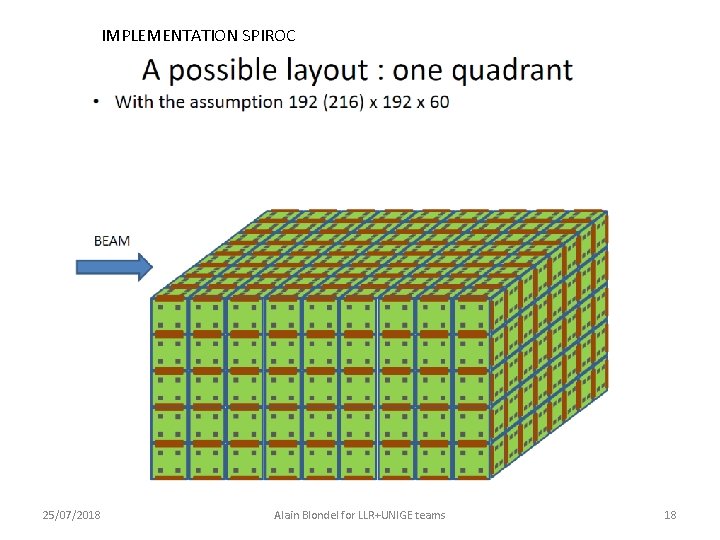

IMPLEMENTATION SPIROC 25/07/2018 Alain Blondel for LLR+UNIGE teams 18

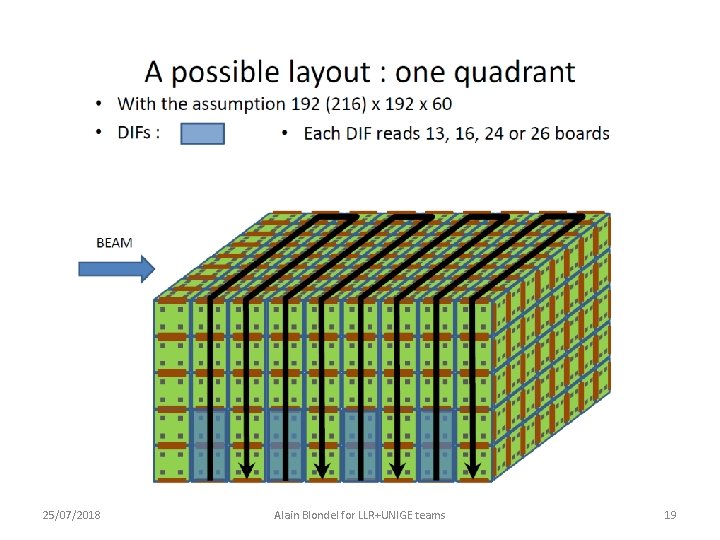

25/07/2018 Alain Blondel for LLR+UNIGE teams 19

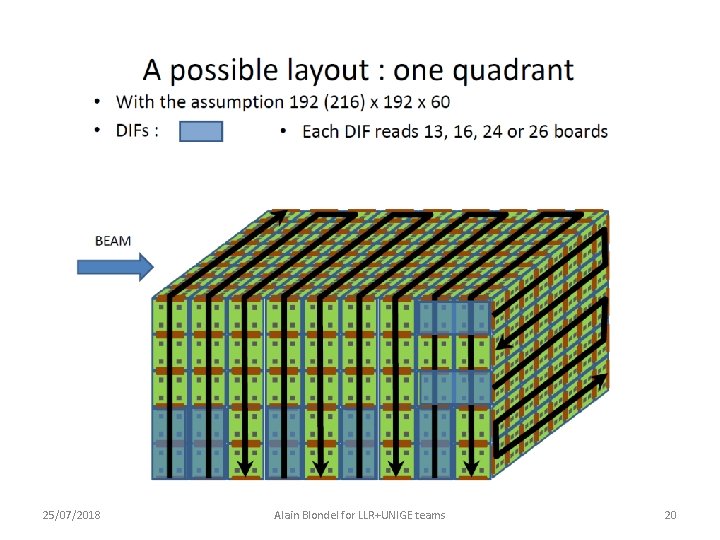

25/07/2018 Alain Blondel for LLR+UNIGE teams 20

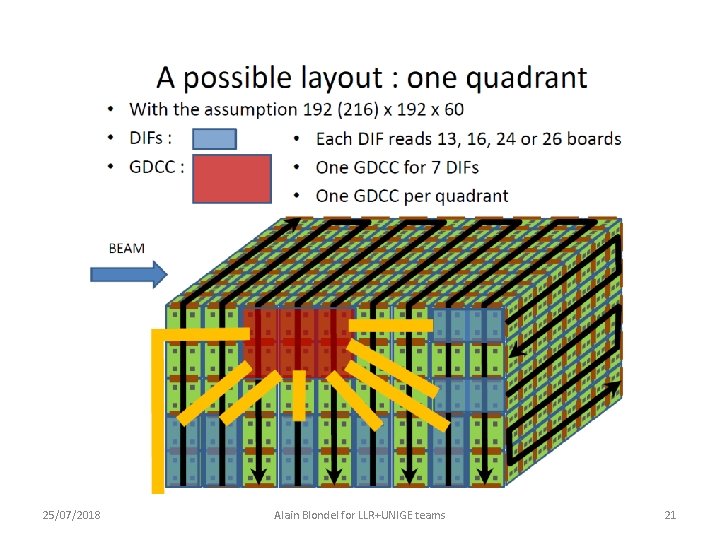

25/07/2018 Alain Blondel for LLR+UNIGE teams 21

25/07/2018 Alain Blondel for LLR+UNIGE teams 22

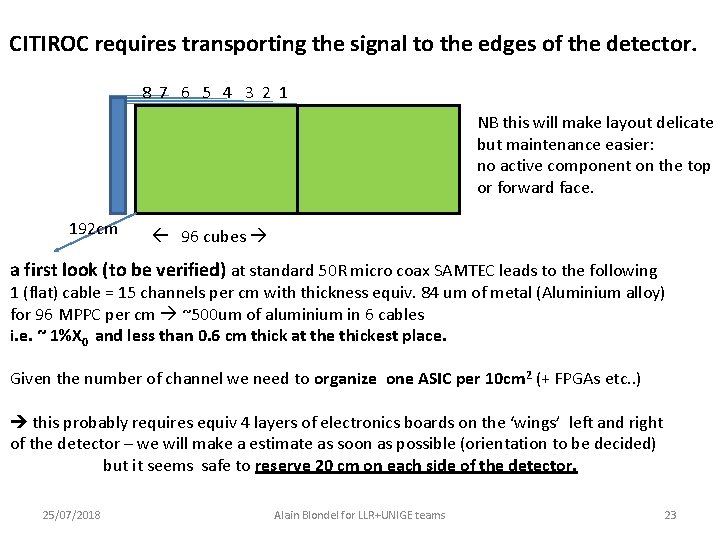

CITIROC requires transporting the signal to the edges of the detector. 8 7 6 5 4 3 2 1 NB this will make layout delicate but maintenance easier: no active component on the top or forward face. 192 cm 96 cubes a first look (to be verified) at standard 50 R micro coax SAMTEC leads to the following 1 (flat) cable = 15 channels per cm with thickness equiv. 84 um of metal (Aluminium alloy) for 96 MPPC per cm ~500 um of aluminium in 6 cables i. e. ~ 1%X 0 and less than 0. 6 cm thick at the thickest place. Given the number of channel we need to organize one ASIC per 10 cm 2 (+ FPGAs etc. . ) this probably requires equiv 4 layers of electronics boards on the ‘wings’ left and right of the detector – we will make a estimate as soon as possible (orientation to be decided) but it seems safe to reserve 20 cm on each side of the detector. 25/07/2018 Alain Blondel for LLR+UNIGE teams 23

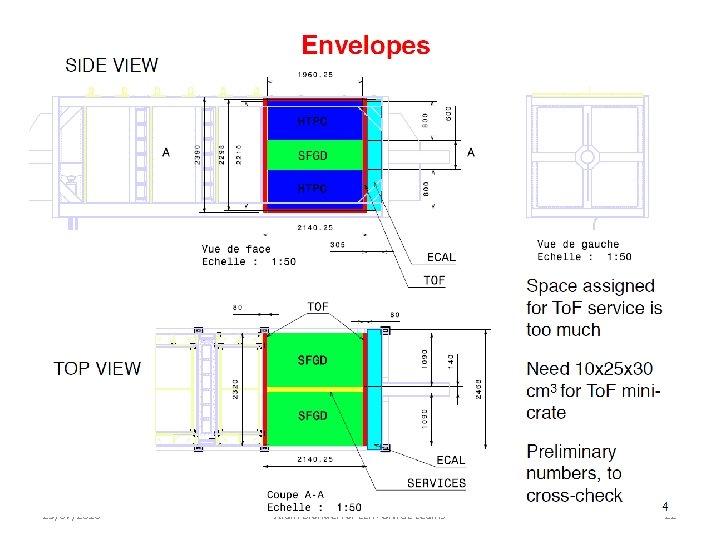

Electronics in these areas… we will need to reduce size to the point where the contents of 80 Baby-MIND mini-crates in these two blue boxes 25/07/2018 Alain Blondel for LLR+UNIGEfit teams 24 of size 200 x 60 x 20 cm. This is an important challenge/risk that will need to be attacked asap.

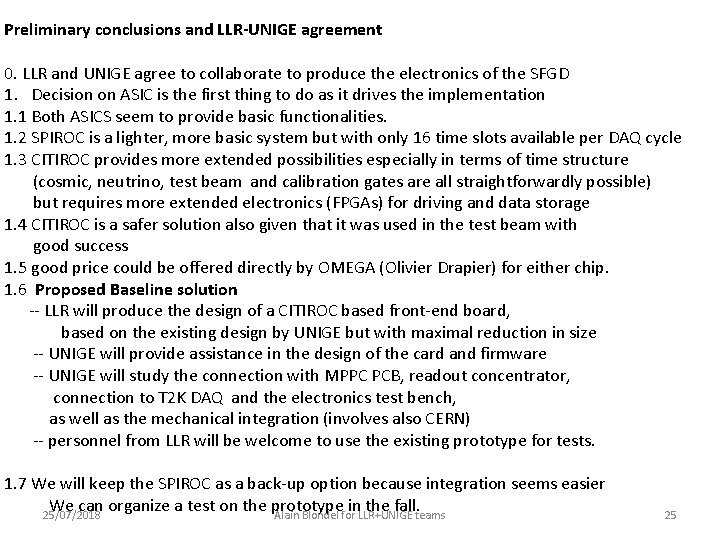

Preliminary conclusions and LLR-UNIGE agreement 0. LLR and UNIGE agree to collaborate to produce the electronics of the SFGD 1. Decision on ASIC is the first thing to do as it drives the implementation 1. 1 Both ASICS seem to provide basic functionalities. 1. 2 SPIROC is a lighter, more basic system but with only 16 time slots available per DAQ cycle 1. 3 CITIROC provides more extended possibilities especially in terms of time structure (cosmic, neutrino, test beam and calibration gates are all straightforwardly possible) but requires more extended electronics (FPGAs) for driving and data storage 1. 4 CITIROC is a safer solution also given that it was used in the test beam with good success 1. 5 good price could be offered directly by OMEGA (Olivier Drapier) for either chip. 1. 6 Proposed Baseline solution -- LLR will produce the design of a CITIROC based front-end board, based on the existing design by UNIGE but with maximal reduction in size -- UNIGE will provide assistance in the design of the card and firmware -- UNIGE will study the connection with MPPC PCB, readout concentrator, connection to T 2 K DAQ and the electronics test bench, as well as the mechanical integration (involves also CERN) -- personnel from LLR will be welcome to use the existing prototype for tests. 1. 7 We will keep the SPIROC as a back-up option because integration seems easier We can organize a test on the prototype in the fall. 25/07/2018 Alain Blondel for LLR+UNIGE teams 25

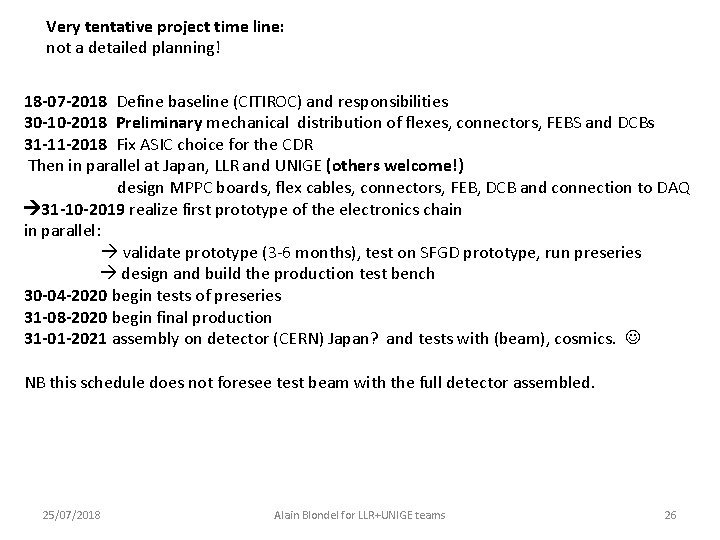

Very tentative project time line: not a detailed planning! 18 -07 -2018 Define baseline (CITIROC) and responsibilities 30 -10 -2018 Preliminary mechanical distribution of flexes, connectors, FEBS and DCBs 31 -11 -2018 Fix ASIC choice for the CDR Then in parallel at Japan, LLR and UNIGE (others welcome!) design MPPC boards, flex cables, connectors, FEB, DCB and connection to DAQ 31 -10 -2019 realize first prototype of the electronics chain in parallel: validate prototype (3 -6 months), test on SFGD prototype, run preseries design and build the production test bench 30 -04 -2020 begin tests of preseries 31 -08 -2020 begin final production 31 -01 -2021 assembly on detector (CERN) Japan? and tests with (beam), cosmics. NB this schedule does not foresee test beam with the full detector assembled. 25/07/2018 Alain Blondel for LLR+UNIGE teams 26

- Slides: 26